Special Issue Reprint

# **Memory Nanomaterials**

Growth, Characterization and Device Fabrication

Edited by Chao Zhao, Guilei Wang and Huihui Li

mdpi.com/journal/nanomaterials

## Memory Nanomaterials: Growth, Characterization and Device Fabrication

## Memory Nanomaterials: Growth, Characterization and Device Fabrication

**Guest Editors**

Chao Zhao Guilei Wang Huihui Li

$\texttt{Basel} \bullet \texttt{Beijing} \bullet \texttt{Wuhan} \bullet \texttt{Barcelona} \bullet \texttt{Belgrade} \bullet \texttt{Novi} \texttt{Sad} \bullet \texttt{Cluj} \bullet \texttt{Manchester}$

Guest Editors Chao Zhao Beijing Superstring Academy of Memory Technology Beijing China

Guilei Wang Beijing Superstring Academy of Memory Technology Beijing China Huihui Li Beijing Superstring Academy of Memory Technology Beijing China

*Editorial Office* MDPI AG Grosspeteranlage 5 4052 Basel, Switzerland

This is a reprint of the Special Issue, published open access by the journal *Nanomaterials* (ISSN 2079-4991), freely accessible at: https://www.mdpi.com/journal/nanomaterials/special\_issues/ Nano\_Memory\_Materials.

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

Lastname, A.A.; Lastname, B.B. Article Title. Journal Name Year, Volume Number, Page Range.

ISBN 978-3-7258-4285-8 (Hbk) ISBN 978-3-7258-4286-5 (PDF) https://doi.org/10.3390/books978-3-7258-4286-5

© 2025 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license. The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) license (https://creativecommons.org/licenses/by-nc-nd/4.0/).

## Contents

| About the Editors                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Ke-Jing Lee, Wei-Shao Lin, Li-Wen Wang, Hsin-Ni Lin and Yeong-Her Wang</b><br>Resistive Switching Memory Cell Property Improvement by Al/SrZrTiO <sub>3</sub> /Al/SrZrTiO <sub>3</sub> /ITO<br>with Embedded Al Layer                                                                                                                             |

| Reprinted from: <i>Nanomaterials</i> <b>2022</b> , <i>12</i> , 4412, https://doi.org/10.3390/nano12244412 1                                                                                                                                                                                                                                          |

| <b>Jingwei Long, Qi Hu, Zhengping Yuan, Yunsen Zhang, Yue Xin, Jie Ren, et al.</b><br>Comparative Study of Temperature Impact in Spin-Torque Switched Perpendicular and<br>Easy-Cone MTJs                                                                                                                                                            |

| Reprinted from: <i>Nanomaterials</i> <b>2023</b> , <i>13</i> , 337, https://doi.org/10.3390/nano13020337 <b>11</b>                                                                                                                                                                                                                                   |

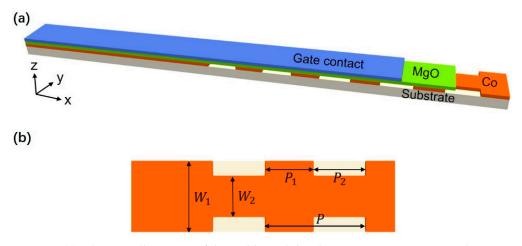

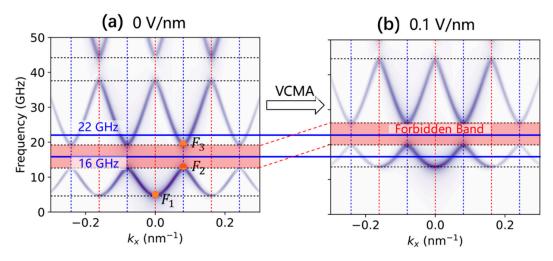

| Huihui Li, Bowen Dong, Qi Hu, Yunsen Zhang, Guilei Wang, Hao Meng and Chao ZhaoA Voltage-Modulated Nanostrip Spin-Wave Filter and Spin Logic Device ThereofReprinted from: Nanomaterials 2022, 12, 3838, https://doi.org/10.3390/nano1221383822                                                                                                      |

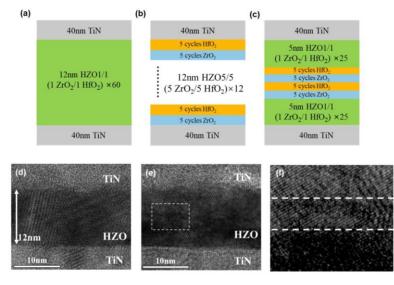

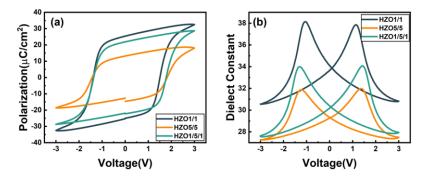

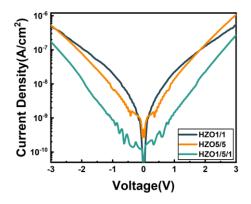

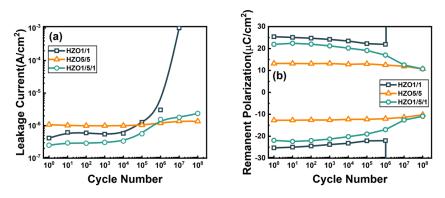

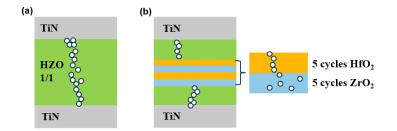

| <b>Meiwen Chen, Shuxian Lv, Boping Wang, Pengfei Jiang, Yuanxiang Chen, Yaxin Ding, et al.</b><br>Improved Endurance of Ferroelectric Hf <sub>0.5</sub> Zr <sub>0.5</sub> O <sub>2</sub> Using Laminated-Structure Interlayer<br>Reprinted from: <i>Nanomaterials</i> <b>2023</b> , <i>13</i> , 1608, https://doi.org/10.3390/nano13101608 <b>30</b> |

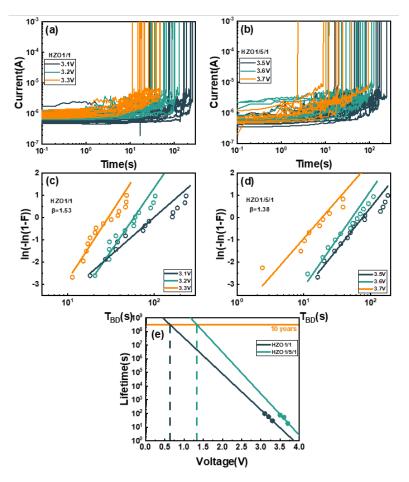

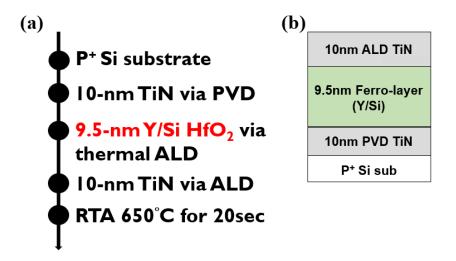

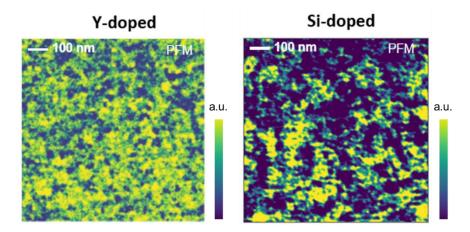

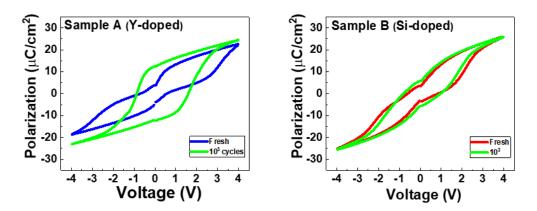

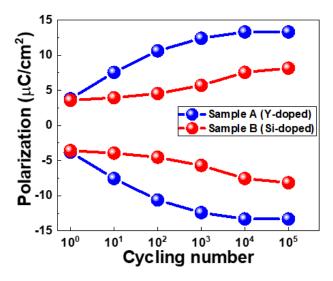

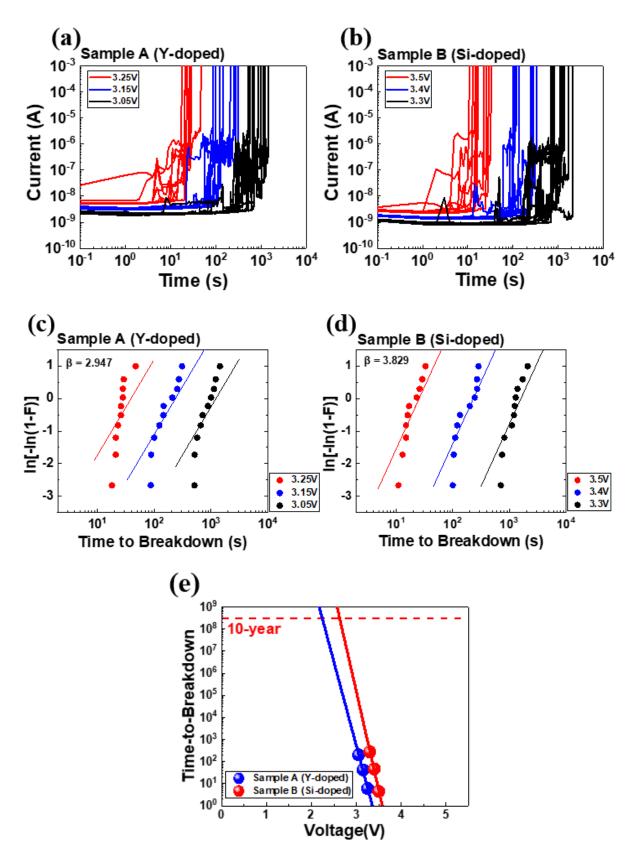

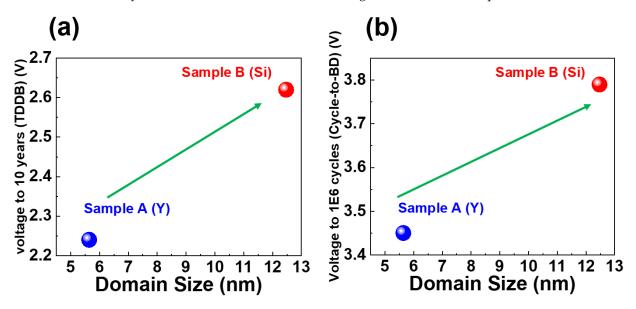

| <b>Ting-Yu Chang, Kuan-Chi Wang, Hsien-Yang Liu, Jing-Hua Hseun, Wei-Cheng Peng, Nicolò Ronchi, et al.</b><br>Comprehensive Investigation of Constant Voltage Stress Time-Dependent Breakdown and Cycle-to-Breakdown Reliability in Y-Doped and Si-Doped HfO <sub>2</sub> Metal-Ferroelectric-Metal                                                  |

| Memory<br>Reprinted from: <i>Nanomaterials</i> <b>2023</b> , <i>13</i> , 2104, https://doi.org/10.3390/nano13142104 <b>40</b>                                                                                                                                                                                                                        |

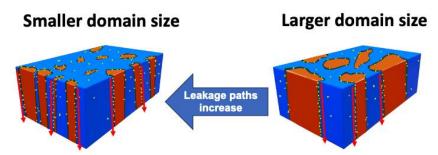

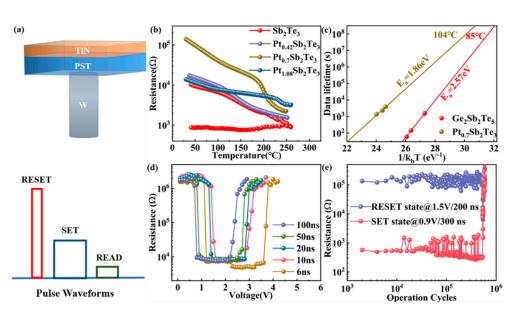

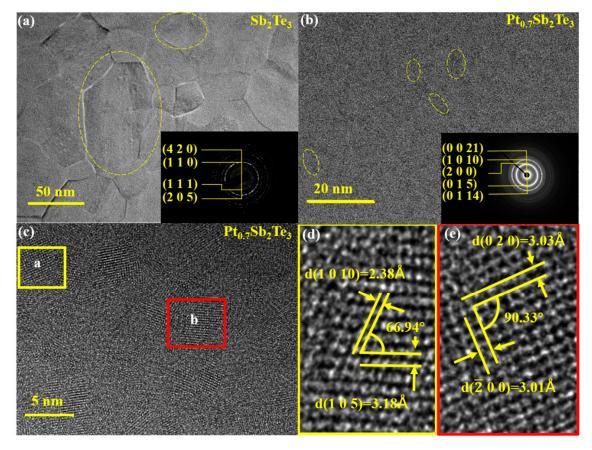

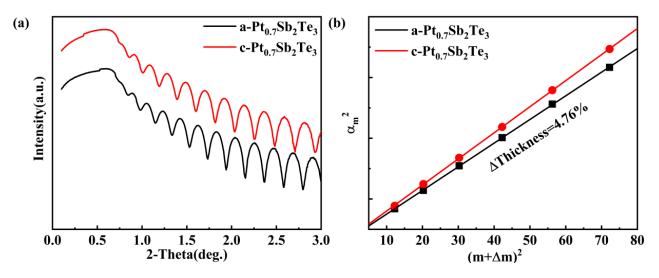

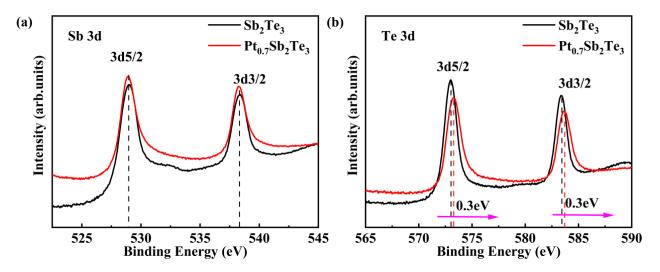

| Yang Qiao, Jin Zhao, Haodong Sun, Zhitang Song, Yuan Xue, Jiao Li and Sannian SongPt Modified Sb2Te3 Alloy Ensuring High—Performance Phase Change MemoryReprinted from: Nanomaterials 2022, 12, 1996, https://doi.org/10.3390/nano1212199649                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                      |

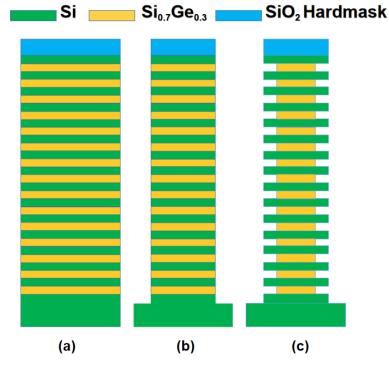

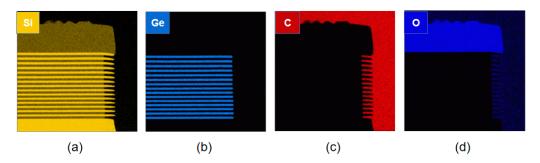

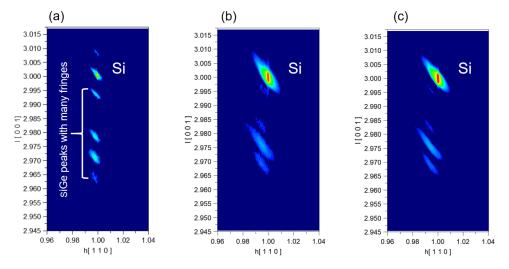

| Enxu Liu, Junjie Li, Na Zhou, Rui Chen, Hua Shao, Jianfeng Gao, et al.<br>Study of Selective Dry Etching Effects of 15-Cycle Si <sub>0.7</sub> Ge <sub>0.3</sub> /Si Multilayer Structure in<br>Gate-All-Around Transistor Process                                                                                                                   |

| Reprinted from: <i>Nanomaterials</i> <b>2023</b> , <i>13</i> , 2127, https://doi.org/10.3390/nano13142127 <b>57</b>                                                                                                                                                                                                                                  |

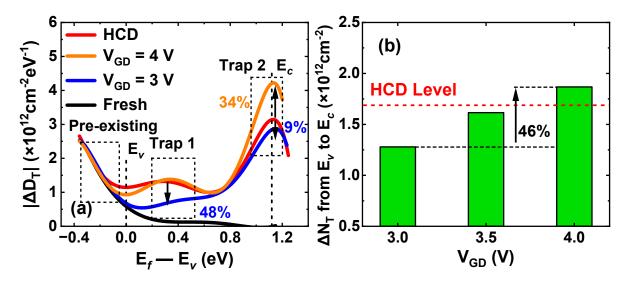

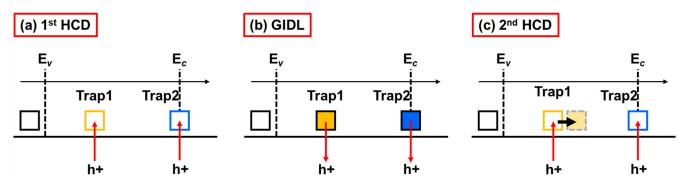

| <b>Hao Chang, Guilei Wang, Hong Yang, Qianqian Liu, Longda Zhou, Zhigang Ji, et al.</b><br>Insight into over Repair of Hot Carrier Degradation by GIDL Current in Si p-FinFETs Using<br>Ultra-Fast Measurement Technique                                                                                                                             |

| Reprinted from: <i>Nanomaterials</i> <b>2023</b> , <i>13</i> , 1259, https://doi.org/10.3390/nano13071259 69                                                                                                                                                                                                                                         |

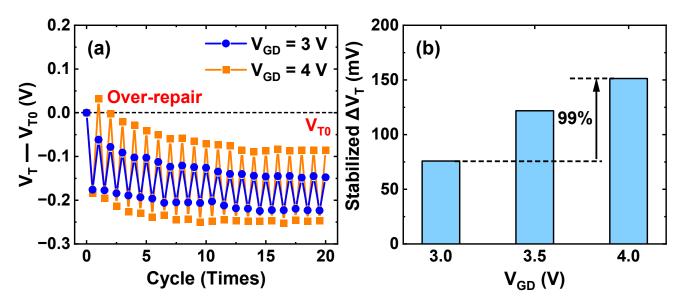

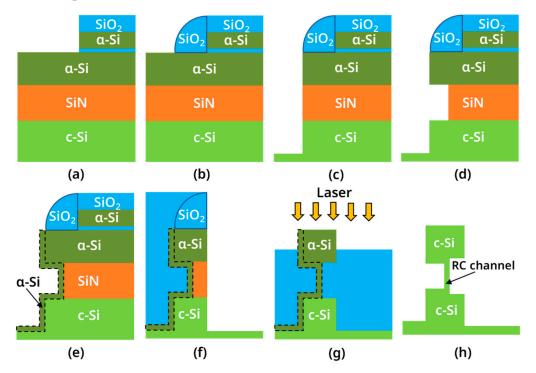

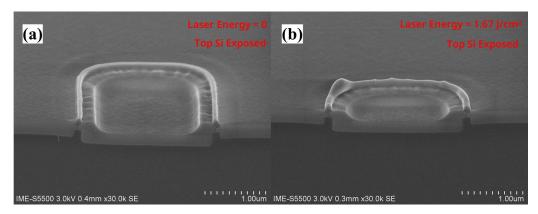

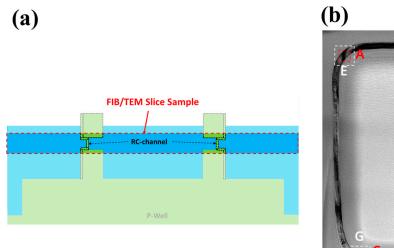

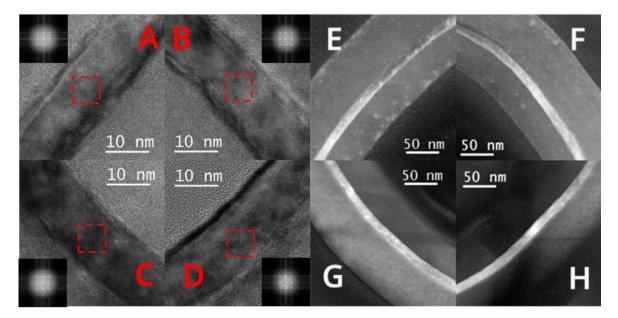

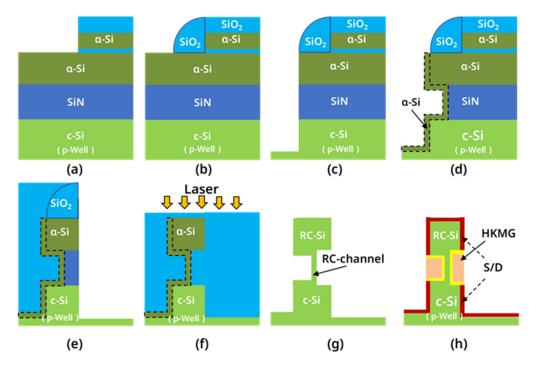

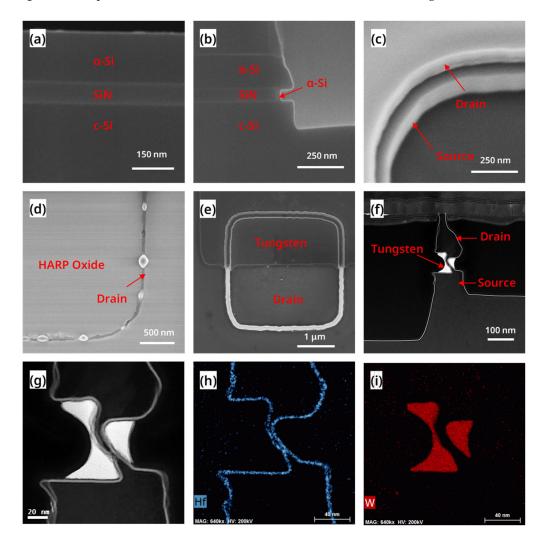

| <b>Zhuo Chen, Huilong Zhu, Guilei Wang, Qi Wang, Zhongrui Xiao, Yongkui Zhang, et al.</b><br>High-Quality Recrystallization of Amorphous Silicon on Si (100) Induced via Laser Annealing at<br>the Nanoscale                                                                                                                                         |

| Reprinted from: <i>Nanomaterials</i> <b>2023</b> , <i>13</i> , 1867, https://doi.org/10.3390/nano13121867 <b>81</b>                                                                                                                                                                                                                                  |

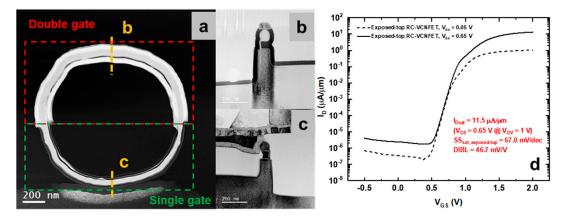

| <b>Zhuo Chen, Huilong Zhu, Guilei Wang, Qi Wang, Zhongrui Xiao, Yongkui Zhang, et al.</b><br>Investigation on Recrystallization Channel for Vertical C-Shaped-Channel Nanosheet FETs by<br>Laser Annealing                                                                                                                                           |

Reprinted from: *Nanomaterials* **2023**, *13*, 1786, https://doi.org/10.3390/nano13111786 ..... **94**

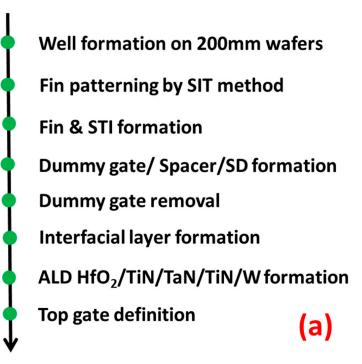

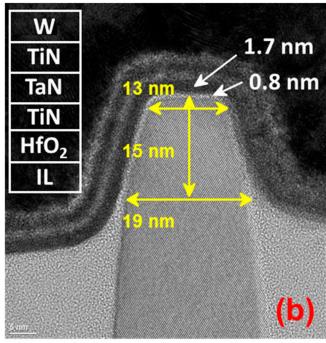

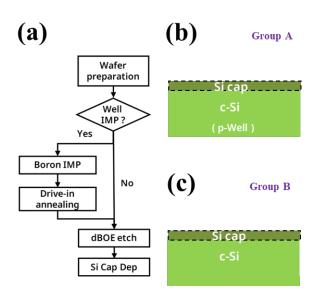

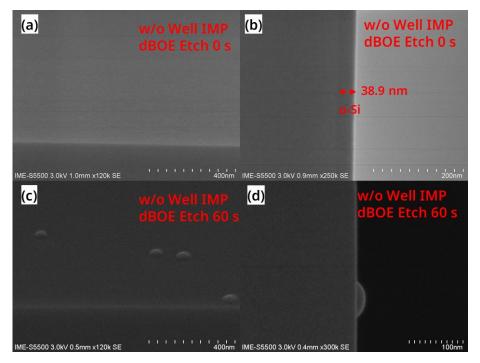

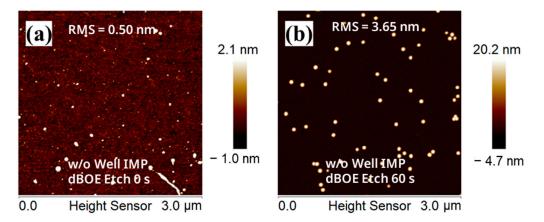

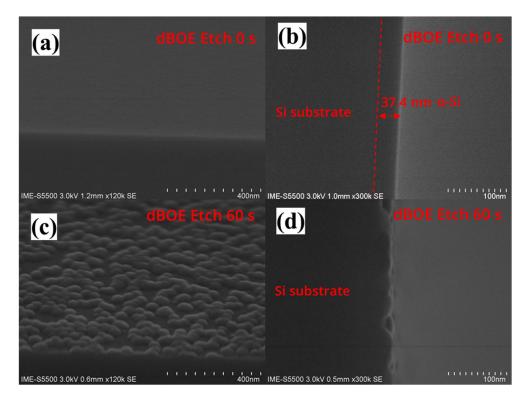

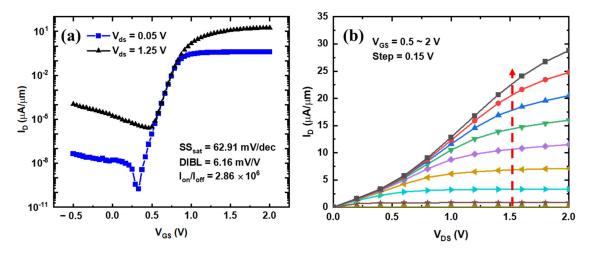

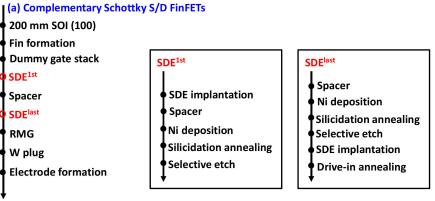

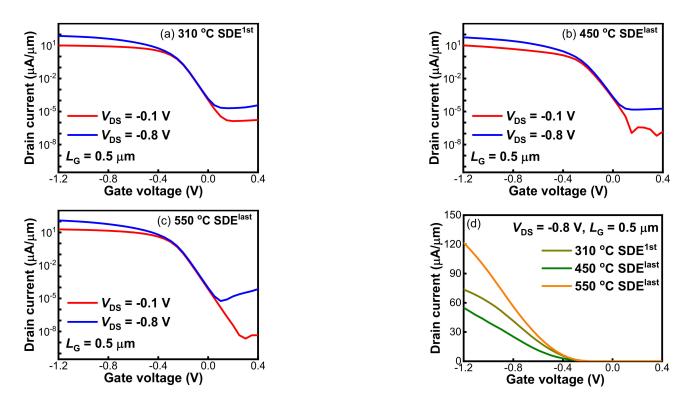

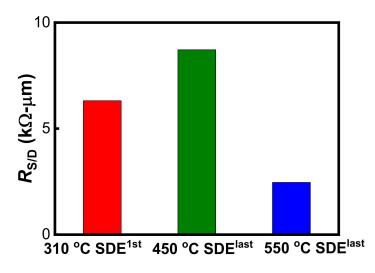

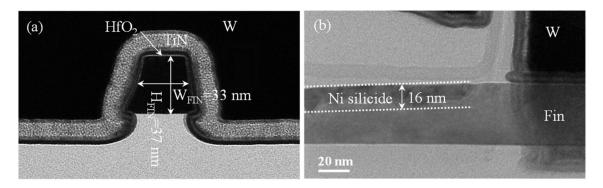

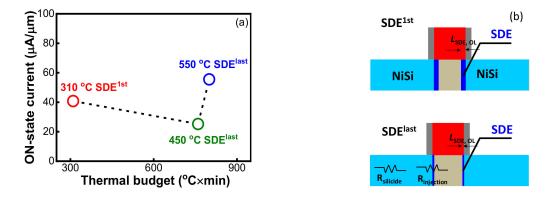

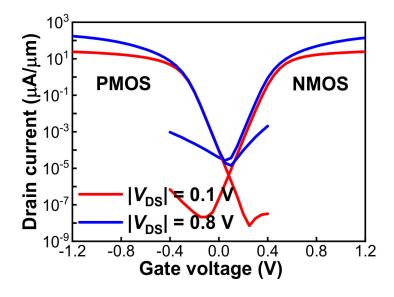

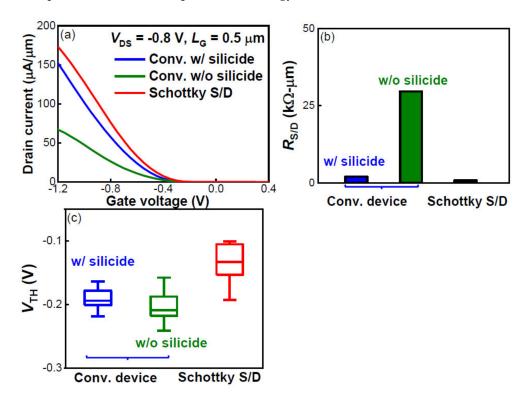

Shujuan Mao, Jianfeng Gao, Xiaobin He, Weibing Liu, Jinbiao Liu, Guilei Wang, et al. Low-Temperature (≤500 °C) Complementary Schottky Source/Drain FinFETs for 3D Sequential Integration

Reprinted from: *Nanomaterials* **2022**, *12*, 1218, https://doi.org/10.3390/nano12071218 . . . . . . **104**

## About the Editors

#### Chao Zhao

Chao Zhao received PhD degree from Katholieke Universiteit Leuven of Belgium in Material Science and Engineering in 1999. From 2000 to 2010, he worked in IMEC as a senior scientist, and from 2010 to 2021, he served as a full professor in University of Chinese Academy of Sciences and IMECAS. Since 2021, he has been working in Beijing Superstring Academy of Memory Technology as Senior VP. He has also been a part-time professor at Beihang University since 2013.

His research focuses on CMOS and Memory processing technology. He has authored or coauthored over 408 scientific papers, 4 book chapters, and 2 books ("CMOS Past, Present and Future" by Elsevier in 2018 and "Semiconductor Process and Integrated Circuit Manufacturing Technology" by Science Press in 2023) and has been guest editor of two Special Issues, "Advanced Microelectronic and Optoelectronic Materials" (JMSE, 2020) and "Memory Nanomaterials: Growth, Characterization and Device Fabrication (MDPI, 2023)".

He is the fellow of European Academy of Sciences (EurASc), and the Member of the Council and Deputy Secretary General of Chinese Materials Research Society (C-MRS).

#### Guilei Wang

Guilei Wang received his PhD in 2016 from the University of Chinese Academy of Sciences. He has been worked as a professor at the Institute of Microelectronics of Chinese Academy of Sciences (IMECAS) until 2021. In October 2021, he joined the Beijing Superstring Academy of Memory Technology as a full professor.

His research focuses on new materials, devices, and process integration for the IC industry. So far, more than 160 research papers have been published in international journals. He has completed more than 300 patent applications. He has published 1 book (Investigation on SiGe Selective Epitaxy for Source and Drain Engineering in 22 nm CMOS Technology Node and Beyond), and 1 SiGe epitaxy chapter.

He served as a member of the Technical Program Committee (TPC) of the 2018 European Materials Research Society (E-MRS) Spring Conference. He has been guest editor of three Special Issues. He has won the "E-MRS Young Scientist", "Springer Excellent Doctorate Thesis", and "Excellent Member of the Youth Innovation Promotion Association of the Chinese Academy of Sciences" awards.

#### Huihui Li

Huihui Li holds a bachelor's degree in theoretical physics from Lanzhou University and a PhD in materials science and engineering from the National University of Singapore. He has previously worked at CAS, CETHIK Group, and Beijing Superstring Academy of Memory Technology, conducting materials and process research related to semiconductor memory technologies such as MRAM, FeRAM, and DRAM. He is currently with Changxin Memory Technologies, working on advanced materials and devices for DRAM.

### Article Resistive Switching Memory Cell Property Improvement by Al/SrZrTiO<sub>3</sub>/Al/SrZrTiO<sub>3</sub>/ITO with Embedded Al Layer

Ke-Jing Lee <sup>1,2</sup>, Wei-Shao Lin <sup>1</sup>, Li-Wen Wang <sup>1</sup>, Hsin-Ni Lin <sup>3</sup> and Yeong-Her Wang <sup>1,2,\*</sup>

- <sup>1</sup> Institute of Microelectronics, Department of Electrical Engineering, National Cheng-Kung University, Tainan 701, Taiwan

- <sup>2</sup> Program on Semiconductor Process Technology, Academy of Innovative Semiconductor and Sustainable Manufacturing, National Cheng-Kung University, Tainan 701, Taiwan

<sup>3</sup> Department of Physics, National Sun Yat-sen University, Kaohsiung 804, Taiwan

\* Correspondence: yhw@ee.ncku.edu.tw; Tel.: +886-6-275-7575-62352; Fax: +886-6-2080598

**Abstract:** The SrZrTiO<sub>3</sub> (SZT) thin film prepared by sol-gel process for the insulator of resistive random-access memory (RRAM) is presented. Al was embedded in the SZT thin film to enhance the switching characteristics. Compared with the pure SZT thin-film RRAM, the RRAM with the embedded Al in SZT thin film demonstrated outstanding device parameter improvements, such as a resistance ratio higher than 10<sup>7</sup>, lower operation voltage (V<sub>SET</sub> = -0.8 V and V<sub>RESET</sub> = 2.05 V), uniform film, and device stability of more than 10<sup>5</sup> s. The physical properties of the SZT thin film and the embedded-Al SZT thin-film RRAM devices were probed.

Keywords: resistive random-access memory (RRAM); sol-gel; strontium zirconate titanium

#### 1. Introduction

Among various candidates for nonvolatile memories, resistive random-access memory (RRAM) attracts considerable attention owing to its advantages, such as simple metal– insulator-metal (MIM) structure, fast operation speed, low operation voltage, and low fabrication temperature. Numerous materials, such as transition metal oxides (HfO<sub>2</sub>, TiO<sub>2</sub>, and NiO), organic material (composites containing nanoparticles and polyimide), or perovskite oxides ( $SrZrO_3$  and  $SrTiO_3$ ), have been investigated as potential materials for RRAMs. In this study, we focused on the SrTiO<sub>3</sub> material because of its high dielectric constant, low dielectric loss, tenability, high breakdown strength, low leakage current, and great film quality [1]. Numerous attempts have been exerted to further improve the properties of SrTiO<sub>3</sub>-based ceramics. Doping is considered an effective approach for altering their properties [2]. Reproducible resistive switching behaviors have been observed in doped perovskite oxide films [3,4], such as Mo-doped SrTiO<sub>3</sub> [5], Mg-doped SrTiO<sub>3</sub> [6], Nb-doped SrTiO<sub>3</sub> films [7], and Ni-doped SrTiO<sub>3</sub> films [3]. Several studies have indicated that  $Zr^{4+}$  in SrTiO<sub>3</sub> can stabilize the charge of Ti<sup>4+</sup> and suppress oxygen dissociation [1,2,8]. In addition, our previous study showed that the addition of Zr can effectively improve the surface morphology of insulators [9]. Moreover, the sol-gel process has advantages, such as low fabrication temperature, low cost, and easy adjustment of proportions. This process can be applied in numerous devices [10]. Based on the above advantages and research results, in this work, we utilized Zr in the doping process to fabricate  $SrZrTiO_3$  (SZT) using the sol-gel process for RRAM insulators.

Various inserted metal layers in the insulator layer, including Cu, Pt, and Ti, improve the resistive switching properties of RRAMs [11–14]. However, a relatively limited number of studies have been performed regarding the mechanism of embedded metal-based RRAM devices. In this study, the effects of Al-included SZT on the resistive switching properties of SZT thin film for RRAM applications were also investigated. For comparison, a memory device with a single-SZT active layer was also fabricated and characterized.

1

#### 2. Materials and Methods

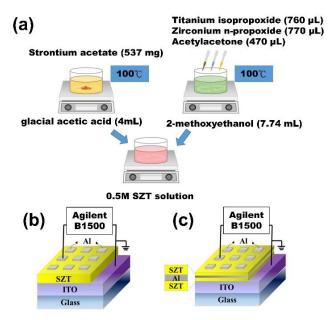

The solutions used in this study were prepared in reference to the previous literature, and the additives and ratios were varied based on experimental requirements [8,15,16]. The 0.5 M SZT solution was prepared in three steps (Figure 1a). First, strontium acetate (537 mg) was dissolved in glacial acetic acid (4 mL) by stirring and then heated on a 100 °C hot plate until complete dissolution (A1 solution). Titanium isopropoxide (760  $\mu$ L) and zirconium n-propoxide (770  $\mu$ L) were mixed with acetylacetone (470  $\mu$ L) and dissolved in 2-methoxyethanol (7.74 mL) by stirring (A2 solution). Finally, A1 was slowly dropped into A2 until a completely transparent solution was obtained (mole proportion of Sr:Zr:Ti was approximately 1:1:1). After chemically cleaning the substrate, the prepared 0.5 M SZT solution was spun coated on an indium tin oxide (ITO)/glass substrate. Each layer was baked at 100 °C for 15 min to remove volatile materials. A 90 nm-thick Al film with an area of 3 mm<sup>2</sup> was deposited with a shadow mask using DC magnetron sputtering as the top electrode (TE) of the MIM structure, whereas ITO served as the bottom electrode (BE). Figure 1b shows the schematic configuration of the A1/SZT/ITO structures.

**Figure 1.** (a) Preparation of 0.5 M SZT solution. (b) Schematic of SZT-based RRAM devices. (c) Schematic of Al embedded in SZT thin-film RRAM devices.

The SZT/Al/SZT tri-layer structure was deposited on the ITO/glass substrate. Both SZT films were prepared through the same process above, and Al was embedded by DC magnetron sputtering. Finally, the same processes were applied for Al TEs. For comparison, we fabricated four different thicknesses of embedded Al layer (5, 18, 25, and 33 nm). Figure 1c displays the schematic configuration of embedded Al in SZT thin-film RRAM devices. Transmission electron microscopy (TEM) analysis was carried out using a JEM-2100F electron microscope. The X-ray diffraction (XRD) spectra were developed via BRUKER, D8 DISCOVER SSS Multi-Function High Power XRD using the copper K $\alpha$  line with  $\lambda = 0.154060$  nm. The roughness value and surface morphology of the films were calculated using atomic force microscopy (AFM, Dimension ICON with NanoScope V controller, Bruker, Billerica, MA, USA). X-ray photoelectron spectroscopy (XPS) was performed using a PHI 5000 VersaProbe. Electrical measurements were performed using an Agilent B1500 semiconductor parameter analyzer.

#### 3. Results

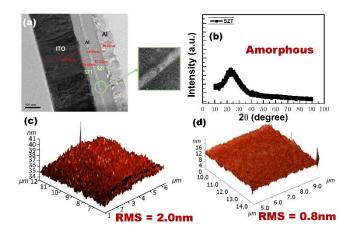

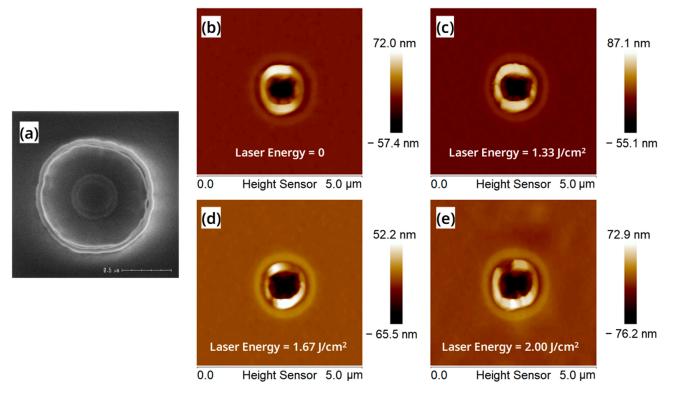

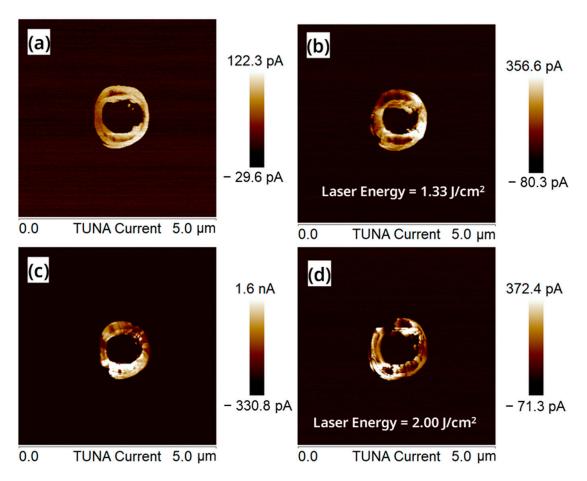

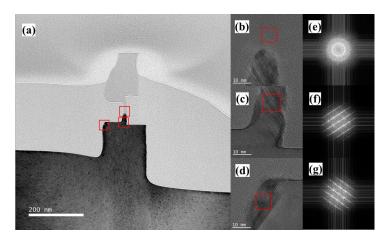

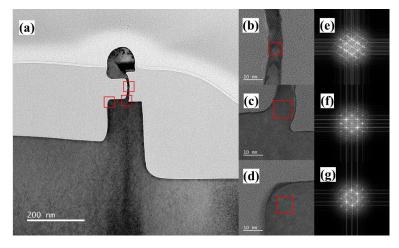

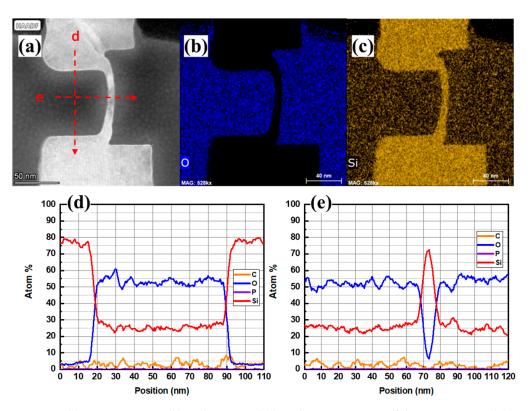

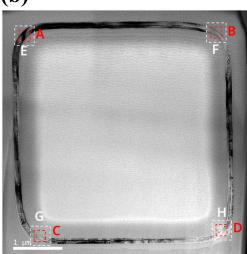

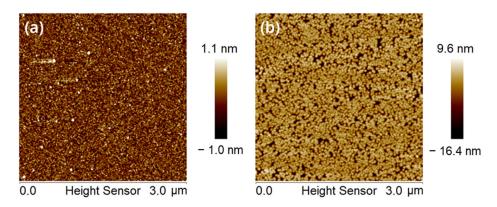

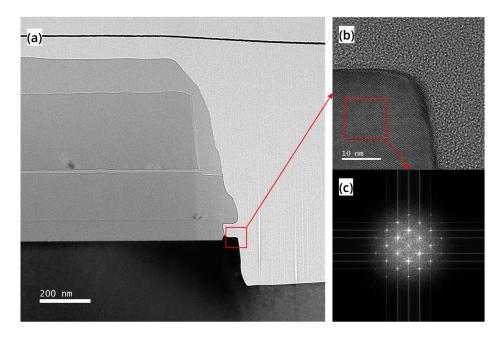

Figure 2a presents the TEM image of the cross-sectional SZT/Al/SZT tri-layered thin films sandwiched between ITO BE and Al TE. The estimated thicknesses of the top SZT

layer, Al interlayer, and bottom SZT layer were 54, 18, and 67 nm, respectively. The thin films were uniform, and the interfaces were clear. Figure 2b depicts the XRD analysis of the SZT thin film. As shown in the analysis results, no evident peak was observed in the XRD spectrum. The SZT thin film prepared in this experiment had an amorphous phase. Compared with the polycrystalline phase, the amorphous phase is preferred for dielectric layer materials because the former may lead to a high-grain boundary leakage current and a rough film surface [17]. The AFM images in Figure 2c,d reveal the surface morphology of the SZT and SZT/Al/SZT tri-layered thin films. The root-mean-square roughness ( $R_{rms}$ ) values of SZT and the SZT/Al/SZT thin film were approximately 2.0 and 0.8 nm, respectively. The roughness of the thin films decreased due to the insertion of Al layer.

**Figure 2.** (a) TEM image of cross-sectional SZT/Al/SZT tri-layered thin films sandwiched between ITO BE and Al TE. (b) XRD spectrum of SZT thin film. AFM image of (c) SZT and (d) SZT/Al/SZT tri-layered thin films.

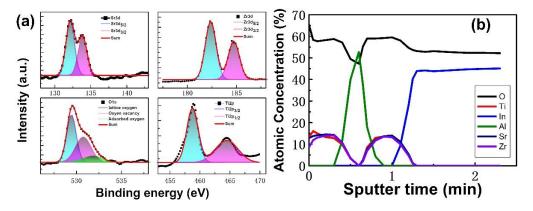

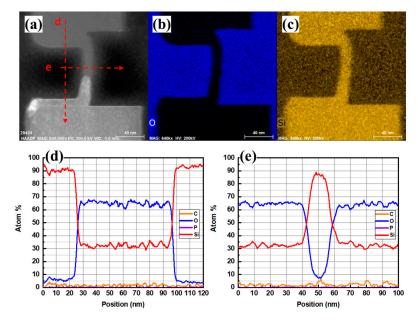

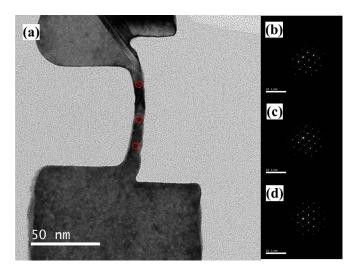

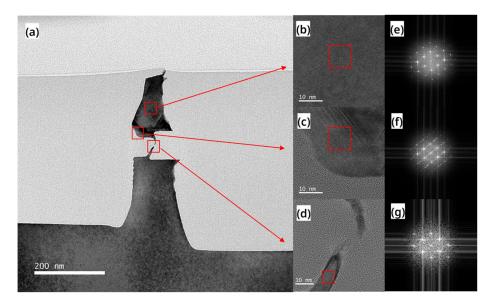

The XPS analysis was used to obtain the chemical composition of SZT thin film, as shown in Figure 3a. The atomic percentage of Sr, Zr, Ti, and O were obtained as 13%, 11%, 16%, and 60%, respectively. By fitting the peaks of Sr 3d signal can be decomposed into two peaks of Sr  $3d_{5/2}$  and Sr  $3d_{3/2}$ , which are centered at 132.7 and 134.1 eV, respectively. The peak at 132.7 eV can be attributed to SrTiO<sub>3</sub>, and the peak at 134.1 eV can be attributed to  $SrCO_3$ . By fitting the peaks of Zr3d signal can be decomposed into two peaks of Zr3d5/2 and Zr 3d<sub>3/2</sub>, which are centered at 182 and 184.4 eV, respectively. This result confirms that most of Zr atoms are incorporated at Ti lattice site instead of forming  $ZrO_2$  [18,19]. The binding energy around 182 and 184.4 eV are assigned for  $ZrTiO_4$ . The peaks for the O1s signal may be consistently fitted by three different near-Gaussian subpeaks centered at 529.2, 530.9, and 532.1 eV. The binding energy of lattice oxygen is 529.2 eV, which is attributed to the O<sub>2</sub> ions bonded with Sr, Zr, and Ti ions. The peaks located at 530.9 eV were associated with non-lattice oxygen ions, such as oxygen vacancy, and the peak at 532.1 eV corresponds to surface adsorption oxygen in the SrTiO<sub>3</sub> catalyst [3,9,20]. Peaks fitting analyses of the Ti 2p signal can be decomposed into two peaks of Ti  $2p_{3/2}$ and Ti  $2p_{1/2}$ , with two components of the binding energies at 458.8 eV and 464.3 eV, which are attributed to  $SrTiO_3$  and  $ZrTiO_4$ . To investigate the possible inter-diffusion in the SZT/Al/SZT tri-layer, we determined the XPS depth profile of the SZT/Al/SZT tri-layer thin film (Figure 3b). The Al concentration increased, and Sr, Zr, and Ti concentrations correspondingly decreased with depth after 36 s Ar<sup>+</sup> sputtering. This result demonstrated the significant interfacial diffusion between SZT/Al/SZT, which is in good agreement with the TEM cross-sectional image. In spite of this finding, the memory units of the SZT/Al/SZT tri-layer structure on ITO-coated glass have been fabricated by sputtering [21,22].

**Figure 3.** (a) High-resolution XPS spectra of Sr3d, Zr3d, Ti2p, and O1s of the SZT thin film. (b) Atomic concentrations of six elements in the SZT/Al/SZT tri-layered thin film with XPS depth profiling.

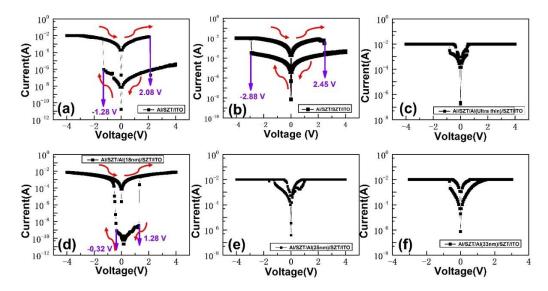

Figure 4a depicts the bipolar and reproducible resistive switching behaviors of the Al/SZT/ITO structures. During the negative sweep from 0 to -4 V, the current increased sharply, a phenomenon called the "set" process, switching from a high resistance state (HRS) to a low resistance state (LRS). Sequentially, during the positive sweep from 0 to 4 V, an abrupt decrease in current, that is, the "reset" process, was observed, and it switched the resistance state from LRS to HRS with 10 mA compliance current. The  $V_{SET}/V_{RESET}$ of Al/SZT/ITO was -1.28 V/+2.08 V. The ON/OFF ratio of the devices was around  $10^3$ . Figure 4b shows the Al/SZT/SZT/ITO RRAM devices. The set voltage ( $V_{SET}$ ) was -2.88 V, and the reset voltage ( $V_{RESET}$ ) was located at +2.48 V. The ON/OFF ratio of the devices was around 10. Figure 4c-f shows the discussed resistive switching I-V characteristic of different thicknesses (5, 18, 25, and 33 nm) of the embedded Al. Therefore, the observed I–V characteristic of the 18 nm embedded Al displayed an especially outstanding performance. However, the memory margins of embedded Al layer with different thicknesses were insufficient for memory application. The V<sub>SET</sub>/V<sub>RESET</sub> of Al/SZT/Al (18 nm)/SZT/ITO was -0.32/+1.28 V (Figure 4d). The ON/OFF ratio of the devices was around  $10^7$ . No significant switching behavior was observed in the embedded structure with different thicknesses (5, 25, and 33 nm) of Al (Figure 4c,e,f).

**Figure 4.** I–V switching curves of (**a**) Al/SZT/ITO, (**b**) Al/SZT/SZT/ITO, and (**c**–**f**) Al/SZT/different thicknesses (5, 18, 25, and 33 nm) of embedded metal –Al/SZT/ITO device RRAMs.

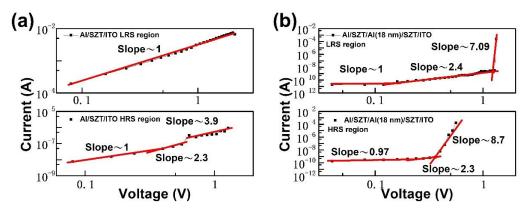

To probe the mechanisms of resistive switching characteristics of SZT-based RRAM, we performed the curve fittings of conduction mechanisms for HRS and LRS in the

Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO devices, and the I–V characteristic was plotted in log-log scale (Figure 5a,b). At low applied voltage, the slope of HRS was very close to linear. As the voltage increased, the current of HRS followed a voltage-square dependence. With the continuous increase in bias voltage, the current of HRS increased rapidly, corresponding to the steep increase in the current region. After the abrupt increase in its region, the current showed voltage-square dependence again. The fitting results of HRS illustrated that the current showed typical space-charge-limited conduction, which consists of the ohmic region (I  $\propto$  V), trap-filled limit current (I  $\propto$  V<sup>2</sup>), and Child's law region (I  $\propto$  V<sup>2</sup>) [23,24].

**Figure 5.** Double logarithmic plot and linear fitting of the switching I–V curve of (**a**) Al/SZT/ITO and (**b**) Al/SZT/Al (18 nm)/SZT/ITO device RRAMs.

However, the conduction behaviors of the LRS showed distinct features for Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO devices. By contrast, the curve fitting of LRS of Al/SZT/ITO device showed the ohmic conduction behavior, coinciding with a conducting filamentary model [25,26]. The I-V curve of the LRS of Al/SZT/Al (18 nm)/SZT/ITO device consisted of the ohmic region (I  $\propto$  V) and trap-filled limit current (I  $\propto$  V<sup>2</sup>) and Child's law region (I  $\propto$  V<sup>2</sup>), which indicates that resistance switching in Al/SZT/Al (18 nm)/SZT/ITO device was mediated by a carrier trapping/de-trapping process [27]. They can remain below V<sub>RESET</sub> in LRS Part 3 but reset did not occur until V<sub>RESET</sub> was reached again in HRS Part 4 because of the lag induced by the relaxation of trap-filled states (Figure 4d). The simple embedded Al layer not only remarkably improved the device parameters but essentially altered the switching mechanism.

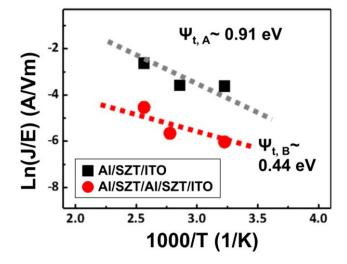

The trap depth ( $\psi_t$ ) of ~0.91 eV for the SZT memory device at the HRS can be extrapolated from an intercept of ln(J/E) as the function of temperature (Figure 6) [24,28].  $\psi_{t,A}$  and  $\psi_{t,B}$  are the trap depth of the Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO structure, respectively. The equivalent trap depth can be reduced to ~0.44 eV after the insertion of Al layer. The possible carrier transporting according to the carriers hops along the trapping states. Under the same barrier height condition, the reduction of trap depth enhances opportunities for electron hopping, thereby significantly reducing the HRS current and leading to a high ON/OFF ratio of 10<sup>7</sup>. From the above results, initially, native defects of oxygen vacancies scatter in the SZT film. Injected electrons are trapped in the defects and affect the current conduction. Thus, the conduction mechanism in HRS is dominated by SCLC.

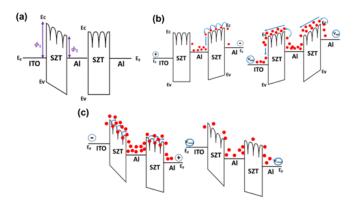

Figure 7a shows the Al/SZT/Al (18 nm)/SZT/ITO structure band diagram under zero bias. The valleys on the upper side of the SZT insulator represent the traps inside the SZT insulator. The left SZT insulator layer was leaned as the result of the different work functions between ITO and Al (ITO: 4.5 eV and Al: 4.2 eV). The Al layer embedded in the SZT thin film acted as a trap for electrons because the electron affinity of SZT was higher than the work function of Al. When the devices were under low negative bias, which was equivalent to the Al TE, a negative bias was applied, and the ITO bottom was under applied positive bias (Figure 7b). In the low applied-bias negative region, the transport in RRAM

devices was caused by thermally generated carriers [11]. When the carriers crossed over the first SZT insulator from the Al TE, they were trapped inside the embedded Al layer. When the applied negative voltage increased, the traps in the SZT insulator were almost filled, the carriers began to transport in the SZT insulator, and the concentration of carriers inside the SZT insulator increased. Meanwhile, the carriers trapped in the embedded Al layer also joined the transport. In this region, the current steeply increased, and the RRAM switched from HRS to LRS. By contrast, the switch of devices from LRS to HRS was also discussed. First, when the applied positive was small, the carriers were gradually released by the trap in the SZT insulator, that is, the detrapping process (Figure 7c). When the positive arrives at the  $V_{RESET}$ , the devices originally should switch from LRS to HRS. However, given the carriers trapped inside the embedded Al layer, the carrier concentration in the SZT insulator remained high, and the devices were maintained in the LRS state. During the applied positive sweeps from +4 V to the V<sub>RESET</sub> (about +1.28 V), the RRAM devices reached the detrapping situation. The carriers could not fill the trap, and the carrier concentration in the SZT insulator decreased, causing the devices to switch from the LRS to HRS. As a result, the embedded Al layer structures in RRAM devices caused a decrease in the HRS current and resulted in a high on/off ratio. Further, the embedded Al layer structures in RRAM devices caused a lag in the transport process, and we can discover the phenomenon in the I–V characteristic.

Figure 6. ln(J/E) as the function 1/T of the Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO structure.

**Figure 7.** Possible resistive switching mechanism of Al/SZT/Al (18 nm)/SZT/ITO devices. (**a**) Thermal equilibrium, (**b**) negative bias, and (**c**) positive bias.

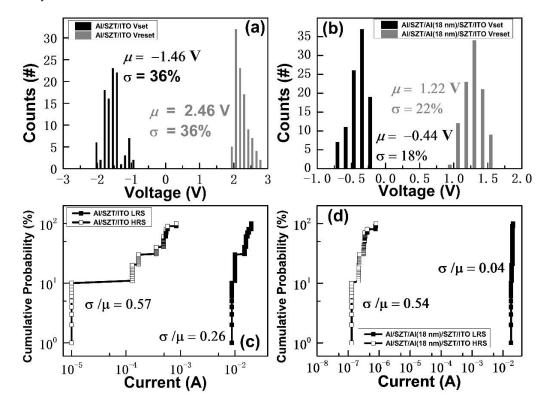

Figure 8 shows the reliability issues of Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO structures. The distribution of current and operation voltage was investigated. The  $V_{SET}$  and  $V_{RESET}$  distribution were plotted in a histogram to demonstrate the reliability of the

Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO RRAM (Figure 8a,b, respectively). In mathematics,  $\mu$  is the mean, and  $\sigma$  is the standard deviation [29]. As presented in Figure 8a, the V<sub>SET</sub> and V<sub>RESET</sub> were distributed widely. The average and standard deviation values of the V<sub>SET</sub> were –1.46 and 0.36, respectively. The average and standard deviation values of V<sub>RESET</sub> were 2.46 and 0.36 V, respectively. As shown in Figure 8b, when the devices switched between ON and OFF states, V<sub>SET</sub> was distributed in the range of –0.2 to –0.68 V, whereas V<sub>RESET</sub> was distributed in the range of 0.92 to 1.52 V. The average and standard deviation values of V<sub>RESET</sub> were –0.44 and 0.18 V, respectively. The average and standard deviation values of V<sub>RESET</sub> were 1.22 and 0.22 V, respectively. The reduction and more stable distribution of V<sub>SET</sub> and V<sub>RESET</sub> may be related to the addition of an 18 nm embedded Al layer [30].

**Figure 8.** Statistical and cumulative probability distribution of  $V_{SET}$  and  $V_{RESET}$  measured from (a) Al/SZT/ITO and (b) Al/SZT/Al (18 nm)/SZT/ITO devices unit during 100 time tests. The distribution of HRS/LRS resistance of (c) Al/SZT/ITO and (b) Al/SZT/Al (18 nm)/SZT/ITO devices unit for 100 time tests.

Figure 8c,d illustrates the cumulative probabilities of HRS/LRS resistance for the Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO device. Comparing the 18 nm embedded Al RRAM with the SZT-based RRAM, the coefficient declined from 0.26 to 0.04 at LRS and decreased by 0.03% at HRS, which reveals the 18 nm embedded Al RRAM depicted a large memory window and uniformity compared with SZT-based RRAM.

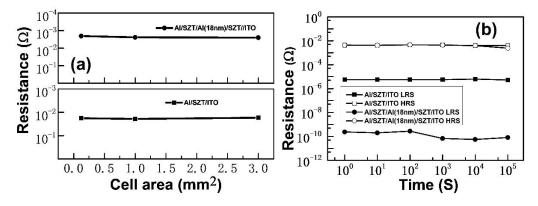

Figure 9a plots the scaling trend of the LRS resistance versus the cell area of the Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO structures. The LRS resistance is mainly a filamentary conduction current, and thus, it only had a slight dependence on the cell area. These results are similar to those for other metal oxides [31]. Figure 9b presents the retention capabilities of Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO structures measured at room temperature at a voltage of 0.5 V. The ON/OFF ratio of the Al/SZT/Al (18 nm)/SZT/ITO structure remained higher than 10<sup>6</sup>, and that for the Al/SZT/ITO structure was around 10<sup>3</sup>. For the Al/SZT/Al (18 nm)/SZT/ITO structure, the current magnitudes did not differ significantly over 10<sup>5</sup> s. The smooth roughness may facilitate

stable resistive switching [3], and the stability of the switching cycle and retention capability improved compared with those of the SZT memory device.

**Figure 9.** (**a**) LRS current with cell sizes ranging from 0.125 mm<sup>2</sup> to 3 mm<sup>2</sup> and (**b**) retention capability of Al/SZT/ITO and Al/SZT/Al (18 nm)/SZT/ITO structures.

From Table 1, the I–V switching characteristics of RRAM devices were promoted by inserting the Al embedded layer. Compared with the pure SZT-based RRAM devices and reported data [11–14], the resistance ratio increased from  $10^3$  to  $10^7$ , which is an ultrahigh memory margin, which led to distinguishing the storage information easily. The V<sub>SET</sub> decreased from -1.28 to -0.32 V, and the V<sub>RESET</sub> from 2.08 to 1.28 V. These results indicate that the operation voltage and current can be decreased to lower power consumption.

| <b>Table 1.</b> Performance comparison of the SZT-based RRAM devices with reported data. |

|------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------|

| Insulator<br>Material | Insert<br>Metal | Fabrication of the<br>Insulator | Fabrication of the<br>Insert Metal | Resistance<br>Ratio | Vest (V) | Vreset (V) | Current of<br>HRS (A) | Ref       |

|-----------------------|-----------------|---------------------------------|------------------------------------|---------------------|----------|------------|-----------------------|-----------|

| ZnO                   | Cu              | Sputter                         | Sputter                            | $10^{4}$            | 0.9      | -0.6       | $10^{-4}$             | [11]      |

| TiOx                  | Pt              | Thermal oxidation               | _                                  | $10^{5}$            | 3.7      | -0.9       | $10^{-8}$             | [12]      |

| HfO <sub>2</sub>      | Ti              | Sputter                         | Sputter                            | 50                  | 0.7      | -1.3       | $10^{-3}$             | [13]      |

| ZrO <sub>2</sub>      | Ti              | Electron-beam<br>evaporation    | Implant                            | 104                 | 1.3      | -0.66      | 10 <sup>-9</sup>      | [14]      |

| SZT                   | -               | Sol-gel                         | Sputter                            | 10 <sup>3</sup>     | -1.28    | 2.08       | $10^{-8}$             | This work |

| SZT                   | Al              | Sol-gel                         | Sputter                            | 107                 | -0.32    | 1.28       | $10^{-10}$            | This work |

#### 4. Conclusions

In conclusion, resistive switching behaviors in sol-gel SZT thin films have been probed, and the bipolar resistive switching characteristics of Al/SZT/ITO devices can utilize Al as an embedded layer in the SZT thin film for enhancing properties. Significant improvements in the ON/OFF ratios from  $10^3$  to over  $10^7$  were observed upon application to the Al/SZT/Al (18 nm)/SZT/ITO structure without the forming processes. A high interface trap density with a large amount of trapped electrons will help in building a favorable electric field to attract oxygen vacancies, and thus, the lower V<sub>SET</sub> and V<sub>RESET</sub> compared with those of the SZT memory device were obtained. The reduced trapping depths from 0.91 eV to 0.44 eV were found after the insertion of the Al layer, resulting in a low HRS current or high ON/OFF ratio. Therefore, the free-forming Al/SZT/Al (18 nm)/SZT/ITO structure with a high ON/OFF ratio of over  $10^7$ , excellent voltage distribution, and good retention of over  $10^5$  s can be achieved.

**Author Contributions:** K.-J.L. was responsible for the device preparation and characterization, data analysis, modeling discussion, and writing and editing of the manuscript. W.-S.L. was responsible for data analysis. L.-W.W. and H.-N.L. were responsible for the characterization and modeling discussion. Y.-H.W. monitored the progress and paper editing. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported in part by the Ministry of Science and Technology of Taiwan under grant MOST 108-2221-E-006-040-MY3. The authors would like to thank the Core Facility Center, Micro/Nano Technology Group, National Cheng-Kung University, Tainan, Taiwan, and Taiwan Semiconductor Research Institute, National Applied Research Laboratories, Taiwan for the support of high frequency and flicker noise measurements.

Institutional Review Board Statement: Not applicable.

**Informed Consent Statement:** Not applicable.

**Data Availability Statement:** The data presented in this study are available upon request from the corresponding author.

Acknowledgments: We appreciate the Core Facility Center, Micro/Nano Technology Group, National Cheng-Kung University, Tainan, Taiwan (device fabrication and characterization) and Taiwan Semiconductor Research Institute, National Applied Research Laboratories, Taiwan for their support including high frequency measurements.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Muhamad, N.F.; Osman, R.A.M.; Idris, M.S.; Yasin, M.N.M. Physical and electrical properties of SrTiO<sub>3</sub> and SrZrO<sub>3</sub>. *EPJ Web Conf.* **2017**, *162*, 01052. [CrossRef]

- 2. Muhamad, N.F.; Osman, R.A.M.; Idris, M.S.; Jamlos, F.; Hambali, N.A.M.A. Microwave and Electrical Properties of Zr-Doped SrTiO<sub>3</sub> for Dielectric Resonator Antenna Application. *Solid State Phenom.* **2018**, *280*, 142–148. [CrossRef]

- 3. Lee, K.-J.; Chang, Y.-C.; Lee, C.-J.; Wang, L.-W.; Chou, D.-W.; Chiang, T.-K.; Wang, Y.-H. Effects of Ni in Strontium Titanate Nickelate Thin Films for Flexible Nonvolatile Memory Applications. *IEEE Trans. Electron Devices* **2017**, *64*, 2001–2007. [CrossRef]

- 4. Chen, G.; Zhang, P.; Pan, L.; Qi, L.; Yu, F.; Gao, C. Flexible nonvolatile resistive memory devices based on SrTiO<sub>3</sub> nanosheets and polyvinylpyrrolidone composites. *J. Mater. Chem. C* 2017, *5*, 9799–9805. [CrossRef]

- 5. Padmini, E.; Ramachandran, K. Electrical properties of Mo-doped SrTiO<sub>3</sub> prepared by solid state reaction method. *Mater. Res. Express* **2019**, *6*, 115919. [CrossRef]

- 6. Zhang, W.; Wang, H.; Xu, J.; Liu, G.; Xie, H.; Yang, L. Effects of Mg Doping Concentration on Resistive Switching Behavior and Properties of SrTi<sub>1-v</sub>Mg<sub>y</sub>O<sub>3</sub> Films. *J. Wuhan Univ. Technol.-Mater. Sci. Ed.* **2019**, *34*, 888–892. [CrossRef]

- 7. Zhang, T.F.; Tang, X.G.; Liu, Q.X.; Jiang, Y.P. Electrode effect regulated resistance switching and selector characteristics in Nb doped SrTiO<sub>3</sub> single crystal for potential cross-point memory applications. *J. Alloys Compd.* **2018**, 730, 516–520. [CrossRef]

- 8. Bera, J.; Rout, S.K. SrTiO<sub>3</sub>–SrZrO<sub>3</sub> solid solution: Phase formation kinetics and mechanism through solid-oxide reaction. *Mater. Res. Bull.* **2005**, *40*, 1187–1193. [CrossRef]

- 9. Wei, C.Y.; Huang, W.C.; Yang, C.K.; Chang, Y.Y.; Wang, Y.H. Low-operating-voltage pentacene-based transistors and inverters with solution-processed barium zirconate titanate insulators. *IEEE Electron Device Lett.* **2011**, *32*, 1755–1757. [CrossRef]

- 10. Lee, K.-J.; Wang, Y.-H. Effect of Alkaline Earth Metal on AZrO<sub>x</sub> (A = Mg, Sr, Ba) Memory Application. Gels 2022, 8, 20. [CrossRef]

- 11. Yang, Y.C.; Pan, F.; Zeng, F.; Liu, M. Switching mechanism transition induced by annealing treatment in nonvolatile Cu/ZnO/Cu/ZnO/Pt resistive memory: From carrier trapping/detrapping to electrochemical metallization. *J. Appl. Phys.* 2009, 106, 123705-1–123705-5. [CrossRef]

- 12. Chung, Y.L.; Lai, Y.; Chen, Y.C.; Chen, J.S. Schottky barrier mediated single-polarity resistive switching in Pt layer-included TiOx memory device. *ACS Appl. Mater. Interfaces* **2011**, *3*, 1918–1924. [CrossRef] [PubMed]

- 13. Lee, D.; Sung, Y.; Lee, I.; Kim, J.; Sohn, H.; Ko, D.H. Enhanced bipolar resistive switching of HfO<sub>2</sub> with a Ti interlayer. *Appl. Phys. A* **2011**, *102*, 997–1001. [CrossRef]

- 14. Liu, Q.; Long, S.; Wang, W.; Zuo, Q.; Zhang, S.; Chen, J.; Liu, M. Improvement of resistive switching properties in ZrO<sub>2</sub>-based ReRAM with implanted Ti ions. *IEEE Electron Device Lett.* **2009**, *30*, 1335–1337. [CrossRef]

- Ruth, E.; McKnight, A.; Kennedy, B.J.; Zhou, Q.; Carpenter, M.A. Elastic anomalies associated with transformation sequences in perovskites: II. The strontium zirconate–titanate Sr (Zr, Ti)O<sub>3</sub> solid solution series. *J. Phys. Condens. Matter* 2008, 21, 015902. [CrossRef]

- 16. Dixit, D.; Agrawal, C.; Mohapatra, Y.N.; Majumder, S.B.; Katiyar, R.S. Studies on the dielectric and relaxor behavior of sol–gel derived barium strontium zirconate titanate thin films. *Mater. Lett.* **2007**, *61*, 3685–3688. [CrossRef]

- 17. Huang, S.; Lee, K.-J.; Wang, Y.-H. Magnesium Zirconate Titanate Thin Films Used as an NO<sub>2</sub> Sensing Layer for Gas Sensor Applications Developed Using a Sol–Gel Method. *Sensors* **2021**, *21*, 2825. [CrossRef] [PubMed]

- Avilés, M.A.; Córdoba, J.M.; Sayagués, M.J.; Gotor, F.J. Mechanochemical synthesis of Ti<sub>1-x</sub>Zr<sub>x</sub>B<sub>2</sub> and Ti<sub>1-x</sub>Hf<sub>x</sub>B<sub>2</sub> solid solutions. *J. Phys. Chem. B* 1998, 102, 5094–5098. [CrossRef]

- 19. Victor, S.B. Krupanidhi, Impact of microstructure on electrical characteristics of laser ablation grown ZrTiO<sub>4</sub> thin films on Si substrate. *J. Phys. D. Appl. Phys* **2005**, *38*, 41–50. [CrossRef]

- 20. Praveen, T.; Rose, T.P.; Saji, K.J. Top electrode dependent resistive switching in M/ZnO/ITO memristors, M = Al, ITO, Cu, and Au. *Microelectron. J.* **2022**, *121*, 105388. [CrossRef]

- Zhang, W.; Kong, Z.J.; Cao, Y.Z.; Li, D.A.; Wang, G.L.; Zhu, L.; Li, X.; Cao, Y.-Q.; Wu, D. Bipolar Resistive Switching Characteristics of HfO<sub>2</sub>/TiO<sub>2</sub>/HfO<sub>2</sub> Trilayer-Structure RRAM Devices on Pt and TiN-Coated Substrates Fabricated by Atomic Layer Deposition. *Nanoscale Res. Lett.* 2017, *12*, 393. [CrossRef] [PubMed]

- 22. Saleem, F.; Simanjuntak, M.; Chandrasekaran, S.; Rajasekaran, S.; Tseng, T.-Y.; Prodromakis, T. Transformation of digital to analog switching in TaO<sub>x</sub>-based memristor device for neuromorphic applications. *Appl. Phys. Lett.* **2021**, *118*, 112103. [CrossRef]

- 23. Lampert, M.A. Simplified Theory of Space-Charge-Limited Currents in an Insulator with Traps. *Phys. Rev. J. Arch.* **1956**, *103*, 1648. [CrossRef]

- 24. Chiu, F.C. A review on conduction mechanisms in dielectric films. Adv. Mater. Sci. Eng. 2014, 2014, 1–18. [CrossRef]

- 25. Wang, Z.S.; Zeng, F.; Yang, J.; Chen, C.; Yang, Y.C.; Pan, F. Reproducible and controllable organic resistive memory based on Al/poly(3,4-ethylene-dioxythiophene):poly(styrenesulfonate)/Al structure. *Appl. Phys. Lett.* **2010**, *97*, 253301. [CrossRef]

- 26. Yang, Y.C.; Pan, F.; Liu, Q.; Liu, M.; Zeng, F. Fully Room-Temperature-Fabricated Nonvolatile Resistive Memory for Ultrafast and High-Density Memory Application. *Nano Lett.* **2009**, *9*, 1636–1643. [CrossRef]

- Park, K.H.; Jung, J.H.; Li, F.; Son, D.I.; Kim, T.W. Carrier transport mechanisms of nonvolatile memory devices based on nanocomposites consisting of ZnO nanoparticles with polymethylmethacrylate nanocomposites sandwiched between two C60 layers. *Appl. Phys. Lett.* 2008, *93*, 132104. [CrossRef]

- 28. Sedghi, N.; Davey, W.; Mitrovic, I.Z.; Hall, S. Design and focused ion beam fabrication of single crystal diamond nanobeam cavities. *J. Vac. Sci. Technol.* **2011**, *B29*, 01AB10. [CrossRef]

- 29. Ryu, S.W.; Cho, S.; Park, J.; Kwac, J.; Kim, H.J.; Nishi, Y. Effects of ZrO<sub>2</sub> doping on HfO<sub>2</sub> resistive switching memory characteristics. *Appl. Phys. Lett.* **2014**, *105*, 072102. [CrossRef]

- Chen, L.; Dai, Y.W.; Sun, Q.Q.; Guo, J.J.; Zhou, P.; Zhang, D.W. Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> functional stack films based resistive switching memories with controlled SET and RESET voltages. *Solid State Ion.* 2015, 273, 66–69. [CrossRef]

- 31. Wong, H.S.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, S.; Lee, B.; Chen, F.T.; Tsai, M.J. Metal-oxide RRAM. *Proc. IEEE* 2012, 100, 1951–1970. [CrossRef]

## Article Comparative Study of Temperature Impact in Spin-Torque Switched Perpendicular and Easy-Cone MTJs

Jingwei Long <sup>1,†</sup>, Qi Hu <sup>2,†</sup>, Zhengping Yuan <sup>1,†</sup>, Yunsen Zhang <sup>2</sup>, Yue Xin <sup>1</sup>, Jie Ren <sup>1</sup>, Bowen Dong <sup>2</sup>, Gengfei Li <sup>2</sup>, Yumeng Yang <sup>1,3</sup>, Huihui Li <sup>2,\*</sup> and Zhifeng Zhu <sup>1,3,\*</sup>

- <sup>1</sup> School of Information Science and Technology, Shanghai Tech University, Shanghai 201210, China

- <sup>2</sup> Beijing Superstring Academy of Memory Technology, Beijing 100176, China

- <sup>3</sup> Shanghai Engineering Research Center of Energy Efficient and Custom AI IC, Shanghai 201210, China

- \* Correspondence: huihui.li@bjsamt.org.cn (H.L.); zhuzhf@shanghaitech.edu.cn (Z.Z.)

- + These authors contributed equally to this study.

**Abstract:** The writing performance of the easy-cone magnetic tunnel junction (MTJ) and perpendicularly magnetized MTJ (pMTJ) under various temperatures was investigated based on the macrospin model. When the temperature is changed from 273 K to 373 K, the switching current density of the pMTJ changes by 56%, whereas this value is only 8% in the easy-cone MTJ. Similarly, the temperature-induced variation of the switching delay is more significant in the pMTJ. This indicates that the easy-cone MTJ has a more stable writing performance under temperature variations, resulting in a wider operating temperature range. In addition, these two types of MTJs exhibit opposite temperature dependence in the current overdrive and write error rate. In the easy cone MTJ, these two performance metrics will reduce as temperature is increased. The results shown in this work demonstrate that the easy-cone MTJ is more suitable to work at high temperatures compared with the pMTJ. Our work provides a guidance for the design of STT-MRAM that is required to operate at high temperatures.

**Keywords:** spin-transfer torque; easy-cone magnetization; precession switching; current overdrive; write error rate

#### 1. Introduction

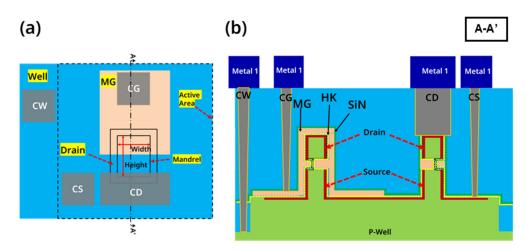

Spin-transfer torque magnetic random-access memory (STT-MRAM) with perpendicular magnetization is a promising and emerging technology. Benefiting from its nonvolatility, faster access speed compared with DRAM and higher capacity compared with SRAM, STT-MRAM has become a competitive candidate to replace SRAM and DRAM to realize the universal memory [1,2]. STT-MRAM consists of the transistor and magnetic tunnel junction (MTJ). As shown in Figure 1a, MTJ consists of a nonmagnetic spacer layer and two ferromagnetic layers. One of the ferromagnetic layers is magnetically pinned, named the pinned layer (PL). The magnetization of the other ferromagnetic layer can be changed by the external excitations. This layer is named the free layer (FL). Since the two magnetic layers have the same easy axis, their magnetization,  $m_{FL}$  and  $m_{PL}$ , can only be parallel or antiparallel. According to the tunneling magnetoresistance effect, the electrical resistance of MTJ is low (high) when  $m_{FL}$  and  $m_{PL}$  are parallel (antiparallel), which can be used to represent the binary states [3].

In the STT-MRAM, a current flowing through the device generates the STT (indicated by the blue arrows in Figure 1a), which can be used to switch the magnetization of the FL. The magnitude of STT is proportional to the relative angle between  $m_{FL}$  and  $m_{PL}$  ( $\theta$ ), given as  $\tau_{STT} m_{FL} \times (m_{FL} \times m_{PL})$ , where  $\tau_{STT}$  is the coefficient dependent on the physical parameters of MTJ [4]. Restricted to the collinear magnetization at equilibrium, the STT is vanished although the current is applied. In consequence, the STT-induced magnetization

11

switching relies on the thermal fluctuations that can break the collinearity of  $m_{FL}$  and  $m_{PL}$ . Nevertheless, since these fluctuations are random in nature, the switching time is greatly varied and cannot be controlled [5–7]. This stochasticity put forward stringent requirements for the design of the device to achieve an appropriate write error rate [8–10]. Some studies focused on the design of the device structure to increase the relative angle between  $m_{FL}$  and  $m_{PL}$ . For example, the PL with a tilted easy axis has been employed, but it brought difficulties to the epitaxial growth. Two spin polarizing layers with in-plane and out-of-plane magnetization are also considered. However, it is limited by the complex stacking structure [11–14].

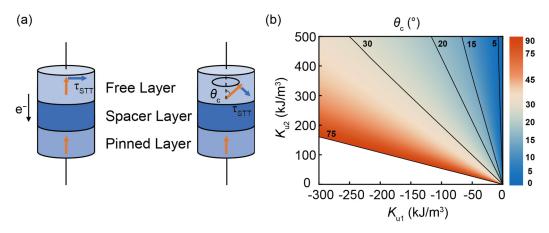

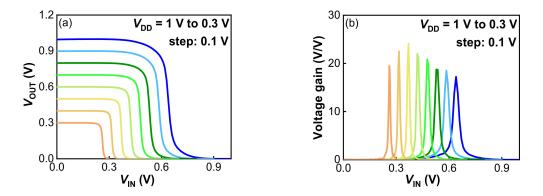

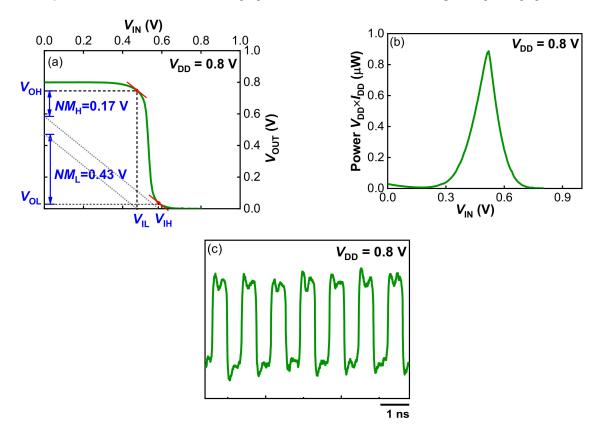

**Figure 1.** (a) Schematic of magnetic tunneling junctions with perpendicular and tilted magnetized FL. The orange arrows represent the magnetization of FL and PL. The blue arrows represent the spin transfer torque exerted on the magnetization.  $\theta_c$  is defined as the polar angle of easy-cone FL magnetization. (b)  $\theta_c$  as a function of K<sub>u1</sub> and K<sub>u2</sub>.

Some analytical and macrospin studies have revealed that the switching characteristics of MTJs can be improved by exploiting a conically magnetized FL [15-18], which can be realized by the second-order magnetic anisotropy. As shown in the right panel of Figure 1a, when the demagnetizing energy is partially or fully balanced by the first-order anisotropy energy, the second-order magnetic anisotropy leads to an easy cone state which has a fixed polar angle ( $\theta_c$ ) with respect to the out-of-plane direction [19–22]. This selfcontained misalignment brings advantages such as faster switching, lower switching current density, and better write error rate compared with the pMTJ. However, almost all studies that compare the easy-cone MTJ and pMTJ focus on the room temperature performance. Meanwhile, the temperature studies on the easy-cone MTJ only focus on how to stabilize the easy-cone magnetization under various temperatures or the temperature effect on the TMR ratio [15,19]. The temperature effect on the writing performance of the easy-cone MTJ has not been systematically investigated. It has been reported that there are many issues in the pMTJ as the temperature is varied. For example, at low temperatures, the reduced thermal fluctuations decrease the relative angle between  $m_{FL}$  and  $m_{PL}$ . The initial STT will thus be decreased and the incubation delay will be increased [23]. However, in the easy-cone MTJ, this angle is mainly determined by the magnetocrystalline anisotropy energy and demagnetizing energy. It will not be constrained by thermal fluctuations. At high temperatures, the thermal stability ( $\Delta$ ) of the pMTJ will be reduced a lot [24]. However, the existence of second-order anisotropy in the easy-cone MTJ increases the energy barrier between the equilibrium magnetization state and the in-plane magnetization state  $(E_B)$ , which compensates for the reduction in  $\Delta$ .  $\Delta$  is closely related to the writing performance of the MTJ. Therefore, it is believed that the writing performance of the easy-cone MTJ is more stable under temperature variations. This makes it more suitable to operate at extreme temperatures.

In this work, the width and length of FL is assumed to be 20 nm and 48 nm, respectively. Previous studies pointed out that the ferromagnets with a lateral size smaller than 80 nm

can be described by the macrospin model [25]. Thus, we use the macrospin model to simulate the dynamics of the device. Based on the temperature dependence of physical parameters, we show that the easy-cone MTJ has a larger  $\Delta$  at high temperatures due to the second-order anisotropy. Meanwhile,  $\Delta$  changes less significantly in the easy-cone MTJ as the temperature is varied. As a result, the writing performance of the easy-cone MTJ show a better immunity under temperature variations. In addition, our results show that the easy-cone MTJ exhibits a smaller switching current density and a lower write error rate at high temperatures. These results further confirm the remarkable potential of the easy-cone MTJ in memory applications. Meanwhile, our work can stimulate the design of high performance STT-MRAM operating at high temperatures.

#### 2. Methodology

In the easy-cone state, the tilted magnetization is stabilized by the competition of the magnetic anisotropy energy and demagnetization energy. Here, the former consists of both first- and second-order magnetic anisotropy energies. Thus, the energy density of easy-cone FL is given by:

$$\varepsilon = \frac{1}{2}\mu_0 M_{sat}^2 (N_{xx}m_x^2 + N_{yy}m_y^2 + N_{zz}m_z^2) + K_{u1}(1 - m_z^2) + K_{u2}(1 - m_z^2)^2$$

(1)

Here,  $N_{xx}$ ,  $N_{yy}$ , and  $N_{zz}$  represent demagnetization coefficients in the three dimensions.  $\mu_0$  is the vacuum permeability and  $M_{sat}$  is the saturation magnetization, which refers to the maximum magnetization that the ferromagnet can reach when it is magnetized by a magnetic field.  $K_{u1}$  and  $K_{u2}$  are the first- and second-order magnetic anisotropy constants, respectively. The demagnetization energy will generate an in-plane shape anisotropy field,  $\mathbf{H}_{IP}$ , with the magnitude of  $M_{sat}$  ( $N_{zz}$ - $N_{xx}$ ) [26]. Thus, the energy density of FL can be rewritten as:

$$\varepsilon = K_{u1,eff} \left( 1 - m_z^2 \right) + K_{u2} \left( 1 - m_z^2 \right)^2$$

(2)

where  $K_{u1,eff}$  is the effective first-order anisotropy constant with demagnetization energy considered, given by  $K_{u1,eff} = K_{u1} - (1/2)\mu_0 M_{sat}^2 (N_{zz} - N_{xx})$ . Figure 1b reveals that the competition of  $K_{u1,eff}$  and  $K_{u2}$  determines the  $\theta_c$ . When  $K_{u1,eff} < 0$  and  $-K_{u2}/K_{u1,eff} > 1/2$  (indicated by the shaded region), the easy-cone state can be stabilized. By minimizing the energy density of the FL, the equilibrium polar angle can be expressed as:

$$\theta_c = \sin^{-1} \sqrt{\frac{-K_{u1,eff}}{2K_{u2}}} \tag{3}$$

For practical applications,  $\theta_c$  is often required to be smaller than 15° to ensure an appropriate  $\Delta$ .

In this study, the temperature dependence of physical parameters is included. Here, we mainly consider the dependence of  $M_{sat}$ ,  $K_{u1}$ , and the spin polarization factor P on temperature. They can be modeled by following formulas [27–29]:

$$M_{sat}(T) = M_{sat}(0)[1 - (\frac{T}{T_c})^{3/2}]$$

(4)

$$K_{u1}(T) = K(0) \left[\frac{M_{sat}(T)}{M_{sat}(0)}\right]^3$$

(5)

$$P(T) = P(0) \left( 1 - \beta T^{\frac{3}{2}} \right)$$

(6)

where *T* is the temperature, and  $\beta = 2 \times 10^{-5} \text{ K}^{-3/2}$  is the fitting parameters dependent on materials.  $T_c = 750 \text{ K}$  is the Curie temperature.  $M_{sat}(0)$ ,  $K_{u1}(0)$ , and P(0) are the values at T = 0 K. Their values are given in Table 1 so that the corresponding values at T = 300 Kare consistent with those reported in [30]. The pMTJ and easy-cone MTJ studied in this work differ only in magnetic anisotropy energy. That is,  $M_{sat}(0)$  and P(0) of both devices are the same but the  $K_{u1}(0)$  is different. As for  $K_{u2}$ , previous studies pointed out that the significant  $K_{u2}$  does not intrinsically originate from the ferromagnetic interfaces. The spatial fluctuations of film thickness and atomic structure at the interface should be responsible for its emergence [31–33]. Therefore, we exclude the temperature dependence of  $K_{u2}$  in this study. As illustrated in Figure 2a–c, all these three parameters decrease as *T* is increased. The same monotonicity of  $M_{sat}$  and  $K_{u1}$  makes it difficult to directly derive the changes of  $\Delta$  as the temperature is varied, and we resort to the numerical calculation. The  $\Delta$  of the easy-cone state is given by [14]:

$$\Delta = \frac{E_B}{k_B T} = \frac{\left(\varepsilon \left(\theta = \frac{\pi}{2}\right) - \varepsilon \left(\theta = \theta_c\right)\right) V}{k_B T}$$

(7)

| Parameter                         | Unit                                 | Value             |

|-----------------------------------|--------------------------------------|-------------------|

| <i>P</i> (0)                      | ~                                    | 0.446             |

| $K_{u1}(0)$ for the pMTJ          | $J/m^3$                              | $1.82 	imes 10^6$ |

| $K_{u1}(0)$ for the easy-cone MTJ | J/m <sup>3</sup><br>J/m <sup>3</sup> | $1.1	imes10^6$    |

| $M_{\rm sat}(0)$                  | A/m                                  | $1.22	imes10^{6}$ |

| $t_{\rm FL}$                      | nm                                   | 1.2               |

| $l_{\rm FL}$                      | nm                                   | 48                |

| $w_{ m FL}$                       | nm                                   | 20                |

Table 1. Parameters of the system.

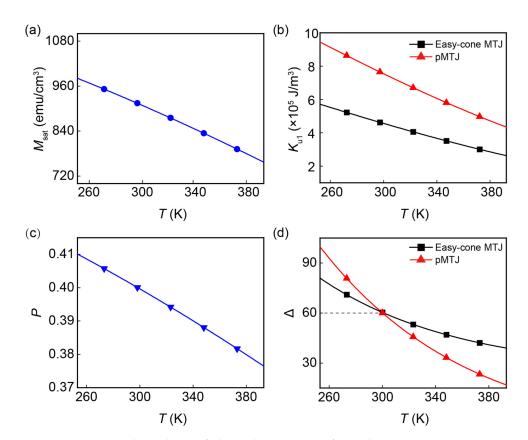

**Figure 2.** Temperature dependence of physical parameters of MTJ device: (**a**) saturation magnetization  $M_{sat}$ , (**b**) first order anisotropy constant  $K_{u1}$ , (**c**) spin polarization factor *P*, and (**d**) thermal stability  $\Delta$ . Both devices have  $\Delta = 60$  at room temperature.

Here, *V* is the volume of FL and  $k_B$  is the Boltzmann constant. Figure 2d shows  $\Delta$  as a function of *T* for the pMTJ and easy-cone MTJ. It is important to note that we set  $\Delta$  = 60 at

room temperature (T = 300 K) in both devices for a fair comparison between them. It can be observed that the pMTJ has a higher  $\Delta$  before the intersection point due to the larger  $K_{u1}(0)$ . However, it becomes more thermally unstable than the easy-cone MTJ when T is increased. We attribute this to the presence of  $K_{u2}$  in the easy-cone MTJ and the faster decreasing  $K_{u1}$  in the pMTJ. As T is increased, the invariant  $K_{u2}$  in the easy-cone MTJ can produce a stable  $E_B$  to slow down the degradation of  $\Delta$ . In contrast, the rapidly decreased  $K_{u1}$  in the pMTJ leads to a sharply reduced  $E_B$ . Thus, under high-temperature circumstance, easy-cone MTJ has a superior  $\Delta$ . This indicates that the easy-cone MTJs have a better performance in the data retention when they are operating at elevated temperatures.

The current driven magnetization dynamics is studied by solving the Landau–Lifshitz–Gilbert–Slonczewski (LLGS) equation  $d\mathbf{m}/dt = -\gamma \mathbf{m} \times \mathbf{H}_{eff} + \alpha \mathbf{m} \times d\mathbf{m}/dt - \gamma \eta \hbar J/(2 et_{FL}M_{sat})\mathbf{m} \times (\mathbf{m} \times \sigma_{STT})$  [34] with the gyromagnetic  $\gamma$ , the current density *J*, the reduced Planck constant  $\hbar$ , the electron charge *e*, the thickness of FL,  $t_{FL} = 1.2$  nm, the damping constant,  $\alpha = 0.01$ , the spin polarization,  $\sigma_{STT}$ , and the effective magnetic field,  $\mathbf{H}_{eff}$ , which includes the first- and second-order magnetic anisotropy field, the demagnetizing field, and the thermal field. The STT efficiency  $\eta = P/[1 + P^2\cos(\theta)]$  is determined by the spin polarization factor and polar angle of FL magnetization.

#### 3. Results and Discussion

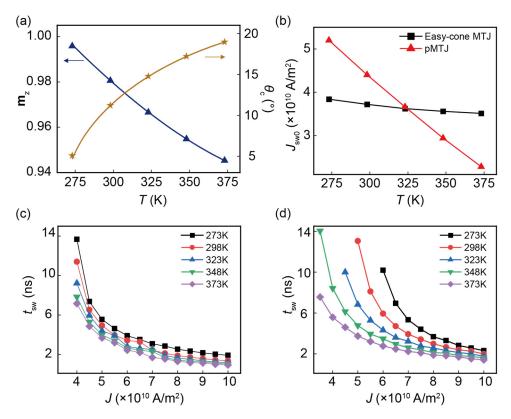

To study the temperature effect, we consider the standard operating temperature range of commercial electronic devices, from 273 K to 343 K. To further verify the superiority of the easy-cone MTJ at higher temperatures, we also perform the simulations at the temperature range of 343–373 K. The results show that the easy-cone MTJ is still superior. Therefore, it can be predicted that the advantages of the easy-cone MTJ will become even more apparent above 373 K. When the temperature is smaller than 273 K, it is hard to obtain the easy-cone state since the first-order anisotropy constant is so large that the anisotropy energy cannot be compensated by the demagnetizing energy. Finally, we determined the temperature region 273–373 K. We consider that the temperature affects the writing performance in two ways. One is the temperature dependence of physical parameters, which dominates the variations of the device performance. The other is the influence of the temperaturedependent H<sub>thermal</sub>, which arises from the thermal fluctuations. To investigate the intrinsic writing performance, we firstly exclude the  $\mathbf{H}_{ ext{thermal}}$ . To determine the equilibrium state for the easy-cone MTJ,  $\theta_c$  at various temperatures is calculated using Equation (3), which is shown in Figure 3a. Meanwhile, we determine the  $\theta_c$  at T = 273 K to T = 373 K using the numerical simulation. The results of the calculation and simulation fit well. It can be seen that the misalignment between the FL and PL will become more pronounced at a higher T. The maximum  $\theta_c$  in our simulation reaches 19° at T = 373 K. It has been demonstrated that a larger  $\theta_c$  will lead to lower intrinsic switching current density ( $J_{sw0}$ ) and switching delay ( $t_{sw}$ ).  $J_{sw0}$  is defined as the critical current density above which STT can overcome the damping and magnetization switching will be initialized. A small  $J_{sw0}$  should be promised to ensure a low-power consumption. For the easy-cone MTJ and pMTJ,  $J_{sw0}$  is given by Equations (8) and (9), respectively [14,35].

$$J_{\rm sw0,easy-cone} = \frac{8}{3\sqrt{6}} \frac{\alpha t_{FL}|e|}{\hbar P} \sqrt{\frac{(K_{u1,eff} + 2K_{u2})^3}{K_{u2}}}$$

(8)

$$J_{\rm sw0,PMA} = \frac{4\alpha t_{FL}|e|}{\hbar P} K_{u1,eff}$$

(9)

As depicted in Figure 3b,  $J_{sw0}$  of the easy-cone MTJ and pMTJ will drop as *T* is increased. In our study, the spin polarization *P* and  $K_{u1,eff}$  determine  $J_{sw0}$  when *T* varies. The reduced  $K_{u1,eff}$  at high temperatures leads to a lower  $\Delta$ , and consequently a smaller current density is able to realize magnetization switching. In contrast, the reduced *P* results in a weaker STT, which calls for additional current density to switch the magnetization [36–38]. Note that  $K_{u1,eff}$  is more sensitive to temperatures, it is the dominated parameter in the

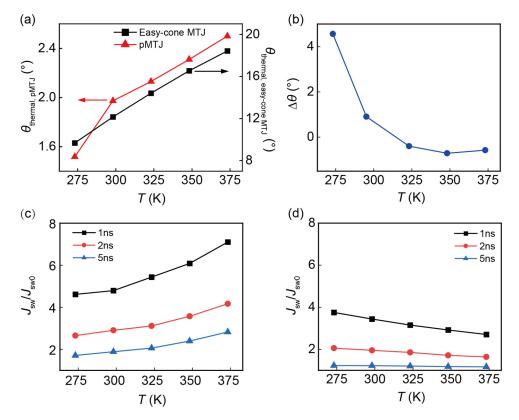

variation of  $J_{sw0}$ . Thus, the  $J_{sw0}$  curves of both easy-cone MTJ and pMTJ show a downward trend. It is worth noting that the decrease in  $J_{sw0}$  in pMTJ is steep, while that of the easy-cone MTJ shows a much gradual trend. This is because the variation of  $K_{u1,eff}$  in the pMTJ is more significant. Therefore, compared with the easy-cone MTJ, the pMTJ has a much lower  $J_{sw0}$  when *T* is higher than 323 K. However, this is at the cost of its stability under temperature variation. For example, in the range of 273 K to 373 K,  $J_{sw0}$  of the pMTJ changes by 56%. This value in the easy-cone MTJ is only 8%. In practical applications, this stability is very attractive since it can promise a wider operating temperature range.

**Figure 3.** (a) The equilibrium  $\mathbf{m}_z$  and initial polar angle  $\theta_c$  as a function of temperature. (b) Temperature dependence of the intrinsic switching current density  $J_{sw0}$  in the easy-cone MTJ and pMTJ. Switching delay  $t_{sw}$  as a function of current density in the (c) easy-cone MTJ and (d) pMTJ. T = 273 K, 298 K, 323 K, 348 K, and 373 K are represented by square, circle, triangle, down-pointing triangle, and rhombus, respectively.

Next, we examined the switching delay  $t_{sw}$ , which characterizes the writing speed of STT-MRAM. Here,  $t_{sw}$  is defined as the required time for the magnetic moment switching from  $\theta = \theta_c$  to  $\theta = 90^\circ$ . As illustrated in Figure 3c,d,  $t_{sw}$  of both MTJs decreases as *T* is increased. This stems from the reduced  $M_{sat}$  at a high *T*, which can enhance the STT. In particular, for the easy-cone MTJ, the initial  $\theta_c$  becomes larger with increasing *T*, resulting in a larger STT [17]. Such an increase in STT has been confirmed to accelerate the magnetic switching [14]. It is observed that the same as  $J_{sw0}$ , for the easy-cone MTJ, the variation of  $t_{sw}$  as a function of temperatures is less significant compared with that in the pMTJ. This is more pronounced at moderate current densities  $6 \times 10^{10}$  to  $8 \times 10^{10}$  A/m<sup>2</sup>.

At finite temperatures, the thermal fluctuations cannot be ignored, which leads to a stochastic switching. The thermal fluctuations are included as an effective random field:

$$\mathbf{H}_{thermal} = \zeta \sqrt{\frac{2k_B T \alpha}{V M_{sat} (1 + \alpha^2) \delta t}}$$

(10)

where  $\zeta$  is a vector with three components that are independent Gaussian random variables, and the time-step  $\delta t$  is 10 ps in our simulation. We then investigate the writing performance of both types of MTJs with pulse duration  $\tau = 1$  ns, 2 ns, and 5 ns. When  $\tau < 5$  ns, the switching in the conventional pMTJ is in the fast precession regime, where a large current is required for the successful switching [5,6]. As a result, the torque from thermal fluctuations plays a negligible role in the magnetization switching. However, it is important to note that the thermal fluctuations also affect the distribution of initial magnetization, which has a strong impact in the switching current density. Therefore, before studying the switching dynamics, one has to determine  $\theta$  by taking the thermal fluctuations into account. To capture the thermal distribution of the magnetization, we have solved the LLGS equation with the effective thermal field described by Equation (10). Figure 4a shows the mean of  $\theta$  with thermal fluctuations considered ( $\theta_{\text{thermal}}$ ) as a function of temperatures for the easy-cone MTJ and pMTJ. It can be observed that raising T helps achieve a higher  $\theta_{\text{thermal}}$ for both devices, leading to easier spin transfer switching. In addition,  $\theta_{\text{thermal}}$  of the easy-cone MTJ changes more violently with T. However, thermal fluctuations play different roles in the variations of  $\theta_{\text{thermal}}$  in the two devices. In the pMTJ, a larger *T* results in an intense thermal fluctuation, and further enhances the precession of the FL magnetization. Therefore,  $\theta_{\text{thermal}}$  will increase accordingly. In contrast, for the easy-cone MTJ, the variation of  $\theta_{\text{thermal}}$  mainly arose from the temperature dependence of the physical parameters. As illustrated in Figure 4b, at high temperatures (T > 298 K), the difference between  $\theta_{\text{thermal}}$ and  $\theta_c$ , defined as  $\Delta \theta$ , is within 1°. However, at low temperature *T* = 273 K,  $\theta_{\text{thermal}}$  was enlarged a lot with respect to the intrinsic  $\theta_c$ . This is because the effective anisotropy field in the easy-cone MTJ is decreased at low temperatures, which becomes comparable to  $\mathbf{H}_{\text{thermal}}$ . Three components of the magnetization tend to have the same statistical value under the influence of  $\mathbf{H}_{\text{thermal}}$ . Thus, thermal fluctuations can help achieve a higher  $\theta_{\text{thermal}}$ .

**Figure 4.** (a)  $\theta_{\text{thermal}}$  as a function of temperature for the easy-cone MTJ and pMTJ. (b) The difference between  $\theta_c$  and  $\theta_{\text{thermal}}$  is represented as  $\Delta \theta$ . The current overdrive as a function of temperature in (c) pMTJ and (d) easy-cone MTJ.

In the fast precession regime, the required current density for the magnetization switching is several times of  $J_{sw0}$ . We define  $J_{sw}$  as the current density, at which the switching probability is 50% and investigate how the current overdrive  $J_{sw0}$  is affected when T is varied. The theoretical expression of the overdrive is  $1 + [\ln(\pi/2\theta)/J_{sw0}\tau]$ , which is determined by the combined effect of  $\theta$  and  $J_{sw0}$  [5]. With increased T, benefiting from the stronger thermal fluctuations and reduced  $K_{u1.eff}$ ,  $\theta$  will be enlarged, leading to a smaller overdrive. However, this will be compensated by the reduced  $J_{sw0}$  at higher T (see Figure 3b). It can be observed in Figure 4c,d that the overdrive of the two devices has an opposite temperature dependence. For the pMTJ, it shows an upward tendency as T is increased, while that of the easy-cone MTJ decreases at elevated T. This is attributed to the larger variations of  $J_{sw0}$  compared with the change of  $\theta$  in the pMTJ. Therefore,  $J_{sw0}$ dominates the variations of the overdrive. However, for the easy-cone MTJ, since  $J_{sw0}$ barely changes as T is varied,  $\theta$  dominates the variations of the current overdrive. As mentioned above,  $\theta$  will be enlarged at higher *T*. Therefore, the overdrive will decrease as *T* is raised. In both devices, the variations of the overdrive mainly arise from the temperature dependence of the physical parameters. In contrast, the thermal fluctuations are less important in the fast precession regime. However, when  $\tau$  is 5 ns, the overdrive of the easycone MTJ is almost unchanged as T is varied. It is confirmed that the easy-cone MTJ enters dynamic reversal regime, which is a transitory stage of the fast precession and thermally activated regimes. In this regime, restricted to the short  $\tau$ , the reduction in overdrive is more gradual. Only when  $\tau$  is further increased, and the magnetization switching enters thermally activated regime, the overdrive can be further decreased and becomes less than 1 [39]. In conclusion, in the precession regime, the easy-cone MTJ requires lower current density to realize switching than the pMTJ at high temperatures.

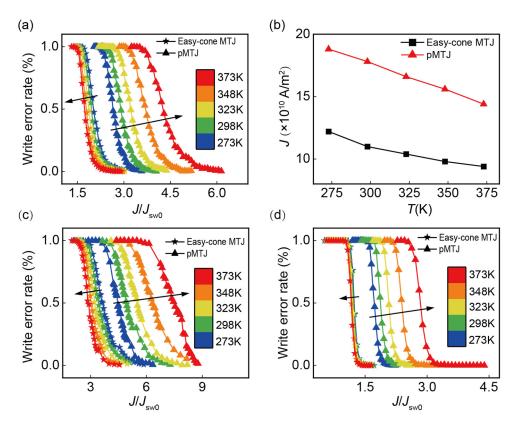

The write error rate is the probability of non-switching cases with current applied. In order to ensure the data writing function, the write error rate should be low enough. Figure 5 shows the write error rate as a function of the current density J normalized by  $J_{

m sw0}$  at different au. An opposite temperature dependence of WER can be observed for the pMTJ and easy-cone MTJ. For the pMTJ, it requires a larger  $J/J_{sw0}$  to ensure an appropriate write error rate as T is raised, resulting in the right shift of the write error rate curves. In contrast, for the easy-cone MTJ, the  $J/J_{sw0}$  required to achieve the same write error rate becomes smaller at elevated T. For instance, in Figure 5a, the pulse duration is 2 ns and both types of MTJs work in the precession regime. To realize a write error rate of  $10^{-3}$ in the easy-cone MTJ, the required  $J/J_{sw0}$  is 2.67 at T = 373 K, and this value is increased to 3.18 at a lower T = 273 K. However, in the pMTJ, the corresponding  $J/J_{sw0}$  is 6.31 at T = 373 K and decreased to 3.62 at T = 273 K. It can be observed in Figure 5b that when T changes from 273 K to 373 K, the required J for a write error rate of  $10^{-3}$  at  $\tau = 2$  ns will decrease by 22.9% and 23.4% in the easy-cone and pMTJ, respectively. However, as shown in Figure 3b, the  $J_{sw0}$  of the pMTJ changes by 56% and this value in the easy-cone MTJ is only 8%. This indicates that although  $J_{sw0}$  of the pMTJ has been reduced a lot at elevated T, the required *J* for an appropriate write error rate cannot benefit from it. In contrast, *J* in the easy-cone MTJ becomes much smaller when T is increased. This demonstrates that the easy-cone MTJ exhibits a better performance at high temperatures. In addition, it can be observed that the slope of the write error rate curves in both devices is almost unchanged as T is varied. This is attributed to the opposite impact of  $M_{sat}$  and P on the write error rate slope. When T is raised, both  $M_{sat}$  and P are reduced, and it has been shown that a smaller  $M_{\rm sat}$  leads to a larger slope, whereas a reduced P makes the curve more gradual [40]. Since the slope of write error rate curve remains the same, the effect of different T is manifested in the shift of the curves, which is much larger in the pMTJ due to the large variations of  $J/J_{sw0}$  required for a specific write error rate. In contrast, there is negligible shifts in the easy-cone MTJ, which is beneficial when the device is required to work stably in a wide temperature range.

**Figure 5.** (a) Write error rate as a function of current density (normalized by  $J_{sw0}$ ) with pulse duration  $\tau = 2$  ns. The easy-cone MTJ and pMTJ are represented by star and triangle, respectively. The arrow indicates the direction of increased temperature. (b) The required current density for the write error rate of  $10^{-3}$  at  $\tau = 2$  ns. Write error rate as a function of current density (normalized by  $J_{sw0}$ ) with pulse duration  $\tau$  of (c) 1 ns and (d) 5 ns.

#### 4. Conclusions

In conclusion, we used the macrospin model to investigate the temperature dependence of the writing performance of the easy-cone MTJ and pMTJ. Consistent with the previous studies, at the same temperature, easy-one MTJ has a better writing performance [13,17,24]. In addition, the investigation of the temperature effect revealed that the writing performance of the easy-cone MTJ varies little under temperature variations, leading to its superiority in operating at high temperatures. We first examined the intrinsic switching current density and switching delay.  $J_{sw0}$  and  $t_{sw}$  of both devices were decreased at high temperatures, and for the pMTJ, they fell even faster. With the effective thermal field introduced, we then performed the stochastic simulations. In the fast precession regime, the easy-cone MTJ and pMTJ had an opposite temperature dependence in the current overdrive  $J_{sw}/J_{sw0}$ . At higher temperatures, easy-cone MTJ had a smaller  $J_{sw}/J_{sw0}$ . Meanwhile, the write error rate curve shifted in opposite directions with increased temperatures for the two devices. It was also demonstrated that the required current density for an appropriate write error rate is smaller in the easy-cone MTJ. Our work reveals the potential of the easy-cone MTJ-based STT-MRAM in commercial electronic devices. Benefiting from its outstanding performance at high temperatures, the easy-cone MTJ is also fully capable of working in the automotive IC.

Author Contributions: Conceptualization, J.L., Y.Z., and Z.Z.; methodology, J.L., Q.H., Z.Z. and Z.Y.; software, J.L., J.R., Y.X. and Z.Z.; validation, J.L., Z.Y., Q.H., H.L., B.D. and G.L.; formal analysis, J.L., Q.H. and Z.Z.; investigation, J.L. and Z.Y.; resources Z.Z. and Y.Z.; writing—original draft preparation, J.L.; writing—review and editing, J.L., Y.Z., Q.H., Y.Y., Z.Y. and Z.Z. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the National Key R & D Program of China (Grant No. 2022YFB4401700), Shanghai Sailing Program (Grant No. 20YF1430400), and National Natural Science Foundation of China (Grants No. 12104301, 62104130).

Data Availability Statement: Data is available at the correspondence author.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Fong, X.; Kim, Y.; Venkatesan, R.; Choday, S.H.; Raghunathan, A.; Roy, K.J. Spin-transfer torque memories: Devices, circuits, and systems. *Proc. IEEE* 2016, *104*, 1449–1488. [CrossRef]

- 2. Ando, K.; Fujita, S.; Ito, J.; Yuasa, S.; Suzuki, Y.; Nakatani, Y.; Miyazaki, T.; Yoda, H.J. Spin-transfer torque magnetoresistive random-access memory technologies for normally off computing. *J. Appl. Phys.* **2014**, *115*, 172607. [CrossRef]

- 3. Julliere, M. Tunneling between ferromagnetic films. *Phys. Lett. A* **1975**, *54*, 225–226. [CrossRef]

- 4. Slonczewskim, J.C. Current-driven excitation of magnetic multilayers. J. Magn. Magn. Mater. **1996**, 159, L1–L7. [CrossRef]

- 5. Bedau, D.; Liu, H.; Sun, J.; Katine, J.; Fullerton, E.; Mangin, S.; Kent. Spin-transfer pulse switching: From the dynamic to the thermally activated regime. *Appl. Phys. Lett.* **2010**, *97*, 262502. [CrossRef]

- 6. Huai, Y. Spin-transfer torque MRAM (STT-MRAM): Challenges and prospects. AAPPS Bull. 2008, 18, 33–40.

- 7. Joshi, V.K.; Barla, P.; Bhat, S.; Kaushik, B.K. From MTJ device to hybrid CMOS/MTJ circuits: A review. *IEEE Access* 2020, *8*, 194105–194146. [CrossRef]

- Shiota, Y.; Nozaki, T.; Tamaru, S.; Yakushiji, K.; Kubota, H.; Fukushima, A.; Yuasa, S.; Suzuki, Y. Evaluation of write error rate for voltage-driven dynamic magnetization switching in magnetic tunnel junctions with perpendicular magnetization. *Appl. Phys. Express* 2015, 9, 013001. [CrossRef]

- Shiota, Y.; Nozaki, T.; Tamaru, S.; Yakushiji, K.; Kubota, H.; Fukushima, A.; Yuasa, S.; Suzuki, Y.J. Reduction in write error rate of voltage-driven dynamic magnetization switching by improving thermal stability factor. *Appl. Phys. Lett.* 2017, 111, 022408. [CrossRef]

- 10. Yamamoto, T.; Nozaki, T.; Imamura, H.; Shiota, Y.; Tamaru, S.; Yakushiji, K.; Kubota, H.; Fukushima, A.; Suzuki, Y.; Yuasa, S. Improvement of write error rate in voltage-driven magnetization switching. *J. Phys. D Appl. Phys.* **2019**, *52*, 164001. [CrossRef]

- 11. Zhu, X.; Zhu, J.-G. Spin torque and field-driven perpendicular MRAM designs scalable to multi-Gb/chip capacity. *IEEE. Trans. Magn.* **2006**, *42*, 2739–2741. [CrossRef]

- 12. Zha, C.; Persson, J.; Bonetti, S.; Fang, Y.; Åkerman, J. Pseudo spin valves based on L10 (111)-oriented FePt fixed layers with tilted anisotropy. *Appl. Phys. Lett.* **2009**, *94*, 163108. [CrossRef]

- 13. He, P.-B.; Li, Z.-D.; Pan, A.-L.; Wan, Q.; Zhang, Q.-L.; Wang, R.-X.; Wang, Y.-G.; Liu, W.-M.; Zou, B.-S. Theory of ferromagnetic resonance in magnetic trilayers with a tilted spin polarizer. *Phys. Rev. B* **2008**, *78*, 054420. [CrossRef]

- 14. Matsumoto, R.; Arai, H.; Yuasa, S.; Imamura, H. Spin-transfer-torque switching in a spin-valve nanopillar with a conically magnetized free layer. *Appl. Phys. Express* 2015, *8*, 063007. [CrossRef]

- 15. Timopheev, A.; Teixeira, B.; Sousa, R.; Aufret, S.; Nguyen, T.; Buda-Prejbeanu, L.; Chshiev, M.; Sobolev, N.; Dieny, B. Inhomogeneous free layer in perpendicular magnetic tunnel junctions and its impact on the effective anisotropies and spin transfer torque switching efficiency. *Phys. Rev. B* 2017, *96*, 014412. [CrossRef]

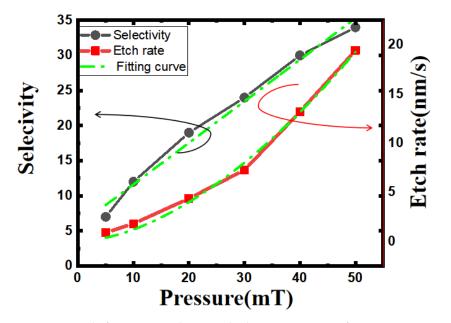

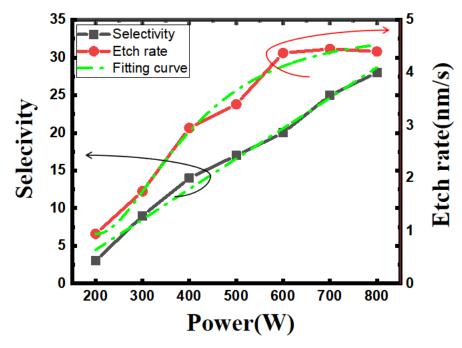

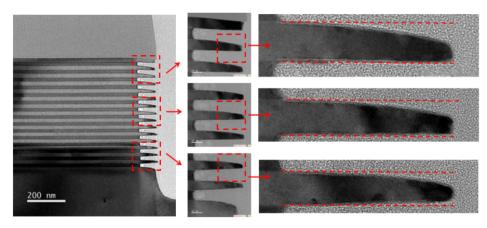

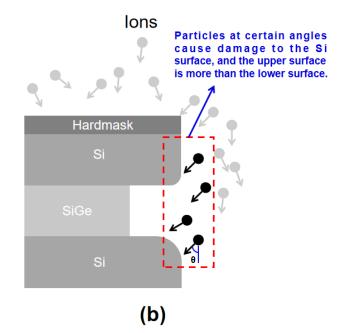

- 16. Matsumoto, R.; Arai, H.; Yuasa, S.; Imamura, H. Theoretical analysis of thermally activated spin-transfer-torque switching in a conically magnetized nanomagnet. *Phys. Rev. B* 2015, *92*, 140409. [CrossRef]