Special Issue Reprint

# Advanced Control Techniques for Power Converter and Drives

Edited by Daniele Scirè and Gianpaolo Vitale

mdpi.com/journal/electronics

# **Advanced Control Techniques for Power Converter and Drives**

# **Advanced Control Techniques for Power Converter and Drives**

**Guest Editors**

Daniele Scirè Gianpaolo Vitale

**Guest Editors**

Daniele Scirè Gianpaolo Vitale

Department of Engineering Institute for High

University of Palermo Performance Computing and

Palermo Networking

Italy National Research Council

Palermo Italy

Editorial Office MDPI AG Grosspeteranlage 5 4052 Basel, Switzerland

This is a reprint of the Special Issue, published open access by the journal *Electronics* (ISSN 2079-9292), freely accessible at: https://www.mdpi.com/journal/electronics/special\_issues/P26FR87AS2.

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

Lastname, A.A.; Lastname, B.B. Article Title. Journal Name Year, Volume Number, Page Range.

ISBN 978-3-7258-5381-6 (Hbk)

ISBN 978-3-7258-5382-3 (PDF)

https://doi.org/10.3390/books978-3-7258-5382-3

© 2025 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license. The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) license (https://creativecommons.org/licenses/by-nc-nd/4.0/).

## **Contents**

| About the Editors                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------|

| Preface                                                                                                                     |

| Daniele Scirè and Gianpaolo Vitale                                                                                          |

| Advanced Control Techniques for Power Converter and Drives                                                                  |

| Reprinted from: Electronics 2025, 14, 3710, https://doi.org/10.3390/electronics14183710                                     |

| Jun-Hyuk Han and IL-Song Kim                                                                                                |

| Double-Loop Controller Design of a Single-Phase 3-Level Power Factor Correction Converter                                   |

| Reprinted from: Electronics 2024, 13, 2863, https://doi.org/10.3390/electronics13142863 5                                   |

| Fadi Alyoussef, Ibrahim Kaya and Ahmad Akrad                                                                                |

| Robust PI-PD Controller Design: Industrial Simulation Case Studies and a Real-Time Application                              |

| Reprinted from: Electronics <b>2024</b> , 13, 3362, https://doi.org/10.3390/electronics13173362 <b>19</b>                   |

| David Carmona Vicente, Alba Muñoz Carrero, Eduardo Galván Díez, Juan Manuel Carrasco<br>Solís and Francisco Rodríguez Rubio |

| Advanced Distributed Control of Parallel Resonant CLLC DAB Converters                                                       |

| Reprinted from: Electronics 2025, 14, 318, https://doi.org/10.3390/electronics14020318 37                                   |

| Alessandro Ravera, Alberto Oliveri, Matteo Lodi and Marco Storace                                                           |

| FPGA Implementation of Nonlinear Model Predictive Control for a Boost Converter with a                                      |

| Partially Saturating Inductor                                                                                               |

| Reprinted from: Electronics 2025, 14, 941, https://doi.org/10.3390/electronics14050941 58                                   |

| Xin Gu, Kunyang Wu, Xuefeng Jin, Guozheng Zhang, Wei Chen and Chen Li                                                       |

| Dual-Random Space Vector Pulse Width Modulation Strategy Based on Optimized Beta                                            |

| Distribution                                                                                                                |

| Reprinted from: Electronics 2025, 14, 1779, https://doi.org/10.3390/electronics14091779 77                                  |

| Changhee Han, Sungyoon Song and Jaehyeong Lee                                                                               |

| Stochastic Operation of BESS and MVDC Link in Distribution Networks Under Uncertainty                                       |

| Reprinted from: Electronics 2025, 14, 2737, https://doi.org/10.3390/electronics14132737 96                                  |

| Mingyang Ou, Pingping Gong, Huajie Guo and Gaoxiang Li                                                                      |

| A Passivity-Based Control Integrated with Virtual DC Motor Strategy for Boost Converters                                    |

| Feeding Constant Power Loads                                                                                                |

| Reprinted from: <i>Electronics</i> <b>2025</b> , <i>14</i> , 2909, https://doi.org/10.3390/electronics14142909 <b>118</b>   |

| Longfei Cui, Yiming Zhang, Xuhong Wang and Dong Zhang                                                                       |

| Symmetric Optimization Strategy Based on Triple-Phase Shift for Dual-Active Bridge                                          |

| Converters with Low RMS Current and Full ZVS over Ultra-Wide Voltage and Load Ranges                                        |

| Reprinted from: Electronics 2025, 14, 3031, https://doi.org/10.3390/electronics14153031 135                                 |

#### **About the Editors**

#### Daniele Scirè

Daniele Scirè received an M.S. degree in Electronic Engineering and a Ph.D. degree in Information and Communication Technologies from the University of Palermo, Palermo, Italy, in 2017 and 2021, respectively. From 2018 to 2019, he was a visiting Ph.D. student with the Photovoltaic Material and Devices group, Delft University of Technology, the Netherlands, and in 2024 he was a visiting Researcher with the GREAH at Université de Normandie, France. Since 2022, he has been an Assistant Professor with the University of Palermo, Palermo, Italy. His current research interests include power electronics converters and their control, nonlinear magnetic components, modeling and design of solar cells, and thin-film deposition and characterization. Dr. Scirè was a recipient of the Graduate Student Award from the European Material Research Society in 2019 and of the Best Paper Award "Salvatore (Enzo) Piazza" from the Department of Engineering of the University of Palermo in 2022. Dr. Scirè is a reviewer for several journals and conferences.

#### Gianpaolo Vitale

Gianpaolo Vitale received an M.S. degree in electronic engineering from the University of Palermo, Palermo, Italy, in 1988. He is a Research Director of the Institute for High-Performance Computing and Networking, which is part of the National Research Council of Italy. He received his National Academic Qualification as a full professor in electronic engineering (cod 09\_E3) in 2017 and his National Academic Qualification as a full professor in electric energy engineering (cod. 09/E2) in 2013. He teaches industrial electronics in the Department of Engineering, MD Electronics Engineering, University of Palermo. He is a Senior Member of IEEE. He has co-authored two books, three edited books, four book chapters, and more than a hundred scientific works. His current research interests include power electronics, power generation from renewable sources, electromagnetic compatibility, and robotics. He serves as a reviewer for several journals and conferences.

#### **Preface**

This Reprint on Advanced Control Techniques for Power Converters and Drives gathers a selection of recent research papers that address the growing complexity of power electronics and electric drive systems. The subject matter reflects the shift from conventional linear controllers toward predictive, adaptive, and passivity-based strategies, as well as advanced modulation methods that improve performance under stringent constraints.

The scope of this Reprint includes device-level modeling, real-time digital implementation, EMI-aware control, and distributed coordination of converters in large-scale energy and transportation systems. Contributions highlight both theoretical developments and experimental validations, showing how advanced control can be practically realized in motor drives, renewable energy integration, multiport architectures, and emerging aerospace and industrial applications.

The purpose of this collection is to provide a comprehensive reference for the community, showcasing how new control paradigms can enhance efficiency, robustness, and resilience while addressing challenges such as nonlinear component behavior, thermal effects, and system-level uncertainty.

The motivation for preparing this Reprint stems from the rapid adoption of wide-bandgap devices, the increasing penetration of converter-dominated grids, and the demand for certifiable, high-performance control strategies in safety-critical environments.

This Reprint is addressed to researchers, graduate students, and practicing engineers in the fields of power electronics, control systems, and electrical drives. It also serves as a resource for professionals working in renewable energy, electric mobility, aerospace, and industrial automation who are seeking insights into the future of advanced control solutions for power converters and drives.

Daniele Scirè and Gianpaolo Vitale

Guest Editors

Editorial

### **Advanced Control Techniques for Power Converter and Drives**

Daniele Scirè 1,\* and Gianpaolo Vitale 2,\*

- Department of Engineering, University of Palermo, 90128 Palermo, Italy

- Consiglio Nazionale delle Ricerche, ICAR, Institute for High Performance Computing and Networking, Italian National Research Council of Italy, 90146 Palermo, Italy

- \* Correspondence: daniele.scire@unipa.it (D.S.); gianpaolo.vitale@icar.cnr.it (G.V.)

#### 1. Introduction

Advanced control is now central to performance, robustness, and the ability to achieve the highest power density in modern power converters. Beyond classical linear designs, research has rapidly expanded across model predictive control, adaptive and robust methods, passivity-based strategies, and learning-enabled controllers, together with spectrum-shaping modulation to address the EMI and vibro-acoustics in drive systems [1–10]. These techniques are being exploited in demanding contexts such as grid-forming inverters, hybrid AC/DC networks, and electrified transportation, where tight transience, device stress limits, and grid codes must all be satisfied simultaneously.

Despite the progress, several gaps remain regarding the control design, device physics, and implementation: (i) accurate handling of nonlinear magnetic components within real-time controllers; (ii) stability guarantees for distributed and parallelized converter architectures; (iii) realizations of complex control schemes on embedded platforms (e.g., FPGAs); and (iv) grid-interactive scheduling and optimization frameworks that explicitly treat uncertainty while coordinating power–electronic elements in distribution networks.

Recent work has started to close these gaps. For example, the authors of [11] propose a quasi-constant on-time (QCOT) control for SMPS operating with nonlinear temperaturedependent inductors; by estimating the power switch conduction time and exploiting the saturation safely, the QCOT raises the inductor current capability and power density while avoiding thermal runaway. In [12], a 4 MW high-power-density generator for hybrid-electric aircraft, targeting gravimetric power densities around 20 kW/kg with advanced PM design and thermal management is presented. In [13], the authors propose a multiport power conversion system (MPCS) for the More Electric Aircraft, enabling fault-tolerant ring power distribution with minimal weight penalty. An advanced discontinuous PWM for multilevel cascaded H-bridge converters, reducing switching losses while mitigating harmonic degradation in N-cell structures, is reported in [14]. A modulated model-predictive integral control for synchronous reluctance motor drives, ensuring fixed switching frequency, low ripple, and robustness against parameter mismatches is presented in [15]. Finally, ref. [16] explores sampling-time harmonic control for cascaded H-bridges under active thermal control, addressing lifetime extension while suppressing low-order distortion.

This Special Issue was conceived to collect the latest research across advanced control theory, power-device and passive modeling, and embedded implementation and to highlight solutions that translate into experimentally validated performance gains in the specific field of power electronics.

In order to meet the demand for new contributions also relating to the abovementioned topics, we are pleased to announce that a Second Edition of this Special Issue is now open

for submissions. We particularly welcome innovative contributions to the field of advanced control techniques for power electronics converters and drives. For further details, please see https://www.mdpi.com/journal/electronics/special\_issues/M485MV576M, (accessed on 15 September 2025).

#### 2. Highlighting Key Contributions

This Special Issue brings together a selection of innovative research articles that demonstrate the state of the art in control methodologies for power converters and electric drives. The following contributions reflect significant progress in areas including harmonic mitigation, voltage stability, efficiency optimization, and intelligent control implementation.

#### 2.1. Double-Loop Controller Design of a Single-Phase 3-Level Power Factor Correction Converter

Han and Kim (Contribution 1) detail a practical inner–outer loop design (SISOTOOL-based) augmented with a targeted 120 Hz band-stop to suppress ripple injection while preserving the dynamic response. The hardware results show clean boost and buck transitions (210 V to 150 V) without overshoot and stable behavior under load steps (50  $\Omega$  to 25  $\Omega$ ), matching the PSIM predictions.

# 2.2. Robust PI-PD Controller Design: Industrial Simulation Case Studies and a Real-Time Application

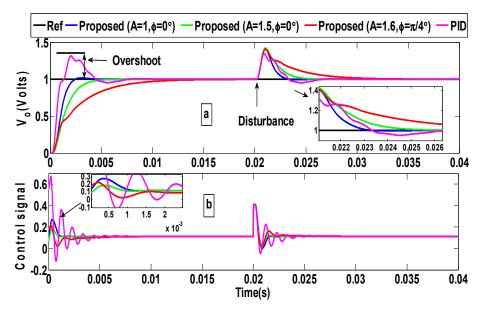

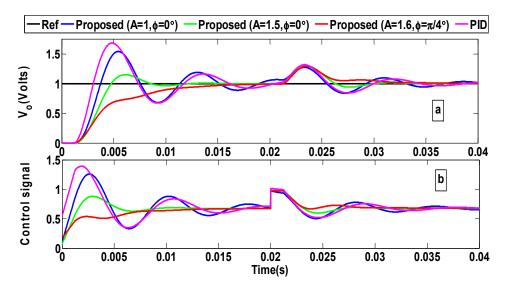

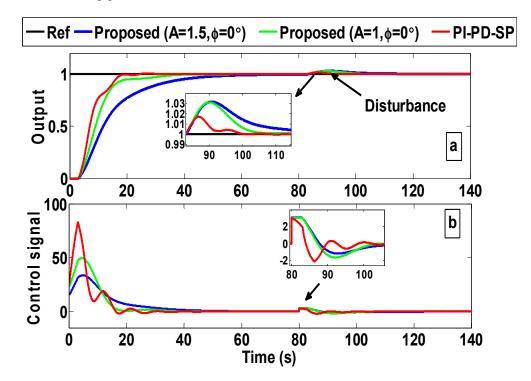

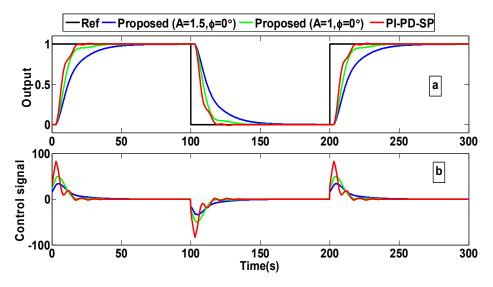

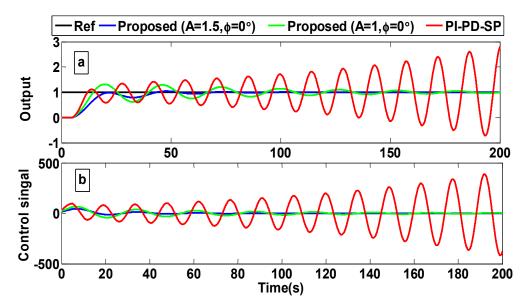

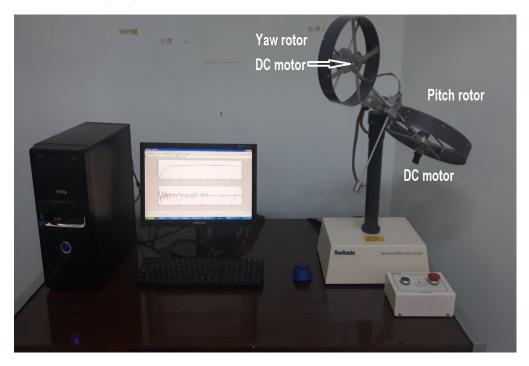

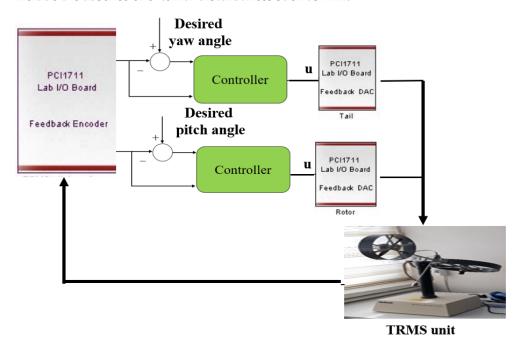

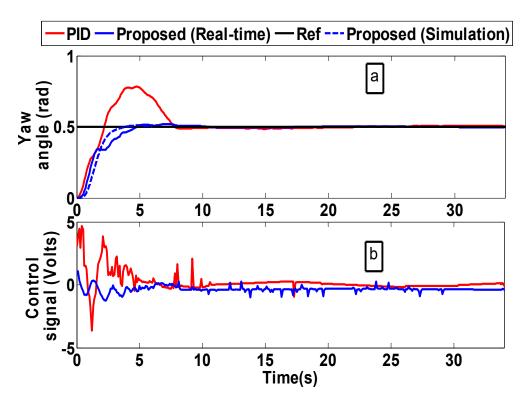

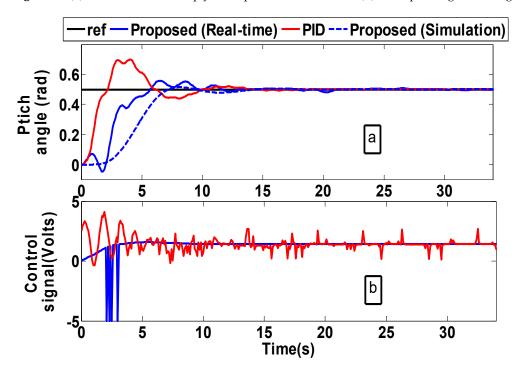

Alyoussef, Kaya, and Akrad (Contribution 2) propose a geometry-driven robust design method that characterizes the controller parameter region, guaranteeing closed-loop stability and adequate margins, which then selects a PI–PD operating point near the region centroid. Hardware-in-the-loop and real-time tests on a twin-rotor MIMO system (TRMS) confirm the setpoint tracking and disturbance rejection with low tuning effort and transparent robustness guarantees.

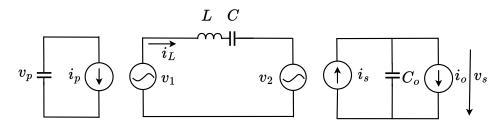

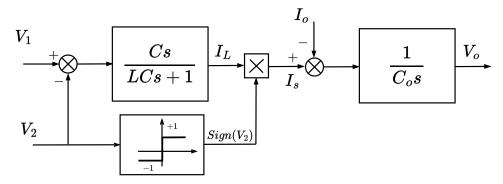

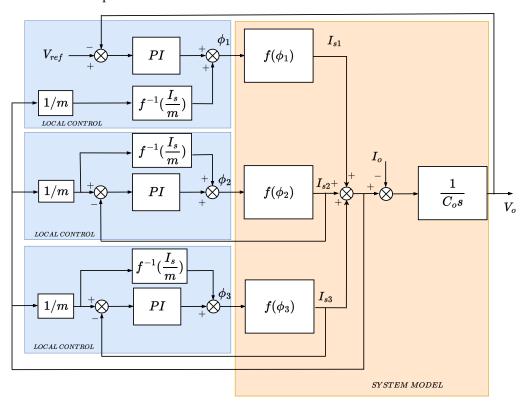

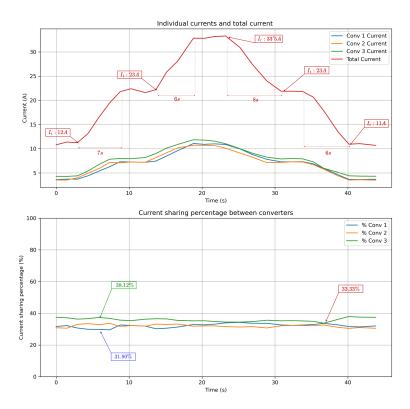

#### 2.3. Advanced Distributed Control of Parallel Resonant CLLC DAB Converters

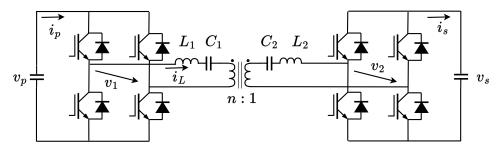

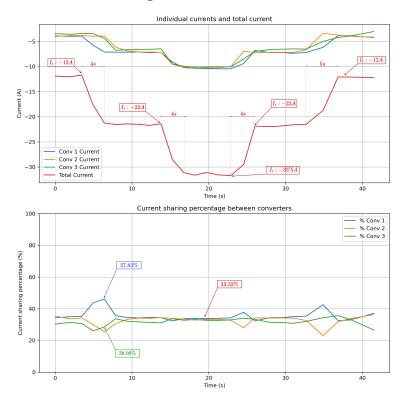

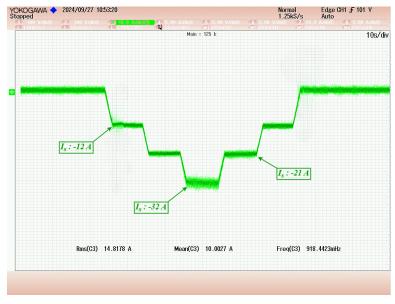

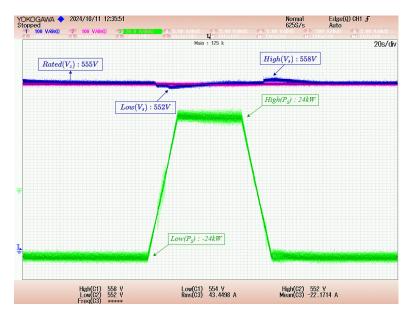

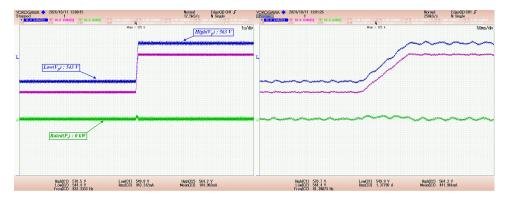

Vicente et al. (Contribution 3) propose a scalable distributed architecture that combines a master voltage controller with local current controllers to balance load and suppress circulating currents in parallel CLLC DAB stages. The experiments demonstrated stability, an  $\sim\!80\%$  faster transient via a feed-forward path, and a current-sharing deviation  $<\!3\%$  from light to full load, achieved without a fragile centralized current bus, making it attractive for hybrid AC/DC microgrids and SST front-ends.

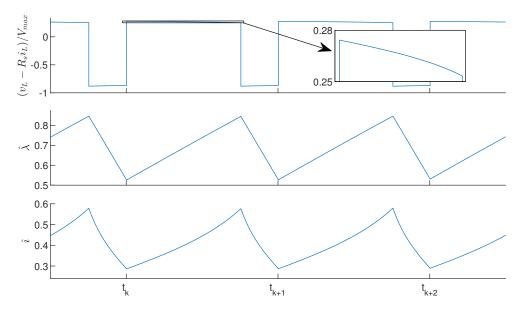

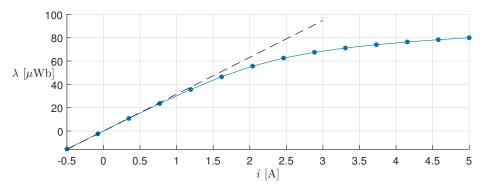

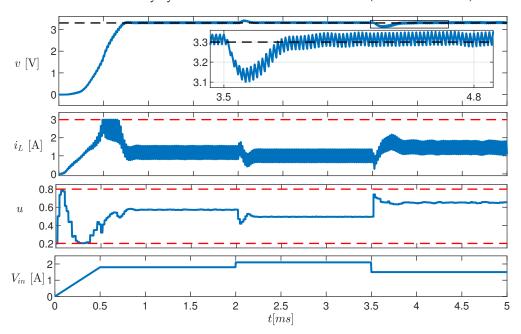

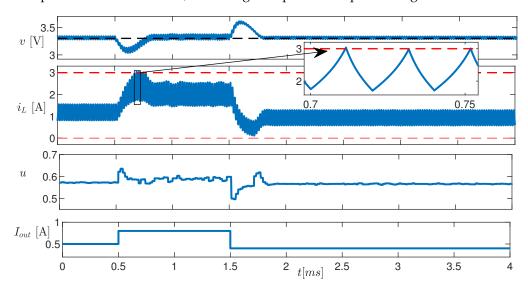

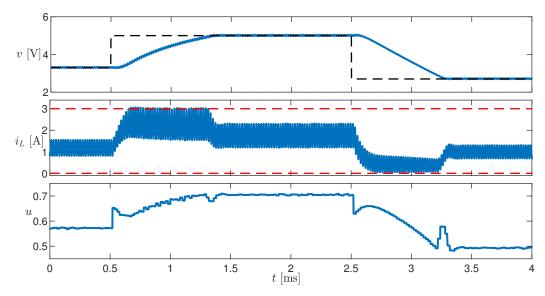

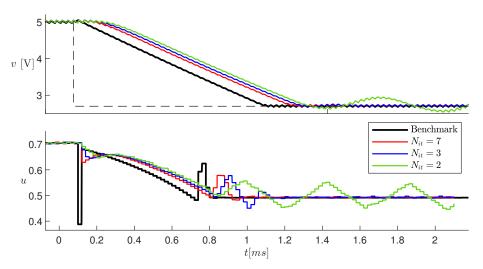

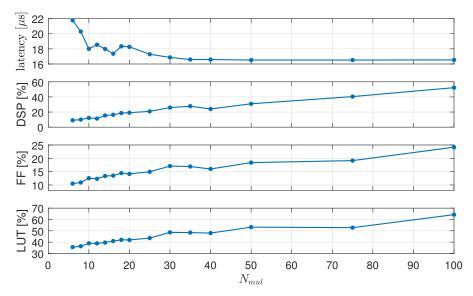

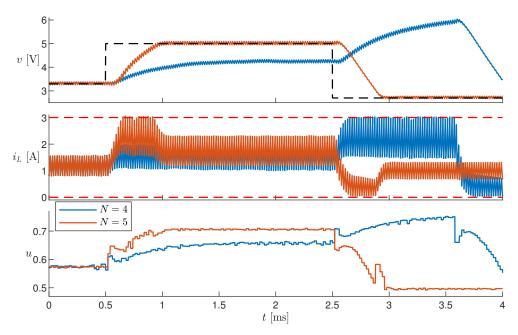

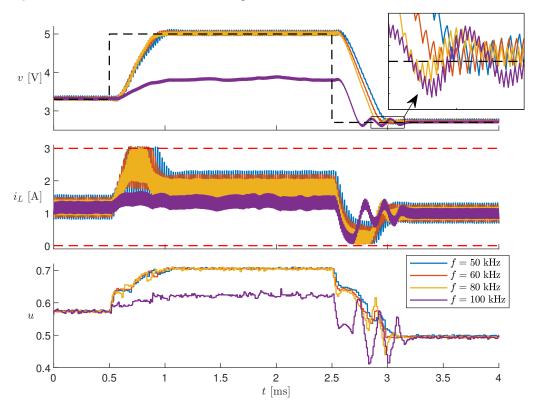

# 2.4. FPGA Implementation of Nonlinear Model Predictive Control for a Boost Converter with a Partially Saturating Inductor

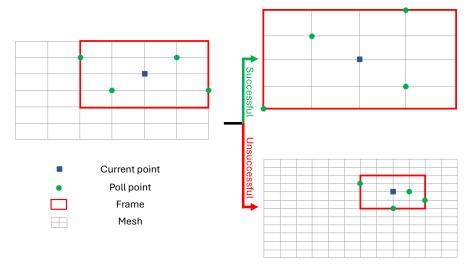

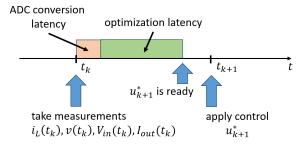

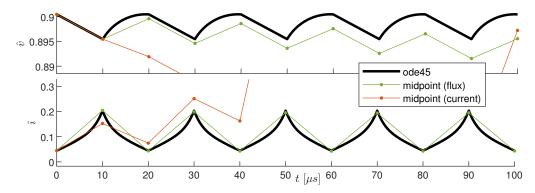

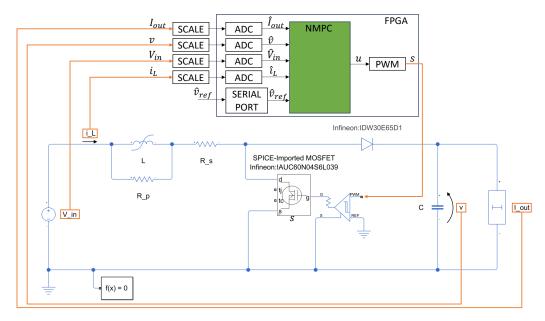

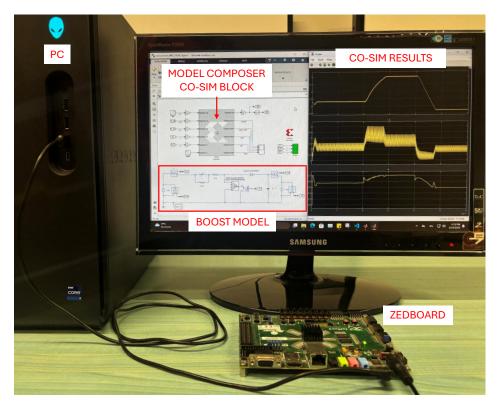

Ravera et al. (Contribution 4) embed a nonlinear inductor and thermal-aware converter model into an NMPC solved by Mesh Adaptive Direct Search, mapped to an AMD/Xilinx FPGA. The co-simulation and experiments show sub-millisecond voltage regulation under steps, while respecting current constraints; practical figures include a control latency of  $\sim\!16.6~\mu s$  and operation up to 60 kHz sampling, illustrating a viable path to high-speed certifiable MPC in power supplies.

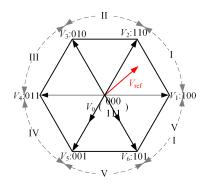

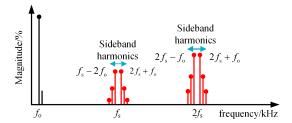

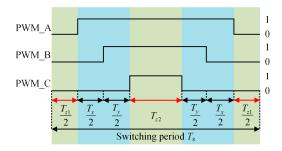

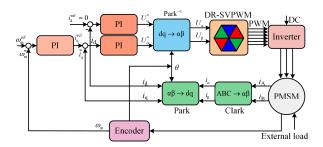

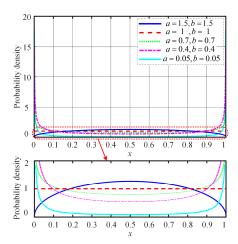

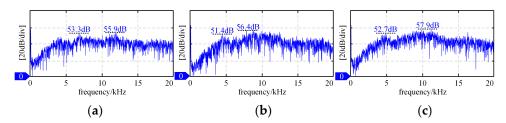

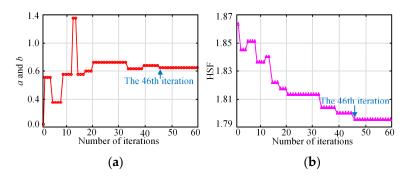

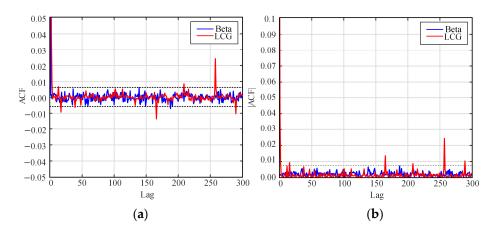

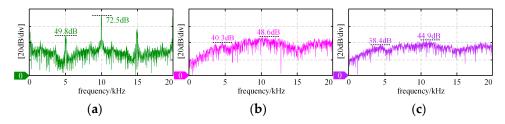

## 2.5. Dual-Random Space Vector Pulse Width Modulation Strategy Based on Optimized Beta Distribution

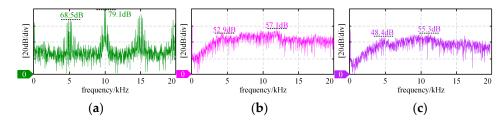

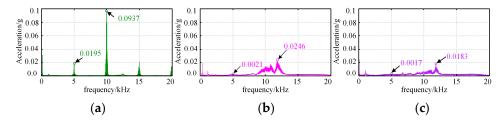

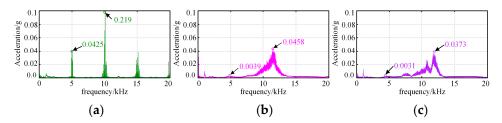

Gu et al. (Contribution 5) introduce a work to reduce high-frequency current harmonics and associated acoustic/vibration signatures in PMSMs; the work randomizes both the switching frequency and zero-vector selection. Using a PSO-tuned Beta distribution for the RNG yielded superior spectral spreading versus classical LCG methods; motor-bench

experiments validated the reductions in high-frequency vibration while preserving the dynamic performance.

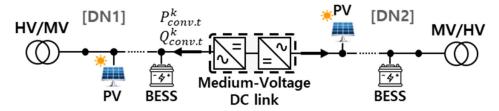

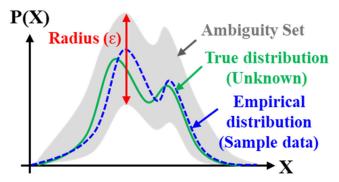

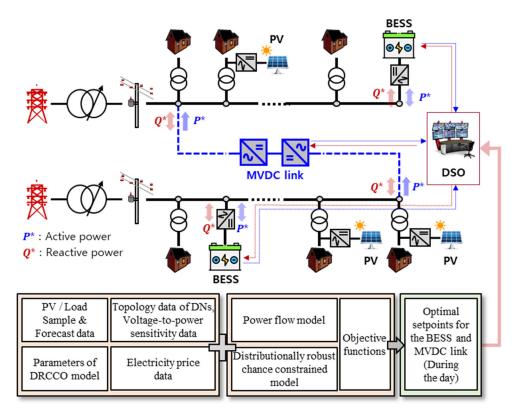

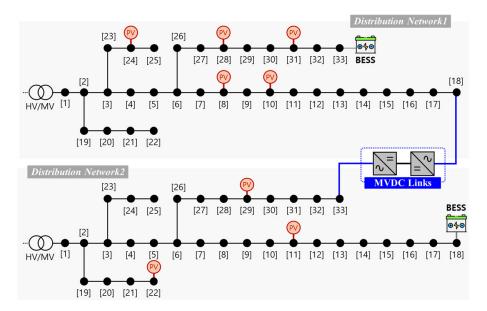

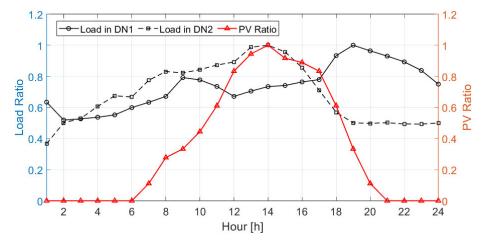

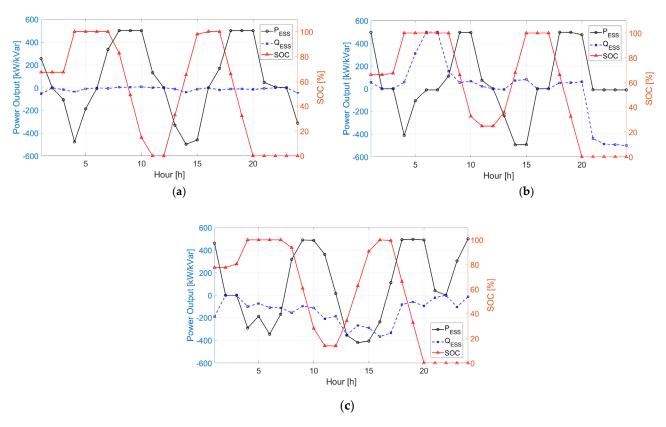

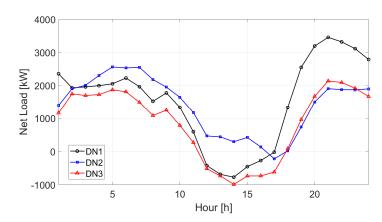

2.6. Stochastic Operation of BESS and MVDC Link in Distribution Networks Under Uncertainty

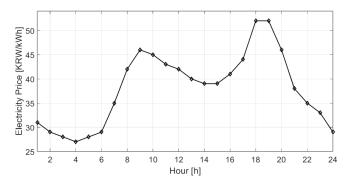

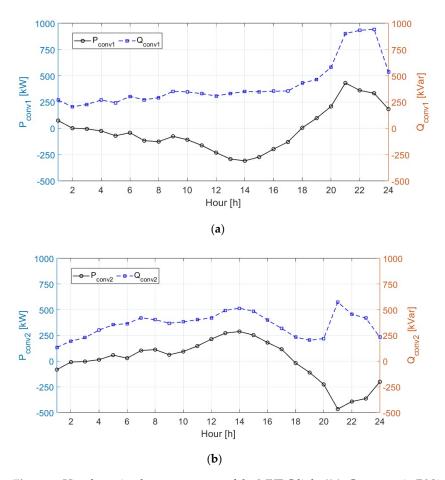

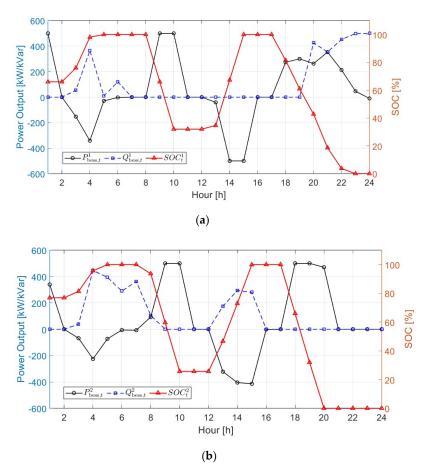

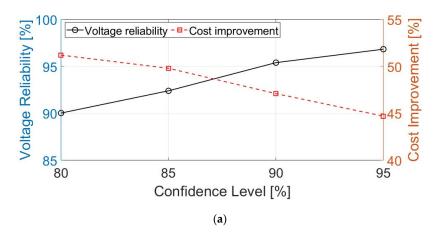

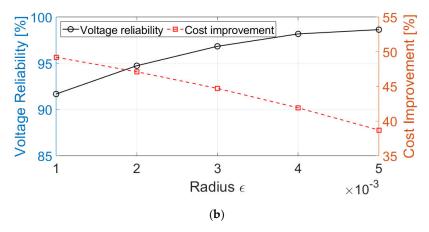

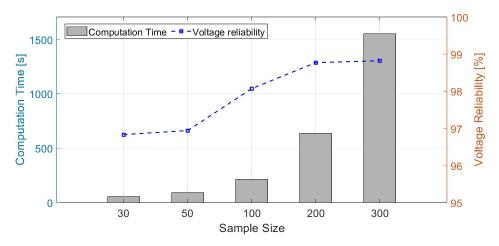

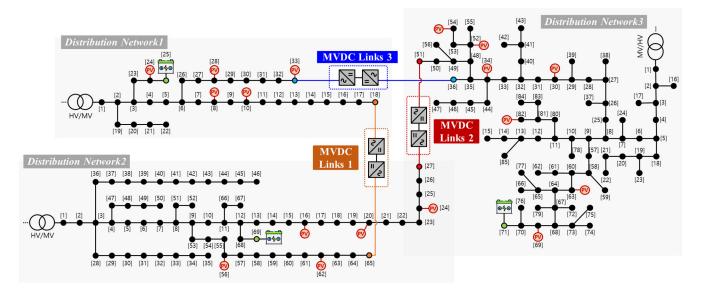

Han, Song, and Lee (Contribution 6) introduce a distributionally robust chance-constrained (DRCC) scheduler that coordinates MVDC link setpoints and BESS dispatch across interconnected feeders with PV/load uncertainty. Case studies quantify the cost–reliability trade, e.g., up to 44.7% operational cost reduction, while maintaining  $\approx$ 96.8% bus-voltage reliability, showing how probabilistic reliability constraints can be tuned to system economics.

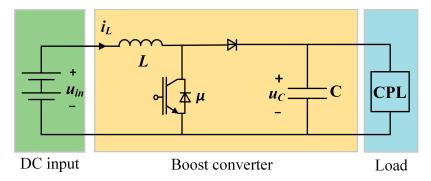

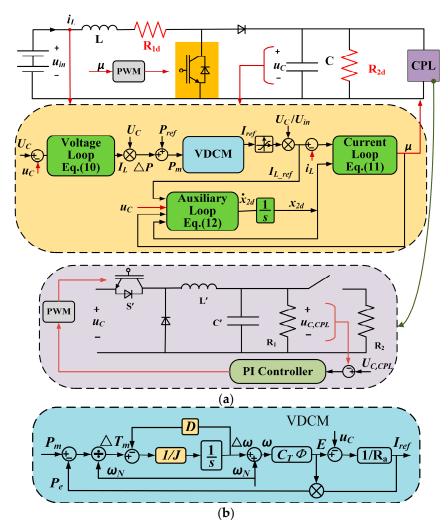

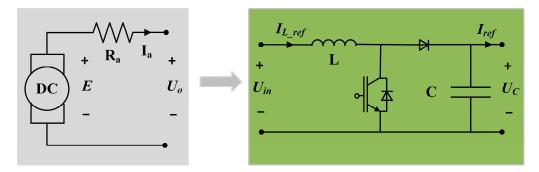

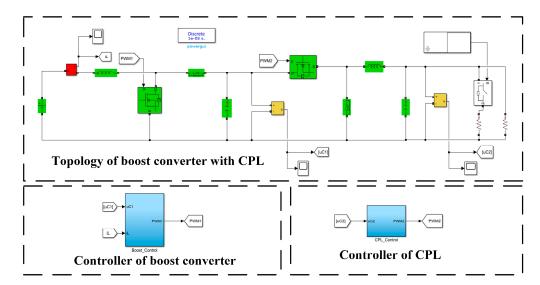

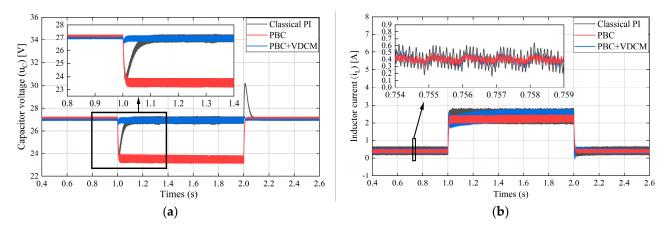

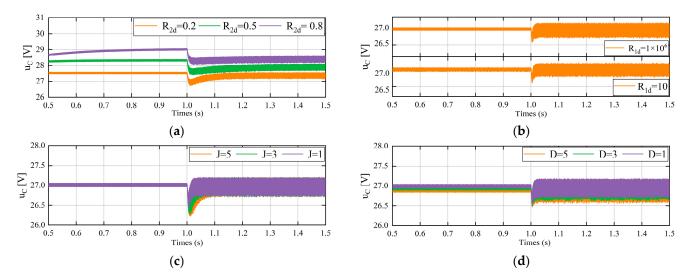

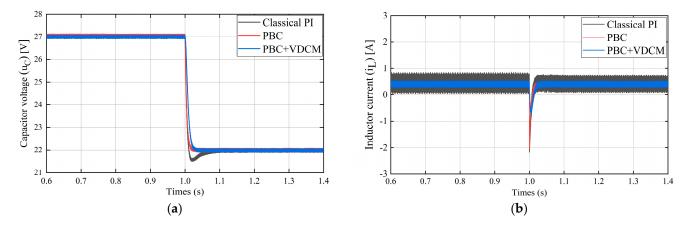

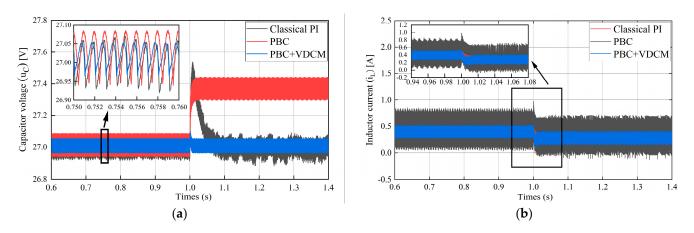

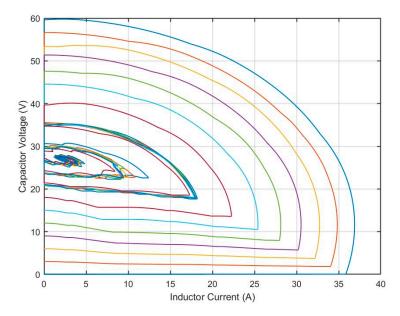

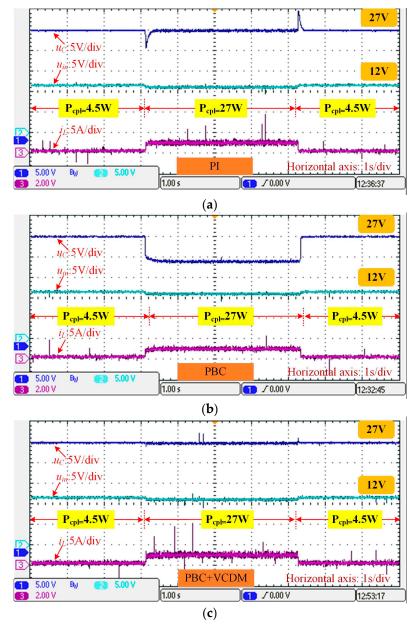

2.7. A Passivity-Based Control Integrated with Virtual DC Motor Strategy for Boost Converters Feeding Constant Power Loads

Ou et al. (Contribution 7) present a passivity observer/controller framework with a "virtual DC motor" current loop that yields robust damping and constraint handling for grid-forming inverters under grid disturbances. The method maintains synchronization and current limits without retuning across operating points, and the experiments indicated improved stability margins relative to standard inner loops.

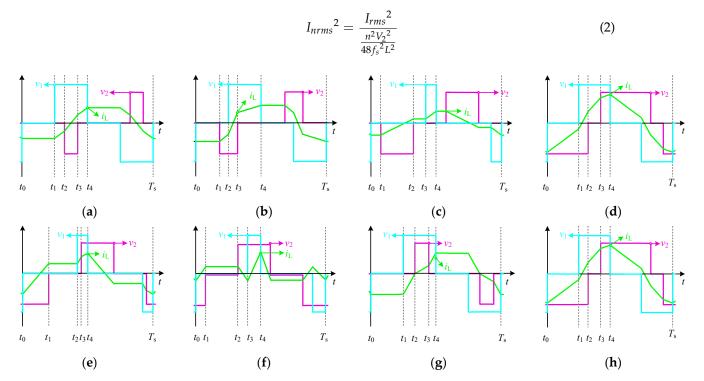

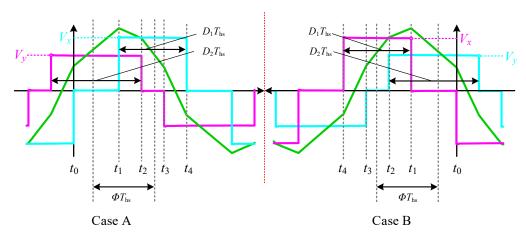

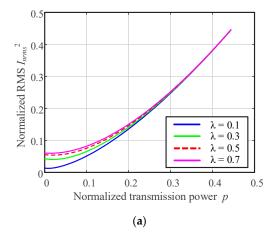

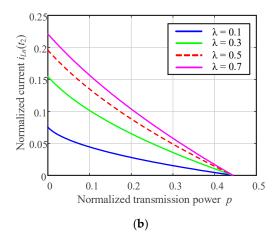

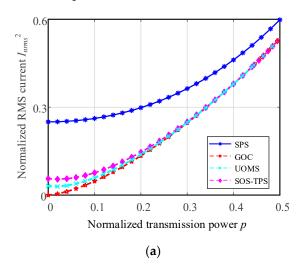

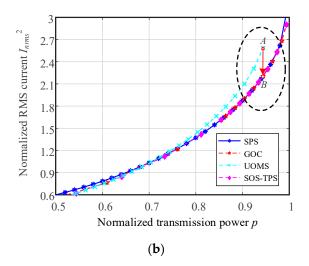

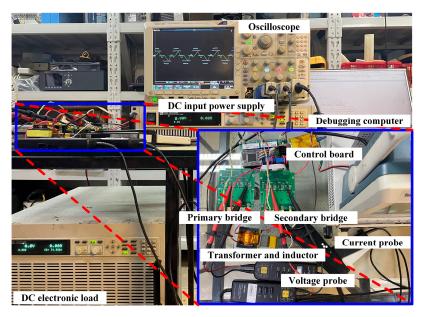

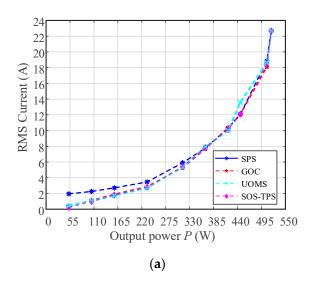

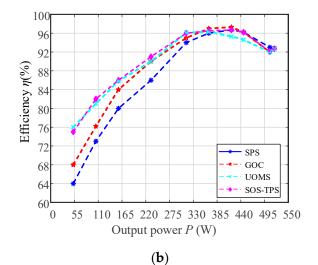

2.8. Symmetric Optimization Strategy Based on Triple-Phase Shift for Dual-Active Bridge Converters with Low RMS Current and Full ZVS over Ultra-Wide Voltage and Load Ranges

Cui et al. (Contribution 8) focus on RMS-current minimization and ZVS extension; this paper synthesizes recent DAB modulation strategies and outlines implementable heuristics for efficiency over wide operating ranges. It provides design guidance that complements distributed and resonant topologies elsewhere in this Special Issue.

Funding: This research received no external funding.

**Acknowledgments:** We extend our appreciation to all the authors who contributed their research to this Special Issue with their innovative work. We are grateful to the reviewers for their thorough and insightful evaluations, which greatly enhanced the scientific rigor and clarity of the published articles. Our special thanks also go to the editorial team and staff of *Electronics* at MDPI for their continued support and for providing us with the opportunity to serve as Guest Editors of this Special Issue.

Conflicts of Interest: The authors declare no conflicts of interest.

#### **List of Contributions**

- Han, J.-H.; Kim, I.-S. Double-Loop Controller Design of a Single-Phase 3-Level Power Factor Correction Converter. *Electronics* 2024, 13, 2863. https://doi.org/10.3390/electronics13142863.

- Alyoussef, F.; Kaya, I.; Akrad, A. Robust PI-PD Controller Design: Industrial Simulation Case Studies and a Real-Time Application. *Electronics* 2024, 13, 3362. https://doi.org/10.3390/electronics13173362.

- Vicente, D.C.; Carrero, A.M.; Díez, E.G.; Solís, J.M.C.; Rubio, F.R. Advanced Distributed Control

of Parallel Resonant CLLC DAB Converters. *Electronics* 2025, 14, 318. https://doi.org/10.3390/

electronics14020318.

- Ravera, A.; Oliveri, A.; Lodi, M.; Storace, M. FPGA Implementation of Nonlinear Model Predictive Control for a Boost Converter with a Partially Saturating Inductor. *Electronics* 2025, 14, 941. https://doi.org/10.3390/electronics14050941.

- 5. Gu, X.; Wu, K.; Jin, X.; Zhang, G.; Chen, W.; Li, C. Dual-Random Space Vector Pulse Width Modulation Strategy Based on Optimized Beta Distribution. *Electronics* **2025**, *14*, 1779. https://doi.org/10.3390/electronics14091779.

- 6. Han, C.; Song, S.; Lee, J. Stochastic Operation of BESS and MVDC Link in Distribution Networks Under Uncertainty. *Electronics* **2025**, *14*, 2737. https://doi.org/10.3390/electronics14132737.

- Ou, M.; Gong, P.; Guo, H.; Li, G. A Passivity-Based Control Integrated with Virtual DC Motor Strategy for Boost Converters Feeding Constant Power Loads. *Electronics* 2025, 14, 2909. https://doi.org/10.3390/electronics14142909.

- 8. Cui, L.; Zhang, Y.; Wang, X.; Zhang, D. Symmetric Optimization Strategy Based on Triple-Phase Shift for Dual-Active Bridge Converters with Low RMS Current and Full ZVS over Ultra-Wide Voltage and Load Ranges. *Electronics* **2025**, *14*, 3031. https://doi.org/10.3390/electronics14153 031.

#### References

- 1. Schwenzer, M.; Ay, M.; Bergs, T.; Abel, D. Review on model predictive control: An engineering perspective. *Int. J. Adv. Manuf. Technol.* **2021**, 117, 1327–1349. [CrossRef]

- 2. Panda, S.K.; Subudhi, B. A Review on Robust and Adaptive Control Schemes for Microgrid. *J. Mod. Power Syst. Clean Energy* **2023**, *11*, 1027–1040. [CrossRef]

- 3. Gholami-Khesht, H.; Davari, P.; Blaabjerg, F. Chapter 5—Adaptive control in power electronic systems. In *Control of Power Electronic Converters and Systems*; Blaabjerg, F., Ed.; Academic Press: Cambridge, MA, USA, 2021; pp. 125–147. [CrossRef]

- 4. Ren, Q.; Chen, A.; Fang, J.; Liu, X.; Liu, T.; Zhang, G.; Zhang, C. An Improved Passivity-Based Direct Power Control Strategy for AC/DC Converter Under Unbalanced and Distorted Grid Conditions. *IEEE Trans. Power Electron.* **2023**, *38*, 12153–12165. [CrossRef]

- 5. Khalid, M. Passivity-Based Nonlinear Control Approach for Efficient Energy Management in Fuel Cell Hybrid Electric Vehicles. *IEEE Access* **2024**, *12*, 84169–84188. [CrossRef]

- 6. Qiu, Z.; Chen, Y.; Liu, X.; Kang, Y.; Liu, H. Analysis of the sideband current harmonics and vibro-acoustics in the PMSM with SVPWM. *IET Power Electron.* **2020**, *13*, 1033–1040. [CrossRef]

- 7. Ibrahim, A.; Salem, M.; Kamarol, M.; Delgado, M.T.; Desa, M.K.M. Review of Active Thermal Control for Power Electronics: Potentials, Limitations, and Future Trends. *IEEE Open J. Power Electron.* **2024**, *5*, 414–435. [CrossRef]

- 8. Yu, Z.; Long, J. Review on Advanced Model Predictive Control Technologies for High-Power Converters and Industrial Drives. *Electronics* **2024**, *13*, 4969. [CrossRef]

- 9. Yusuf, S.S.; Kunya, A.B.; Abubakar, A.S.; Salisu, S. Review of load frequency control in modern power systems: A state-of-the-art review and future trends. *Electr. Eng.* **2025**, *107*, 5823–5848. [CrossRef]

- Zelba, M.; Deveikis, T.; Gudžius, S.; Jonaitis, A.; Bandza, A. Review of Power Control Methods for a Variable Average Power Load Model Designed for a Microgrid with Non-Controllable Renewable Energy Sources. Sustainability 2023, 15, 9100. [CrossRef]

- 11. Scirè, D.; Lullo, G.; Vitale, G. A Quasi-Constant On-Time Control for SMPS with a Nonlinear Inductor Based on Power Switch Conduction Time Estimation. *IEEE Trans. Ind. Inform.* **2024**, 21, 1419–1428. [CrossRef]

- 12. Golovanov, D.; Gerada, D.; Sala, G.; Degano, M.; Trentin, A.; Connor, P.H.; Xu, Z.; Rocca, A.L.; Galassini, A.; Tarisciotti, L.; et al. 4-MW Class High-Power-Density Generator for Future Hybrid-Electric Aircraft. *IEEE Trans. Transp. Electrif.* 2021, 7, 2952–2964. [CrossRef]

- 13. Gu, C.; Yan, H.; Yang, J.; Sala, G.; De Gaetano, D.; Wang, X.; Galassini, A.; Degano, M.; Zhang, X.; Buticchi, G. A Multiport Power Conversion System for the More Electric Aircraft. *IEEE Trans. Transp. Electrif.* **2020**, *6*, 1707–1720. [CrossRef]

- 14. Marquez, A.; Monopoli, V.G.; Tcai, A.; Leon, J.I.; Buticchi, G.; Vazquez, S.; Liserre, M.; Franquelo, L.G. Discontinuous-PWM Method for Multilevel *N*-Cell Cascaded H-Bridge Converters. *IEEE Trans. Ind. Electron.* **2021**, *68*, 7996–8005. [CrossRef]

- Riccio, J.; Karamanakos, P.; Odhano, S.; Tang, M.; Nardo, M.D.; Tresca, G.; Zanchetta, P. Modulated Model-Predictive Integral Control Applied to a Synchronous Reluctance Motor Drive. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 3000–3010. [CrossRef]

- 16. Marquez, A.; Monopoli, V.G.; Leon, J.I.; Ko, Y.; Buticchi, G.; Vazquez, S.; Liserre, M.; Franquelo, L.G. Sampling-Time Harmonic Control for Cascaded H-Bridge Converters with Thermal Control. *IEEE Trans. Ind. Electron.* **2020**, *67*, 2776–2785. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Article

# Double-Loop Controller Design of a Single-Phase 3-Level Power Factor Correction Converter

Jun-Hyuk Han and IL-Song Kim \*

Department of Electrical Engineering, Korea National University of Transportation, Chungju 27469, Republic of Korea; 22028405@a.ut.ac.kr

\* Correspondence: iskim@ut.ac.kr

Abstract: This paper presents a study on the double-loop controller design technique for a single-phase power factor correction (PFC) three-level (TL) boost converter. Designing a double-loop controller using conventional methods is challenging due to the 120 Hz voltage ripple in the output voltage. This study proposes new double-loop control design methods using a band-stop filter and MATLAB SISOTOOL, detailed in a step-by-step sequence. A band-stop filter with a 120 Hz stop band is applied to the double-loop controller design. Modeling based on the state-space equation, applicable to the full duty range, is constructed to obtain the transfer function. The double-loop controller structure is then designed, and optimal gains that satisfy the design requirements are obtained through automatic tuning using the MATLAB SISOTOOL library. The simulation results demonstrate the performance of the proposed method, which is further verified by experimental results.

Keywords: three-level boost converter; PFC; double-loop control; MATLAB SISOTOOL

#### 1. Introduction

Global population growth, economic growth, industrialization, and technological advancements continue to increase the demand for today's limited energy resources. Electronic systems, in particular, account for a significant portion of energy consumption. Efficient management and conservation of these systems can significantly contribute to energy savings and cost reduction. In response to the growing demand for limited energy resources and rising energy prices, improving power efficiency in electronic systems has become a critical challenge.

In recent years, research on efficient energy conversion technologies has been active, and power factor correction (PFC) has garnered significant attention, particularly for single-phase PFC. Power factor correction offers several benefits, including improved power quality, increased energy efficiency, and reduced power losses.

The circuit to implement a single-phase PFC consists of a voltage controller to regulate the direct current (DC) voltage at the output and a current controller to control the alternating current (AC) at the input, maintaining it in a sinusoidal wave to achieve a nearly uniform power factor. The detailed configuration is presented in Section 3, "Double Loop Controller Design". In a single-phase PFC system, there is only one power source. Therefore, the single-phase AC is passed through an all-pass filter (APF) to create a virtual AC with a 90-degree phase shift. This virtual AC is then converted to DC through a d-q conversion for control purposes. With d-q conversion, alternating current is effectively converted to direct current, allowing for control and regulation in a single-phase PFC system [1]. This approach is widely used due to its high efficiency, simple topology, continuous input current, and step-up voltage conversion ratio. Another approach could involve using the instantaneous AC control method; however, this approach may introduce steady-state errors.

Single-phase PFC systems often utilize boost converters to leverage these benefits. Boost converters are preferred in single-phase PFCs because they can adjust the output voltage by boosting it while maintaining a high power factor.

However, with the recent increase in the use of high-power applications, the use of single-level boost converters in PFC circuits has increased the volume and weight of the inductor, and losses in the power devices have become a major factor affecting the cost and efficiency of the converter. These applications are energy-intensive and consume significant power from the power network. High-power applications, such as electric vehicles, electric buses, railroad cars, power plants, substations, and distribution systems in energy production, as well as distribution systems for electric vehicles, require substantial power.

To compensate for the disadvantages of the single boost converter structure, the application of a boost converter with a three-level (TL) structure to PFC has been studied as a possible solution [2–5]. Compared to conventional boost converters, TL boost converters offer higher efficiency and a wider control range. However, since single-phase PFC circuits generate a 120 Hz ripple at the output, designing a double-loop controller is challenging. This challenge is further compounded when adopting a TL boost converter structure. Previous research has utilized notch filters or lead-lag compensators to compensate for the 120 Hz ripple. However, these methods can potentially induce instability and complicate the design of a double-loop controller [6].

This paper presents the results of a study in which a single-phase PFC double-loop controller design technique, accommodating the 120 Hz ripple, is applied to a TL boost converter. After constructing the state-space equations applicable to the entire duty range to obtain the transfer function, a double-loop controller was designed using MATLAB SISOTOOL. The validity of the designed controller was verified through PSIM simulations and experimental results.

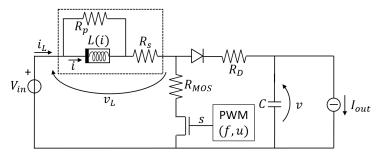

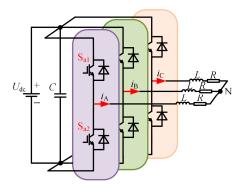

#### 2. System Modeling

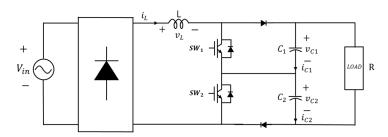

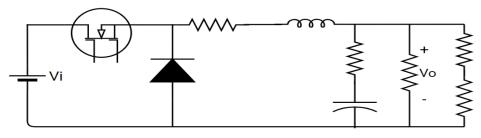

The circuit diagram of the single-phase three-level (TL) PFC converter with a diode bridge rectifier is shown in Figure 1. This configuration has the disadvantage of an increased number of semiconductor switches, diodes, and capacitors due to the cascade connection compared to the two-level configuration. However, it also has advantages, such as a reduced volume and weight of the inductor and reduced voltage stress on the semiconductor switches. In fact, the three-level configuration can reduce the voltage ratings of the semiconductor switches and diodes to half of those in the two-level configuration. Therefore, the three-level PFC converter can significantly reduce material costs.

Figure 1. The circuit diagram of TL PFC converter.

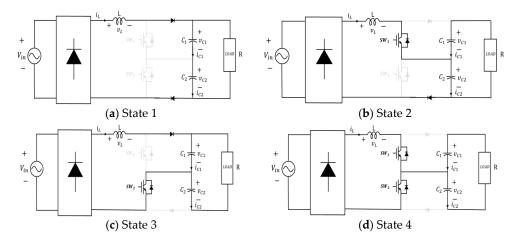

The dynamic mathematical model of the TL PFC converter can be obtained by analyzing the switch operations. The equivalent circuit of the TL PFC converter is divided into four operating states according to the switching operation, as shown in Figure 2. The state when both switches,  $SW_1$  and  $SW_2$ , are off is shown in Figure 2a. The state when  $SW_1$  is on while  $SW_2$  is off is shown in Figure 2b. The state when  $SW_1$  is off, and  $SW_2$  is on is shown in Figure 2c. Finally, Figure 2d depicts the state when both switches,  $SW_1$  and  $SW_2$ , are on.

Figure 2. TL PFC converter switching operation circuit.

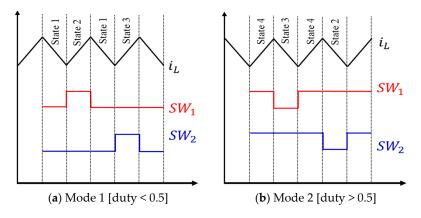

The average state space equation can be derived by analyzing the operation mode determined by the duty boundary of 0.5. When the duty cycle is less than 0.5, it is defined as Mode 1. The operating sequence for Mode 1 is State  $1 \to \text{State } 2 \to \text{State } 1 \to \text{State } 3$ , as depicted in Figure 3a. Conversely, when the duty cycle is greater than 0.5, it is defined as Mode 2. The operating sequence for Mode 2 is State  $4 \to \text{State } 3 \to \text{State } 4 \to \text{State } 2$ , as shown in Figure 3b. Since the system control involves two operation modes with a duty boundary of 0.5, it is necessary to analyze their operations for both modes. The state space equations for each state are summarized in Table 1.

Figure 3. Mode operation by duty range.

**Table 1.** The summary of the state space equation for each operation states.

| State 1: $[SW_1, SW_2 OFF]$<br>Operation time : $(1 - 2d)Ts$                                                                                                                                                   | State 2: $[SW_1 ON, SW_2 OFF]$<br>Operation time : $(d)Ts$ |                                                                                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $\dot{l}_{L} = \frac{v_{in}}{L} - \frac{(v_{C1} + v_{C2})}{L}$ $\dot{v}_{c1} = \frac{i_{L}}{C_{1}} - \frac{(v_{C1} + v_{C2})}{RC_{1}}$ $\dot{v}_{c2} = \frac{i_{L}}{C_{2}} - \frac{(v_{C1} + v_{C2})}{RC_{2}}$ | (1)                                                        | $\dot{l}_{L} = \frac{v_{in}}{L} - \frac{v_{C2}}{L}$ $\dot{v}_{c1} = -\frac{(v_{C1} + v_{C2})}{RC_{1}}$ $\dot{v}_{c2} = \frac{i_{L}}{C_{2}} - \frac{(v_{C1} + v_{C2})}{RC_{2}}$ | (2) |

|                                                                                                                                                                                                                |                                                            | State 4: $[SW_1, SW_2 ON]$<br>Operation time : $(2d-1)Ts$                                                                                                                      |     |

| $\dot{v}_{c1} = rac{v_{in}}{L} - rac{v_{C1}}{L} \ \dot{v}_{c1} = rac{i_L}{C_1} - rac{(v_{C1} + v_{C2})}{RC_1} \ \dot{v}_{c2} = -rac{(v_{C1} + v_{C2})}{RC_2}$                                             | (3)                                                        | $\dot{\hat{l}}_L = rac{v_{in}}{L} \ \dot{v}_{c1} = -rac{(v_{c1} + v_{c2})}{RC_1} \ \dot{v}_{c2} = -rac{(v_{c1} + v_{c2})}{RC_2}$                                            | (4) |

The state-averaging equations can be calculated by multiplying the state equations and their operation time for each Mode. The resultant state-averaging equations are the same for Mode 1 and Mode 2 and can be expressed as displayed in (5).

$$\begin{pmatrix} \dot{l}_L \\ \dot{v}_{c1} \\ \dot{v}_{c2} \end{pmatrix} = \begin{pmatrix} 0 & -\frac{(1-d)}{L} & -\frac{(1-d)}{L} \\ -\frac{(1-d)}{C_1} & -\frac{1}{RC_1} & -\frac{1}{RC_1} \\ -\frac{(1-d)}{C_2} & -\frac{1}{RC_2} & -\frac{1}{RC_2} \end{pmatrix} \begin{pmatrix} i_L \\ v_{C1} \\ v_{C2} \end{pmatrix} + \begin{pmatrix} \frac{1}{L} \\ 0 \\ 0 \end{pmatrix} v_{in}$$

(5)

The state-averaging equation of Mode 1 is the same as that of Mode 2, which means that mode transition does not need to be considered when designing the controller. This means that the above equation can be applicable to the full duty range. However, since the above equation includes duty, that is, a variable that changes with time, linearization at the operating point is necessary [7–11]. By applying small signal perturbation for linearization at the operating point, the following linearized equation can be obtained:

$$\begin{pmatrix}

\hat{i}_L \\

\hat{v}_{c1} \\

\hat{v}_{c2}

\end{pmatrix} = \begin{pmatrix}

0 & -\frac{(1-D)}{L} & -\frac{(1-D)}{L} \\

\frac{(1-D)}{C_1} & -\frac{1}{RC_1} & -\frac{1}{RC_1} \\

\frac{(1-D)}{C_2} & -\frac{1}{RC_2} & -\frac{1}{RC_2}

\end{pmatrix} \begin{pmatrix}

\hat{l}_L \\

\hat{v}_{c1} \\

\hat{v}_{c2}

\end{pmatrix} + \begin{pmatrix}

\frac{(V_{c1}+V_{c2})}{L} \\

-\frac{I_L}{C_1} \\

-\frac{I_L}{C_2}

\end{pmatrix} \hat{d}$$

(6)

If assuming that capacitor  $C_1$  and  $C_2$  are equal in the small signal analysis equation, it can be expressed as a quadratic equation, and, thus, a simple controller design is possible. The capacitor imbalance occurs in actual applications. Therefore, the capacitor voltage balancing controller is required for the reduced quadratic equation. The balancing controller design is shown in the controller design section. The final linearized state space equation is shown as follows:

$$\begin{pmatrix} \dot{l}_L \\ \dot{v}_{c0} \end{pmatrix} = \begin{pmatrix} 0 & -\frac{(1-D)}{L} \\ \frac{(1-D)}{C_0} & -\frac{1}{RC_0} \end{pmatrix} \begin{pmatrix} i_L \\ v_{C0} \end{pmatrix} + \begin{pmatrix} \frac{1}{L} \\ 0 \end{pmatrix} v_{in}$$

(7)

And the derived steady-state DC values of  $V_{C0}$ ,  $I_L$  are shown in (8).

$$I_L = \frac{V_{in}}{R(1-D)}, V_{C0} = \frac{V_{in}}{(1-D)}$$

(8)

The input–output transfer function equation for voltage and current controller design can be obtained from the Laplace transform and is shown in the following equations from (9) to (11):

$$\frac{\hat{l}_L(s)}{\hat{d}(s)} = G_1(s) = \frac{\frac{V_{C0}}{L}s + \frac{V_{C0}}{RC_0L} + \frac{I_L}{LC_0}(1-D)}{s^2 + \frac{1}{RC_0} + \frac{1}{LC_0}(1-D)^2}$$

(9)

$$\frac{\hat{v}_{co}(s)}{\hat{d}(s)} = G_2(s) = \frac{-\frac{I_L}{C_0}s + \frac{V_{C0}}{LC_0}(1-D)}{s^2 + \frac{1}{RC_0} + \frac{1}{LC_0}(1-D)^2}$$

(10)

$$\frac{\hat{v}_{c0}(s)}{\hat{l}_{L}(s)} = G_3(s) = \frac{-\frac{I_L}{C_0}s + \frac{V_{C0}}{LC_0}(1-D)}{\frac{V_{C0}}{L}s + \frac{V_{C0}}{RC_0L} + \frac{I_L}{LC_0}(1-D)}$$

(11)

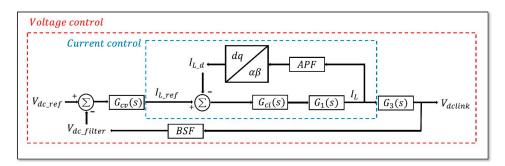

#### 3. Double-Loop Controller Design

The configuration of the single-phase PFC controller consists of a double-loop structure, as illustrated in Figure 4. It comprises a voltage controller for regulating the DC output voltage in the outer loop and a current controller for ensuring the power factor remains close to unity by controlling the current of the AC input terminal as a sine wave in the inner loop. In single-phase PFC control, the Proportional-Integral (PI) controller cannot be directly applied to the current controller because the current waveform is sinusoidal,

not DC. Conventional methods often use an instantaneous AC current controller that adopts a Proportional (P) controller. However, these methods may fail to achieve zero steady-state error and can be problematic when there are abrupt changes in the command or disturbances in the environment.

Figure 4. Double-loop controller configuration.

To achieve zero steady-state error, a PI current controller using DQ transformation can be applied. However, this transformation typically requires at least two sources, which poses a challenge in single-source systems. To overcome this limitation, a virtual 90-degree phase-shifted signal is created. This can be achieved by using a virtual power source or implementing a filter such as an All Pass Filter (APF) [12]. This paper explores the use of APF to facilitate single-phase DQ conversion.

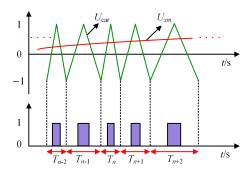

The detailed control block diagram of the outer loop, regulating the output voltage, and the inner loop, controlling the inductor current, is depicted in Figure 4. The output of the voltage controller,  $I_{L\_ref}$  (inductor current reference), is generated through voltage control at the DC output stage. However, in single-phase PFC, voltage ripple occurs at twice the AC input power frequency and manifests in the DC link voltage [13,14]. This ripple not only complicates voltage control but also impacts current control, posing challenges in designing single-phase PFC controllers and determining PI gain values. To address this issue, this paper proposes the use of a band-stop filter in voltage control to suppress the 120 Hz DC voltage ripple. The equation for the Band-stop filter is expressed in (12).

$$BSF = \frac{s^2 + \omega_0^2}{s^2 + Bs + \omega_0^2} \tag{12}$$

From (12), the equations for the stop-band frequency, B and  $\omega_0$ , can be obtained through (13) and (14), respectively.  $f_b$  represents the stop-band frequency, and  $f_c$  represents the reference frequency [15].

$$f_b = \frac{B}{2\pi} \to B = 2\pi f_b \tag{13}$$

$$f_C = \frac{\omega_0}{2\pi} \to \omega_0 = 2\pi f_c \tag{14}$$

By using (13) and (14), the values corresponding to each frequency can be calculated. The transformation from the s-domain (continuous) to the z-domain (discrete), is shown in (15) which is derived by substituting s with  $\frac{2}{T}\frac{1-z^{-1}}{1+z^{-1}}$  in the s-domain equation and expanding it.

$$BSF(Z) = \frac{\left(\frac{4}{T^2} + \omega_0^2\right) + \left(-\frac{8}{T^2} + 2\omega_0^2\right)z^{-1} + \left(\frac{4}{T^2} - \frac{2\omega_0}{2T} + \omega_0^2\right)z^{-2}}{\left(\frac{4}{T^2} + \frac{2\omega_0}{2T} + \omega_0^2\right) + \left(-\frac{8}{T^2} + 2\omega_0^2\right)z^{-1} + \left(\frac{4}{T^2} - \frac{2\omega_0}{2T} + \omega_0^2\right)z^{-2}}$$

(15)

The 120 Hz ripple can be effectively removed using a band-stop filter, as described by Equation (15). The selected parameters are  $f_b = 9.55$  [Hz] and  $f_C = 120$  [Hz]. Equation (15) has been implemented on a microcontroller, such as a Digital Signal Processor (DSP), using C-code programming. The filter can be applied to both 50 Hz and 60 Hz frequencies by

adjusting the parameters of the band-stop filter (BSF). While the manuscript focuses on  $60 \, \text{Hz}$  operation due to its relevance to the grid system used, the flexibility to accommodate both frequencies is noted. Adjusting the BSF parameters enables straightforward adaptation to  $50/60 \, \text{Hz}$  operation.

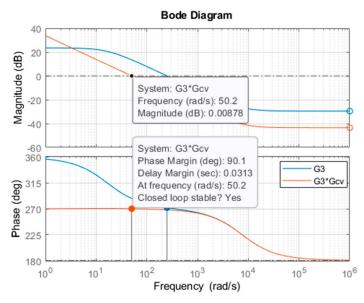

For the design of the voltage controller, specifications are set with a phase margin of 90 degrees and a bandwidth of 50 [rad/s]. The optimal gains that satisfy these design specifications are automatically determined using the MATLAB SISOTOOL library. The transfer function of the final designed voltage controller can be expressed as shown in Equation (16).

$$G_{cv}(s) = 0.2015 \times \frac{s + 16.2}{s} \tag{16}$$

The resultant Bode plot for the designed voltage controller is presented in Figure 5. It can be observed that the phase margin is 90.1 degrees, and the bandwidth is 50.2 [rad/s], meeting the specified design criteria. Therefore, the stability of the system can be confirmed through the Bode plot analysis.

Figure 5. TL PFC converter voltage controller Bode plot.

In the current control configuration, an APF is used to create a virtual 90-degree phase axis, enabling the design of a single-phase DQ transformation. The APF used in the current controller is a mathematical equation that introduces a phase delay without altering the magnitude of the input signal. It became a transfer function with a magnitude of one across all frequency bands and a phase delay ranging from 0 to 180 deg. (1-pole filter). By utilizing the APF, the actual current axis  $I_{\alpha}$  and the virtual current axis  $I_{\beta}$  were generated, as expressed in Equation (17) [16,17]. The DQ transformation formula based on (17) is described in (18).

In the current control configuration, an All Pass Filter (APF) is employed to generate a virtual 90-degree phase axis, facilitating the design of a single-phase DQ transformation. The APF utilized in the current controller is a mathematical equation that introduces a phase delay while preserving the magnitude of the input signal. It operates as a transfer function with a magnitude of one across all frequency bands and introduces a phase delay ranging from 0 to 180 degrees (a 1-pole filter). By utilizing the APF, both the actual current axis  $I_{\alpha}$  and the virtual current axis  $I_{\beta}$  are generated, as expressed in Equation (17). The DQ transformation formula based on Equation (17) is described in Equation (18).

$$I_{\alpha}(k) = I_{L}$$

$$I_{\beta}(k) = 0.9813 \cdot I_{\beta}(k-1) + 0.9813I_{L}(k) - I_{L}(k-1)$$

(17)

$$\begin{bmatrix} I_{Ld} \\ I_{Lq} \end{bmatrix} = \begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} I_{\alpha} \\ I_{\beta} \end{bmatrix}$$

(18)

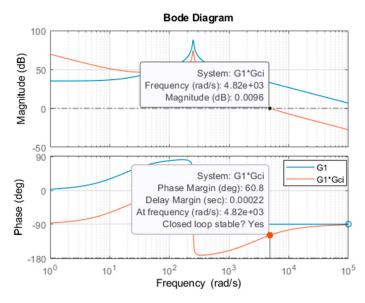

Current control is achieved through the use of an APF and DQ transformation. The design specifications for the current controller are set with a phase margin of 60 degrees and a bandwidth of 4800 [rad/s]. The transfer function of the designed current controller is expressed in Equation (19).

$$G_{ci} = 0.019522 \times \frac{s + 2690}{s} \tag{19}$$

The Bode plot for the current controller is presented in Figure 6. It can be observed from the plot that the phase margin is 60.8 degrees, and the bandwidth is 4820 [rad/s], meeting the specified design criteria. Therefore, the stability of the system can be confirmed through the Bode plot analysis.

Figure 6. TL PFC converter current controller Bode plot.

The MATLAB m-file, which was used in the controller design, is shown below:

```

s = tf('s');

Vin = 310;

L = 2.4 \times 10^{-3}; % L = 2.4 \text{ mh}

C = 2400 \times 10^{-6}; %C = 2400 \ \mu f

R = 50;

D = 0.311;

D1 = 1 - D;

Vc = Vin/D1;

IL = Vc/(R*D1);

G1 = (Vc/L)*(s + 1/(R*C) + (1 - D)*IL/(Vc*C))/(s^2 + s/(R*C) + (1 - D)^2/(L*C));

G2 = -Vin/(L^*C)^*(-1 + L^*s/(R^*(1-D)^2))/(s^2 + s/(R^*C) + (1-D)^2/(L^*C));

G3 = (IL/Vc)*(L/C)*(-s + (1-D)*Vc/(L*IL))/(s + 1/(R*C) + (1-D)*IL/(Vc*C));

Kpv = 1; Kiv = 1;

% temporarily set to 1

Gcv = Kpv*(s+Kiv)/s; %wc = 50 [rad/s], P.M = 90 [deg]

Kpi = 1; Kii = 1;

% temporarily set to 1

Gci = Kpi*(s + Kii)/s; %wc = 4800 [rad/s], P.M = 60 [deg]

```

```

Vref = Vin/D1; % sisotool\ Double-loop\ configuration T = sisoinit\ (6); T.F.Value = Vref; T.G1.Value = G1; % current\ loop\ G1 = (iL/d) T.C2.Value = Gci; % current\ controller\ PI = (d/ie) T.G2.Value = G3; % voltage\ loop\ tf. = (Vc/iL) % voltage\ controller\ PI = (Iref/Ve) voltage\ controller\ PI = (Iref/Ve)

```

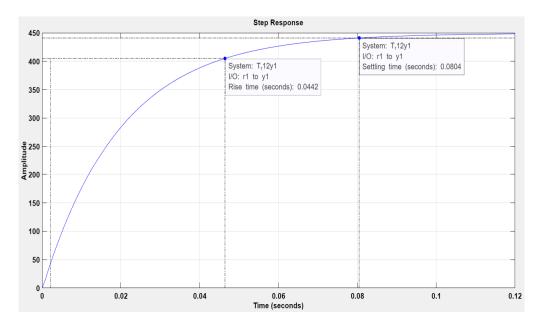

The MATLAB step response of the DC link voltage is depicted in Figure 7. As expected from the design requirements, the waveform of the DC link exhibits no overshoot. The rising time, defined as the time from 10% to 90% of the waveform, is measured as 0.0443 s, while the settling time is found to be 0.0812 s.

Figure 7. Voltage step response characteristics in MATLAB.

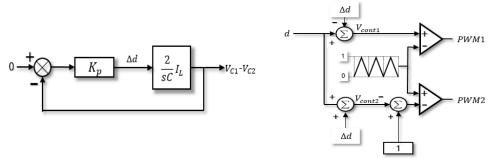

The capacitor balancing controller can be designed from the following equations:

$$i_{C1} = -\frac{v_{c1} + v_{c2}}{R} + i_L(1 - v_{cont1})$$

$$i_{C2} = -\frac{v_{c1} + v_{c2}}{R} + i_L(1 - v_{cont2})$$

(20)

From the above equations, the following relationship can be obtained:

$$i_{C1} - i_{C2} = i_L(v_{cont1} - v_{cont2}) = 2\Delta di_L$$

(21)

The capacitor voltage difference equation over duty difference can then be rewritten as follows:

$$G_{\Delta C} = \frac{\Delta v_c(s)}{\Delta d(s)} = \frac{2}{sC} i_L \tag{22}$$

where,  $\Delta v_c(s) = v_{c1} - v_{c2}$ .

The closed-loop transfer function of the capacitor voltage difference is given as follows:

$$\frac{\Delta v_c(s)}{\Delta v_{c_{ref}}(s)} = \frac{\frac{2k_p}{C}i_L}{s + \frac{2k_p}{C}i_L}$$

(23)

where,

$$\Delta v_{c_{ref}}(s) = 0$$

.

The controller configuration of the balancing controller is illustrated in Figure 8a, while its real implementation is depicted in Figure 8b. The controller gain  $K_p$  is set to 0.1 based on the design using MATLAB SISOTOOL.

(a) controller configuration

(b) structure of the balancing controller

Figure 8. Capacitor balancing controller.

#### 4. Simulation

The controller was designed using the parameter values shown in Table 2, and the controller design was verified by the PSIM simulation.

Table 2. Controller system parameter.

| Parameter                     | Value   |  |  |  |

|-------------------------------|---------|--|--|--|

| Input Voltage $(V_{in})$      | 310 V   |  |  |  |

| Output Voltage $(V_{dclink})$ | 450 V   |  |  |  |

| Inductance $(I_L)$            | 2.4 mH  |  |  |  |

| Capacitance $(C_1, C_2)$      | 2400 μF |  |  |  |

| Resistance ( <i>R</i> )       | 50 Ω    |  |  |  |

| Switching frequency $(f_s)$   | 20 KHz  |  |  |  |

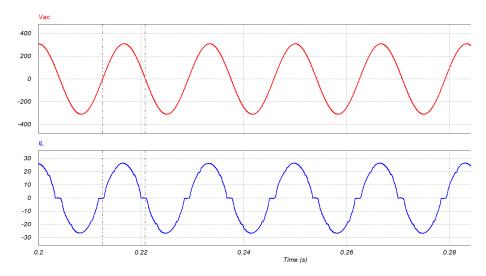

Figure 9 displays the waveforms of the AC input voltage and AC current from the double-loop controller. It is evident that the power factor (PF) was stably controlled at 0.9932, which is very close to unity.

Figure 9. The waveforms of the AC input voltage and AC current.

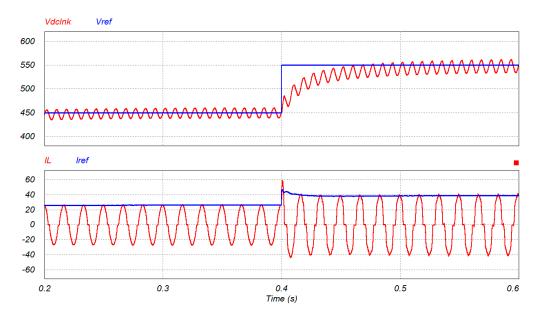

In Figure 10, the waveforms of the voltage step-up from 450 V to 550 V are presented. Both the output voltage and current are observed to be stably controlled in the boosting section. The actual voltage waveform closely matches the design requirements, except for the 120 Hz ripple components, as shown in Figure 10.

Figure 10. The waveforms of voltage step-up (PSIM simulation).

The control performance for the load variation is shown in Figure 11. This waveform demonstrates the control performance when the load resistance is changed from 25  $\Omega$  to 50  $\Omega$  and back. Comparing Figures 9 and 10 confirms that the control remains stable even after load changes.

Figure 11. TL PFC converter control performance waveform for load variation.

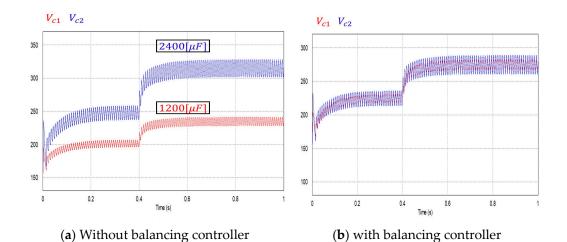

The waveforms of the balancing controller are depicted in Figure 12. Capacitors  $C_1$  and  $C_2$  are set to 1200 [ $\mu$ F] and 2400 [ $\mu$ F], respectively. The difference in capacitance results in a voltage difference between the capacitors, as shown in Figure 12a. This imbalance can be controlled using the balancing controller, the waveform of which is illustrated in Figure 12b.

Figure 12. The waveforms of the balancing controller.

#### 5. Experiments

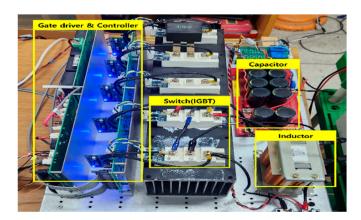

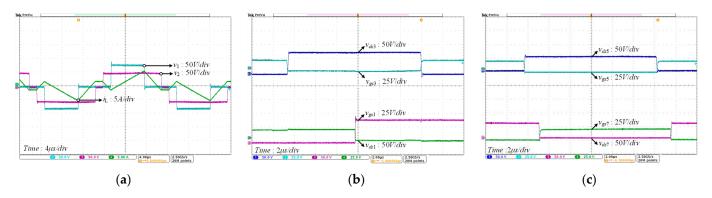

The hardware is constructed based on the simulation environment. The Texas Instruments' 320F28069 DSP is utilized for the micro-controller, and the circuit components used in the experiment are configured to match the values presented in Table 1. The detailed setup of the experiment is depicted in Figure 13. While single-phase AC power at 220 V is used in the PSIM simulation, due to limitations in the experimental system's power, a reduced voltage rating of 110 V is employed during the experiments.

Figure 13. Hardware setup used in the experiment.

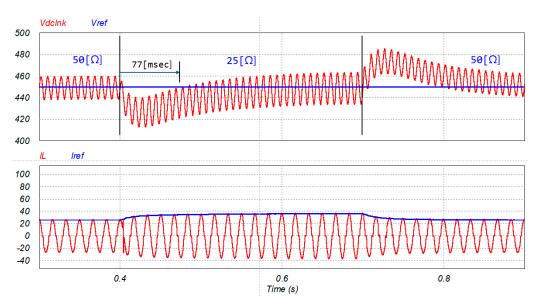

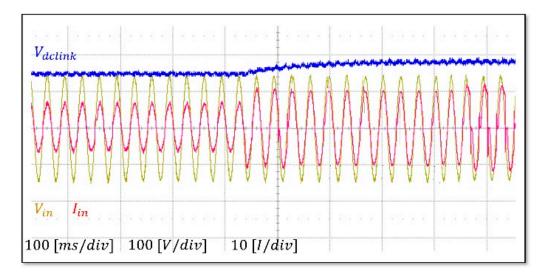

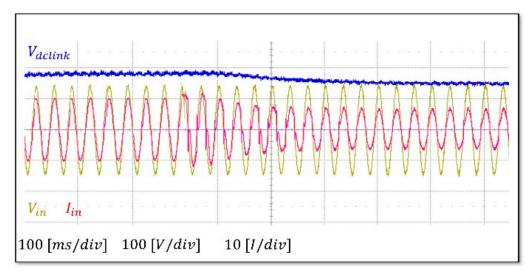

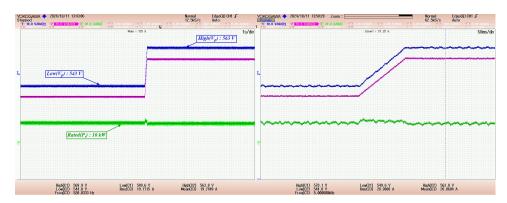

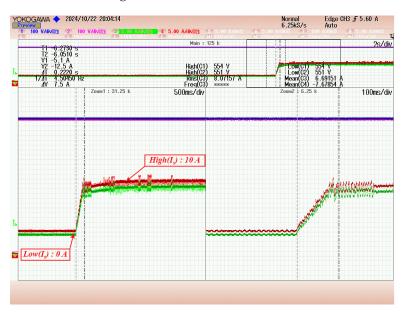

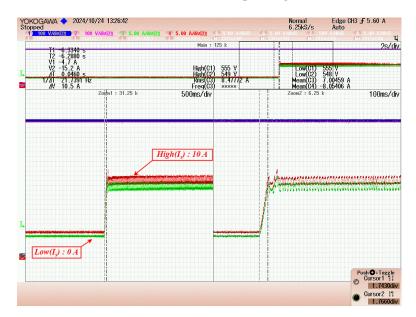

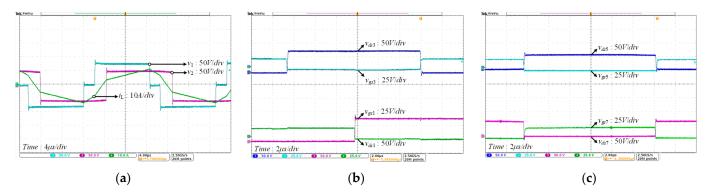

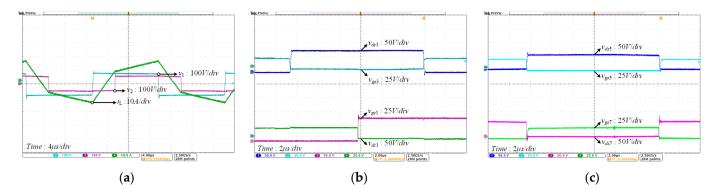

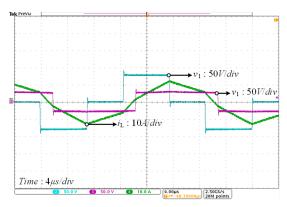

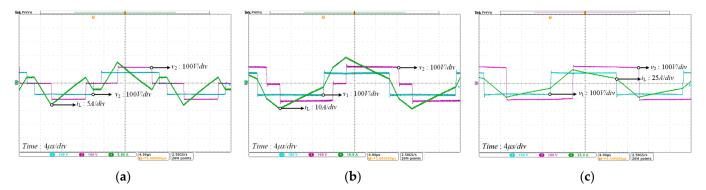

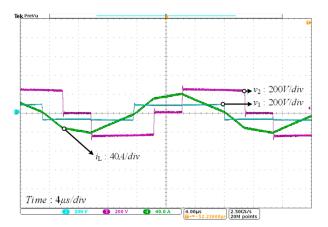

First, the step-up and step-down control for output voltage response characteristics are depicted in Figures 14 and 15, respectively. Figure 14 illustrates the result of boosting the output voltage from 150 V to 210 V, with both voltage and current stably controlled without overshoot. Similarly, Figure 15 displays the waveform resulting from stepping down the output voltage from 210 V to 150 V, where both voltage and current are observed to be stably controlled without overshoot.

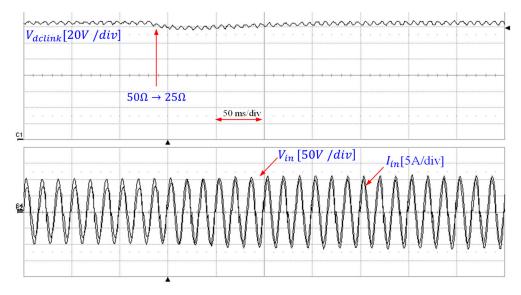

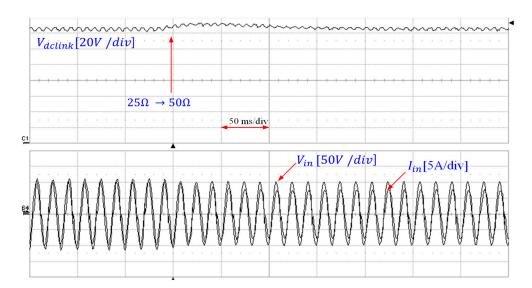

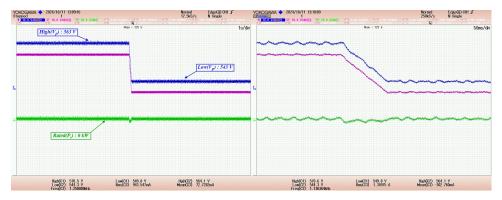

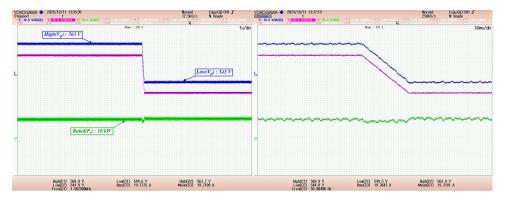

Figure 16 shows the waveform when changing the load resistance from 50  $\Omega$  to 25  $\Omega$ , and Figure 17 shows the waveform when changing it from 25  $\Omega$  to 50  $\Omega$ . In both cases, it was observed that the voltage was stably controlled. However, with regard to the current, fluctuations were initially observed, but the control stabilized within a short period of time.

The waveforms obtained through the actual experiment closely match the PSIM simulation results, confirming the theoretical validity of the proposed modeling and controller design through experimentation.

Figure 14. Voltage and current waveforms for reference voltage from  $150~\mathrm{V}$  to  $210~\mathrm{V}$ .

Figure 15. Voltage and current waveforms for reference voltage from 210 V to 150 V.

**Figure 16.** Waveforms for the load change (50 ightarrow 25 [ $\Omega$ ]).

**Figure 17.** Waveforms for the load change (25  $\rightarrow$  50 [ $\Omega$ ]).

#### 6. Conclusions

The paper proposes a double-loop controller design technique to enhance the modeling of a 3-level power factor correction (PFC) converter. The research aims to address challenges encountered in existing single-phase PFC circuits, particularly concerning the presence of a 120 Hz ripple voltage. Prior studies have not adequately addressed double-loop controller design or voltage ripple rejection in this context. Therefore, this paper presents a novel approach by applying a 3-level structure to achieve these goals.

The proposed technique involves configuring the obtained state space expression of the transfer function to be applicable across the full duty range. Subsequently, a double-loop controller is designed using MATLAB SISOTOOL. To evaluate the effectiveness of the proposed controller, verification is conducted through PSIM simulation. Moreover, the proposed controller is implemented in practice, and the efficacy of the system design is confirmed through experimental validation.

The primary contribution of this paper is demonstrating the controllability of the double-loop controller for a three-level PFC converter under varying operating points. This highlights the capability of the proposed controller to maintain operation across the entire duty cycle range, achieving unified control. This achievement distinguishes our work, as previous research has not explored this comprehensive aspect.

**Author Contributions:** Equally contributed. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was supported by "Regional Innovation Strategy (RIS)" through the National Research Foundation of Korea(NRF) funded by the Ministry of Education(MOE)(2021RIS-001). This work was supported by the Human Resources Development of the Korea Institute of Energy Technology Evaluation and Planning(KETEP) grant funded by the Korea government. (No. 20224000000070).

Data Availability Statement: Data are contained within the article.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Lee, K.-M.; Kim, I.-S. An Study on the Improved Modeling and Double-loop Controller Design for Three-Level Boost Converter. *Trans. Korean Inst. Power Electron.* **2020**, 25, 442–450.

- 2. Pahlevani, M.; Eren, S.; Bakhshai, A.; Jain, P. A DC-bus voltage control technique for grid-connected AC/DC converters used in smart energy storage units. In Proceedings of the 2015 IEEE 6th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aachen, Germany, 22–25 June 2015; pp. 1–7.

- 3. Lee, J.-Y.; Chae, H.-J. 6.6-kW Onboard Charger Design Using DCM PFC Converter With Harmonic Modulation Technique and Two-Stage DC/DC Converter. *IEEE Trans. Ind. Electron.* **2014**, *61*, 1243–1252. [CrossRef]

- 4. Ryan, R.T.; Hayes, J.G.; Morrison, R.; Hogan, D. Digital control of an interleaved BCM boost PFC converter with fast transient response at low input voltage. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017. [CrossRef]

- 5. Kim, J.-S.; Kang, J.-I.; Cho, J.-H.; Lee, J.-H.; Ahn, H.-M. DC-link voltage fluctuation compensating algorithm for PFC input voltage magnitude variation. *Power Electron. Conf.* **2023**, 465–466.

- 6. Ciobotaru, M.; Rossé, A.; Bede, L.; Karanayil, B.; Agelidis, V.G. Adaptive Notch Filter Based Active Damping for Power Converters Using LCL Filters. In Proceedings of the IEEE 7th International Symposium on Power Electronics for Distributed Generation Systems (PEDG'16), Vancouver, BC, Canada, 27–30 June 2016.

- 7. Yang, D.; Choi, D.; Shin, J.; Choi, B. Stability Analysis of Boost PFC Considering the External Impedance. *Power Electron. Conf.* **2023**, 255–257.

- 8. Jeong, S.-W.; Lim, J.-H.; Lee, D.-I.; Hyeon, Y.-J.; Lee, S.-Y.; Kim, W.-J.; Youn, H.-S. PFC DC/DC Integrated Converter for High Density of On-Board Charger. *Power Electron. Conf.* **2023**, 550–551.

- 9. Kim, S.-H.; Cha, H.-N.; Kim, H.-G.; Choi, B.-C. Clamp-mode Three-level High Voltage Gain Boost Converter using Coupled Inductor. *Trans. Korean Inst. Power Electron.* **2012**, *17*, 500–506. [CrossRef]

- 10. Barazarte, R.Y.; González, G.G. Design of a Two-Level Boost Converter. In Proceedings of the Eleventh LACCEI Latin Acmerican and Caribbean Conference for Engineering and Technology, Cancun, Mexico, 14–16 August 2013; pp. 1–8.

- 11. Kim, I.S. Power Conversion Controller Design (Using PSIM and MATLAB); Hongneung: Seoul, Republic of Korea, 2023.

- 12. Keskin, A.; Pal, K.; Hancioglu, E. Resistorless first-order all-pass filter with electronic tuning. *AEU Int. J. Electron. Commun.* **2008**, 62, 304–306. [CrossRef]

- 13. Song, M.-G.; Lee, W.-C. A Study on the DC-Link miniaturization and the Reduction of output current distortion rate by Reducing the Effect of 120Hz Ripple Voltage on Photovoltaic Systems. *Power Electron. Conf.* **2020**, 166–167.

- 14. Sim, W.; Jo, J.; Kim, Y.; Cha, H. Reactive power control of single-phase reactive power compensator for distribution line. *Trans. Korea Inst. Power Electron.* **2020**, *25*, 73–78.

- 15. Ben Haddi, S.; Zugari, A.; Zakriti, A.; Achraou, S. Design of a Band-Stop Planar Filter for Telecommunications Applications. *Procedia Manuf.* **2020**, *46*, 788–792. [CrossRef]

- 16. Zhang, R.; Cardinal, M.; Szczesny, P.; Dame, M. A grid simulator with control of single-phase power converters in D-Q rotating frame. In Proceedings of the 2002 IEEE 33rd Annual IEEE Power Electronics Specialists Conference, Cairns, Australia, 23–27 June 2002; pp. 1431–1436.

- 17. Park, H.C.; Kim, I.S. Optimal Gain Design Method of the 3 Phase Boost Converter. *Trans. Korean Inst. Power Electron.* **2017**, 22, 1–8. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Article

# Robust PI-PD Controller Design: Industrial Simulation Case Studies and a Real-Time Application

Fadi Alyoussef 1,\*, Ibrahim Kaya 2 and Ahmad Akrad 3

- <sup>1</sup> Institute of Natural and Applied Sciences, Dicle University, 21280 Diyarbakır, Turkey

- <sup>2</sup> Electrical and Electronics Engineering Department, Dicle University, 21280 Diyarbakır, Turkey; ikaya@dicle.edu.tr

- STACA'Lab, Ecole Supérieure des Techniques Aéronautiques et de Construction Automobile, 53000 Laval, France; ahmad.akrad@estaca.fr

- \* Correspondence: 16805505@ogr.dicle.edu.tr

Abstract: PI-PD controllers have superior performance compared to traditional PID controllers, especially for controlling unstable and integrating industrial processes with time delays. However, computing the four tuning parameters of this type of controller is not an easy task. Recently, there has been significant interest in determining the tuning rules for PI-PD controllers that utilize the stability region. Currently, most tuning rules for the PI-PD controller are presented graphically, which can be time-consuming and act as a barrier to their industrial application. There is a lack of analytical tuning guidelines in the literature to address this shortfall. However, the existing analytical tuning guidelines do not consider a rigorous design approach. This work proposes new robust analytical tuning criteria based on predefined gain and phase margin bounds, as well as the centroid of the stability region. The proposed method has been tested using various simulation studies related to a DC-DC buck converter, a DC motor, and a heat exchanger. The results indicate that the proposed tuning rules exhibit strong performance against parameter uncertainty with minimal overshoots. Furthermore, the suggested technique for simultaneous control of yaw and pitch angles has been tested in a real-time application using the twin rotor multi-input multi-output system (TRMS). Realtime results indicate that, compared to other methods under investigation, the suggested approach provides nearly minimal overshoots.

**Keywords:** PI-PD controller; stability region; robust control; centroid point; DC-DC buck converter; DC motor; heat exchanger; twin rotor multi-input multi-output system

#### 1. Introduction

The second order plus time delay (SOPTD) system representation is extensively utilized in the literature because it accurately represents the dynamics of numerous practical industrial applications such as temperature controllers and DC motors. However, long-time delays complicate such systems' control problems as these delays cause uncertainty and slow responses with larger overshoots. Further, the presence of poles on the right-hand side or at the origin of the s-plane adds another complexity to the control design problem. Thus, a robust control approach is required to regulate such systems [1].

PI-PD controllers are strong candidates relative to PID controllers to solve the control mentioned above difficulties [2]. They use the PD part in an inner feedback loop to shift the poles of a process to a more desirable location so that the PI part can control it more effectively in the forward path [3]. Compared to typical PI/PID controllers, PI-PD controllers perform better, especially when it comes to controlling unstable and integrated processes. They also provide the designer more flexibility to enhance closed-loop performance because PI-PD incorporates four adjustable parameters [4]. However, because four controller parameters need to be adjusted, constructing a PI-PD controller is a difficult task [5]. Only a few applications have made use of the PI-PD controller due to the difficulty of calculating

those four parameters [6]. In addition, compared to PID controllers, this controller's design has received comparatively less study attention [7]. Therefore, more research on this type of controller is still necessary.

Utilizing the stability region approach to calculate all stabilizing controller gains is a widely researched topic (see [8-11] for examples). Since it provides straightforward and useful tuning guidelines and gets around the challenge of tuning the PI-PD controller, many researchers have recently explored using the centroid point of the stability region, which can be calculated by using the centroid of convex stability region (CCSR) [12] or the weighted geometrical center (WGC) approaches [13,14], to adjust the parameters of PI-PD controllers. Additionally, it has been suggested that the controller evaluated using the centroid point may produce robustness against parameter fluctuations, faster perturbation rejection, and improved set-point tracking [15,16]. WGC and CCSR have just lately been used to graphically adjust the PID controller's gains, which are intended to control systems with non-integer order delay [17]. Additionally, a comparison study of the PI-PD controller tuning techniques employing CCSR and WGC has recently been conducted [14]. Because CCSR and WGC approaches have only been applied to specified transfer functions in the above-mentioned literature, they share the common drawback of requiring the design process to be repeated whenever the transfer function changes. This might be time-consuming for controller engineers and might require mathematical knowledge. The user-selected step size to be employed in the design phase causes a computational load, which is a unique drawback of the WGC approach [12]. Additionally, if the time lag is particularly significant, the WGC approach may yield an incorrect centroid location because of its sensitivity to the chosen step size [18]. The graphical way of determining the centroid location is a drawback unique to the CCSR approach [4]. Additionally, novel methods for determining a fractional order controller's stability region's centroid point have recently been introduced [19,20]. In addition, the centroid point has recently been used in the controller parameter design for DC-DC boost converters [21]. Nevertheless, the centroid point is still obtained graphically in all of the aforementioned stated approaches, which is laborious.

To remove the above-mentioned disadvantages of centroid point approaches, analytical tuning rules have been recently suggested [3,4,16,18,22]. However, these approaches have not considered incorporating a centroid point based on a robust design method. In fact, since the original work that formulated the stability region's formulas for time delay systems and PI-PD controllers, as documented in Ref. [23], the majority of researchers have tuned these controllers using graphical approaches without taking analytical ones into account. Furthermore, robust design techniques as previously discussed have not taken into account analytical methodologies. Therefore, the main goal of this paper is to design a robust tuning rule based on the centroid point, which can specifically withstand the system parameter uncertainties and provide acceptable settling times and overshoots. The primary contributions made by this work are:

- 1. Relative to the centroid point approaches reported in Refs. [3,4,16,18,22], the proposed method incorporates a robust design approach based on predefined gain and phase margin boundaries, which gives the designer more flexibility to obtain the desired control performances.

- 2. Relative to the centroid point approaches reported in Refs. [12,14,19,20], the proposed methods are analytical and not graphical, which saves time and is easy to implement on the industrial level.

- 3. Compared to the centroid point derived based on a robust design technique for DC–DC converter control published in Ref. [24], the suggested approach is analytical and does not call for any graphical adjustments. Furthermore, any system that can be represented as a stable SOPTD can use the suggested approach.

To conclude, proposing an analytical robust design method for designing the gains of the PI-PD controller is the main contribution of this paper. This is the layout for the rest of the paper. The next part explains the PI-PD controller structure. The suggested

methodology is expounded upon in Section 3. Section 4 describes the simulation and the real-time results. The last section deals with conclusions.

#### 2. PI-PD Controller Structure

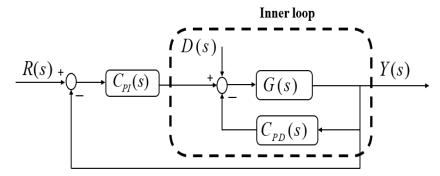

Every action taken by the PID regulator in a traditional closed-loop system occurs via the forward path. This can cause an unwanted occurrence known as a derivative kick. To solve this issue, the PD part of PI-PD regulators is moved to an internal feedback loop, which moves the poles of the plant transfer function to a more favorable location where the PI component operating in the onward path might more adequately control it [4,18]. The PI-PD regulator's architecture is shown in Figure 1. The inner loop is composed of the transfer functions of the plant, G(s), and the PD controller,  $C_{PD}(s)$ , whereas the external loop is composed of the transfer functions of the inner loop and the PI regulator,  $C_{PI}(s)$ . The transfer functions  $C_{PD}(s)$  and  $C_{PI}(s)$  of the PI-PD regulator are written as follows:

$$C_{PD}(\mathbf{s}) = k_f + k_d \mathbf{s} \tag{1}$$

$$C_{PI}(\mathbf{s}) = k_p + \frac{k_i}{s} \tag{2}$$

Figure 1. PI-PD controller.

The behavior of many industrial plants can be described as a second-order transfer function with time delays as follows:

$$G(s) = \frac{Ke^{-\tau s}}{as^2 + bs + c} \tag{3}$$

In the above equation, the time delay, the process gain, and the coefficients of the transfer function are  $\tau$ , K, a, b, and c, respectively.

#### 3. Proposed Approach

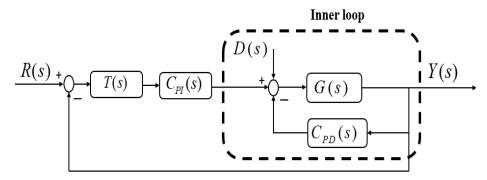

The gain-phase margin tester,  $T(s) = Ae^{-\phi s}$ , is added to the forward path to find boundaries in the general stability boundary corresponding to the predetermined gain and phase margins. Figure 2 shows the structure of the PI-PD controller after adding the tester [23].

The following closed-loop characteristic equation can be used to characterize the inner feedback loop shown in Figure 2, which is made up of the PD controller transfer function,  $C_{PD}(s)$ , and the process transfer functions, G(s):

$$\Delta(s) = 1 + C_{PD}(s)G(s) \Rightarrow \Delta(s) = k_f K e^{-\tau s} + k_d K s e^{-\tau s} + a s^2 + b s + c \tag{4}$$

In the parameter space methodology, the root of a stable polynomial has three ways of crossing over the imaginary axis and becoming unstable. The real root boundary, the infinite root boundary, and the complex root boundary are the three boundaries that these ways define [4]. To find the real root boundary, we solve Equation (4) with s=0 and  $\Delta(s)=0$ . Therefore,  $k_f=-c/K$  defines the boundary. Since the controller parameters are

absent from the coefficient of  $s^2$ , the infinite root boundary cannot be part of the stability region. To find the complex root boundary, we enter  $s=j\omega$ ,  $e^{-j\tau\omega}=\cos(\tau\omega)-j\sin(\tau\omega)$ , and  $j=\sqrt{-1}$  into Equation (4) as given below:

$$\Delta(s) = -a\omega^2 + jb\omega + c + k_f K \cos(\tau\omega) - jk_f K \sin(\tau\omega) + jk_d K\omega \cos(\tau\omega) + k_d K\omega \sin(\tau\omega) = 0$$

(5)

Figure 2. PI-PD controller plus gain-phase margin tester.

The imaginary and real components in Equation (5) are then split and equaled to zero. Consequently, the following equations can be obtained:

$$k_d(\omega\cos(\tau\omega)) - k_f(\sin(\tau\omega)) = -\frac{b}{K}\omega \tag{6}$$

$$k_d(\omega \sin(\tau \omega)) + k_f(\cos(\tau \omega)) = \frac{a\omega^2 - c}{K}$$

(7)

The expressions that follow can be obtained by solving Equations (6) and (7) for  $k_d$  and  $k_f$ :

$$k_d = \frac{1}{K} \left( -b\cos(\tau\omega) + (a\omega - \frac{c}{\omega})\sin(\tau\omega) \right)$$

(8)

$$k_f = \frac{1}{K} \Big( (a\omega^2 - c)\cos(\tau\omega) + b\omega\sin(\tau\omega) \Big)$$

(9)

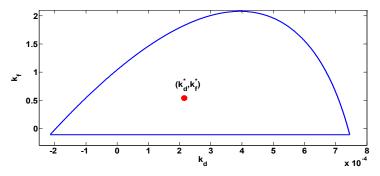

The inner feedback loop's stability region is defined by Equations (8) and (9) and the line  $k_f = -c/K$ . By varying  $\omega$  throughout the range of  $[\varepsilon \ \omega_{PD}]$ , Equations (8) and (9) are utilized to construct the stability region.  $\varepsilon$  is a small number that is used to avoid dividing by zero in Equation (8), while  $\omega_{PD}$  is found by taking the first root of the equation:  $(a\omega^2 - c)\cos(\tau\omega) + b\omega\sin(\tau\omega) = -c$ . The adjusting point of the PD controller can be found using the mathematical relations in the range of  $[e \ f]$  [18]:

$$\overline{x} = \frac{1}{f - e} \int_{e}^{f} z(x) dx \tag{10}$$

$$\overline{y} = \frac{1}{2(f-e)} \int_{e}^{f} g(x)dx \tag{11}$$

The integrations provided in Equations (10) and (11) should be used to analytically calculate the settings of the PD controller. Also, the same mathematical relations will be used later for finding the settings of the PI controller. Considering  $f = \omega_{PD}$ , e = 0, and  $z(x) = k_d$  which is given in Equation (8), and  $g(x) = k_f$  which is given in Equation (9), the gains of the PD controller are analytically computed using Equations (10) and (11). Thus, the following expressions are obtained and used to find the setting of this controller:

$$k_d^* = \frac{1}{K\omega_{PD}} \left( \frac{a(\sin(\tau\omega_{PD}) - \tau\omega_{PD}\cos(\tau\omega_{PD}))}{\tau^2} - \frac{b\sin(\tau\omega_{PD})}{\tau} - c\left(\frac{\tau^6\omega_{PD}^5}{600} - \frac{\tau^4\omega_{PD}^3}{18} + \tau^2\omega_{PD}\right) \right)$$

(12)

$$k_f^* = \frac{1}{2K\omega_{PD}} \begin{pmatrix} \frac{b(\sin(\tau\omega_{PD}) - \tau\omega_{PD}\cos(\tau\omega_{PD}))}{\tau^2} + \frac{1}{(\tau^2(a\omega_{PD}^2 - c) - 2a)\sin(\tau\omega_{PD}) + 2a\tau\omega_{PD}\cos(\tau\omega_{PD})}{\tau^3} \end{pmatrix}$$

(13)

Here, it is important to illustrate that the first three terms of the Taylor series are used for approximation  $\frac{\tau \sin(\tau \omega)}{\tau \omega}$  and consequently achieving the integration action in Equation (13). The first three terms of the Taylor series are selected as they can provide good computation accuracy without introducing mathematical complexity. To compute the controller parameters using Equations (12) and (13), one should first identify the parameters of the SOPTD system reported in Equation (3). After that,  $\omega_{PD}$  should be computed by taking the first root of the equation:  $(a\omega^2 - c)\cos(\tau\omega) + b\omega\sin(\tau\omega) = -c$ . This can be achieved by using a scientific package such as MATLAB.

To find the PI controller parameters  $k_i$  and  $k_p$ , the outer loop's characteristic equation is given below:

$$\Delta(s) = \begin{pmatrix} 1 + G_{PD}(s)G(s) + Ae^{-j\phi}G_{PI}(s)G(s) = \\ as^3 + bs^2 + cs + AKk_pse^{-j(\tau\omega+\phi)} + AKk_ie^{-j(\tau\omega+\phi)} + Kk_fse^{-\tau s} + Kk_ds^2e^{-\tau s} \end{pmatrix}$$

(14)

Afterward, the real root boundary, the infinite root boundary, and the complex root boundary are determined. For the outer loop, the real root boundary is found by solving Equation (14) for s=0 and  $\Delta(s)=0$ . Thus, this boundary is defined by  $k_i=0$ . The infinite root boundary cannot be a component of the stability zone since the controller's settings are missing from the coefficient of  $s^3$ . The complex root boundary is found by entering  $s=j\omega$ ,  $e^{-j\tau\omega}=\cos(\tau\omega)-j\sin(\tau\omega)$ ,  $e^{-j\phi}=\cos(\phi)-j\sin(\phi)$ , and  $j=\sqrt{-1}$  into Equation (14). After that, imaginary and real components are split to obtain the following equations:

$$k_p(\omega\sin(\tau\omega+\phi)) + k_i(\cos(\tau\omega+\phi)) = \frac{b}{AK}\omega^2 - \frac{k_f^*}{A}\omega\sin(\tau\omega) + \frac{k_d^*}{A}\omega^2\cos(\tau\omega)$$

(15)

$$k_p(\omega\cos(\tau\omega+\phi)) - k_i(\sin(\tau\omega+\phi)) = \frac{a}{AK}\omega^3 - \frac{c}{AK}\omega - \frac{k_f^*}{A}\omega\cos(\tau\omega) - \frac{k_d^*}{A}\omega^2\sin(\tau\omega)$$

(16)

The complex root boundary's equations are given by solving Equations (15) and (16) for  $k_p$  and  $k_i$  as follows:

$$k_{p} = \begin{pmatrix} \frac{b}{AK}\omega^{2}\cos(\tau\omega + \phi) + \frac{b}{AK}\omega\sin(\tau\omega + \phi) - \frac{k_{f}^{*}}{A} + \sin(\tau\omega)\sin(\tau\omega + \phi) \\ -\frac{k_{f}^{*}}{A}\cos(\tau\omega)\cos(\tau\omega + \phi) + \frac{k_{d}}{A}\omega\cos(\tau\omega)\sin(\tau\omega + \phi) - \frac{k_{d}^{*}}{A}\omega\sin(\tau\omega)\cos(\tau\omega + \phi) \\ -\frac{c}{AK}\cos(\tau\omega + \phi) \end{pmatrix}$$

(17)

$$k_{i} = \begin{pmatrix} -\frac{a}{AK}\omega^{3}\sin(\tau\omega + \phi) + \frac{c}{AK}\omega\sin(\tau\omega + \phi) + \frac{b}{AK}\omega^{2}\cos(\tau\omega + \phi) \\ +\frac{k_{f}}{A}\omega\cos(\tau\omega)\sin(\tau\omega + \phi) - \frac{k_{f}}{A}\omega\sin(\tau\omega)\cos(\tau\omega + \phi) + \frac{k_{d}}{A}\omega^{2}\sin(\tau\omega)\sin(\tau\omega + \phi) \\ +\frac{k_{d}}{A}\omega^{2}\cos(\tau\omega)\cos(\tau\omega + \phi) \end{pmatrix}$$

(18)

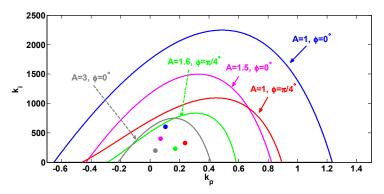

The line  $k_i=0$  and Equations (17) and (18) are used to determine the stability region of the outer loop. To plot Equations (17) and (18),  $\omega$  is changed throughout the range of  $\begin{bmatrix} 0 & \omega_{PI} \end{bmatrix}$ , where  $\omega_{PI}$  is found by equating Equation (18) to zero and taking the first solution. After applying the formulae from Equations (10) and (11) to Equations (17) and (18), correspondingly, the settings of the PI controller are determined as follows:

$$k_{p}^{*} = \frac{1}{\omega_{PI}} \left( \frac{(2a\tau^{2}\omega_{PI}^{2} - 2c\tau^{2} + 2b\tau - 4a)\sin(\tau\omega_{PI} + \phi) + (4a\tau - 2b\tau^{2})\omega_{PI}\cos(\tau\omega_{PI} + \phi)}{2AK\tau^{3}} + \frac{(2c\tau^{2} - 2b\tau + 4a)\sin(\phi)}{2AK\tau^{3}} + \frac{(2c\tau^{2} - 2b\tau + 4a)\sin(\phi)}{2AK\tau^{3}} \right)$$

(19)

$$k_{i}^{*} = \frac{1}{2\omega_{PI}} \begin{pmatrix}

\frac{\left(\left(6b\tau^{3} - 18a\tau^{2}\right)\omega_{PI}^{2} + 6c\tau^{2} - 12b\tau + 36a\right)\sin(\tau\omega_{PI} + \phi)}{6AK\tau^{4}} \\

+ \frac{\left(6a\tau^{3}\omega_{PI}^{3} + \left(-6c\omega_{PI}\tau^{3} + 12b\tau^{2} - 36a\tau\right)\omega_{PI}\right)\cos(\tau\omega_{PI} + \phi)}{6AK\tau^{4}} \\

+ \frac{2Kk_{d}\tau^{4}\cos(\phi)\omega_{PI}^{3} + 3Kk_{f}\tau^{4}\sin(\phi)\omega_{PI}^{2}}{6AK\tau^{4}} - \frac{\left(6c\tau^{2} - 12b\tau + 36a\right)\sin(\phi)}{6AK\tau^{4}}

\end{pmatrix}$$

(20)

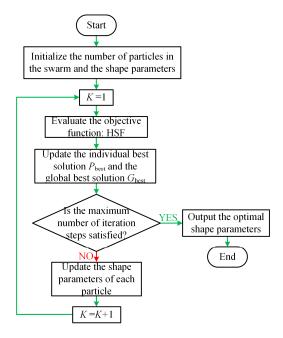

One can find the controller parameters using the flowchart shown in Figure 3. Here, it is important to mention that no approximations have been used to find Equations (19) and (20).

Find the parameters of the system given in equation (3). Real-time input and output data, along with a scientific identification toolbox like the MATLAB toolbox, can be used for this purpose.

Find  $\omega_{PD}$  by taking the first root of the equation:  $(a\omega^2 - c)\cos(\tau\omega) + b\omega\sin(\tau\omega) = -c$ The sloution of the above equaiton can be found by using a scientific package such as MATLAB

Compute the PD controller parameters using equations (12) and (13)

$\omega_{PI}$  is found by equating equation (18) to zero and taking the first solution. This can be done also using MATLAB

Compute the PI controller parameters using equations (19) and (20) based on predefined gain and phase margin boundaries

Figure 3. The flowchart for finding the PI-PD parameters using the proposed method.

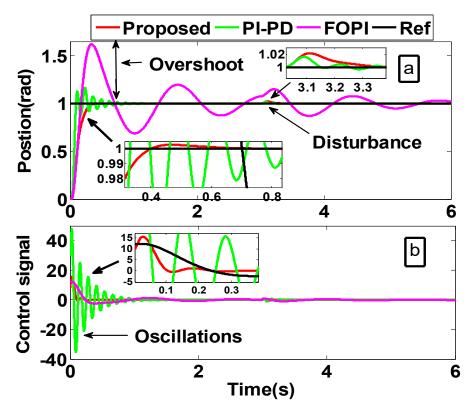

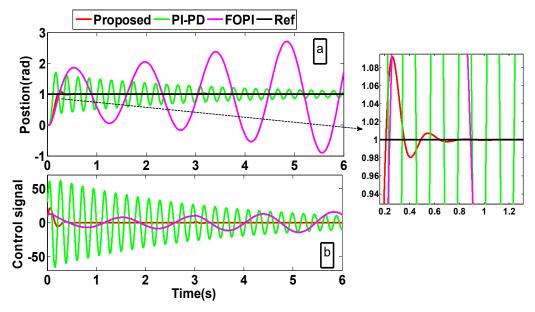

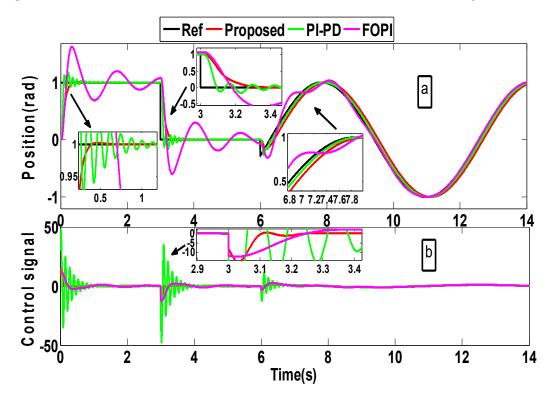

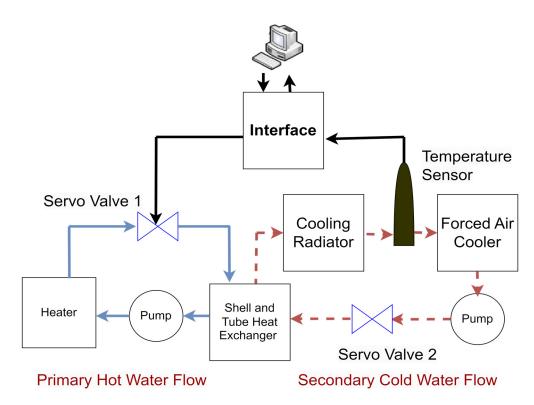

#### 4. Simulation and Real-Time Case Studies