Journal of

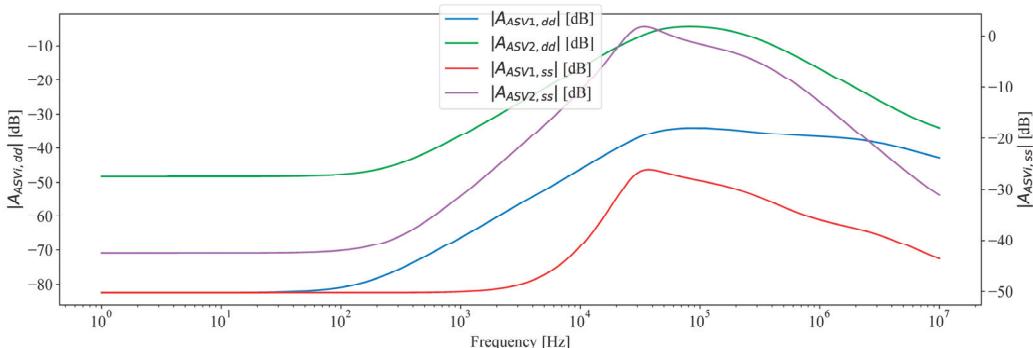

*Low Power Electronics

and Applications*

Special Issue Reprint

---

# Ultra-Low-Power ICs for the Internet of Things (2nd Edition)

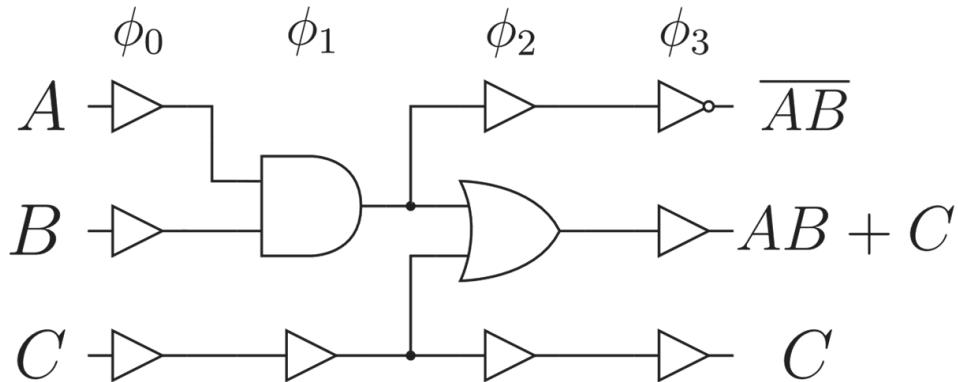

---

Edited by

Orazio Aiello

[mdpi.com/journal/jlpea](http://mdpi.com/journal/jlpea)

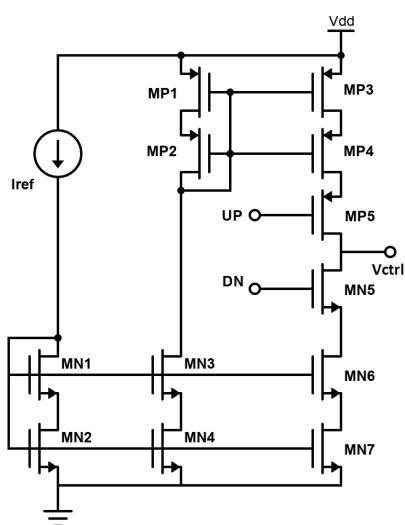

# **Ultra-Low-Power ICs for the Internet of Things (2nd Edition)**

# Ultra-Low-Power ICs for the Internet of Things (2nd Edition)

Guest Editor

**Orazio Aiello**

Basel • Beijing • Wuhan • Barcelona • Belgrade • Novi Sad • Cluj • Manchester

*Guest Editor*

Orazio Aiello

Department of Electrical,

Electronic,

Telecommunications

Engineering and Naval

Architecture (DITEN)

University of Genoa

Genova

Italy

*Editorial Office*

MDPI AG

Grosspeteranlage 5

4052 Basel, Switzerland

This is a reprint of the Special Issue, published open access by the journal *Journal of Low Power Electronics and Applications* (ISSN 2079-9268), freely accessible at: [https://www.mdpi.com/journal/jlpea/special\\_issues/919Q5756T0](https://www.mdpi.com/journal/jlpea/special_issues/919Q5756T0).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

Lastname, A.A.; Lastname, B.B. Article Title. *Journal Name Year, Volume Number, Page Range.*

**ISBN 978-3-7258-6734-9 (Hbk)**

**ISBN 978-3-7258-6735-6 (PDF)**

<https://doi.org/10.3390/books978-3-7258-6735-6>

© 2026 by the authors. Articles in this reprint are Open Access and distributed under the Creative Commons Attribution (CC BY) license. The reprint as a whole is distributed by MDPI under the terms and conditions of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) license (<https://creativecommons.org/licenses/by-nc-nd/4.0/>).

# Contents

|                                                                                                                                                                                                        |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>About the Editor</b>                                                                                                                                                                                | <b>vii</b> |

| <b>Orazio Aiello</b>                                                                                                                                                                                   |            |

| Ultra-Low-Power ICs for the Internet of Things (2nd Edition)                                                                                                                                           |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2025</b> , <i>15</i> , 59,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea15040059">https://doi.org/10.3390/jlpea15040059</a>                                                                                                              | <b>1</b>   |

| <b>Xuan Phuong Tran, Xuan Thuc Kieu, Xuan Thanh Pham, Duy Phong Pham and Manh Kha Hoang</b>                                                                                                            |            |

| A 1.87 $\mu$ W Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8 $\text{G}\Omega$ Input Impedance for Biomedical Recording                                 |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 37,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea14030037">https://doi.org/10.3390/jlpea14030037</a>                                                                                                              | <b>4</b>   |

| <b>Xuan Thanh Pham, Xuan Thuc Kieu and Manh Kha Hoang</b>                                                                                                                                              |            |

| Ultra-Low Power Programmable Bandwidth Capacitively-Coupled Chopper Instrumentation Amplifier Using 0.2 V Supply for Biomedical Applications                                                           |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2023</b> , <i>13</i> , 37,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea13020037">https://doi.org/10.3390/jlpea13020037</a>                                                                                                              | <b>18</b>  |

| <b>Ali Namdari, Orazio Aiello and Daniele D. Caviglia</b>                                                                                                                                              |            |

| A 0.5 V, 32 nW Compact Inverter-Based All-Filtering Response Modes Gm-C Filter for Bio-Signal Processing                                                                                               |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 40,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea14030040">https://doi.org/10.3390/jlpea14030040</a>                                                                                                              | <b>30</b>  |

| <b>Giovanni Nicolini, Alessandro Fava, Francesco Centurelli, Giuseppe Scotti</b>                                                                                                                       |            |

| A 0.064 mm <sup>2</sup> 16-Channel In-Pixel Neural Front End with Improved System Common-Mode Rejection Exploiting a Current-Mode Summing Approach                                                     |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 38,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea14030038">https://doi.org/10.3390/jlpea14030038</a>                                                                                                              | <b>47</b>  |

| <b>Siqi Wang, Zhenghao Lu, Kunpeng Xu, Hongguang Dai, Zhanxia Wu and Xiaopeng Yu</b>                                                                                                                   |            |

| A Sub-1-V Nanopower MOS-Only Voltage Reference                                                                                                                                                         |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 13,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea14010013">https://doi.org/10.3390/jlpea14010013</a>                                                                                                              | <b>67</b>  |

| <b>William Morell and Jin-Woo Choi</b>                                                                                                                                                                 |            |

| Design and Analysis of Self-Tanked Stepwise Charging Circuit for Four-Phase Adiabatic Logic                                                                                                            |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 34,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea14030034">https://doi.org/10.3390/jlpea14030034</a>                                                                                                              | <b>84</b>  |

| <b>Muhammad Omer Shah, Manfredi Caruso and Salvatore Pennisi</b>                                                                                                                                       |            |

| 0.35 V Subthreshold Bulk-Driven CMOS Second-Generation Current Conveyor                                                                                                                                |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 36,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea14030036">https://doi.org/10.3390/jlpea14030036</a>                                                                                                              | <b>94</b>  |

| <b>Riccardo Della Sala, Francesco Centurelli, Giuseppe Scotti</b>                                                                                                                                      |            |

| An Ultra-Low-Voltage Approach to Accurately Set the Quiescent Current of Digital Standard Cells Used for Analog Design and Its Application on an Inverter-Based Operational Transconductance Amplifier |            |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 39,                                                                                                                      |            |

| <a href="https://doi.org/10.3390/jlpea14030039">https://doi.org/10.3390/jlpea14030039</a>                                                                                                              | <b>106</b> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

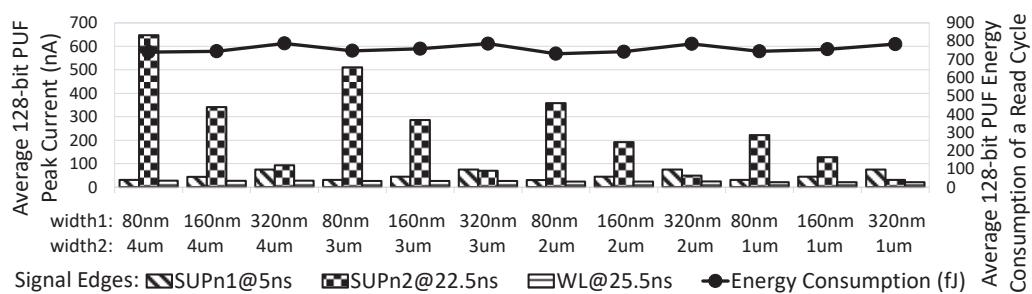

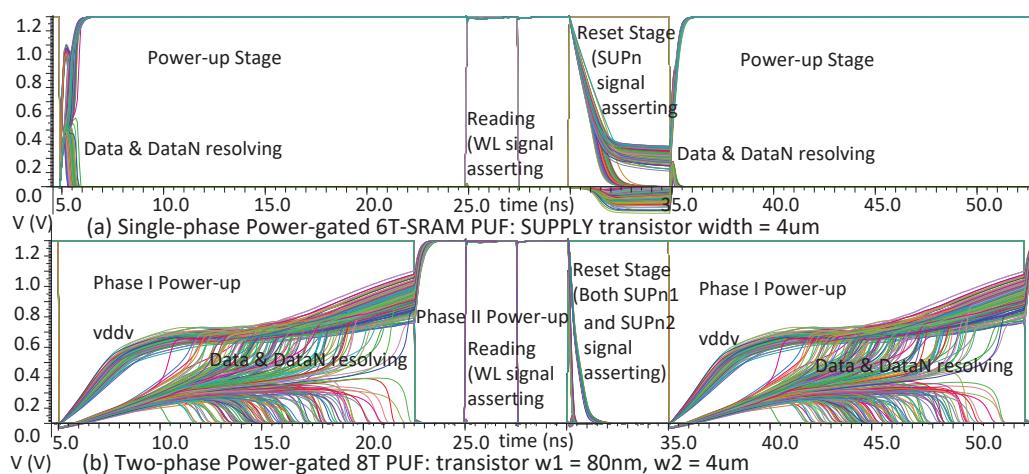

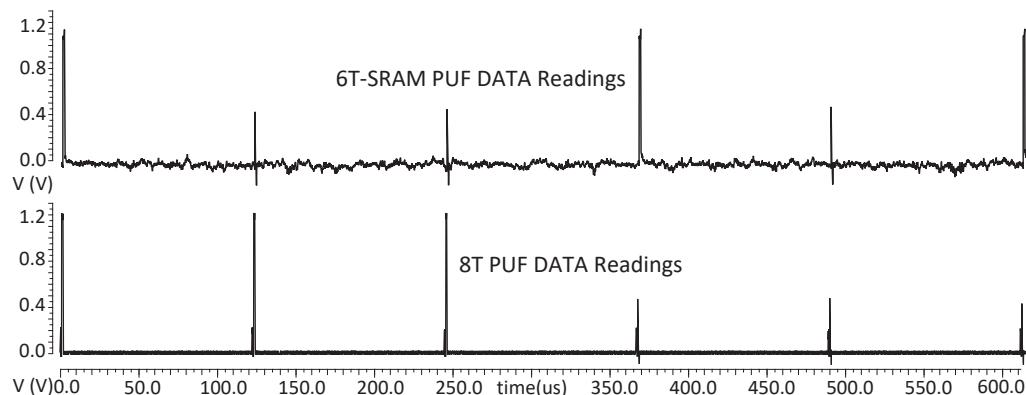

| <b>Yujin Zheng, Alex Yakovlev and Alex Bystrov</b><br>A Power-Gated 8-Transistor Physically Unclonable Function Accelerates Evaluation Speeds<br>Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2023</b> , <i>13</i> , 53,<br><a href="https://doi.org/10.3390/jlpea13040053">https://doi.org/10.3390/jlpea13040053</a> . . . . .                                                                                                              | <b>120</b> |

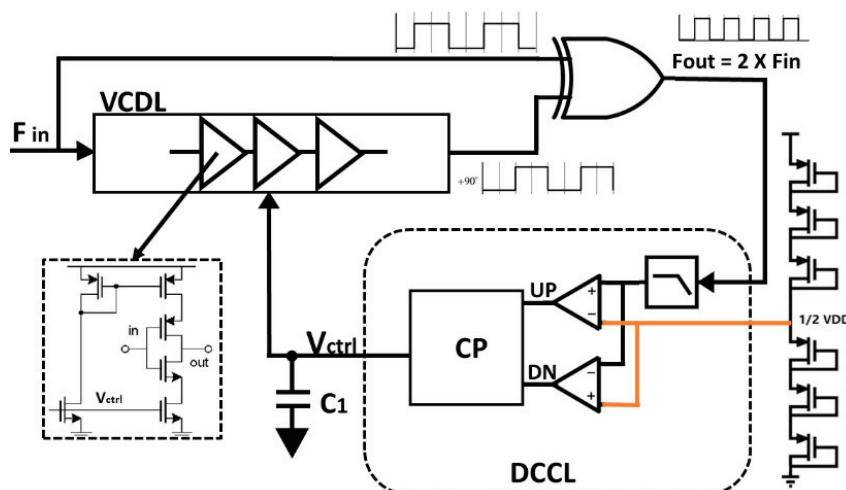

| <b>Naveed and Jeff Dix</b><br>Design of a Low-Power Delay-Locked Loop-Based 8 $\times$ Frequency Multiplier in 22 nm FDSOI<br>Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2023</b> , <i>13</i> , 64,<br><a href="https://doi.org/10.3390/jlpea13040064">https://doi.org/10.3390/jlpea13040064</a> . . . . .                                                                                                                                 | <b>135</b> |

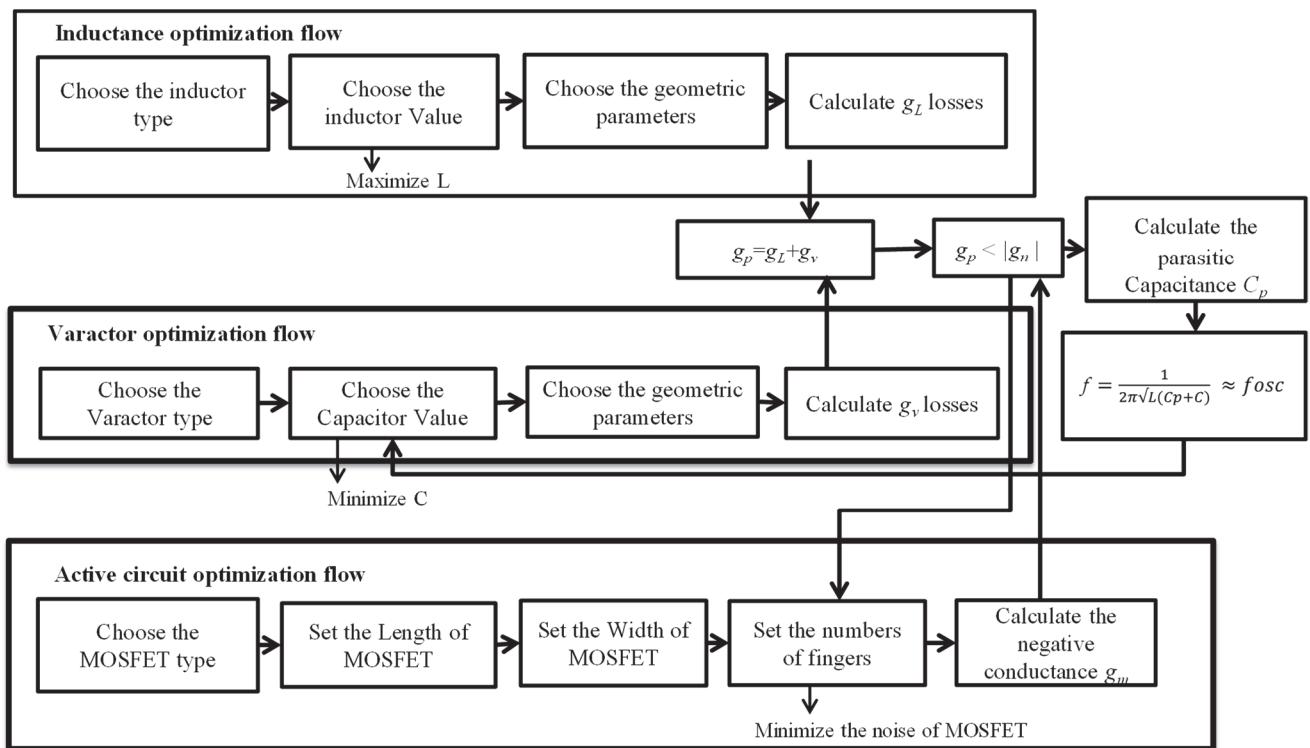

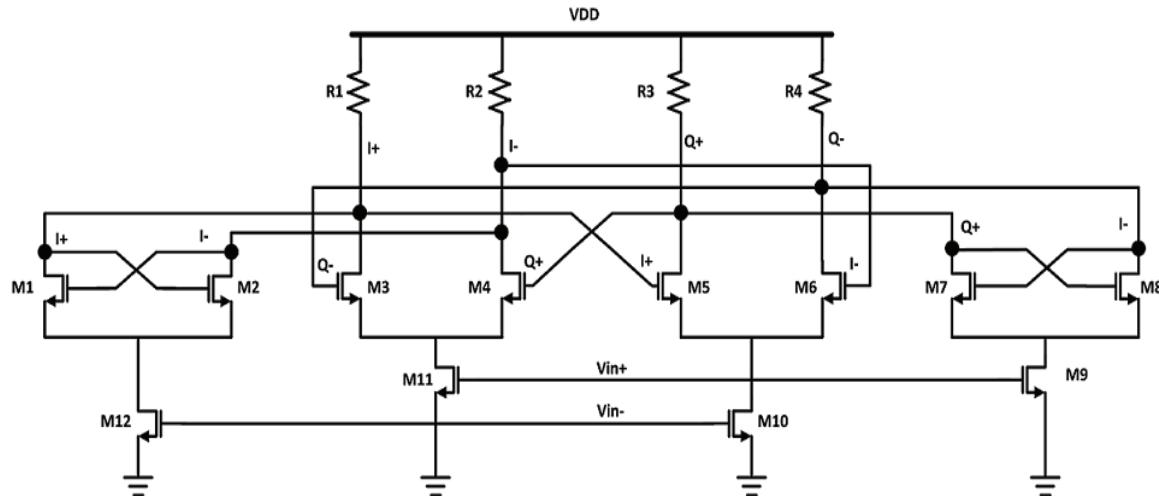

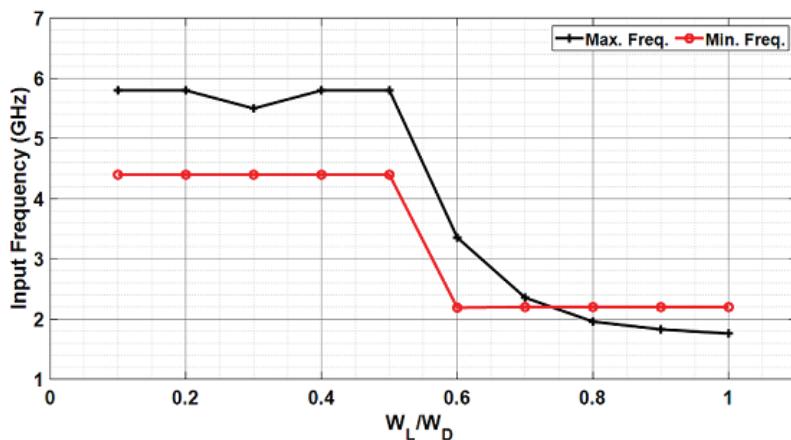

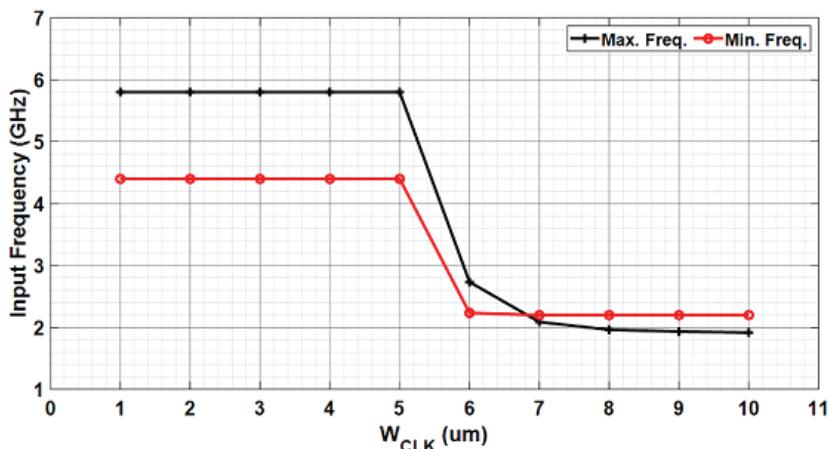

| <b>Muhammad Faisal Siddiqui, Mukesh Kumar Maheshwari, Muhammad Raza and Aurangzeb Rashid Masud</b><br>Design and Optimization of an Ultra-Low-Power Cross-Coupled LC VCO with a DFF Frequency Divider for 2.4 GHz RF Receivers Using 65 nm CMOS Technology<br>Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2023</b> , <i>13</i> , 54,<br><a href="https://doi.org/10.3390/jlpea13040054">https://doi.org/10.3390/jlpea13040054</a> . . . . . | <b>144</b> |

| <b>Billy Baker, John Woods, Martin J. Reed and Martin Afford</b><br>A Survey of Short-Range Wireless Communication for Ultra-Low-Power Embedded Systems<br>Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2024</b> , <i>14</i> , 27,<br><a href="https://doi.org/10.3390/jlpea14020027">https://doi.org/10.3390/jlpea14020027</a> . . . . .                                                                                                    | <b>165</b> |

# About the Editor

## **Orazio Aiello**

Orazio Aiello received a B.Sc. and M.Sc. (cum laude) from the University of Catania, Italy, in 2005 and 2008, respectively; an M.Sc. (cum laude) from the Scuola Superiore di Catania, Italy, in 2009; and a Ph.D. from the Politecnico di Torino, Italy, in 2013. He gained his technical background in worldwide universities' R&D institutions, as well as through consultant activities and direct work experience in semiconductor companies. He is currently an Associate Professor at the University of Genoa, Italy. His main research interests include energy-efficient analog mixed-signal circuits and sensor interfaces.

Editorial

## Ultra-Low-Power ICs for the Internet of Things (2nd Edition)

Orazio Aiello

Department of Electrical, Electronics and Telecommunication Engineering and Naval Architecture (DITEN), University of Genoa, 16100 Genova, Italy; orazio.aiello@unige.it

After the success of the first edition [1], we are delighted to launch this second edition of our Special Issue focusing on Ultra-Low-Power (ULP) Integrated Circuits (ICs) operating within a tight power budget, which represent an essential element in building electronic devices that rely less and less on batteries. Our aim is, once again, to present novel IC design strategies to reduce the cost and power consumption of devices.

In this Special Issue, Tran et al., Pham et al., and Namdari et al. (Contributions 1–3) discuss IC solutions for biomedical applications. In particular, two capacitively coupled chopper instrumentation amplifiers (CCIAs) are presented as part of a 180 nm technology process for monitoring neural potentials. Tran et al. present a chopping ripple reduction to 0.36 mV, with an overall area of 0.123 mm<sup>2</sup> and a power consumption of 1.87 μW at a supply voltage of 1 V. Pham et al. show a programmable bandwidth from 0.2 to 10 kHz in an area of 0.083 mm<sup>2</sup> and an overall power consumption of 0.47 μW with two supply voltages at 0.2 V and 0.8 V.

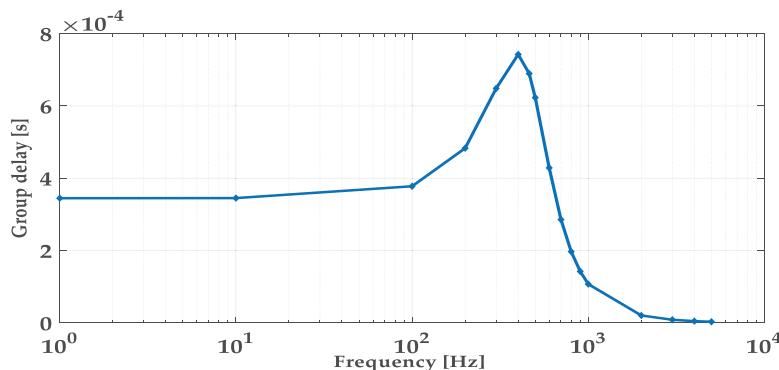

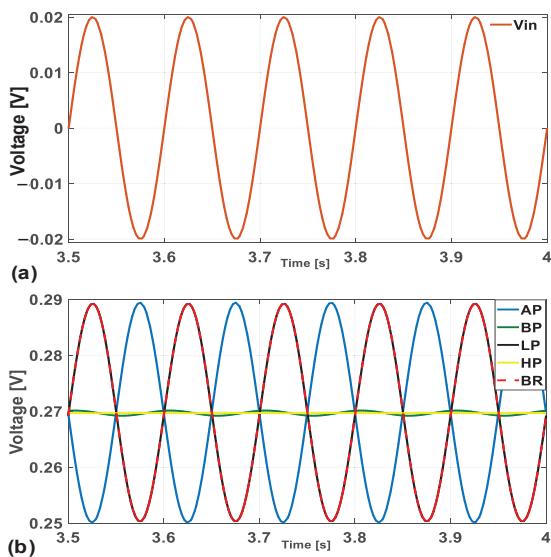

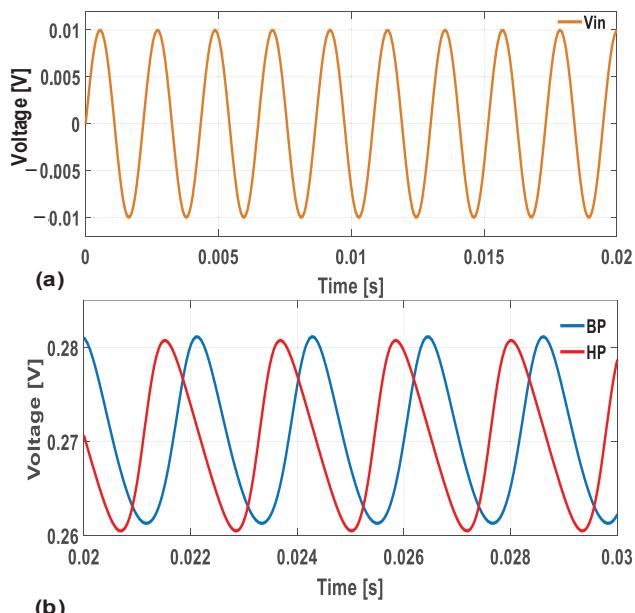

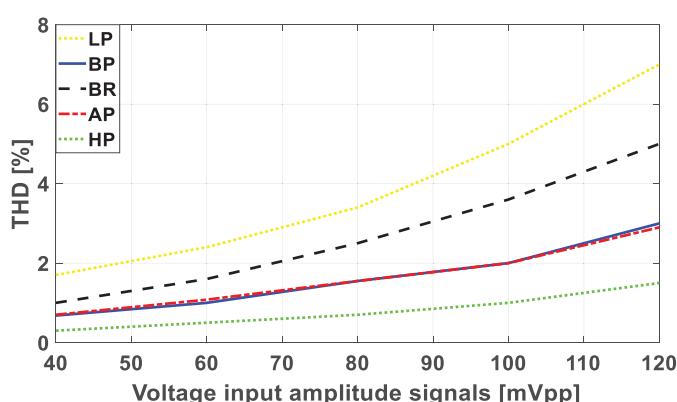

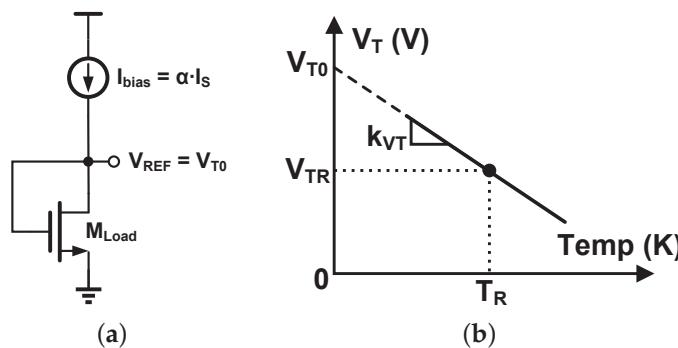

A compact, universal, multi-mode Gm-C filter centered at 462 Hz using a 180 nm, with a supply voltage of 0.5 V, resulting in a power consumption of 32 nW, is reported in the work by Namdari et al. (Contribution 3). The work by Nicolini et al. (Contribution 4) presents a 16-channel in-pixel neural analog front end, enhancing both the system common-mode rejection ratio (SCMRR) and the common-mode interference (CMI) range with a power consumption of 3.77 μW per channel in 180 nm technology nodes.

This Special Issue then addresses general-purpose IC blocks (i.e., Contributions 5–8).

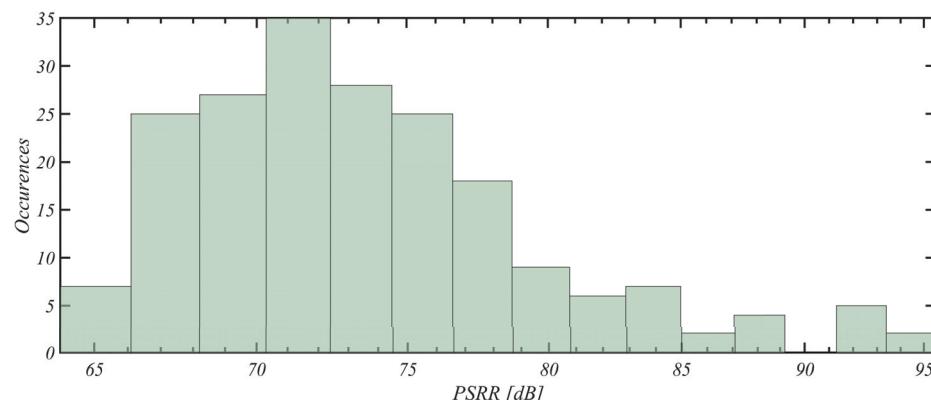

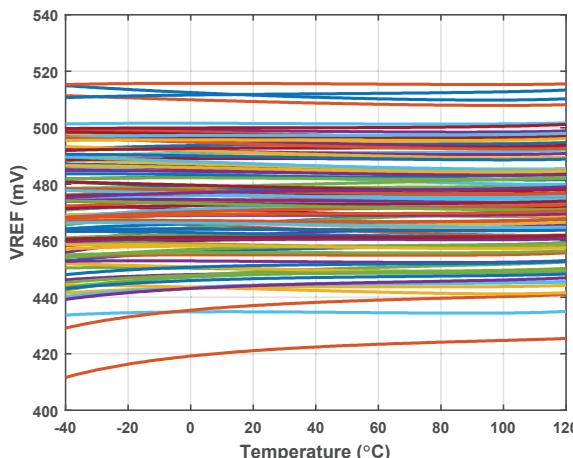

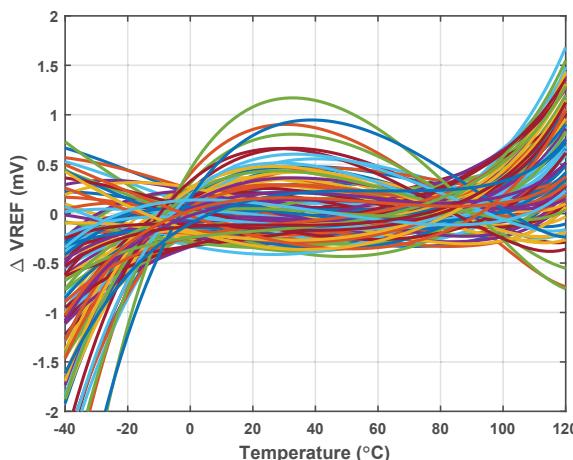

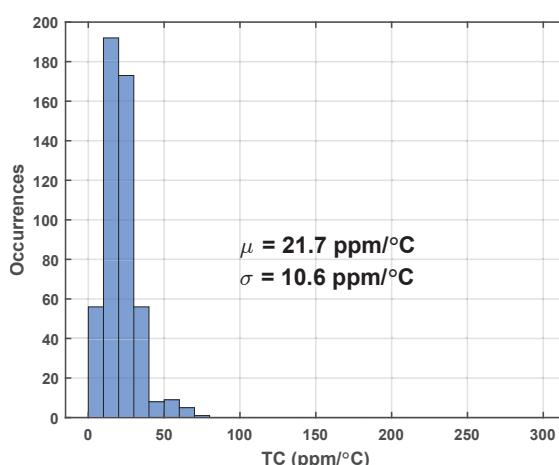

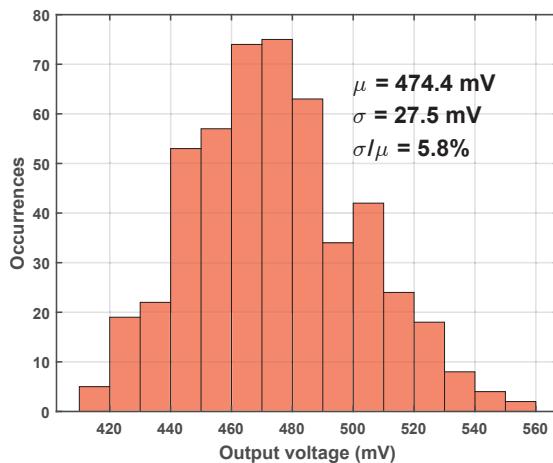

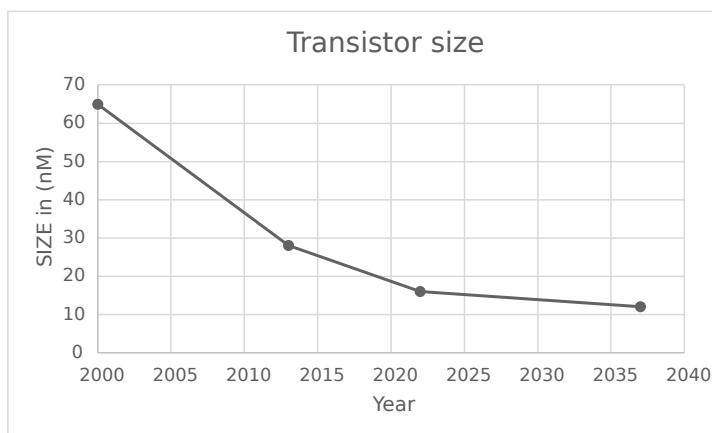

Wang et al. (Contribution 5) design a novel low-power MOS-only voltage reference, showing 21.7 ppm/°C of variation in a temperature range from –40 °C to 120 °C, consuming 23.2 nW with a supply voltage of 0.8 V in 55nm technology nodes.

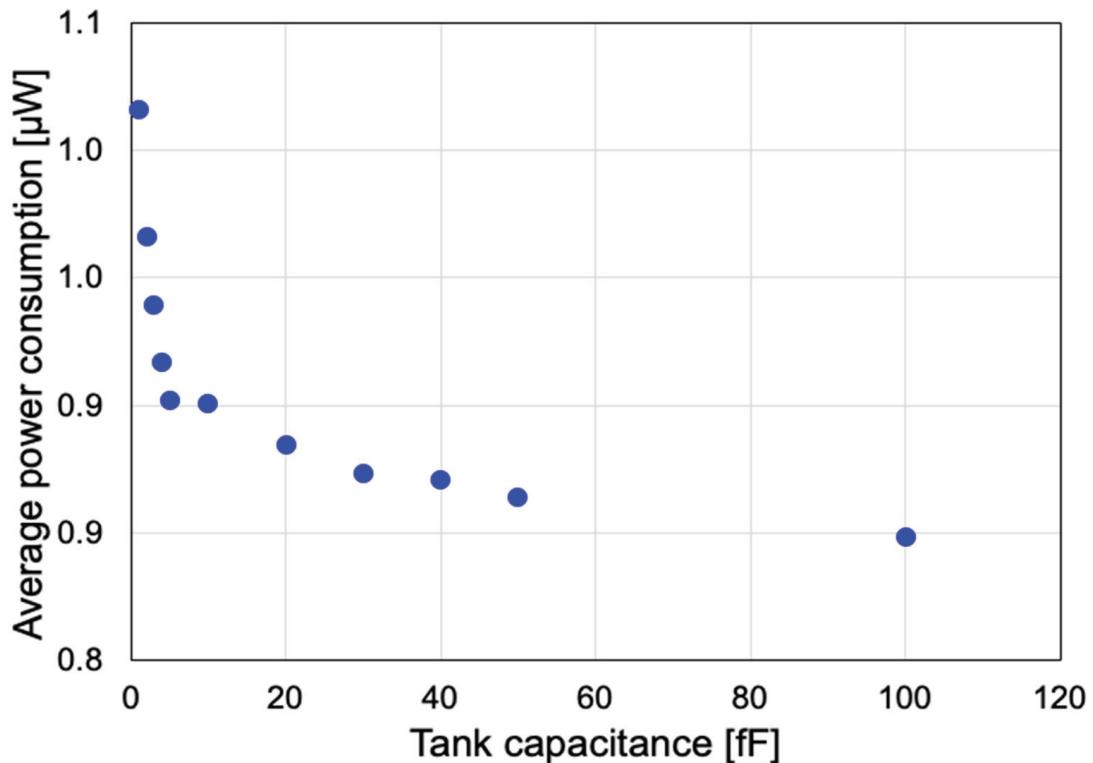

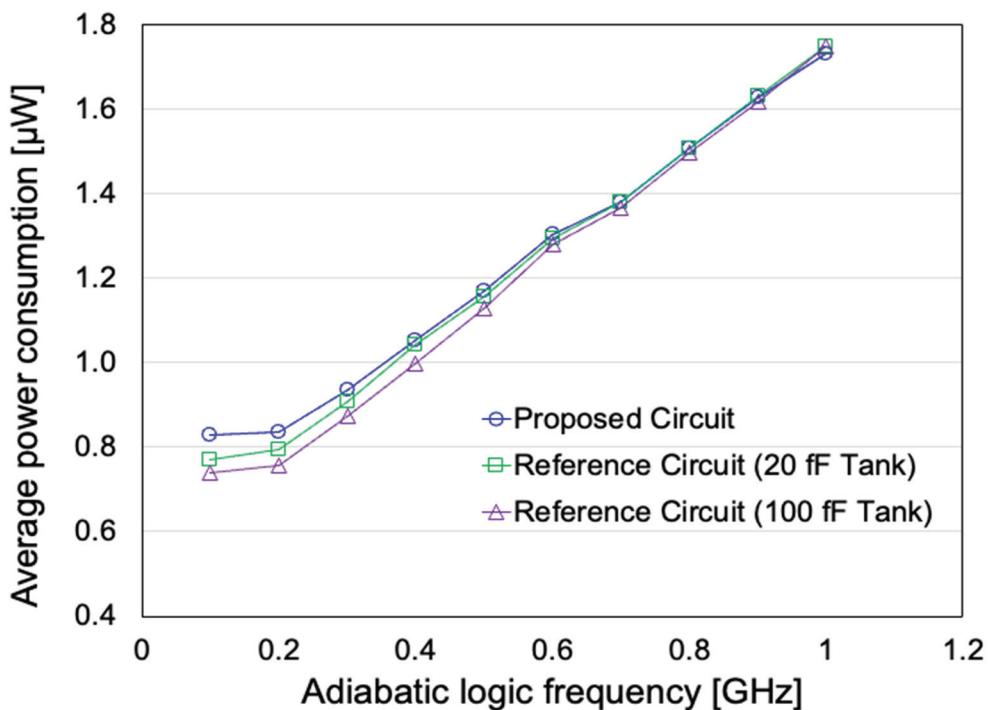

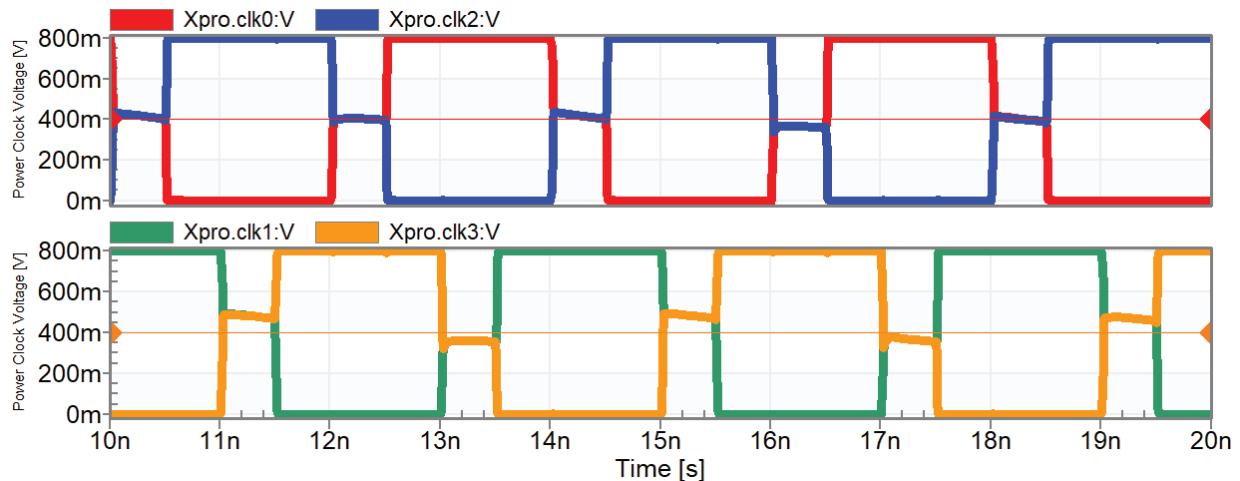

Morell et al. (Contribution 6) propose a novel, stepwise charging driver circuit for four-phase adiabatic logic and validate it through an analysis in 15 nm FinFET technology nodes.

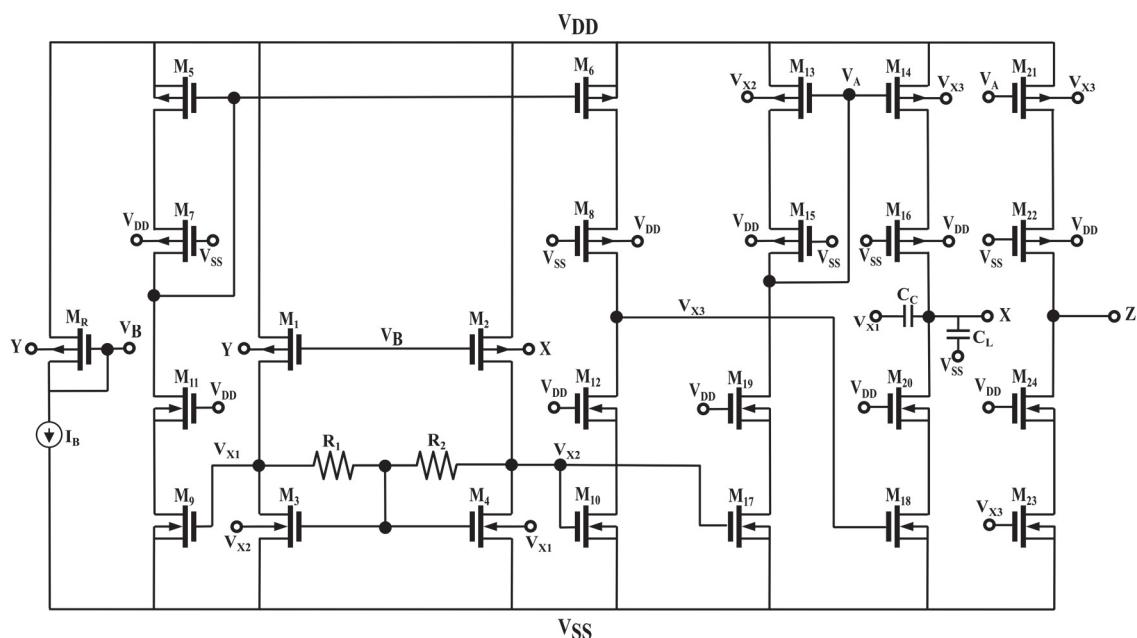

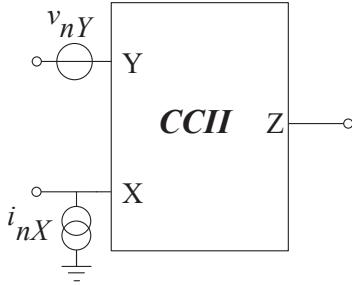

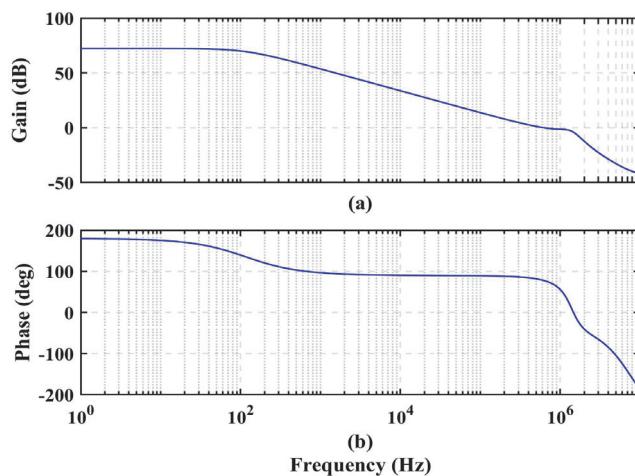

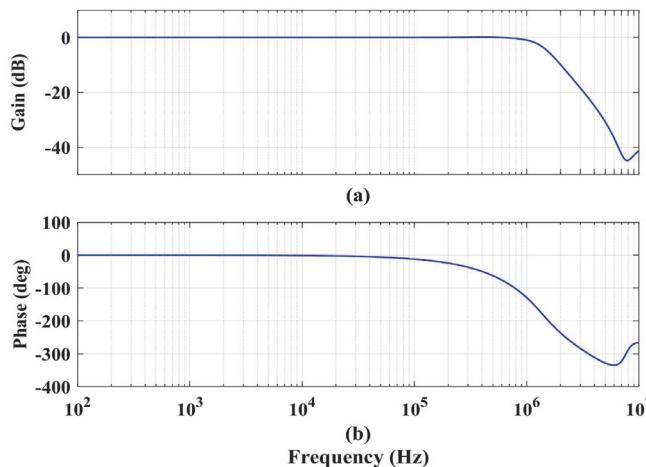

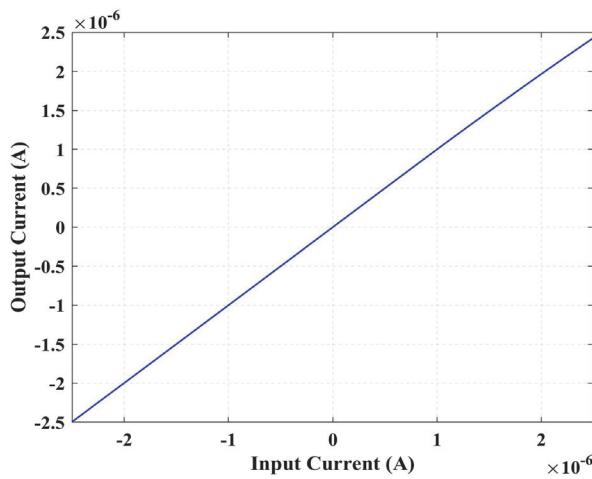

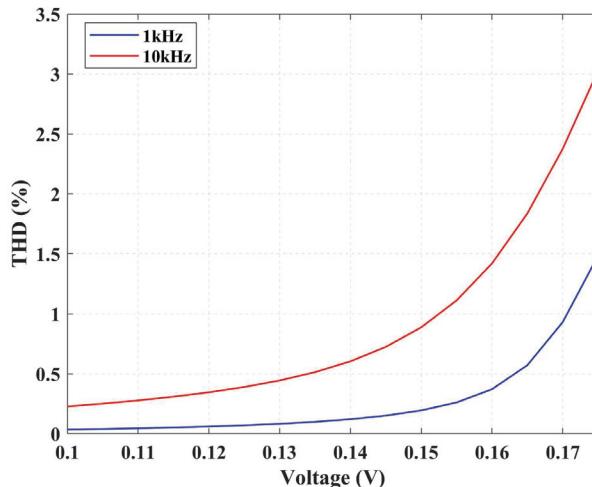

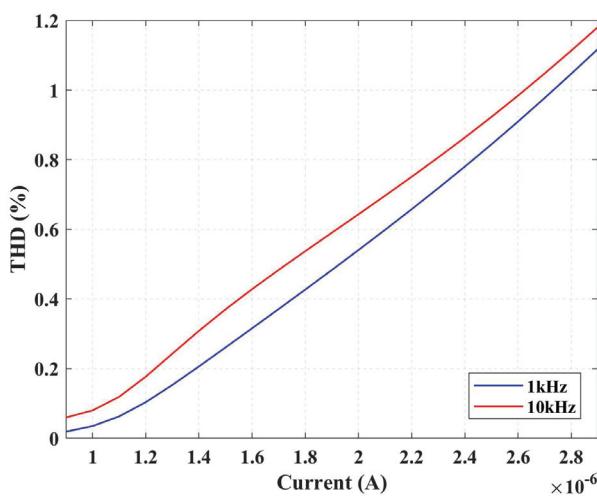

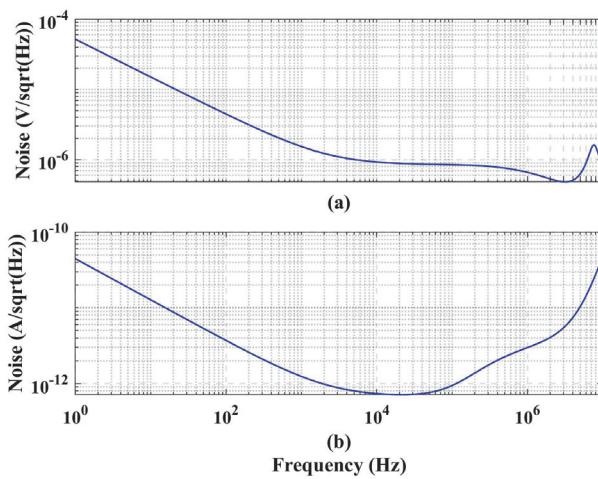

The work by Shah et al. (Contribution 7) describes a bulk-driven second-generation Current Conveyor (CCII) operating at 0.35 V, offering a linear current drive up to 2.5 μA, while consuming a total quiescent current of 2.86 μA.

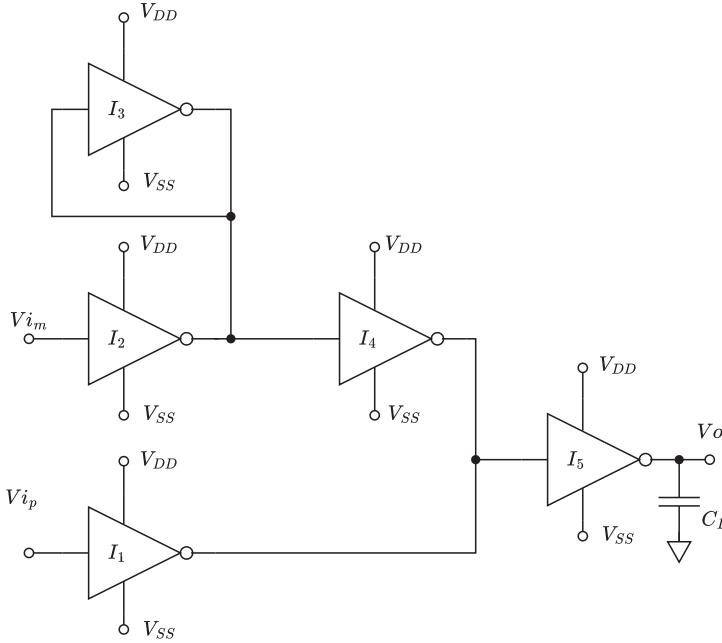

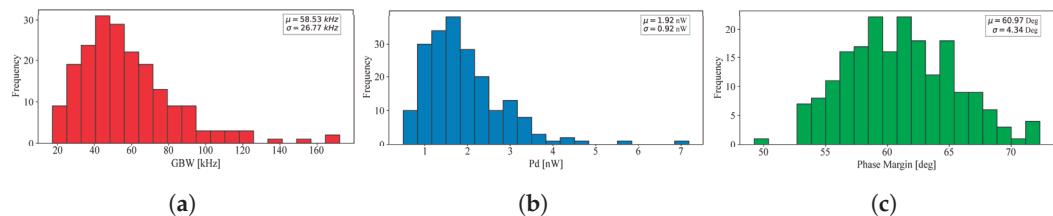

Della Sala et al. (Contribution 8) report an approach to designing digital-based operational transconductance amplifiers (OTAs) by ensuring that the gates operate with a well-defined quiescent current and output voltage, meaning that they are resistant to PVT variations.

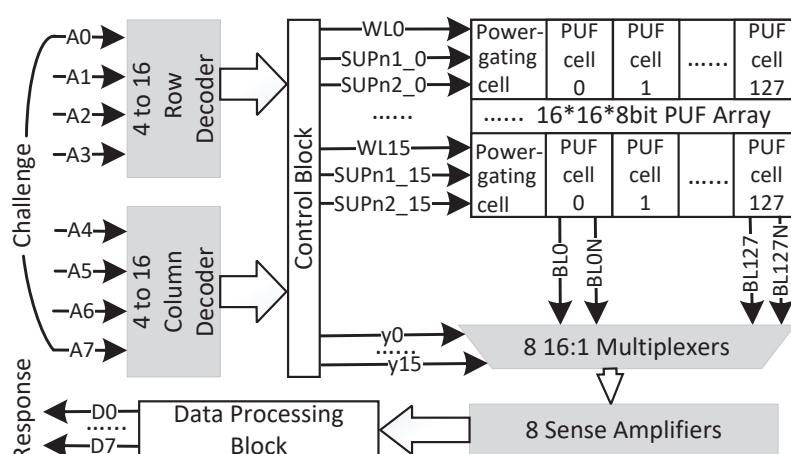

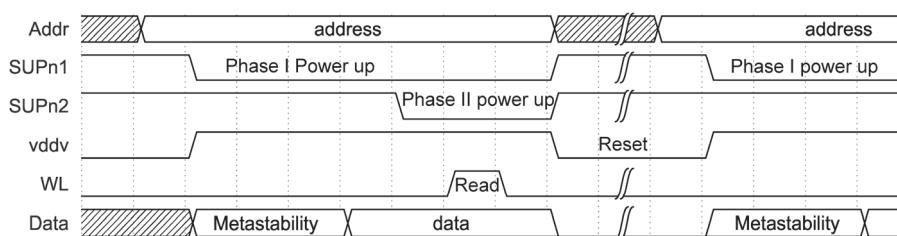

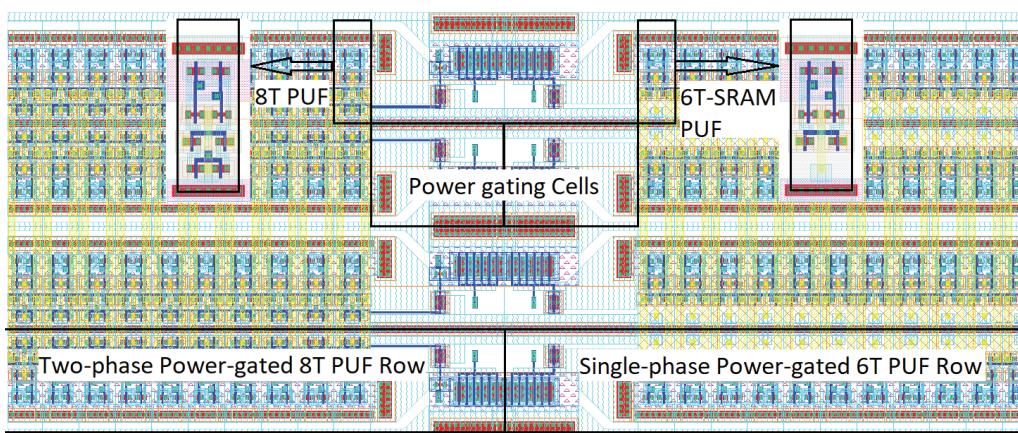

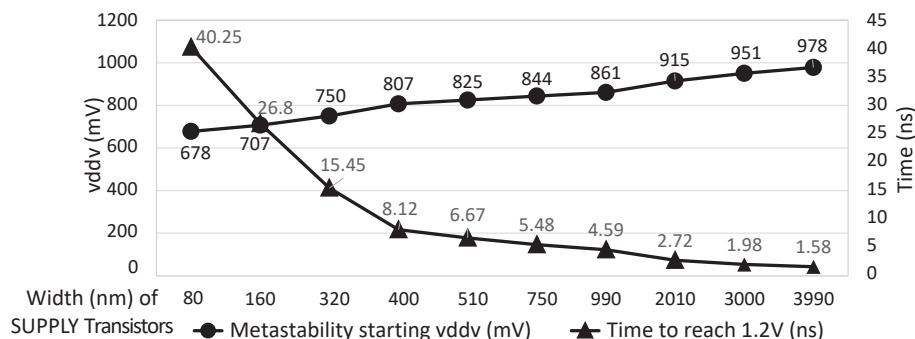

Regarding security applications, in their article, Zheng et al. (Contribution 9) propose an 8-Transistor (8T) power-gated Physically Unclonable Function (PUF) implemented in 65 nm technology, built to swiftly eliminate data remanence and maximize physical mismatch.

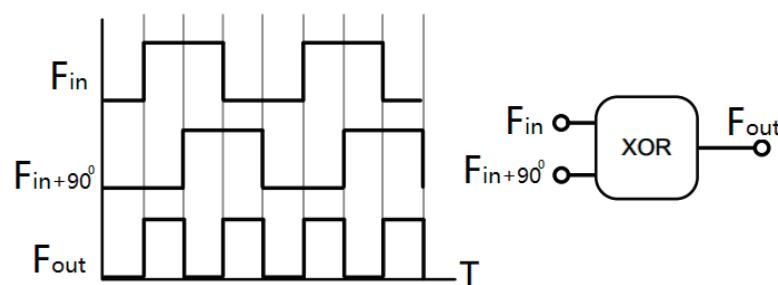

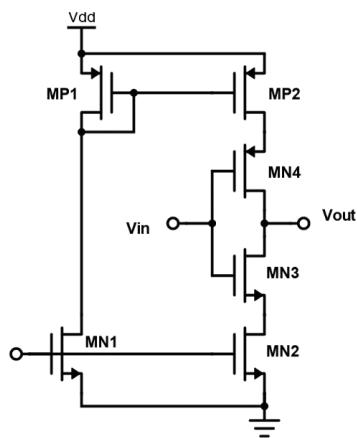

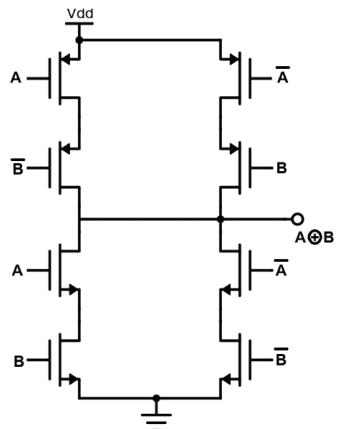

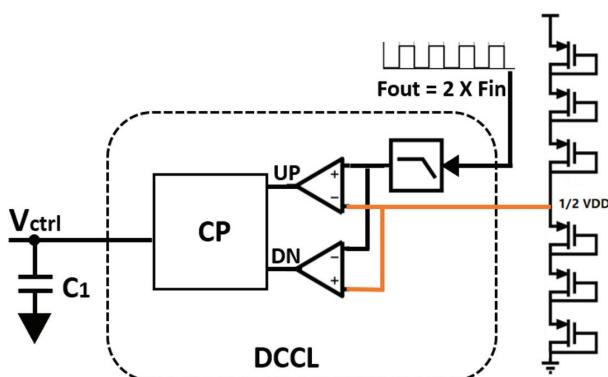

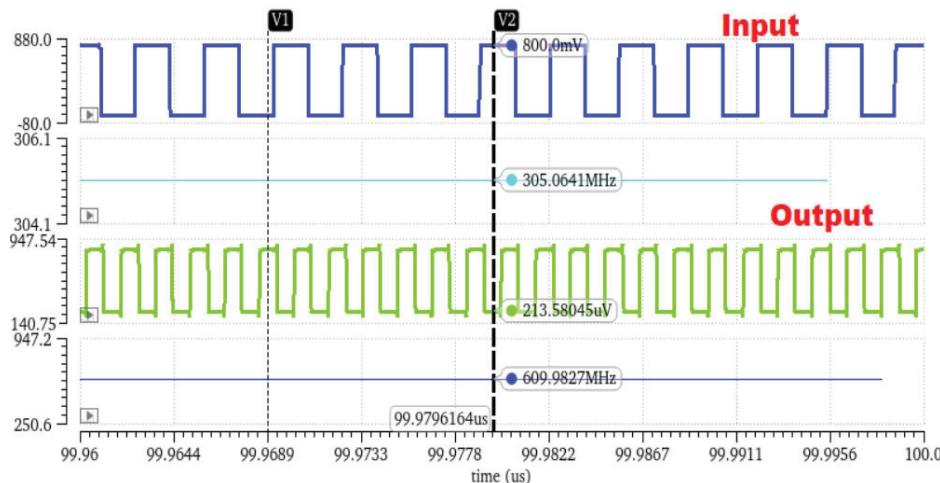

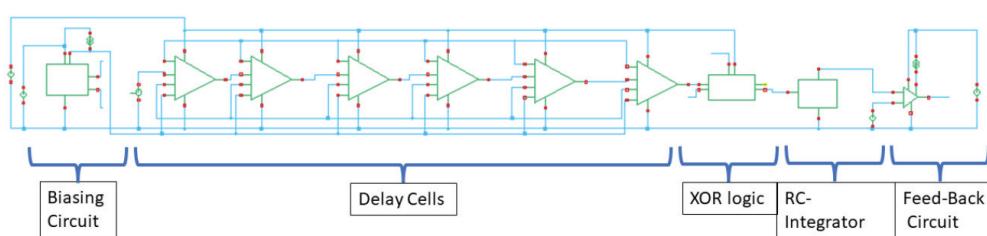

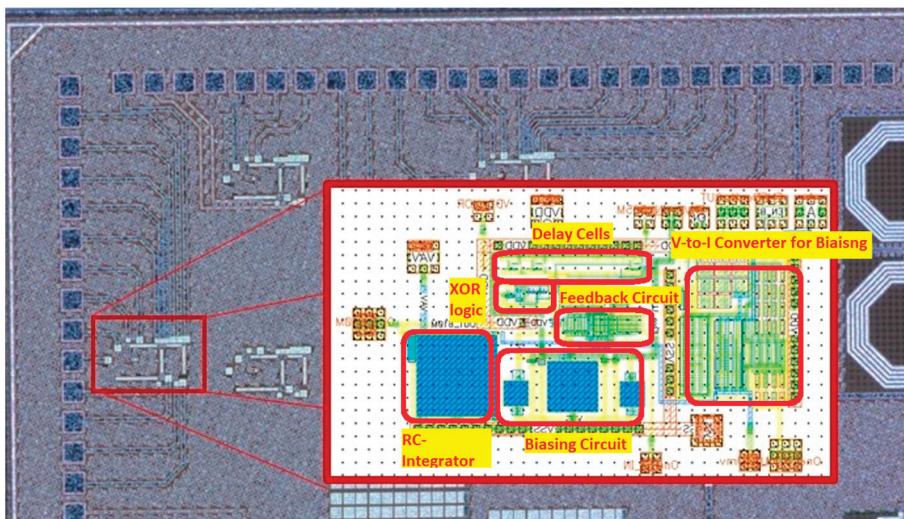

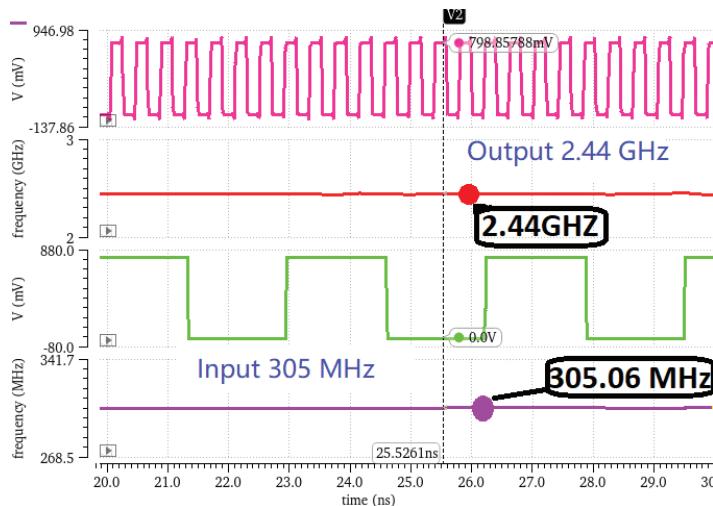

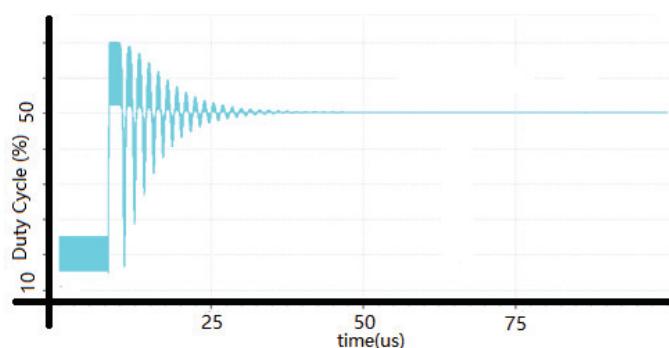

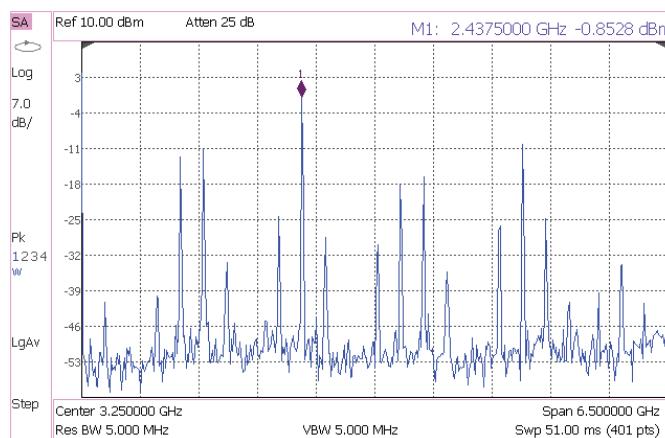

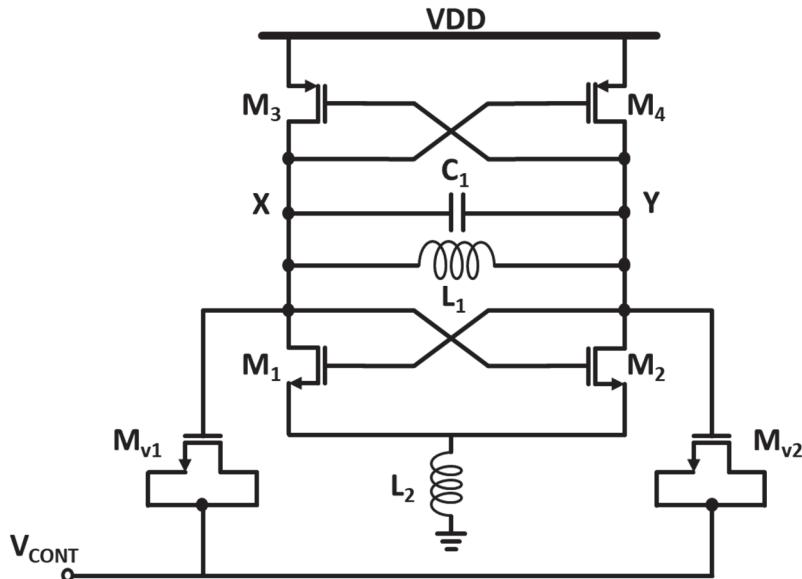

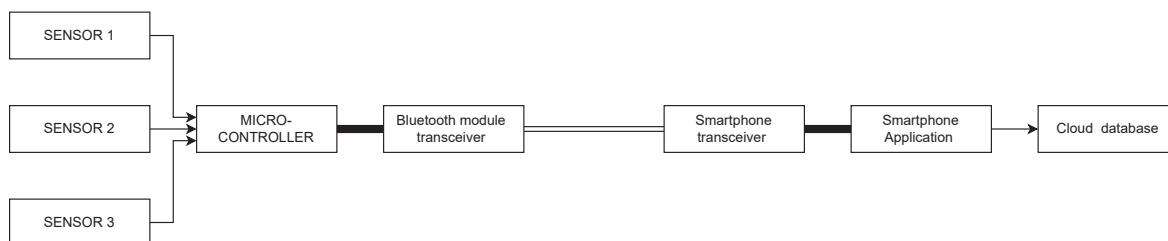

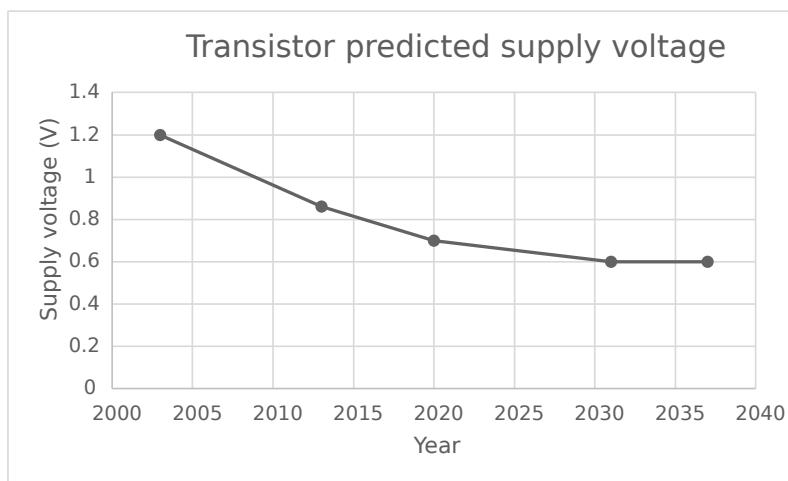

Among the faster and thus more power-hungry solutions, Naveed et al. (Contribution 10) present a multiplier and Siddiqui et al. (Contribution 11) present a VCO. Contribution 10 reports a delay-locked loop (DLL)-based frequency 8× multiplier with

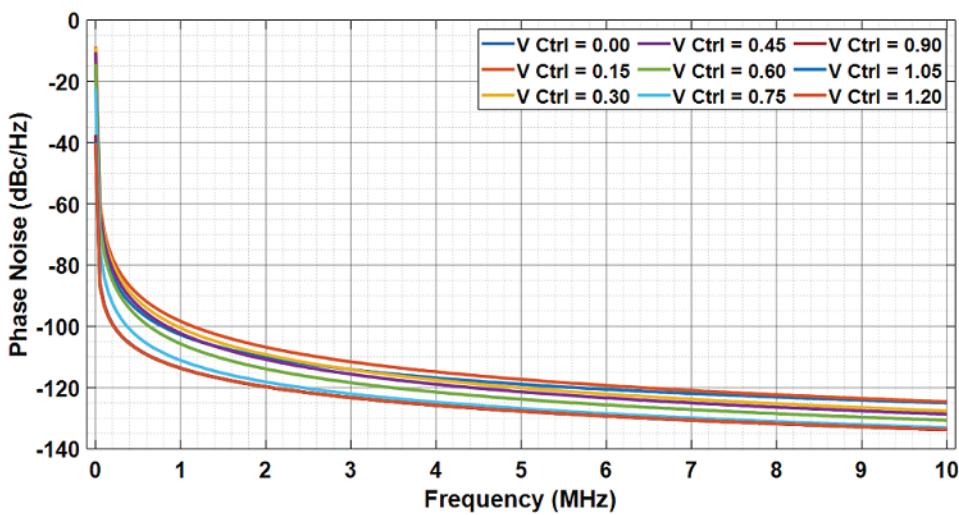

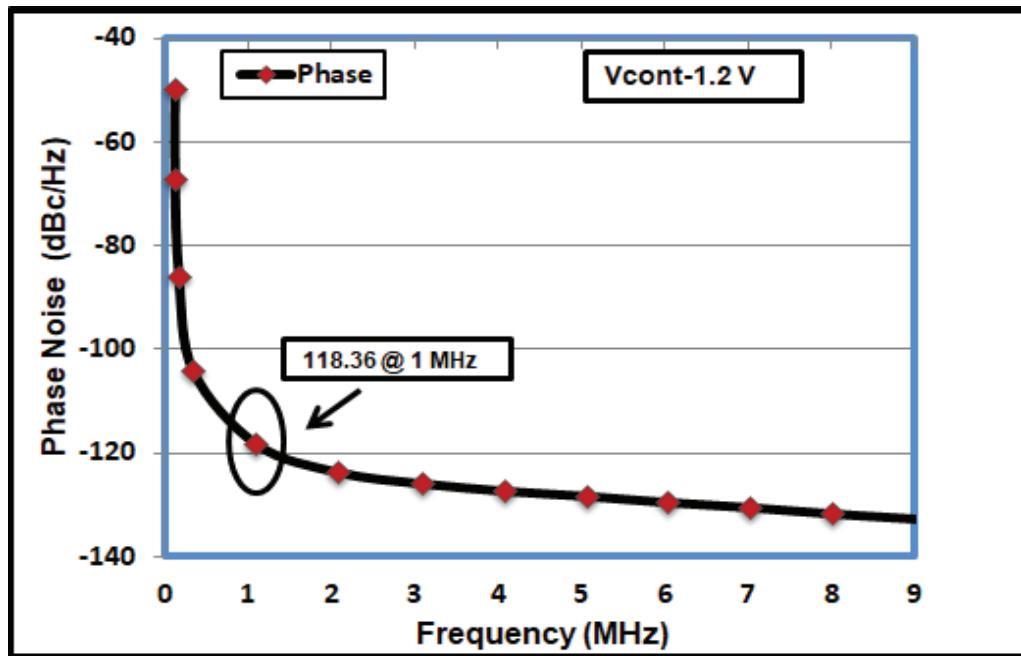

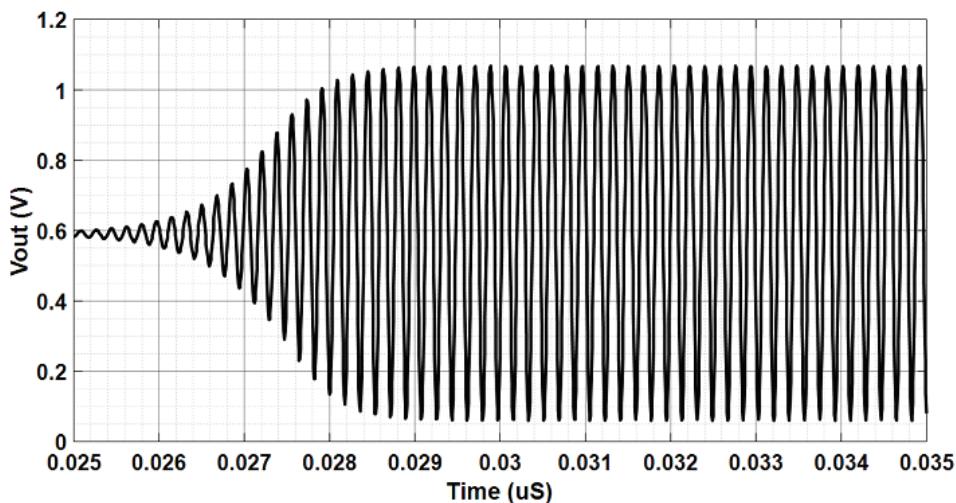

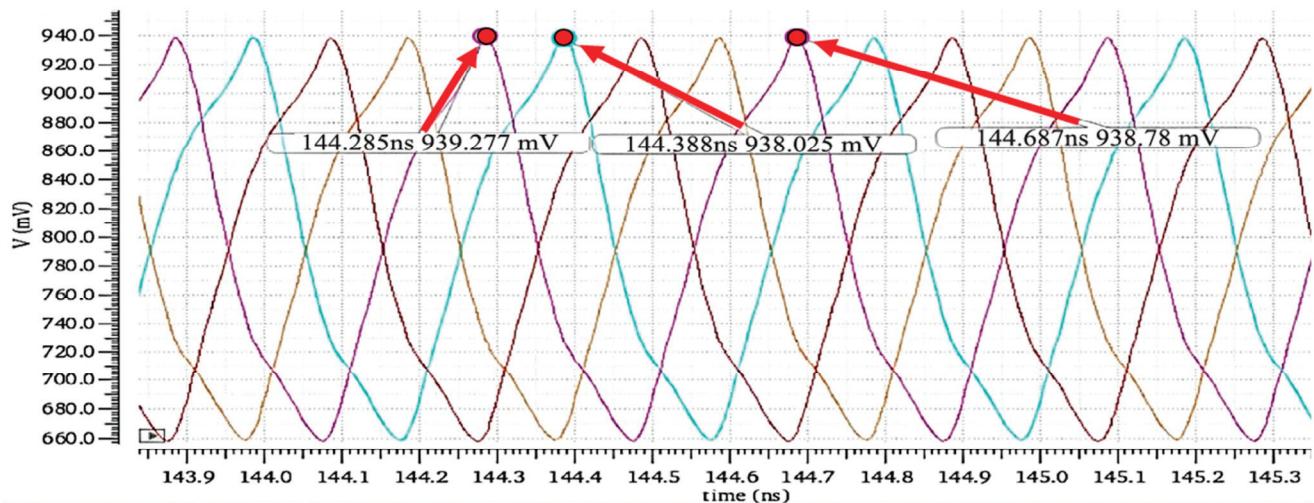

a 22 nm FDSOI power consumption of 130  $\mu$ W at 0.8 V supply with a new simple duty cycle correction circuit that is XOR logic-based for frequency multiplication. In Contribution 11, a tunable quadrature differential LC CMOS voltage-controlled oscillator (VCO) with a D flip-flop (DFF) frequency divider, consuming 2.02 mW with a tuning range of 4.4 to 5.7 GHz and showing a phase noise of  $-118.36$  dBc/Hz at a 1 MHz offset frequency with a 1.2 V supply voltage, is designed through a 65 nm technology process.

Last, but not least, Baker et al. (Contribution 12) review advancements in wireless short-range communication (i.e., Bluetooth, RFID, and NFC), adding further value to this second Special Issue volume.

In summary, these research publications explore a wide array of prospects inspired by these innovative designing techniques, covering a broad range of areas in the ULP/ULV IC field.

**Acknowledgments:** As the Guest Editor of this Special Issue, “Ultra-Low-Power ICs for the Internet of Things (2nd Edition)”, I would like to thank MDPI for the invitation to write this Editorial and introduce the 12 contributions. This Special Issue is freely available to read at [https://www.mdpi.com/journal/jlpea/special\\_issues/919Q5756T0](https://www.mdpi.com/journal/jlpea/special_issues/919Q5756T0) (accessed on 16 September 2025). Moreover, based on the success of this Special Issue, a third edition has been launched at [https://www.mdpi.com/journal/jlpea/special\\_issues/5X3201Q4L8](https://www.mdpi.com/journal/jlpea/special_issues/5X3201Q4L8) (accessed on 16 September 2025).

**Conflicts of Interest:** The author declares no conflicts of interest.

#### List of Contributions:

1. Tran, X.P.; Kieu, X.T.; Pham, X.T.; Pham, D.P.; Hoang, M.K. A 1.87  $\mu$ W Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8  $\text{G}\Omega$  Input Impedance for Biomedical Recording. *J. Low Power Electron. Appl.* **2024**, *14*, 37. <https://doi.org/10.3390/jlpea14030037>.

2. Pham, X.T.; Kieu, X.T.; Hoang, M.K. Ultra-Low Power Programmable Bandwidth Capacitively-Coupled Chopper Instrumentation Amplifier Using 0.2 V Supply for Biomedical Applications. *J. Low Power Electron. Appl.* **2023**, *13*, 37. <https://doi.org/10.3390/jlpea13020037>.

3. Namdari, A.; Aiello, O.; Caviglia, D.D. A 0.5 V, 32 nW Compact Inverter-Based All-Filtering Response Modes Gm-C Filter for Bio-Signal Processing. *J. Low Power Electron. Appl.* **2024**, *14*, 40. <https://doi.org/10.3390/jlpea14030040>.

4. Nicolini, G.; Fava, A.; Centurelli, F.; Scotti, G. A 0.064 mm<sup>2</sup> 16-Channel In-Pixel Neural Front End with Improved System Common-Mode Rejection Exploiting a Current-Mode Summing Approach. *J. Low Power Electron. Appl.* **2024**, *14*, 38. <https://doi.org/10.3390/jlpea14030038>.

5. Wang, S.; Lu, Z.; Xu, K.; Dai, H.; Wu, Z.; Yu, X. A Sub-1-V Nanopower MOS-Only Voltage Reference. *J. Low Power Electron. Appl.* **2024**, *14*, 13. <https://doi.org/10.3390/jlpea14010013>.

6. Morell, W.; Choi, J.-W. Design and Analysis of Self-Tanked Stepwise Charging Circuit for Four-Phase Adiabatic Logic. *J. Low Power Electron. Appl.* **2024**, *14*, 34. <https://doi.org/10.3390/jlpea14030034>.

7. Shah, M.O.; Caruso, M.; Pennisi, S. 0.35 V Subthreshold Bulk-Driven CMOS Second-Generation Current Conveyor. *J. Low Power Electron. Appl.* **2024**, *14*, 36. <https://doi.org/10.3390/jlpea14030036>.

8. Della Sala, R.; Centurelli, F.; Scotti, G. An Ultra-Low-Voltage Approach to Accurately Set the Quiescent Current of Digital Standard Cells Used for Analog Design and Its Application on an Inverter-Based Operational Transconductance Amplifier. *J. Low Power Electron. Appl.* **2024**, *14*, 39. <https://doi.org/10.3390/jlpea14030039>.

9. Zheng, Y.; Yakovlev, A.; Bystrov, A. A Power-Gated 8-Transistor Physically Unclonable Function Accelerates Evaluation Speeds. *J. Low Power Electron. Appl.* **2023**, *13*, 53. <https://doi.org/10.3390/jlpea13040053>.

10. Naveed; Dix, J. Design of a Low-Power Delay-Locked Loop-Based 8 $\times$  Frequency Multiplier in 22 nm FDSOI. *J. Low Power Electron. Appl.* **2023**, *13*, 64. <https://doi.org/10.3390/jlpea13040064>.

11. Siddiqui, M.F.; Maheshwari, M.K.; Raza, M.; Masud, A.R. Design and Optimization of an Ultra-Low-Power Cross-Coupled LC VCO with a DFF Frequency Divider for 2.4 GHz RF Receivers Using 65 nm CMOS Technology. *J. Low Power Electron. Appl.* **2023**, *13*, 54. <https://doi.org/10.3390/jlpea13040054>.

12. Baker, B.; Woods, J.; Reed, M.J.; Afford, M. A Survey of Short-Range Wireless Communication for Ultra-Low-Power Embedded Systems. *J. Low Power Electron. Appl.* **2024**, *14*, 27. <https://doi.org/10.3390/jlpea14020027>.

## Reference

1. Ultra-Low-Power ICs for the Internet of Things. Available online: [https://www.mdpi.com/journal/jlpea/special\\_issues/low\\_power\\_iot](https://www.mdpi.com/journal/jlpea/special_issues/low_power_iot) (accessed on 16 September 2025).

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Article

# A 1.87 $\mu$ W Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8 G $\Omega$ Input Impedance for Biomedical Recording <sup>†</sup>

Xuan Phuong Tran <sup>1</sup>, Xuan Thuc Kieu <sup>1</sup>, Xuan Thanh Pham <sup>1</sup>, Duy Phong Pham <sup>2</sup> and Manh Kha Hoang <sup>1,\*</sup>

<sup>1</sup> Faculty of Electronics Engineering, Hanoi University of Industry, Hanoi 100000, Vietnam; phuongtx@hau.edu.vn (X.P.T.); thuckx@hau.edu.vn (X.T.K.); thanhpx@hau.edu.vn (X.T.P.)

<sup>2</sup> Faculty of Electronic and Telecommunication Engineering, Electric Power University, Hanoi 100000, Vietnam; phongphd@epu.edu.vn

\* Correspondence: khahoang@hau.edu.vn; Tel.: +84-24-3765-5121

† This paper is an extended version of our paper published in 2023 International Conference on Advanced Technologies for Communications (ATC).

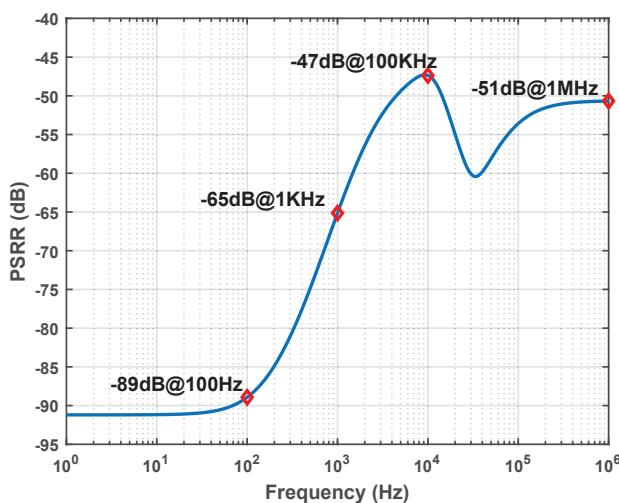

**Abstract:** Chopper and capacitively coupled techniques are employed in instrumentation amplifiers to create capacitively coupled chopper instrumentation amplifiers (CCIAs) that obtain a high noise power efficiency. However, the CCIA has some disadvantages due to the chopper technique, namely chopper ripple and a low input impedance. The amplifier can easily saturate due to the chopper ripple of the CCIA, especially in extremely low noise problems. Therefore, ripple attenuation is required when designing CCIAs. To record biomedical information, a CCIA with a low power consumption and a low noise, low output ripple, and high input impedance ( $Z_{in}$ ) is presented in this paper. By introducing a ripple attenuation loop (RAL) including the chopping offset amplifier and a low pass filter, the chopping ripple can be reduced to 0.36 mV. To increase the  $Z_{in}$  of the CCIA up to 1.8 G $\Omega$ , an impedance boost loop (IBL) is added. By using 180 nm CMOS technology, the 0.123 mm<sup>2</sup> CCIA consumes 1.87  $\mu$ W at a supply voltage of 1 V. According to the simulation results using Cadence, the proposed CCIA architecture achieves a noise floor of 136 nV/  $\sqrt$ Hz, an input-referred noise (IRN) of 2.16  $\mu$ V<sub>rms</sub>, a closed-loop gain of 40 dB, a power supply rejection ratio (PSRR) of 108.6 dB, and a common-mode rejection ratio (CMRR) of 118.7 dB. The proposed CCIA is a helpful method for monitoring neural potentials.

**Keywords:** low power; chopper amplifier; ripple attenuation; input impedance

## 1. Introduction

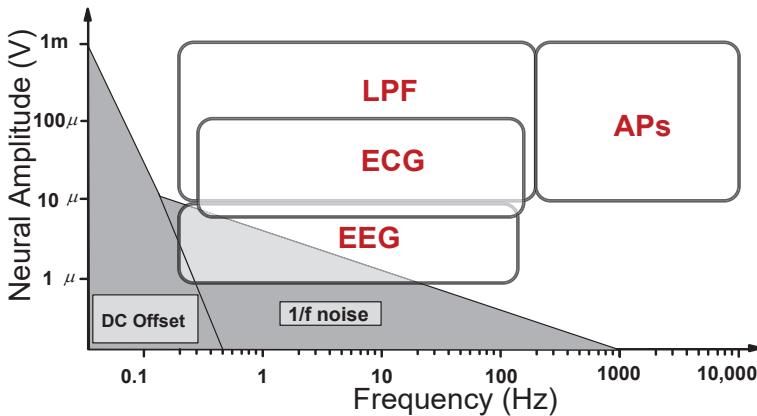

Wireless biomedical sensors (WBSs) are increasingly used to track our daily activities in order to detect cardiovascular diseases at an early stage [1–4]. Monitoring human biopotential requires the use of low-power sensors deployed in wearable or implantable systems. Researchers are currently developing brain–computer interfaces for numerous applications such as long-term monitoring, sports, rehabilitation, mobile monitoring, and improving the quality of life of patients [5,6]. WBSs typically use an instrumentation amplifier (IA) with low power consumption and low noise to connect with many types of biological sensors. The electrocardiograms (ECGs) of the heart and the electroencephalograms (EEGs) of the brain are examples of these biopotential signals. Neuroscience research and therapy can benefit from the use of biomarkers such as action potentials (APs) and local field potentials (LFPs) [7–9]. Biopotential signals often have an extremely small amplitude. For example, the amplitude range of an EEG is from 10 to 100  $\mu$ V and that of an ECG is about 1 mV. The frequency range of the biopotential signals is 0.5–150 Hz [7,8]. The amplitude of the AP and LFP signals is about 100  $\mu$ V to 1 mV, with a frequency range of 0.2 to 10 kHz for APs, and 1 to 200 Hz for LFPs [9]. Consequently, before signal processing is applied, these

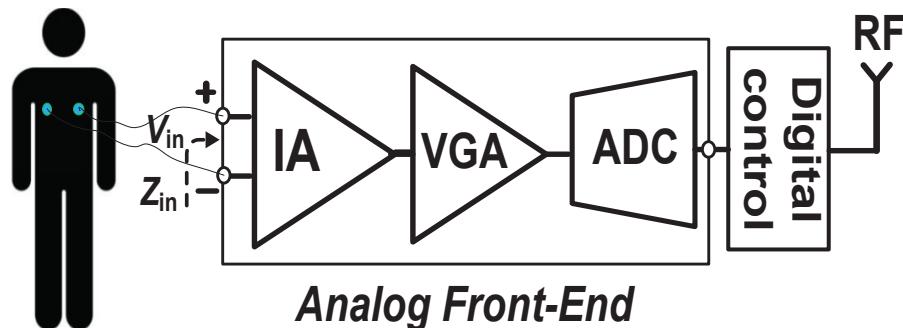

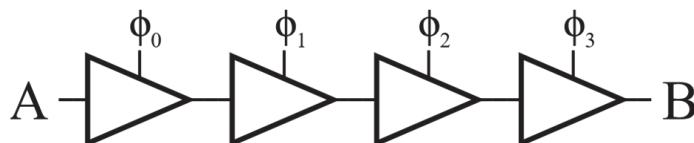

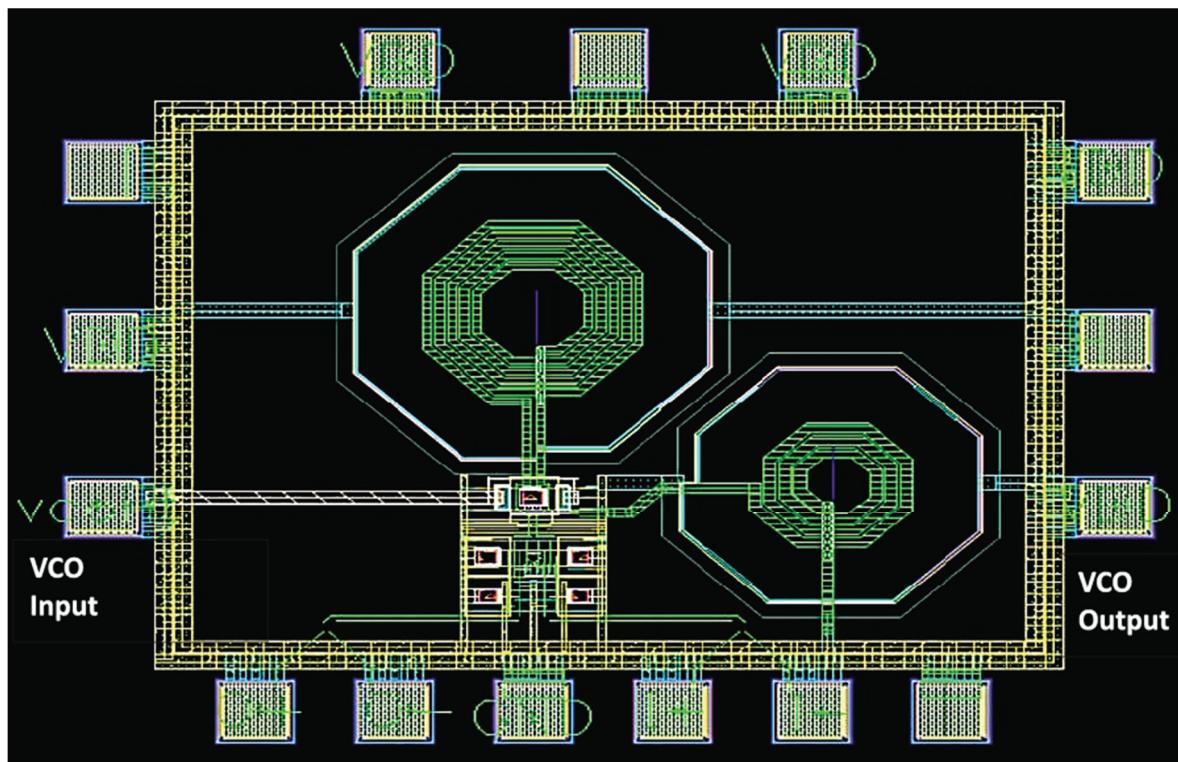

neural signals need to be amplified. A wearable biomedical sensor, constructed as shown in Figure 1, provides these neurological signals.

**Figure 1.** System architecture of a typical wireless sensor biomedical system.

The first stage measures the amplitude of the small bio signal with a dry or wet electrode. An analog front-end, consisting of an IA at the first stage, a variable gain amplifier (VGA) at the middle stage, and an analog-to-digital converter (ADC) at the last stage, processes the neural signal in the second stage before it is transmitted by RF. The preamplifier of the analog front-end must obtain a high input impedance ( $Z_{in}$ ) to reduce the DC input current that could cause tissue damage [8]. The IA must likewise demonstrate a low power, low noise, high-power supply rejection ratio (PSRR), and common-mode rejection ratio (CMRR) to eliminate noise from the power line and environmental factor, which may be important in some cases.

The chopping technique is frequently used in IA [10–17] to create an IA with a high PSRR, CMRR, and noise efficiency. The input capacitance and the switches in the chopper block generate the switched capacitance resistor, which is inversely proportional to the chopper frequency. This leads to a limitation of the  $Z_{in}$  of the amplifier if there are no impedance boosting techniques [18]. The ripple appears as a triangular wave affecting the quality of the signal of interest caused by a modulated intrinsic offset [19–21]. Furthermore, for long-term battery life suitable for WBS applications, the power consumption of the IC must be as small as possible, and the noise must also be low so as not to affect the signal quality at the output of the IC. Although a number of biomedical amplifiers with low power consumption have been published, it has not yet been possible to improve the output ripple or  $Z_{in}$ . For example, in 2020, the chopper amplifier in [22] consumed 3.24  $\mu$ W at a 1.8 voltage supply, the  $Z_{in}$  just reached 440  $M\Omega$ , while the ripple suppression technique used an AC coupling capacitor, which caused this design to be affected by the noise folding [19]. In 2021, the current-reuse instrumentation amplifier [23] dissipated 5.94  $\mu$ W at a voltage supply of 1.8 V to achieve a  $Z_{in}$  of 2.6  $G\Omega$  without any ripple suppression approaches. In 2024, although the amplifier [24] consumed only 2.47  $\mu$ W from a 1.5 V supply, the output ripple and  $Z_{in}$  were not improved.

This paper presents a CCIA for biomedical information recording that is characterized by low noise, high input impedance, low output ripple, and low power consumption. At 1 V, the 0.123  $mm^2$  CCIA, which was simulated using a 180 nm CMOS process, consumes 1.87  $\mu$ W. According to simulation results, it is shown that the output ripple being reduced to 0.36 mV is achieved with an RAL being switched on, and the  $Z_{in}$  of the CCIA increases up to 1.8  $G\Omega$  when the impedance boost loop (IBL) is active. When both the RAL and IBL are activated, the proposed CCIA obtains a closed-loop gain of 40 dB, an input referred noise (IRN) of 1.81  $\mu$ V<sub>rms</sub>, a thermal noise of 136 nV/  $\sqrt{Hz}$ , a common mode rejection ratio (CMRR) of 118.7 dB, and a power supply rejection ratio (PSRR) of 108.6 dB. Achieving a noise efficiency factor (NEF) of 6.8 and 7.5 with both RAL and IBL turned off and on, respectively, demonstrates that the CCIA records biomedical information successfully.

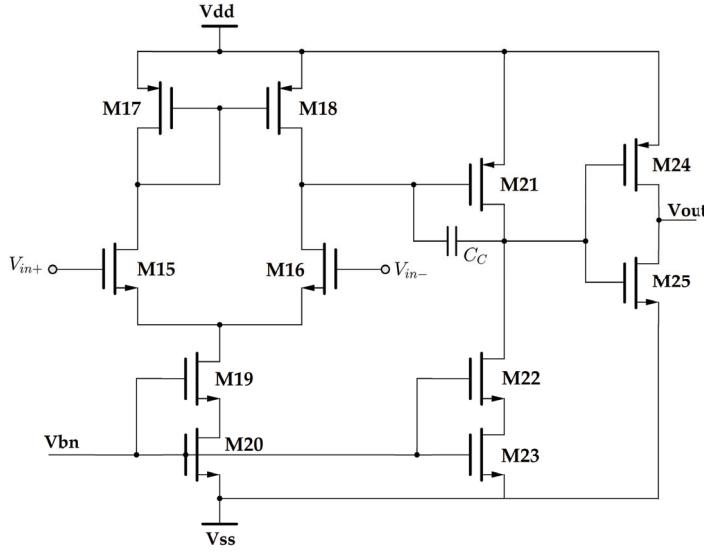

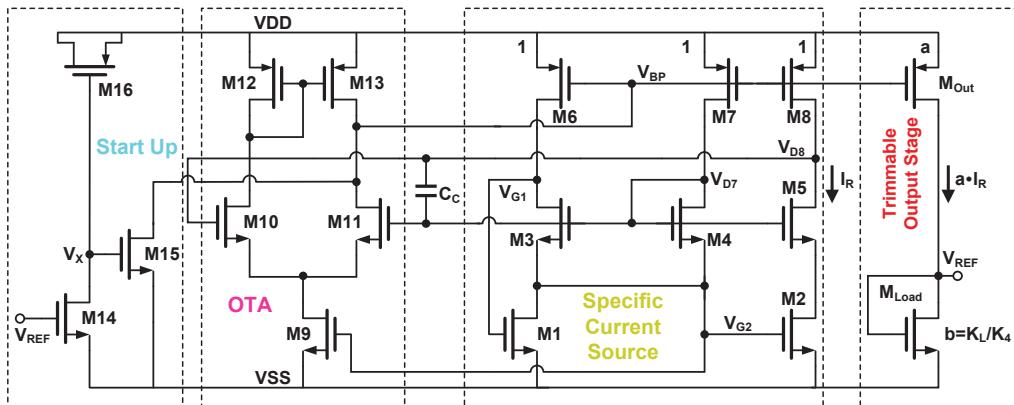

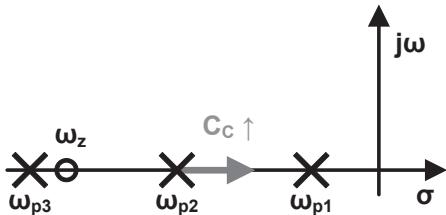

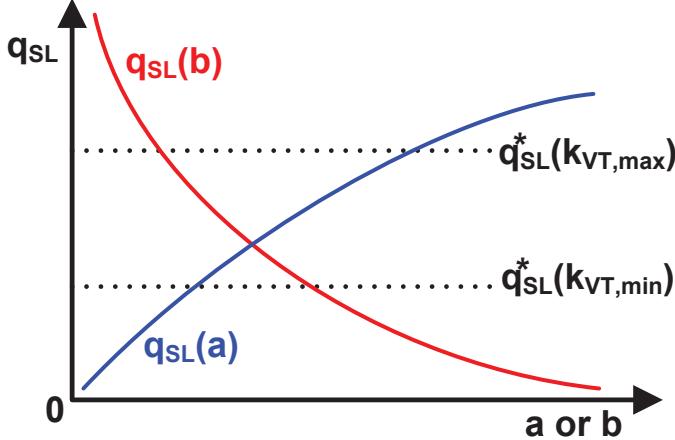

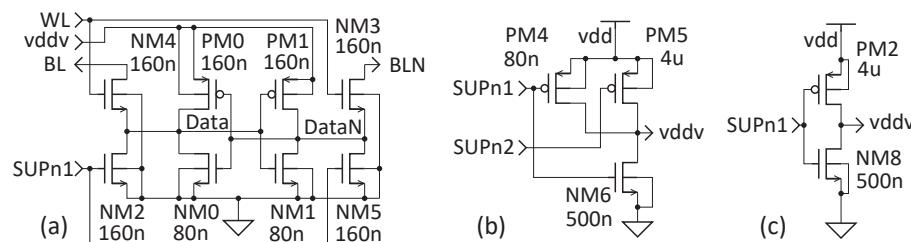

## 2. Design

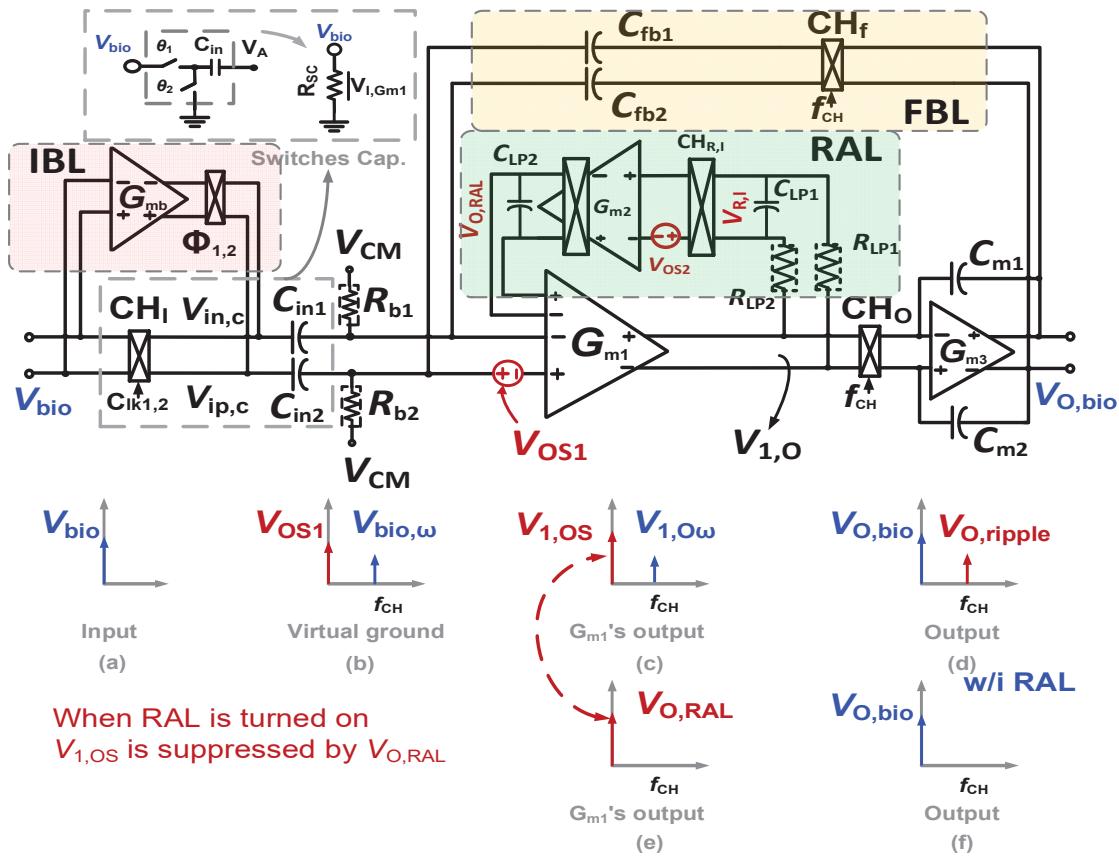

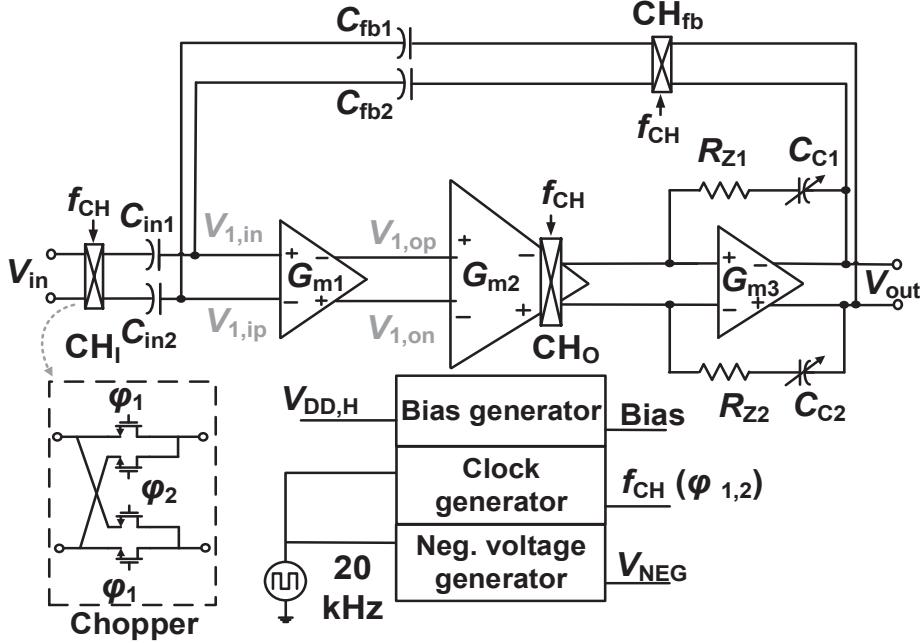

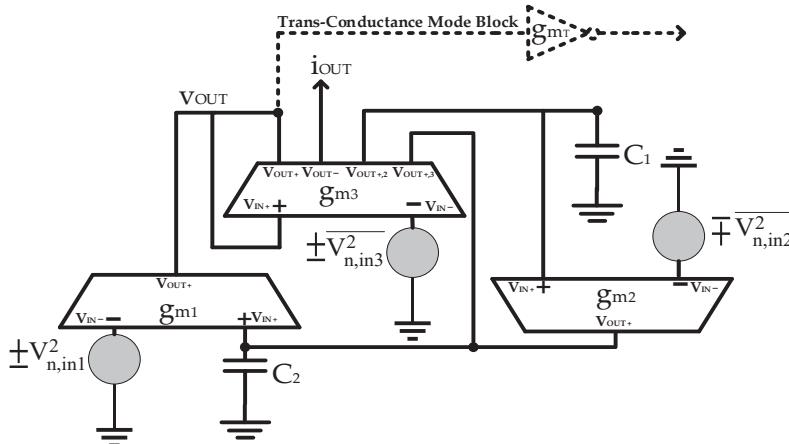

The proposed CCIA for biomedical monitoring applications with a low output ripple and a high  $Z_{in}$ , as shown in Figure 2, consists of the main channel and three auxiliary loops such as a negative feedback loop (FBL), a ripple attenuation loop (RAL), and an impedance boosting loop (IBL) in order to solve the main problems of biopotential amplifiers. The transconductance input stage ( $G_{m1}$ ) of the main path is a dual-folded cascode amplifier (DFC) with a biased current of  $1.2 \mu\text{A}$ . In order to attain a working stability and a high swing, the  $G_{m3}$  used a common source (CS) amplifier, combined with a Miller capacitor of  $1.5 \text{ pF}$ . A bias current of  $1.8 \mu\text{A}$  is used for the channel and global common mode feedback (CMFB) from a  $V_{DD}$  of  $1 \text{ V}$ . The CCIA has a closed-loop gain of  $40 \text{ dB}$ , which is defined by the ratio of the input and negative feedback capacitors. In this design, the input capacitor  $C_{in1,2}$  is set at  $20 \text{ pF}$  and the negative feedback capacitor  $C_{fb1,2}$  is set at  $0.2 \text{ pF}$ . The PMOS pseudo-resistor  $R_{b1,2}$  is used to bias DFC using the common mode voltage  $V_{CM} = 0.5 \text{ V}$ . The capacitors ( $C_{in1,2}$ ,  $C_{fb1,2}$ ,  $C_{m1,2}$ , and  $C_{LP1,2}$ ) are created using the MIM capacitor technique.

**Figure 2.** The schematic of the proposed CCIA with the spectrum of signal corresponding to each node.

As shown in Figure 2, the chopper  $CH_I$  is employed to modulate the bio signal input  $V_{bio}$  at low frequency (as shown in Figure 2a) up to a signal at  $f_{CH} = 10 \text{ kHz}$ , before reducing it with a negative feedback loop at the virtual ground. When  $V_{bio,\omega}$  is at virtual ground (as shown in Figure 2b), it can be written as  $V_{bio,\omega} = V_{bio}/(1 + \beta A_V)$ , where  $A_V$  is the open-loop gain voltage of the CCIA, and  $\beta$  is the factor of the negative feedback loop based on the ratio of  $C_{fb}$  to  $C_{in}$ . The chopper  $CH_O$  converts the  $V_{bio,\omega}$  to the essential frequency band after  $G_{m1}$  has amplified it to produce  $V_{1,O\omega}$ . Finally,  $G_{m3}$  amplifies this signal to

generate a bio signal amplification  $V_{O,\text{bio}}$  at the CCIA's output (as shown in Figure 2d). The transfer function of the proposed CCIA can be expressed as follows:

$$H(s) = - \left( \frac{g_{m1}C_{in1,2}}{(C_{in1,2} + C_{fb1,2})C_{m1,2}} \right) / \left( s + \frac{g_{m1}C_{fb1,2}}{(C_{in1,2} + C_{fb1,2})C_{m1,2}} \right) \quad (1)$$

where  $g_{m1}$  is the transconductance of the first stage; and  $C_{in1,2}$ ,  $C_{fb1,2}$ , and  $C_{m1,2}$  are the input, negative, and Miller capacitors, respectively. Unfortunately,  $G_{m1}$  is attached to the offset voltage  $V_{OS1}$  resulting from the process variation (as shown in Figure 2b). After this is amplified by  $G_{m1}$  to create  $V_{1,OS}$  at the output of DFC, the  $V_{1,OS}$  is also chopped to the chopper frequency before being integrated by the Miller integrator. This results in a considerable ripple at the output (as shown in Figure 2d). The amplitude of the output ripple can be described as follows:

$$V_{O,\text{Ripple}} = \frac{V_{OS1}g_{m1}}{2f_{CH}C_{m1,2}} \quad (2)$$

where  $g_{m1}$  is the transconductance of the first stage;  $f_{CH}$  is the chopping frequency; and  $C_{m1,2}$  are the phase margin compensation capacitors. For example,  $V_{OS1} = 10$  mV,  $g_{m1} = 0.7 \mu\text{S}$ ,  $f_{CH} = 10$  kHz,  $C_{m1,2} = 1.5$  pF, and  $V_{O,\text{Ripple}} = 233$  mV.

The block diagram of an RAL is also shown in Figure 2. Instead of capturing the signal at the output, as in the usual approach, the RAL uses a low-pass filter (LPF) to obtain the signal at the output of the DFC ( $V_{1,O} = V_{1,OS} + V_{1,O\omega}$ ) (as shown in Figure 2c) before the chopper output  $CH_O$ . This is because the  $V_{1,OS}$  signal is continuously amplified, while the AC signal  $V_{1,O\omega}$  is filtered out by the LPF in this case. To ensure that no AC signal is applied to  $G_{m1b}$ , which has the schematic shown in next section, the capacitor  $C_{LP2}$  is added to the output of the RAL, although the LPF has a small low-pass corner controlled by  $R_{LP1,2}$  and  $C_{LP1}$ . After amplifying  $V_{1,OS}$ , the signal  $V_{O,RAL}$  is connected to  $G_{m1b}$ , creating a negative feedback loop to compensate for  $V_{1,OS}$  (as shown in Figure 2e). This means that the ripple caused by  $V_{OS1}$  is reduced at the output of the CCIA (as shown in Figure 2f). To increase the loop gain ( $L_G$ ) of the RAL and achieve a high ripple attenuation factor (RAF),  $G_{m2}$  is implemented using a two-stage operational amplifier for low noise and low power consumption. We assume that  $V_{OS2}$ , another inherent offset caused by process variations, is similarly associated with  $G_{m2}$ . The modulated offset  $V_{OS2}$  also generates the ripple at the CCIA's output and has the same effects as  $V_{OS1}$ , so it needs to be reduced. The ripple at the output of the CCIA is mitigated by a DC loop gain's factor  $L_G(0)$  of the feedback loop RAL. The equation to determine  $L_G(s)$  in the technique proposed in this study is as follows:

$$L_G(s) \cong g_{m1b}R_{LP}A_{vGm2,DC} = g_{m1b}R_{LP} \frac{A_{vGm2,DC}}{1 + s/\omega_p} \quad (3)$$

$$L_G(0) \cong G_{m1}R_{LP}A_{vGm2,DC} \quad (4)$$

where  $G_{m1b}$  is the auxiliary transconductance of the first stage  $G_{m1}$ ; and  $A_{vGm2,DC}$  and  $f_p$  ( $\omega_p = 2\pi f_p$ ) are the DC gain and cut-off frequency of the two-stage amplifier  $G_{m2}$ .

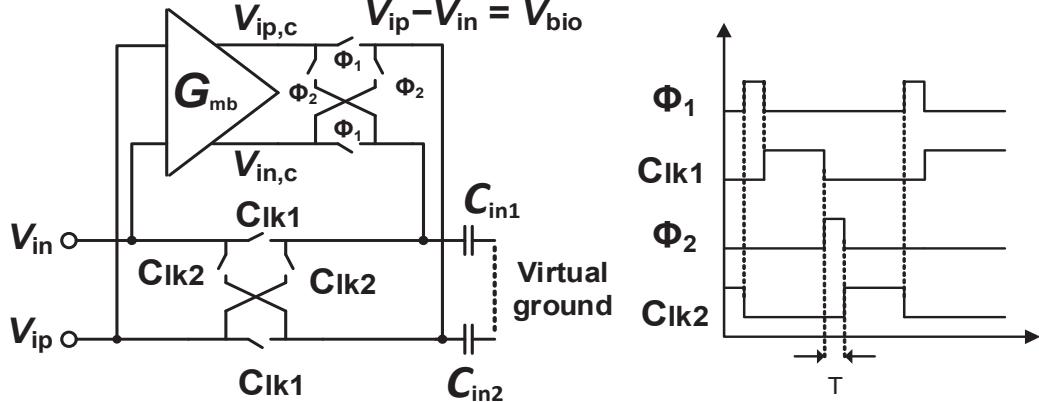

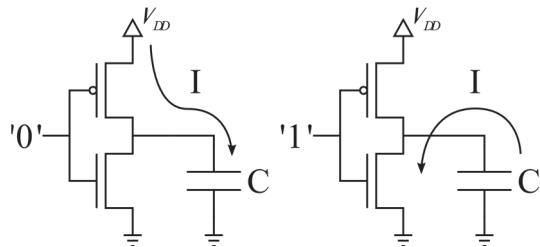

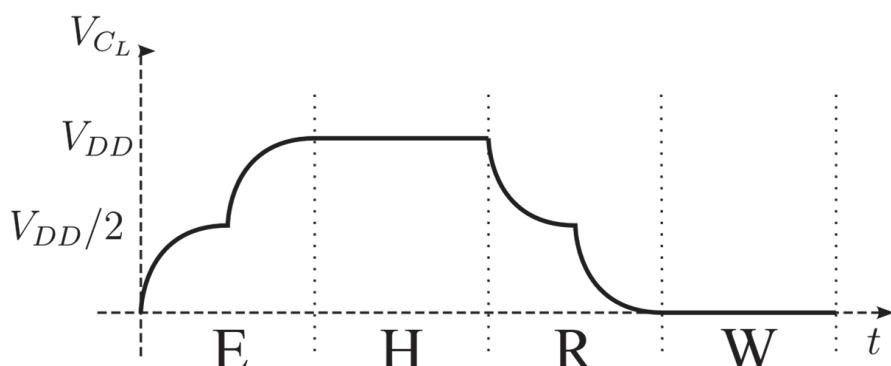

In the chopper biopotential amplifier, the input capacitor and the chopper are combined together, creating a switched capacitor resistor. At the completion of a cycle through the chopper clock  $f_{CH}$ , a charge of  $Q = 2C_{in}V_{in}$  is delivered [7]. Therefore,  $Z_{in}$  can be determined as  $Z_{in} = 1/(2C_{in}f_{CH})$ . For example,  $Z_{in}$  is  $2.5 \text{ M}\Omega$  for biomedical recording applications when the input capacitor  $C_{in} = 20$  pF and  $f_{CH} = 10$  kHz. An impedance boost loop (IBL) with a time diagram, as shown in Figure 3, is used to pre-charge  $Q$  to the  $C_{in}$ , as the  $Z_{in}$  must be improved by minimizing the charge  $Q$  from the input signal  $V_{in}$ . When the IBL is connected to  $C_{in}$ , the connection flowing from the input is interrupted and the  $V_{in}$  is copied by the buffer in IBL and is pre-charged to  $C_{in}$ . Assuming that the pre-charge current from the buffer is high enough,  $C_{in}$  will be fully charged from IBL; thus, when  $C_{in}$  is connected to the input after pre-charging,  $C_{in}$  does not require a charge from the

input signal  $V_{in}$ . This results in the fact that the  $Z_{in}$  can be set indefinitely. The  $Z_{in}$  can be represented following the analysis in [7], as follows:

$$Z_{in} = Z_0 / (\alpha + \exp(-T/\tau)) \quad (5)$$

where  $Z_{in}$  is the input impedance,  $Z_0$  is the input impedance without any boosting technique,  $\alpha$  is the buffer gain error,  $T$  is the pre-charge time, and  $\tau$  is the actual time constant.

Figure 3. Schematics of the IBL and time diagram of the CCIA.

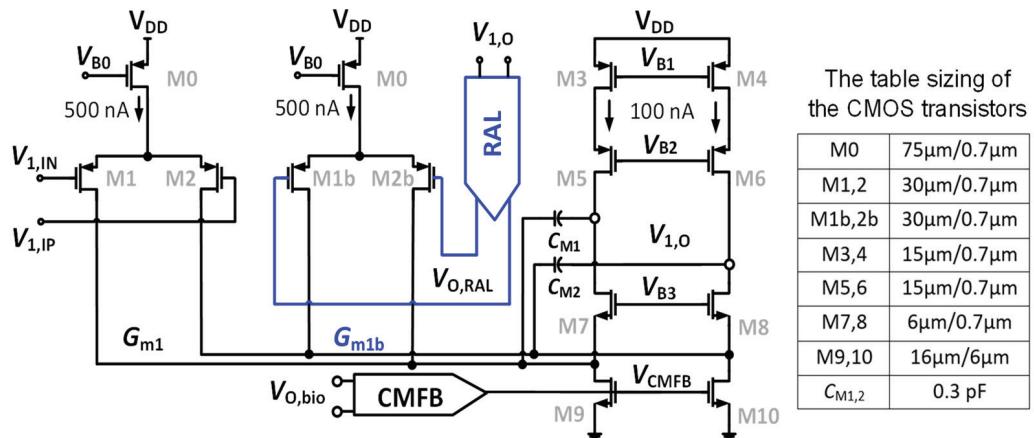

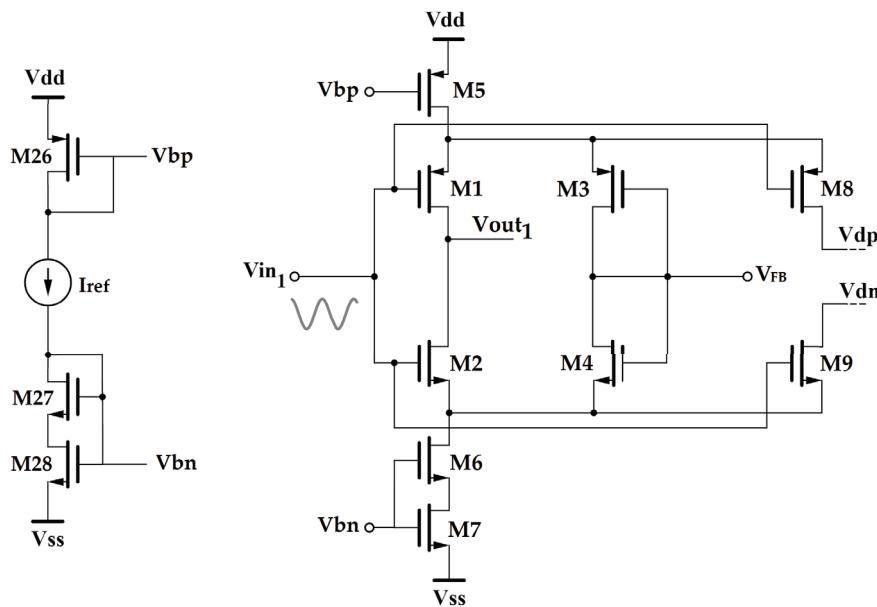

### 3. Circuit Implementation

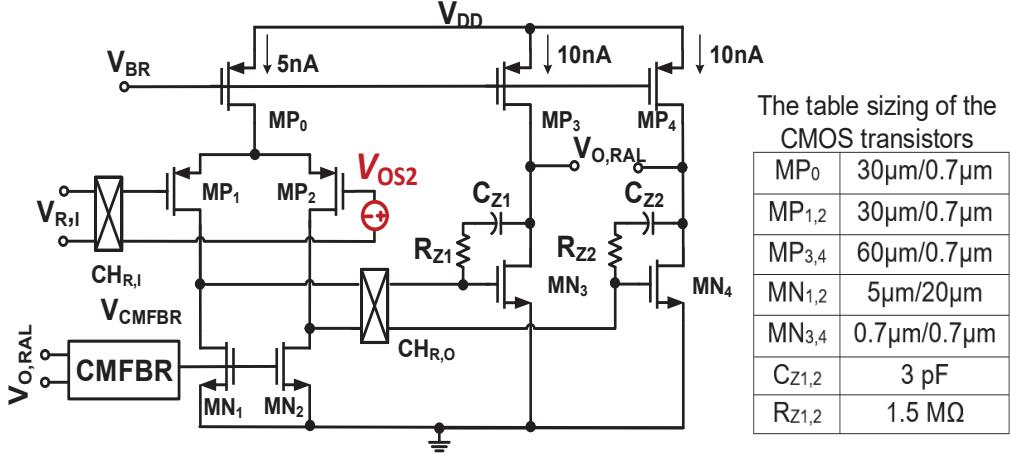

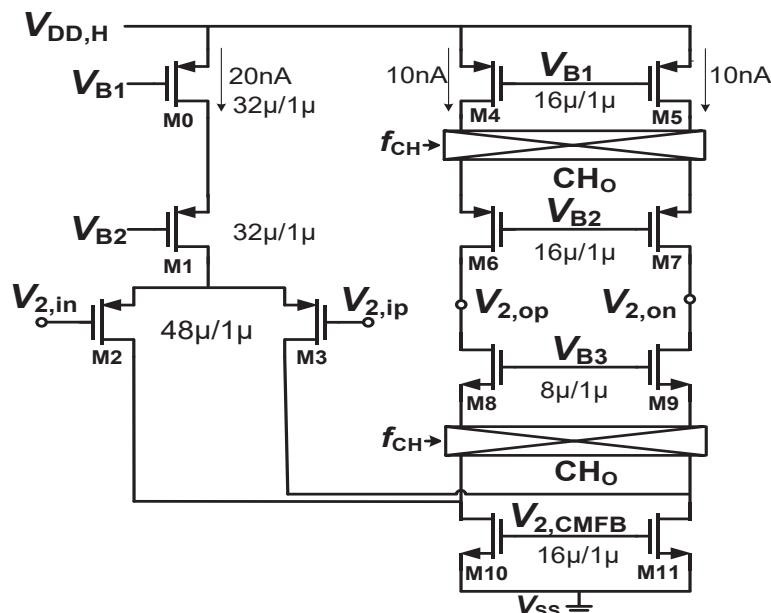

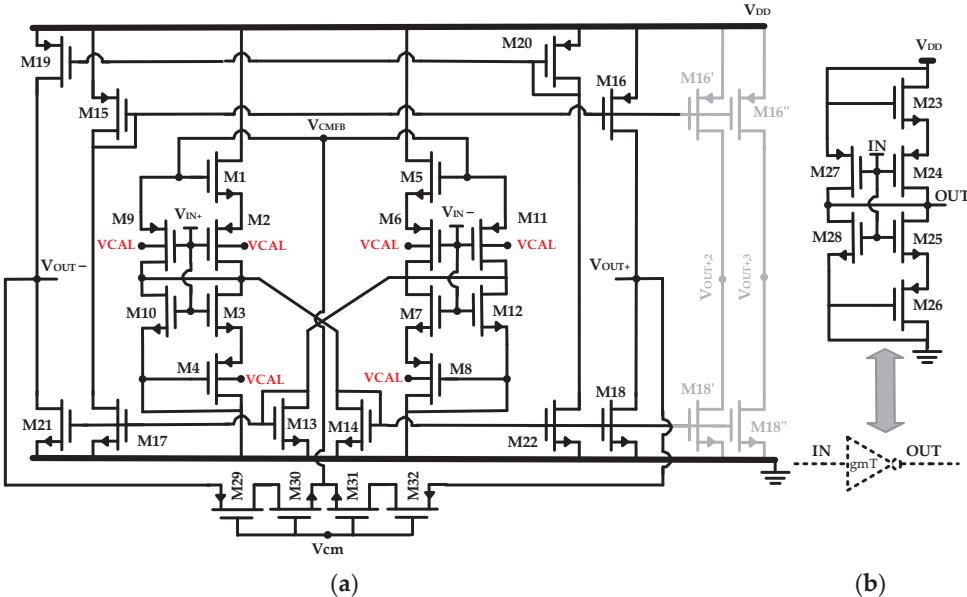

Figure 4 shows the dual cascode amplifier ( $G_{m1}$ ) combining with the RAL block. A feedback loop is set up comprising  $G_{m1b}$ , a two-stage chopper amplifier, and the RC-LPF in order to mitigate the output ripple. Figure 4 shows that the input stage consumes a power of  $1.2 \mu\text{W}$  from a supply voltage of  $1 \text{ V}$ . The global common mode feedback circuit (CMFB) [25], which is used and consumed a biased current of  $200 \text{ nA}$  from  $1 \text{ V}$ , is employed to control the DC voltage at the output node of the CCIA. The gates of the transistors  $M_9$  and  $M_{10}$  are adjusted using the CMFB circuit ( $V_{CMFB}$ ) to control the output DC voltage followed to  $V_{CM} = V_{DD}/2$ . The power consumption of  $1.4 \mu\text{W}$  of  $G_{m1}$  including CMFB is used.

Figure 4. Schematic of the two-folded cascode opamp  $G_{m1}$  with table sizing of CMOS transistors.

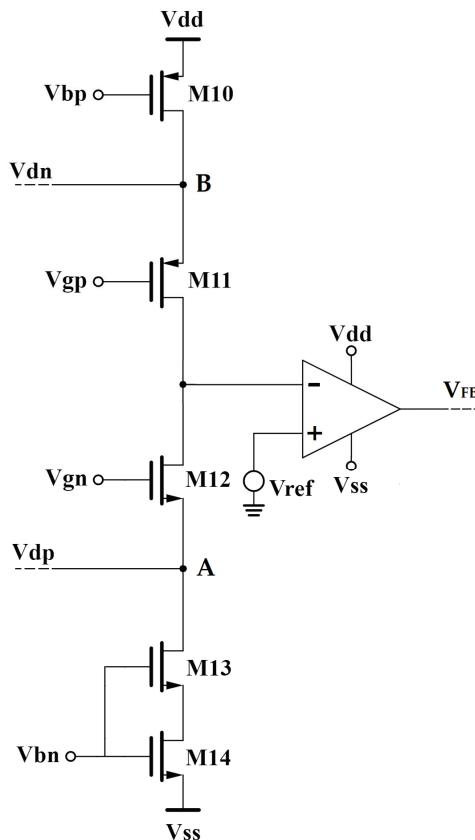

Figure 5 shows the architecture of the chopper two-stage amplifier integrating with a common mode feedback circuit (CMFBR) [25] for  $G_{m2}$ . As already mentioned, the inherent offset  $V_{OS2}$  of  $G_{m2}$  has the same effect as  $V_{OS1}$ ; the offset that is also upmodulated creates the ripple at the output of the CCIA. Consequently, it must be eliminated. In RAL, the chopper  $CH_{R,I}$  is located at the output of the LPF, while the chopper  $CH_{R,O}$  is put between the first and second stage of  $G_{m2}$ . This causes  $V_{OS2}$  to be modulated up to a high frequency

and then modulated down by the chopper  $CH_O$ , resulting in an offset voltage in the front of  $G_{m3}$ . Therefore,  $V_{OS2}$  is considered as an offset at the input of  $G_{m3}$ . Due to the high gain level of  $G_{m1}$  (about 80 dB), this offset is insignificant compared to the input. Therefore, its influence can be neglected. By using a 1 V supply, the first stage of  $G_{m2}$  consumes 5 nA, while the second stage of  $G_{m2}$  is biased to 20 nA for a better swing. The voltage  $V_{CMFBR}$  is generated by the CMFB circuit, which uses a bias current of 5 nA. Therefore, the total power of the RAL is only 30 nW.

Figure 5. Schematic of the chopper two-stage amplifier with table sizing of CMOS transistors.

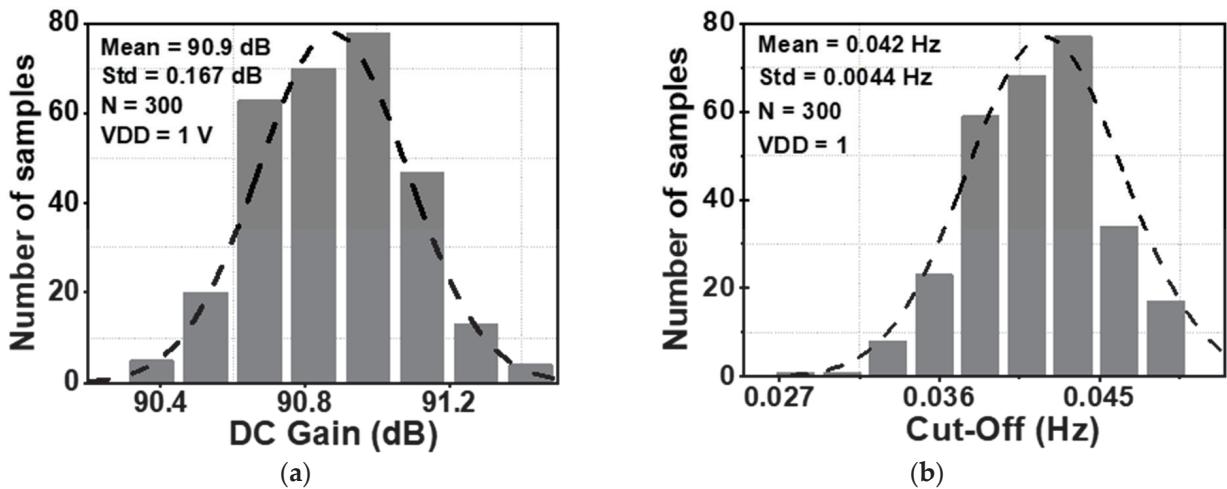

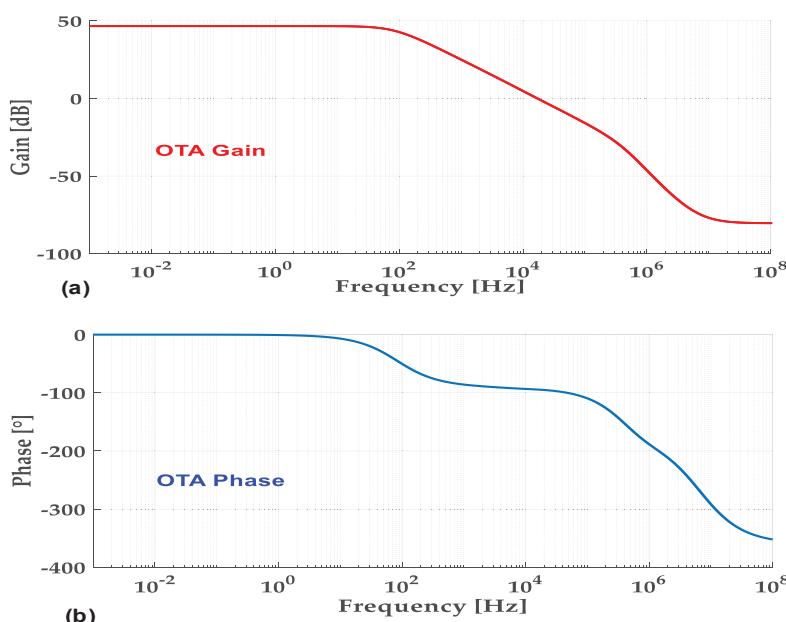

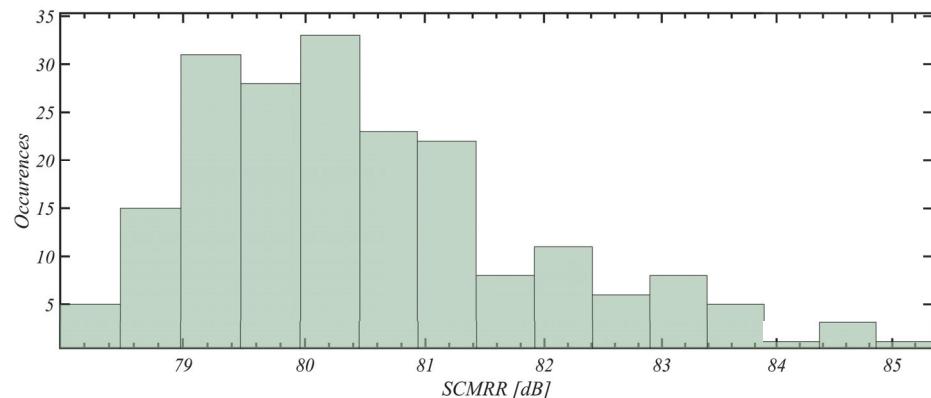

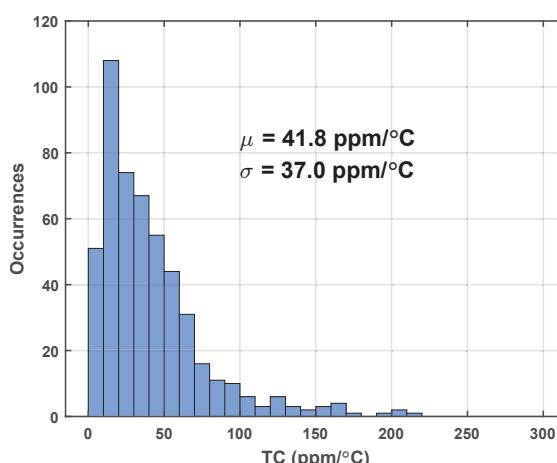

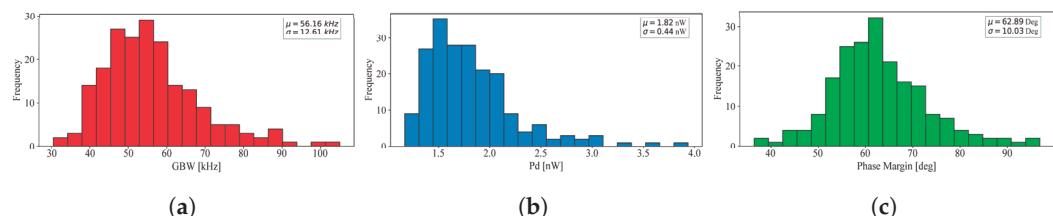

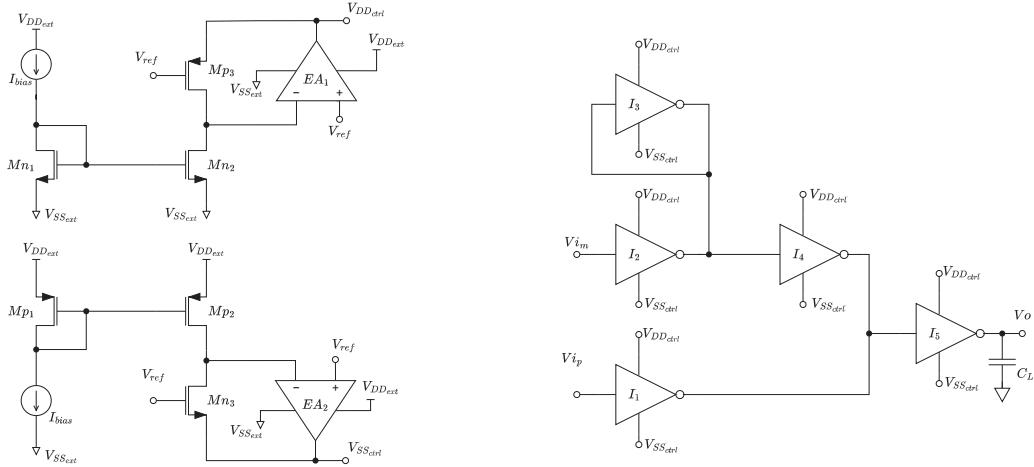

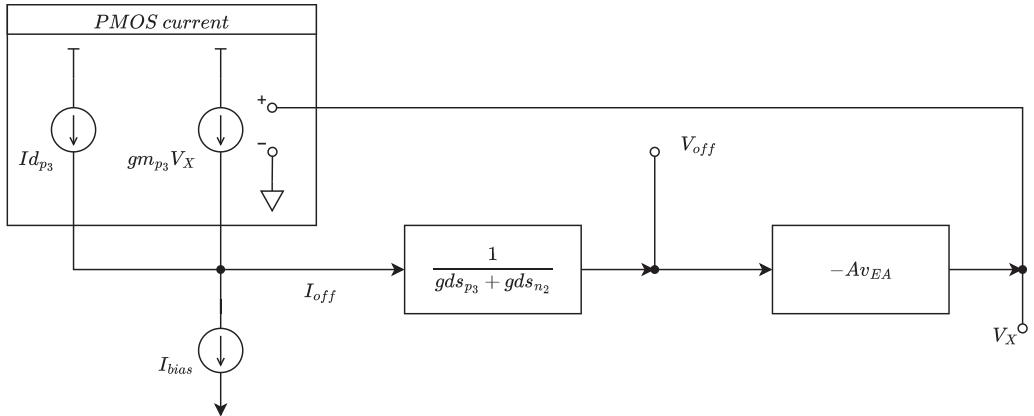

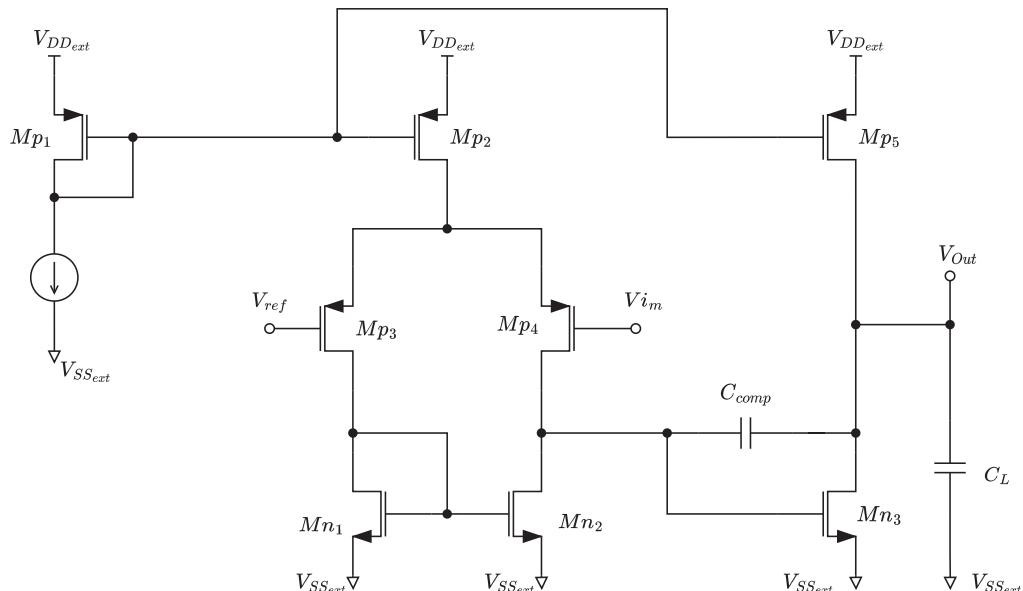

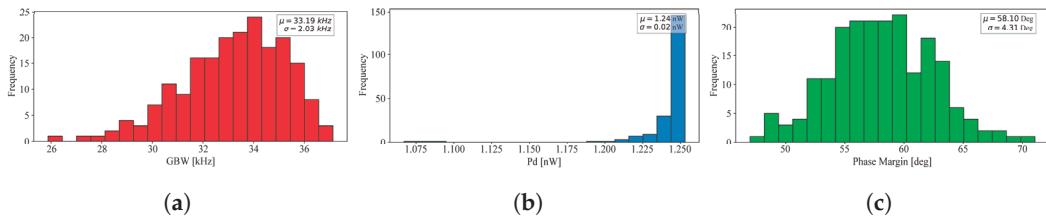

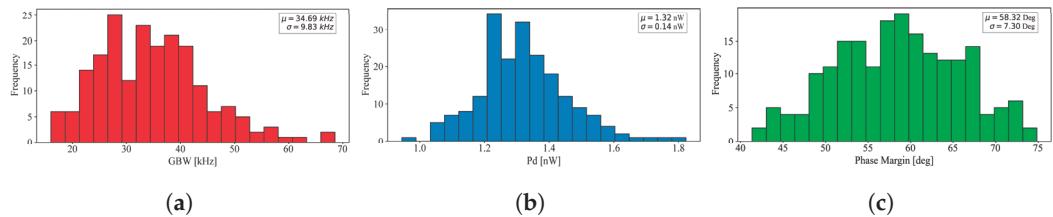

The DC gain and the cut-off frequency of  $G_{m2}$  are decisive factors for determining the ripple attenuation factor and the bandwidth of the loop gain. The Monte Carlo simulation (MCS) method is used to study the fluctuation of these parameters across the chip and the mismatch of the device, including global variation and local mismatch. Figure 6a and Figure 6b show the value of the DC gain and cut-off frequency of  $G_{m2}$ , respectively. These distributions were derived from 300 samples of the MCS. The results show a mean value (MV) of the DC gain of 90.9 dB, with a standard deviation (Std) of 0.167 dB. Furthermore, the MV of the cut-off frequency is 0.042 Hz with a Std of 0.0044 Hz.

Figure 6. Monte Carlo simulation results for (a) DC gain, and (b) cut-off frequency of  $G_{m2}$ .

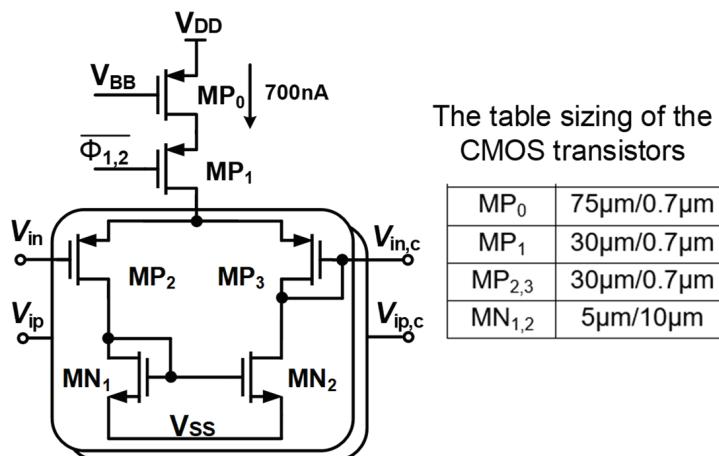

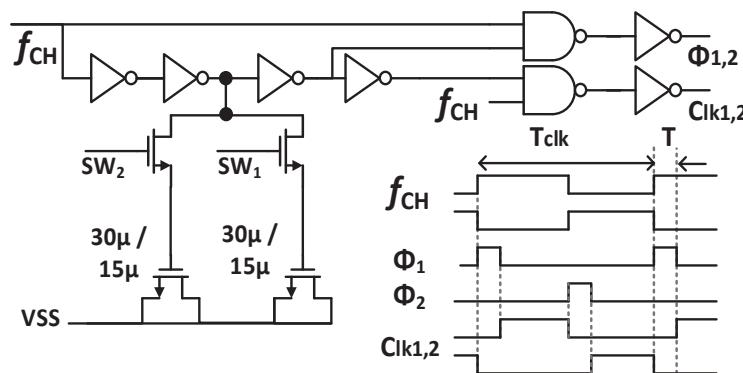

Figure 7 shows the schematic of the  $G_{mb}$  in the IBL. The MP0 and MP1 in  $G_{mb}$  are employed to bias and regulate the buffer with the purpose of reducing the impact of process variation on mismatch devices. The boosted input impedance in IBL can be affected by the pre-charge time  $T$ , the switches sizing of  $\Phi_{1,2}$ , and the buffer design. Figure 8 shows the clock generator for controlling the IBL. The pre-charge time  $T$  and  $C_{lk1,2}$  are generated by

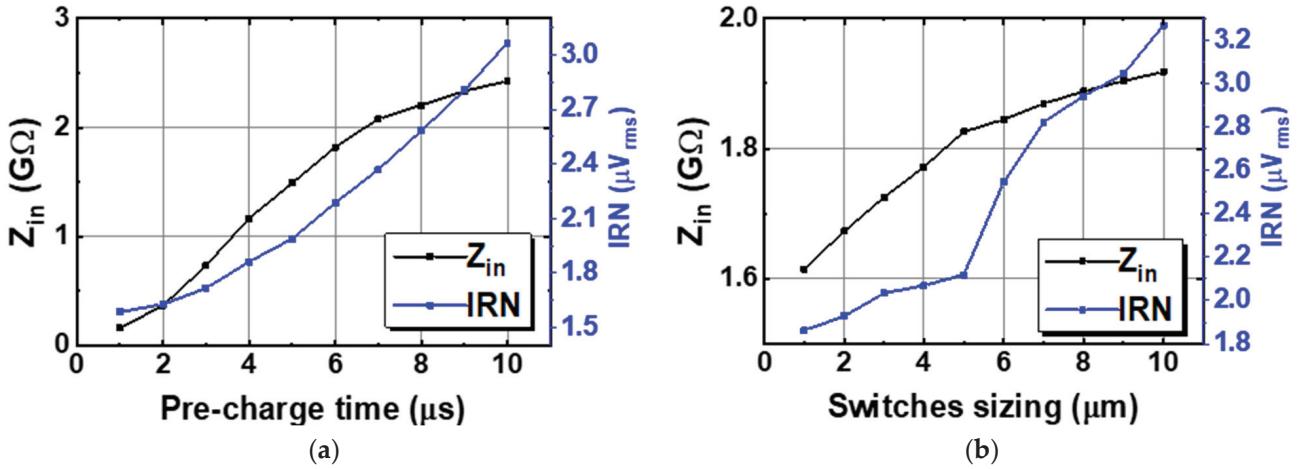

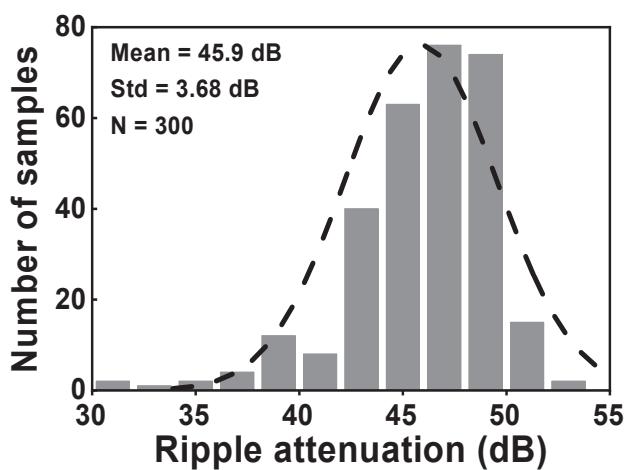

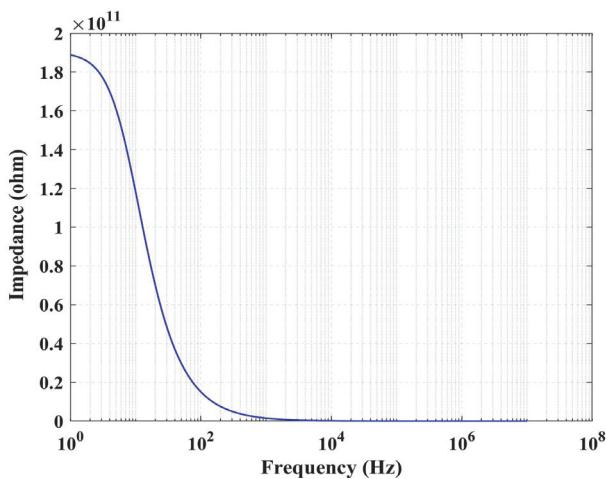

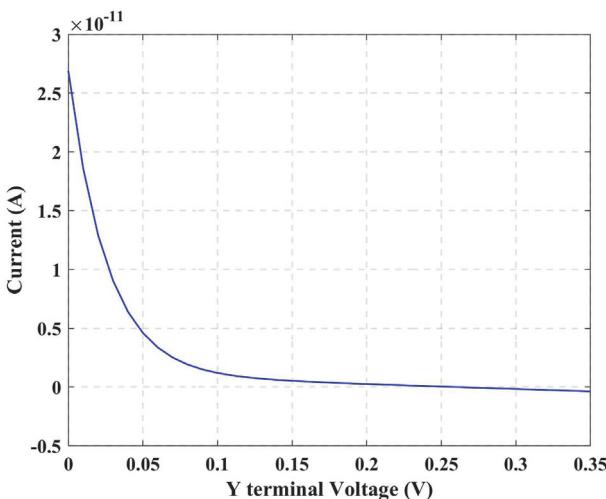

dividing the clock signal  $f_{CH}$ , which can be converted into a delayed signal by the use of several MOS capacitors and inverters. Although using a bias current of 700 nA, IBL is only enabled in 6  $\mu$ s in each cycle of 100  $\mu$ s ( $f_{CH} = 10$  kHz); thus, IBL ( $G_{mb}$ ) consumes only the current of  $700 \text{ nA} \times 6/100 = 42 \text{ nA}$ . The size and number of the MOS capacitor are shown in Figure 8. The sizing W/L of the switches  $SW_{1,2}$  is set at about 0.5  $\mu\text{m}/0.25 \mu\text{m}$  in order to minimize the inherent resistance. Furthermore, the pre-charge time  $T$  can be altered by using a two-switch  $SW_{1,2}$  in order to mitigate the effect of process variability. This research examines the effect of the pre-charge time  $T$  and the size of the switches  $\Phi_{1,2}$ . Lengthening the pre-charge time  $T$  enhances the  $Z_{in}$  of the device, while simultaneously amplifying the noise of the device. The size of switches  $\Phi_{1,2}$  in Figure 3 is another factor that affects the boost in  $Z_{in}$ . A small W/L size can result in a substantial voltage loss between these switches. Figure 9a and Figure 9b show the relationship between the  $Z_{in}$ , the input referred noise, the pre-charge time, and the switch sizing, respectively. As can be seen in Figure 9a, the  $Z_{in}$  improves from 2.5 M $\Omega$  to 0.7–1.8 G $\Omega$  when IBL is enabled with the pre-charge time  $T$  and is increased from 3 to 6  $\mu$ s; however, the IRN increases sharply from 1.7 to 2.2  $\mu\text{V}_{\text{rms}}$ . As shown in Figure 9b, when the switches sizing (Width-W) of  $\Phi_{1,2}$  increases, the parasitic capacitors of these switches are also increased. When clock control for the pre-charge phase is applied to the gate of the CMOS transistor switches, the charge injection noise and clock feed-through increases [26,27], leading to an increase in the IRN. In this work, when the width of the switches sizing of  $\Phi_{1,2}$  is changed from 1 to 5  $\mu\text{m}$ , the IRN is increased from 1.8 to 2.1  $\mu\text{V}_{\text{rms}}$ , while the noise increases from 2.5 to 3.2  $\mu\text{V}_{\text{rms}}$  when W of  $\Phi_{1,2}$  changes from 6 to 10  $\mu\text{m}$ . According to the simulated results, as shown in Figure 9, in order to optimize  $Z_{in}$  and IRN, the pre-charge time  $T$  and the switches sizing  $\Phi_{1,2}$  in this design are therefore set to 6  $\mu$ s and W/L is set to 5  $\mu\text{m}/0.5 \mu\text{m}$ .

Figure 7. The schematic of the circuit in IBL with table sizing of the CMOS transistors.

Figure 8. Schematic of a signal control generator for IBL.

**Figure 9.** The relation between input impedance and noise to (a) the pre-charge time, and (b) the switches sizing.

#### 4. Simulation Results

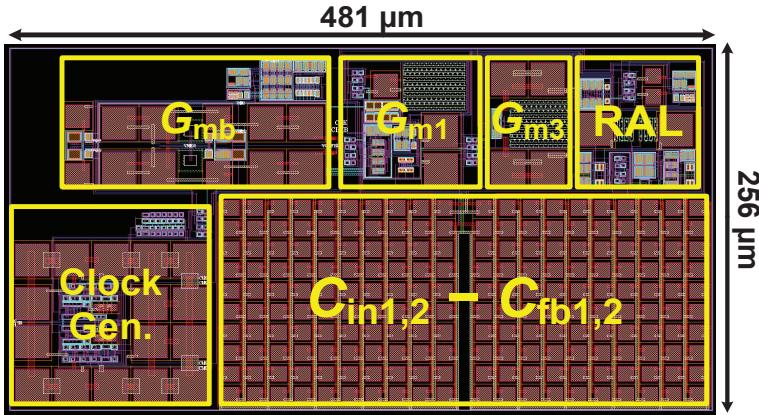

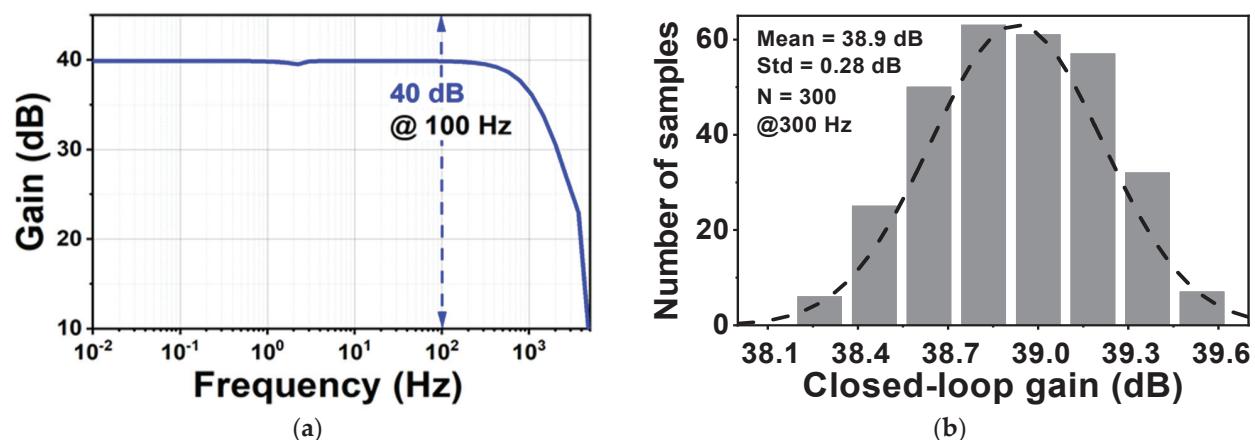

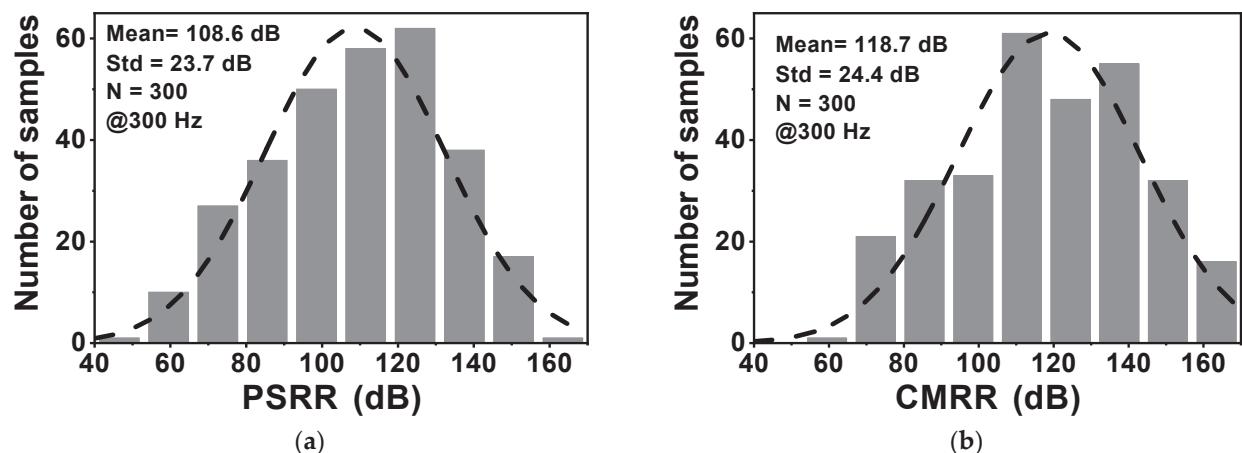

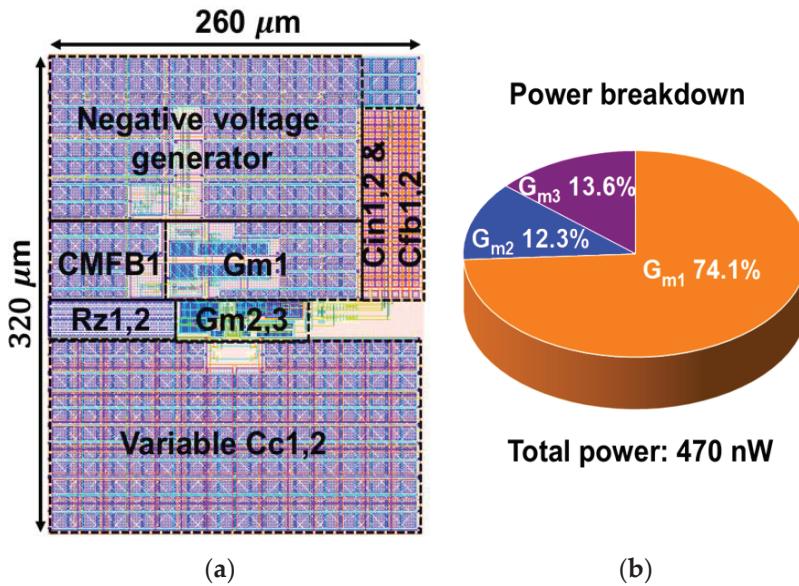

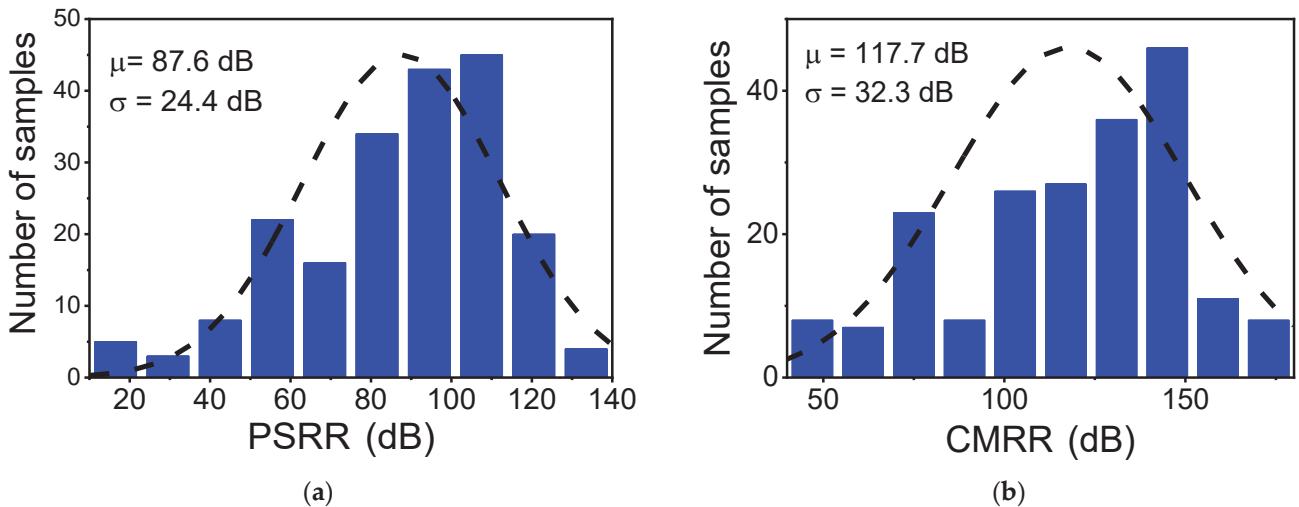

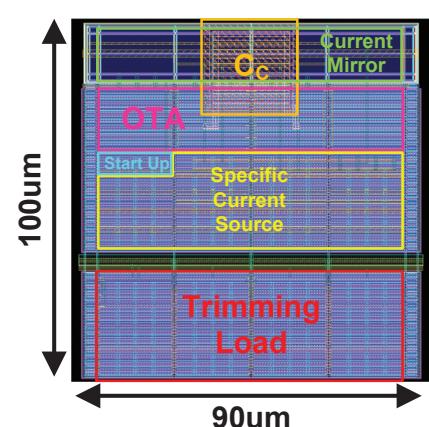

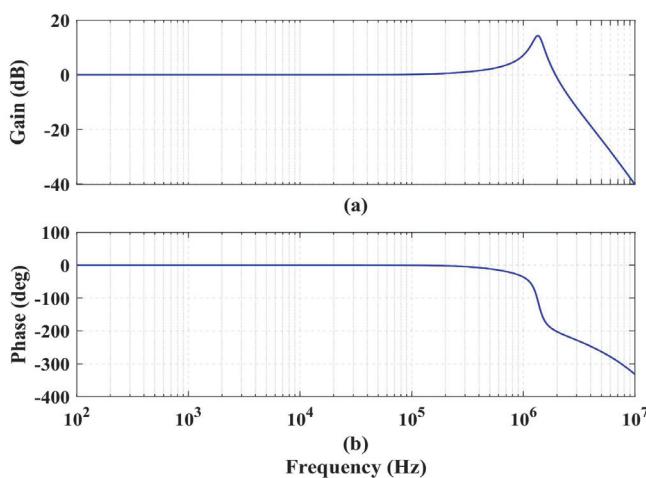

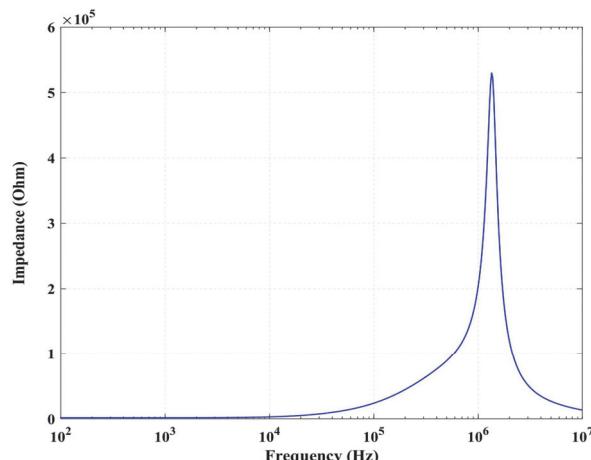

Figure 10 shows the layout of the proposed CCIA in the 180 nm CMOS process. The chip area of the CCIA configuration is 0.123 mm<sup>2</sup>. Table 1 shows the power dissipation of each block in the CCIA. The total power consumption of the proposed CCIA is 1.87  $\mu$ W from a  $V_{DD}$  of 1 V.  $G_{m1}$ ,  $G_{m2}$ ,  $G_{m3}$ , and  $G_{mb}$  consume 1400, 30, 400, and 40 nW, corresponding to 74.8%, 1.6%, 21.36%, and 2.24% of the total power consumption, respectively. According to the post-simulation results, it is shown that Figure 11 shows the simulated results of the CCIA's transfer function—(a) transient; (b) MCs. The CCIA's Av is 40 dB. The MCS results present that the MV of the closed-loop CCIA gain at 300 samples is 38.9 dB, with a Std of 0.28 dB. Figure 12 shows the MCS results for PSRR and CMRR after running 300 samples. At the 1 V supply, the MV of PSRR and CMRR are 108.6 and 118.7 dB with Stds of 23.7 and 24.4 dB, respectively.

**Figure 10.** The layout of the proposed CCIA.

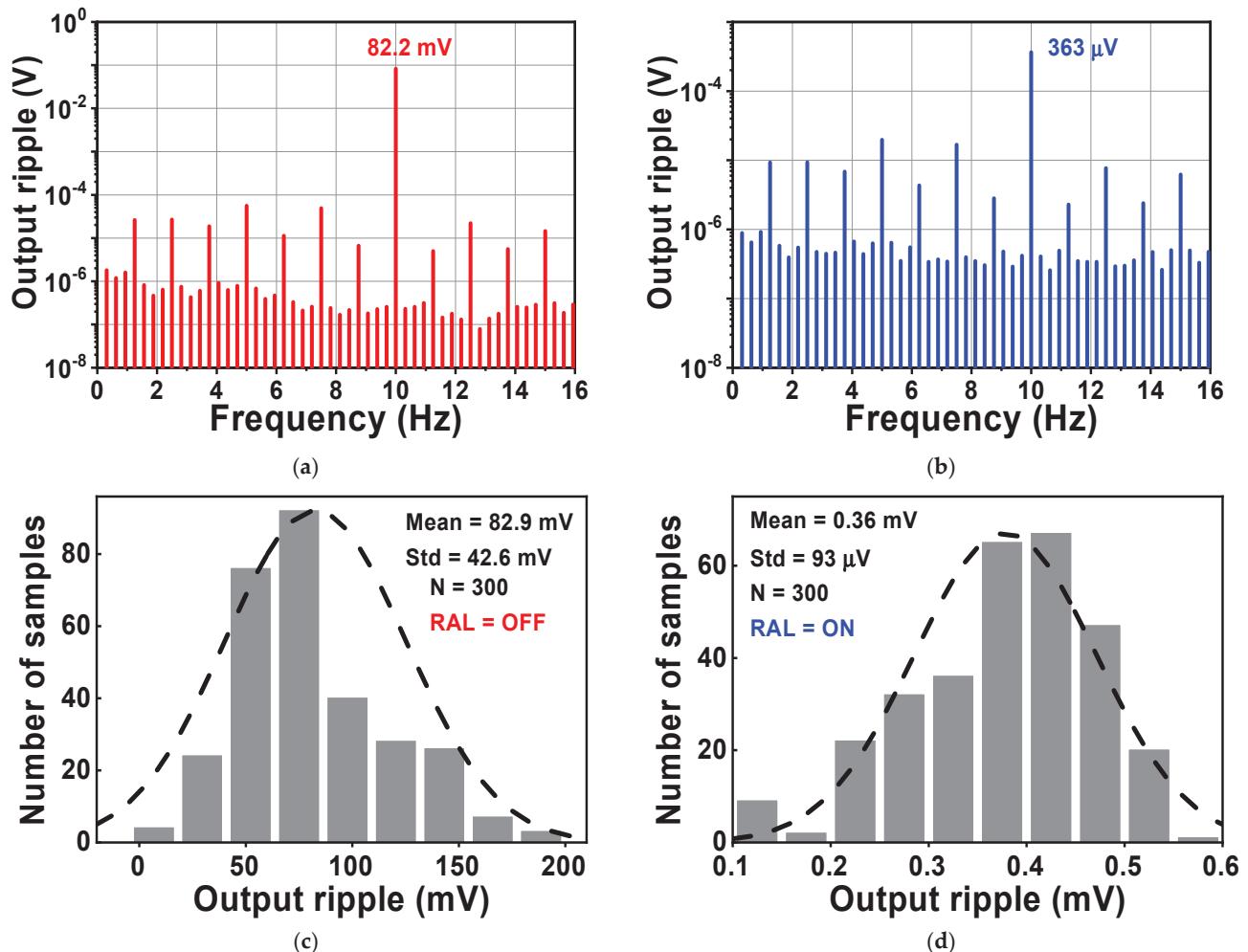

During the simulation, the input of the CCIA is configured so that it is short-circuited in order to test the output spectrum. Both  $V_{OS1}$  and  $V_{OS2}$  were set to a voltage of 5 mV. Figure 13 shows the simulated results of the voltage spectrum and the MCS of the output ripple. When the RAL is disabled, the amplitude of the output spectrum at the chopping frequency is about 82.2 mV, as shown in Figure 13a. The amplitude of the output ripple of the CCIA decreases to 0.36 mV when the RAL is enabled, as shown in Figure 13b. The output ripple is verified using an MCS that includes 300 samples and accounts for both local and global process variations. When the RAL level is changed from off to on, the MV of the output ripple decreases from 82.9 mV to 0.36 mV with a Std of 42.6 mV or 93  $\mu$ V, as

shown in Figure 13c,d. The simulation results shown in Figure 14 therefore give an MV of 45.9 for the ripple attenuation, with a Std of 3.68 dB. The proposed feedback network effectively compensates for the offset voltage ( $V_{OS1}, V_{OS2}$ ) caused by mismatches due to process, voltage, and temperature variations, resulting in a significant reduction in the output ripple voltage.

**Table 1.** The power dissipation of each block of the proposed CCIA.

| Block                | Circuit     | Components        | Power Dissipation (nW) |

|----------------------|-------------|-------------------|------------------------|

| Dual_FC ( $G_{m1}$ ) | OPA-Dual FC | Differential Pair | 500                    |

|                      |             | Differential Pair | 500                    |

|                      |             | Cascode Branches  | 200                    |

|                      | CMFB        |                   | 200                    |

| CS ( $G_{m3}$ )      | OPA-CS      | Common source     | 400                    |

|                      | Stage-1     | Differential Pair | 5                      |

| RAL ( $G_{m2}$ )     | Stage-2     | Common source     | 20                     |

|                      |             | CMFB2             | 5                      |

| IBL ( $G_{mb}$ )     | Buffer      |                   | 42                     |

|                      | Total       |                   | 1872                   |

**Figure 11.** (a) The transient of the proposed CCIA's transfer function; (b) MCS result of the proposed CCIA's transfer function.

**Figure 12.** The MCS results of (a) PSRR; (b) CMRR.

**Figure 13.** The simulated results of the voltage spectrum and MCS of the output ripple when RAL (a,c) is disabled, or (b,d) enabled.

**Figure 14.** The MCS of the ripple attenuation result.

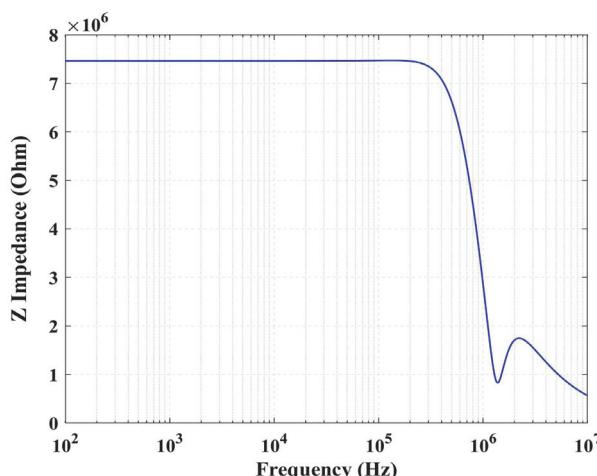

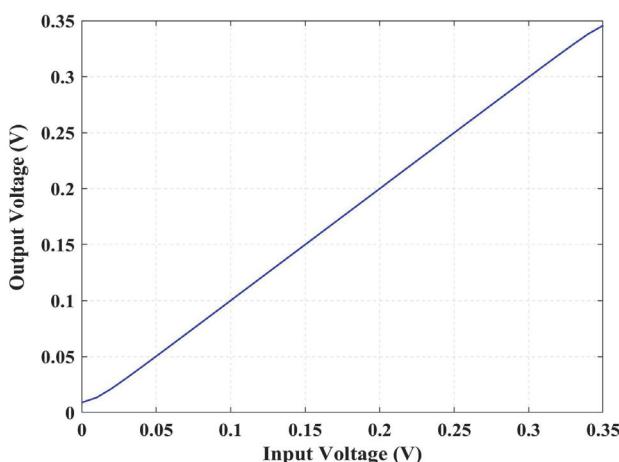

Figure 15 shows the effects of activating the impedance boost loop on the  $Z_{in}$  and the input-related noise. By setting the  $SW_{1,2}$  parameter, it is possible to achieve different results for the input impedance. When  $SW_{1,2}$  is set to 01 and 11, corresponding to a pre charge time of 3 and 6  $\mu$ s, the  $Z_{in}$  in the low frequency range increases to about 0.7 and 1.8 G $\Omega$ , respectively, as shown in Figure 15a. Without the presence of IBL, the noise floor is

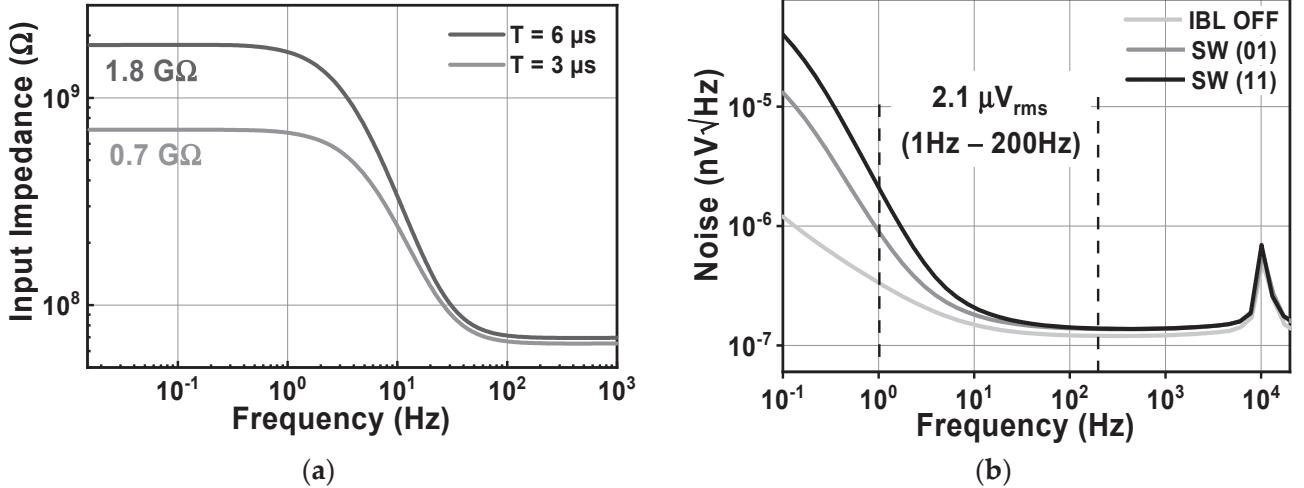

about  $119 \text{ nV}/\sqrt{\text{Hz}}$ , while the  $1/f$  corner frequency is 10 Hz. When IBL is enabled, the noise floor increases to  $136 \text{ nV}/\sqrt{\text{Hz}}$ , resulting in an IRN over a bandwidth of 1 to 200 Hz of  $2.16 \mu\text{V}_{\text{rms}}$ . This increase is observed for different values of  $\text{SW}_{1,2}$ , which determines the pulse width of the pre-charge time. Figure 16a shows the variation of IRN for the proposed amplifier across several process corners, ranging from 1.9 to 2.6  $\mu\text{V}_{\text{rms}}$ . On the other hand, Figure 16b shows the MV of IRN, which is  $2.16 \mu\text{V}_{\text{rms}}$ , with a Std of  $97.9 \text{ nV}_{\text{rms}}$ , verified using an MCS with 300 samples, considering both local and global process variations.

Figure 15. The simulated results of (a) the CCIA's input impedance; (b) the CCIA's noise.

Figure 16. The simulated result of (a) the CCIA's noise across several process corners and (b) the CCIA's noise.

Table 2 shows a brief summary of the primary design specifications, encompassing power consumption, output ripple's amplitude,  $Z_{\text{in}}$ , CMRR, PSRR, and NEF (noise efficient factor). There are several references that show simulation results, such as [24,28,29], in order to guarantee an equitable comparison. Table 2 is employed to evaluate the performance of the proposed design in comparison with the current state-of-the-art studies. The proposed CCIA obtains an NEF of about 7.5 by integrating RAL and IBL. Additionally, it exhibits a minimal output ripple of  $363 \mu\text{V}$  and a significant  $Z_{\text{in}}$  of  $1.8 \text{ G}\Omega$ . The CCIA's dissipation is  $1.87 \mu\text{W}$  from a  $1 \text{ V}$  supply.

**Table 2.** Performance comparison.

| Ref.                                 | [18]  | [23]  | [24] | [28]  | [29] | [30]   | [31]  | This Work |

|--------------------------------------|-------|-------|------|-------|------|--------|-------|-----------|

| Year                                 | 2017  | 2021  | 2024 | 2022  | 2020 | 2021   | 2019  | 2024      |

| Power ( $\mu\text{W}$ )              | 2     | 5.94  | 1.5  | 1.21  | 19.8 | 0.672  | 1.2   | 1.87      |

| Supply (V)                           | 1.2   | 1.8   | 2.47 | 1     | 1.8  | 2      | 5     | 1         |

| Output ripple (mV)                   | 0.012 | NA    | NA   | 0.061 | NA   | NA     | NA    | 0.36      |

| Ripple Attenuation (dB)              | NA    | NA    | NA   | >41   | NA   | NA     | NA    | 45.9      |

| $Z_{\text{in}}$ ( $\text{G}\Omega$ ) | 0.3   | 2.6   | NA   | NA    | 2.1  | 0.0575 | 400   | 1.8       |

| Gain (dB)                            | 25.7  | 40    | 59.7 | 40    | 46   | 40.6   | 20    | 40        |

| PSRR (dB)                            | NA    | 85    | >70  | 87    | NA   | 84.2   | N/A   | 108.6     |

| CMRR (dB)                            | NA    | 93    | >87  | 108   | 96   | 83.24  | >70   | 118.7     |

| IRN ( $\mu\text{V}_{\text{rms}}$ )   | 9     | 1.4   | 1.18 | 1.8   | 1.9  | 2.01   | 3.7   | 2.16      |

| NEF                                  | 7     | NA    | 2.13 | 5.4   | NA   | 2.63   | NA    | 7.5       |

| Tech. (nm)                           | 40    | 180   | 130  | 180   | 180  | 350    | 180   | 180       |

| Meas./Sim.                           | Meas. | Meas. | Sim. | Sim.  | Sim. | Meas.  | Meas. | Sim.      |

## 5. Conclusions

The paper presents a 1.87  $\mu\text{W}$  capacitively coupled chopper instrumentation amplifier for biomedical recording. The output ripple is measured at 0.36 mV, and the input impedance is 1.8  $\text{G}\Omega$ . The CCIA chip occupies a chip area of only 0.123  $\text{mm}^2$  when implemented in a 0.18  $\mu\text{m}$  CMOS technology. The ripple attenuation loop effectively decreases the output ripple of the proposed CCIA down to 0.36 mV. The CCIA is able to achieve a high input impedance of approximately 1.8  $\text{G}\Omega$  due to the impedance boosting loop. The low-power chopper amplifier has a power dissipation of 1.87  $\mu\text{W}$  at a  $V_{\text{DD}}$  of 1 V. It also obtains a closed-loop gain of 40 dB, a PSRR of 108.6 dB, and a CMRR of 118.7 dB. The noise floor of the CCIA has a magnitude of 136  $\text{nV}/\sqrt{\text{Hz}}$ , which leads to an IRN of 2.16  $\mu\text{V}_{\text{rms}}$  across a bandwidth of 200 Hz. Thus, an NEF value of 7.5 is attained. This illustrates our ability to evaluate the performance of the proposed CCIA by comparing it to the most recent studies.

**Author Contributions:** Conceptualization, X.P.T., X.T.P., X.T.K. and M.K.H.; methodology, X.P.T., X.T.K., D.P.P. and M.K.H.; software, X.P.T. and X.T.P.; formal analysis, X.T.K., D.P.P. and M.K.H.; writing—original draft preparation, X.P.T.; writing—review and editing, X.T.K., D.P.P. and M.K.H.; visualization, X.T.P., D.P.P. and M.K.H.; supervision, X.T.K. and M.K.H.; project administration, X.P.T.; funding acquisition, X.P.T., X.T.P., X.T.K. and M.K.H. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research received no external funding.

**Data Availability Statement:** The data presented in this study are available in this article.

**Conflicts of Interest:** The authors declare no conflicts of interest.

## References

- Tran, X.P.; Pham, X.T.; Kieu, X.T.; Nguyen, L.C.; Pham, D.P.; Hoang, M.K. A 1.8- $\text{G}\Omega$  Input Impedance 45-dB Ripple Reduction Factor Chopper Amplifier for Biomedical Recording. In Proceedings of the 2023 International Conference on Advanced Technologies for Communications (ATC), Da Nang, Vietnam, 19–21 October 2023.

- Wang, S.; Koickal, T.J.; Hamilton, A.; Mastropaoolo, E.; Cheung, R.; Abel, A.; Smith, L.S.; Wang, L. A Power-Efficient Capacitive Read-Out Circuit With Parasitic-Cancellation for MEMS Cochlea Sensors. *IEEE Trans. Biomed. Circuits Syst.* **2016**, *10*, 25–37. [CrossRef] [PubMed]

3. Jiang, X.; Bian, G.-B.; Tian, Z. Removal of artifacts from EEG signals: A review. *Sensors* **2019**, *19*, 987. [CrossRef] [PubMed]

4. Lin, C.T.; Ko, L.W.; Chang, M.H.; Duann, J.R.; Chen, J.Y.; Su, T.P.; Jung, T.P. Review of wireless and wearable electroencephalogram systems and brain-computer interfaces-a mini-review. *Gerontology* **2010**, *56*, 112–119. [CrossRef] [PubMed]

5. Fiedler, P.; Mühle, R.; Griebel, S.; Pedrosa, P.; Fonseca, C.; Vaz, F.; Zanow, F.; Haueisen, J. Contact Pressure and Flexibility of Multipin Dry EEG Electrodes. *IEEE Trans. Neural Syst. Rehabil. Eng.* **2018**, *26*, 750–757. [CrossRef] [PubMed]

6. Nguyen, V.-N.; Pham, X.T.; Lee, J.-W. Three-Step Cyclic Vernier TDC Using a Pulse-Shrinking Inverter-Assisted Residue Quantizer for Low-Complexity Resolution Enhancement. *IEEE Trans. Instrum. Meas.* **2021**, *70*, 1–12. [CrossRef]

7. Chandrakumar, H.; Marković, D. A high dynamic-range neural recording chopper amplifier for simultaneous neural recording and stimulation. *IEEE J. Solid-State Circuits* **2017**, *52*, 645–656. [CrossRef]

8. Pham, X.T.; Kieu, X.T.; Hoang, M.K. Ultra-Low Power Programmable Bandwidth Capacitively-Coupled Chopper Instrumentation Amplifier Using 0.2 V Supply for Biomedical Applications. *J. Low Power Electron. Appl.* **2023**, *13*, 37. [CrossRef]

9. Xu, J.; Lin, Q.; Ding, M.; Li, Y.; Van Hoof, C.; Serdijn, W.; Van Helleputte, N. A 0.6V 3.8 $\mu$ W ECG/bio-impedance monitoring IC for disposable health patch in 40nm CMOS. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018.

10. Yaul, F.M.; Chandrakasan, A.P. A noise-efficient 36 nV/  $\sqrt{\text{Hz}}$  chopper amplifier using an inverter-based 0.2-V supply input stage. *IEEE J. Solid-State Circuits* **2017**, *52*, 3032–3042. [CrossRef]

11. Huang, G.; Yin, T.; Wu, Q.; Zhu, Y.; Yang, H. A 1.3 $\mu$ W 0.7 $\mu$ VRMS chopper current-reuse instrumentation amplifier for EEG applications. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015.

12. Wu, R.; Makinwa, K.A.A.; Huijsing, J.H. A Chopper Current-Feedback Instrumentation Amplifier With a 1 mHz 1/f Noise Corner and an AC-Coupled Ripple Reduction Loop. *IEEE J. Solid-State Circuits* **2009**, *44*, 3232–3243. [CrossRef]

13. Park, J.H.; Tang, T.; Zhang, L.; Ng, K.A.; Gammad, G.G.L.; Yen, S.C.; Yoo, J. A 15-Channel Orthogonal Code Chopping Instrumentation Amplifier for Area-Efficient, Low-Mismatch Bio-Signal Acquisition. *IEEE J. Solid-State Circuits* **2020**, *55*, 2771–2780. [CrossRef]

14. Nasseriana, M.; Peiravia, A.; Moradi, F. A fully-integrated 16-channel EEG readout front-end for neural recording applications. *AEU—Int. J. Electron. Commun.* **2018**, *94*, 109–121. [CrossRef]

15. Li, J.; Zhu, L.; Su, R.; Wang, W.; Zhou, Y.; Xie, S.; Mao, G.; Zhou, Z. A Capacitively Coupled Chopper Instrumentation Amplifier With Deadtime Offset Reduction Technique for Neural Signal Sensing. *IEEE Sens. Lett.* **2024**, *8*, 1–4. [CrossRef]

16. Zheng, J.; Ki, W.-H.; Hu, L.; Tsui, C.-Y. Chopper capacitively coupled instrumentation amplifier capable of handling large electrode offset for biopotential recordings. *IEEE Trans. Circuits Syst. II Express Briefs* **2017**, *64*, 1392–1396. [CrossRef]

17. Wu, J.; Law, M.K.; Mak, P.I.; Martins, R.P. A 2- $\mu$ W 45-nV/  $\sqrt{\text{Hz}}$  readout front end with multiple-chopping active-high-pass ripple reduction loop and pseudo feedback DC servo loop. *IEEE Trans. Circuits Syst. II Express Briefs* **2016**, *63*, 351–355.

18. Chandrakumar, H.; Marković, D. An 80-mVpp Linear-Input Range, 1.6- G $\Omega$  Input Impedance, Low-Power Chopper Amplifier for Closed-Loop Neural Recording That Is Tolerant to 650-mVpp Common-Mode Interference. *IEEE J. Solid-State Circuits* **2017**, *52*, 2811–2828. [CrossRef]

19. Zheng, J.; Ki, W.H.; Tsui, C.Y. Analysis and design of ripple reduction chopper bandpass amplifier. *IEEE Trans. Circuits Syst. I Reg. Pap.* **2018**, *65*, 1185–1195. [CrossRef]

20. Chandrakumar, H.; Marković, D. A simple area-efficient ripple rejection technique for chopped biosignal amplifiers. *IEEE Trans. Circuits Syst. II Express Briefs* **2015**, *62*, 189–193. [CrossRef]

21. Fang, L.; Gui, P. A Low-Noise Low-Power Chopper Instrumentation Amplifier With Robust Technique for Mitigating Chopping Ripples. *IEEE J. Solid-State Circuits* **2022**, *57*, 1800–1811. [CrossRef]

22. Luo, D.; Zhang, M.; Wang, Z. A Low-Noise Chopper Amplifier Designed for Multi-Channel Neural Signal Acquisition. *IEEE J. Solid-State Circuits* **2019**, *54*, 2255–2265. [CrossRef]

23. Wenfei, C.; Yi, L.; Shubin, L.; Ling, W.; Rui, M.; Zhangming, Z. A 2.6 G $\Omega$ , 1.4  $\mu$ Vrms current-reuse instrumentation amplifier for wearable electrocardiogram monitoring. *Microelectron. J.* **2021**, *107*, 1049.

24. Chen, X.; Mo, T.; Wu, P.; Wu, B. A Capacitive-Feedback Amplifier with 0.1% THD and 1.18  $\mu$ Vrms Noise for ECG Recording. *Electronics* **2024**, *13*, 378. [CrossRef]

25. Baker, R.J. *CMOS Circuit Design, Layout, and Simulation*; Wiley: Hoboken, NJ, USA, 2010.

26. Xu, J.; Fan, Q.; Huijing, J.H.; Hoof, C.V.; Yazicioglu, R.F.; Makinwa, K.A.A. Measurement and Analysis of Current Noise in Chopper Amplifiers. *IEEE J. Solid-State Circuits* **2013**, *48*, 1575–1584.

27. Ha, H.; Hoof, C.V.; Helleputte, N.V. Measurement and Analysis of Input-Signal Dependent Flicker Noise Modulation in Chopper Stabilized Instrumentation Amplifier. *IEEE Solid-State Circuits Lett.* **2018**, *4*, 90–93. [CrossRef]

28. Pham, X.T.; Vu, T.K.; Nguyen, T.D.; Pham-Nguyen, L. A 1.2- $\mu$ W 41-dB Ripple Attenuation Chopper Amplifier Using Auto-Zero Offset Cancelation Loop for Area-Efficient Biopotential Sensing. *Electronics* **2022**, *11*, 1149. [CrossRef]

29. Xu, W.; Wang, T.; Wei, X.; Yue, H.; Wei, B.; Duan, J.; Li, H. Low Noise, High Input Impedance Digital-Analog Hybrid Offset Suppression Amplifier for Wearable Dry Electrode ECG Monitoring. *Electronics* **2020**, *9*, 165. [CrossRef]

30. Sawigun, C.; Thanapitak, S. A Compact Sub- $\mu$ W CMOS ECG Amplifier With 57.5-M $\Omega$  Zin, 2.02 NEF, 8.16 PEF and 83.24-dB CMRR. *IEEE Trans. Biomed. Circuits Syst.* **2021**, *15*, 549–558. [CrossRef]

31. Chen, M.; Chun, H.S.; Castro, I.D.; Torfs, T.; Lin, Q.; Van Hoof, C.; Wang, G.; Lian, Y.; Van Helleputte, N. A 400 G $\Omega$  Input-Impedance Active Electrode for Non-Contact Capacitively Coupled ECG Acquisition With Large Linear-Input-Range and High CM-Interference-Tolerance. *IEEE Trans. Biomed. Circuits Syst.* **2019**, *13*, 2. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Article

# Ultra-Low Power Programmable Bandwidth Capacitively-Coupled Chopper Instrumentation Amplifier Using 0.2 V Supply for Biomedical Applications

Xuan Thanh Pham, Xuan Thuc Kieu and Manh Kha Hoang \*

Faculty of Electronics Engineering, Hanoi University of Industry, Hanoi 10000, Vietnam;

thanhp@hau.edu.vn (X.T.P.); thuckx@hau.edu.vn (X.T.K.)

\* Correspondence: khahoang@hau.edu.vn; Tel.: +84-243765-5121

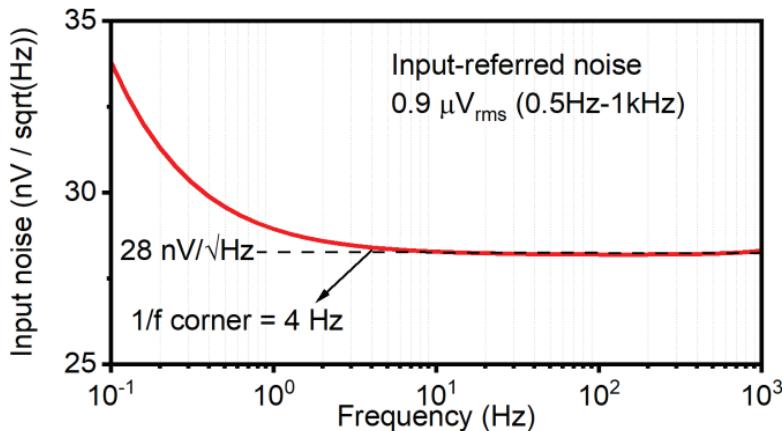

**Abstract:** This paper presents a capacitively coupled chopper instrumentation amplifier (CCIA) with ultra-low power consumption and programmable bandwidth for biomedical applications. To achieve a flexible bandwidth from 0.2 to 10 kHz without additional power consumption, a programmable Miller compensation technique was proposed and used in the CCIA. By using a Squeezed inverter amplifier (SQI) that employs a 0.2-V supply, the proposed CCIA addresses the primary noise source in the first stage, resulting in high noise power efficiency. The proposed CCIA is designed using a 0.18  $\mu$ m CMOS technology process and has a chip area of 0.083 mm<sup>2</sup>. With a power consumption of 0.47  $\mu$ W at 0.2 and 0.8 V supply, the proposed amplifier architecture achieves a thermal noise of 28 nV/ $\sqrt{\text{Hz}}$ , an input-related noise (IRN) of 0.9  $\mu$ V<sub>rms</sub>, a closed-loop gain ( $A_V$ ) of 40 dB, a power supply rejection ratio (PSRR) of 87.6 dB, and a common-mode rejection ratio (CMRR) of 117.7 dB according to post-simulation data. The proposed CCIA achieves a noise efficiency factor (NEF) of 1.47 and a power efficiency factor (PEF) of 0.56, which allows comparison with the latest research results.

**Keywords:** ultra-low power; low noise; chopper amplifier; biomedical amplifier

## 1. Introduction

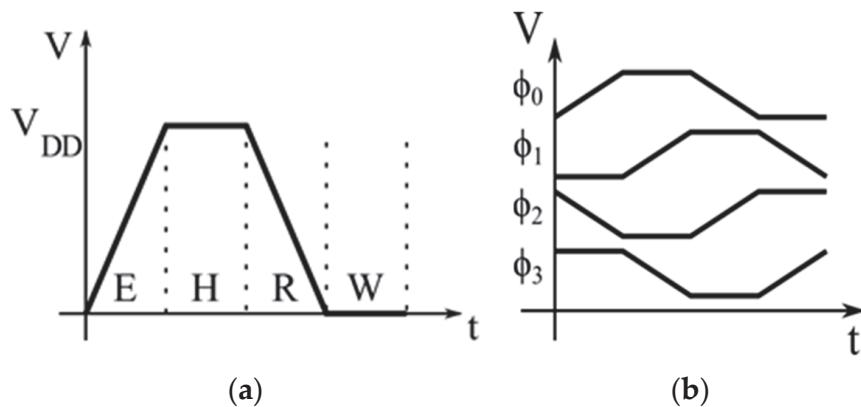

Wireless sensor biomedicine (WSB) is becoming increasingly popular to monitor our daily activities for early detection of cardiovascular diseases [1–3]. Due to its use in wearable or implantable devices, low-power sensors are required to monitor human biopotential signal. In addition to developing standard applications to improve patients' quality of life, long-term monitoring, mobile monitoring, sports and rehabilitation applications, and brain-computer interfaces will also be realized [4]. Typically, WSBs use a low-noise, low-power instrumentation amplifier (IA) to interface with many types of biomedical sensors. These biopotential signals include electrocardiograms (ECGs) and electroencephalograms (EEGs) from the heart and brain, respectively. Local field potentials (LFPs) and action potentials (APs) are biomarkers useful for both neuroscience research and treatment [5]. Biopotential signals, as shown in Figure 1, have a very low amplitude, ranging from 10 to 100  $\mu$ V for EEG and about 1 mV for ECG. The biosignals range from 0.5 to 150 Hz [6]. LFP has a bandwidth of 1 to 200 Hz and a peak amplitude of about 1 mV, while APs have a peak amplitude of about 100  $\mu$ V and occupy a frequency band of 200 Hz to 5 kHz [7]. Therefore, these neural signals must first be amplified before signal processing can be performed.

To improve the quality of neural signals, the readout system often includes an instrumentation amplifier (IA) implemented in CMOS technology. However, the IA has two important noise sources that must be taken into account, flicker noise (1/f) and thermal noise [8]. The chopper stabilization technique is commonly used on IA [9,10] to mitigate 1/f noise by up-modulating this noise at low frequencies beyond the spectrum of IA, while leaving thermal noise unresolved. For example, although the designs in [11,12] consume

only 2  $\mu$ W and 1.89  $\mu$ W, thermal noise remains a concern with values of 100 and 240 nV/Hz, respectively. In addition, the CCIA in [13,14] only have a bandwidth of about 500 Hz. Therefore, CCIA should have a variable bandwidth to allow better bandwidth selection, while biopotential signals are often bandlimited. This work is an extension of the work originally presented at ICCE'22 [15].

**Figure 1.** Amplitude and frequency ranges of the characteristics of neural signals.

This paper presents an ultra-low-power CCIA with programmable bandwidth for biomedical applications. To achieve high noise power efficiency, a squeezed inverter amplifier (SQI) operating with a 0.2-V supply is used in the CCIA. In addition, a programmable Miller compensation capacitor is used in the CCIA to obtain flexible bandwidth without additional power consumption. Simulated with a 0.18  $\mu$ m CMOS technology process, the chip area of the proposed CCIA is only 0.083 mm<sup>2</sup>. While the power consumption of 0.47  $\mu$ W is achieved at the supply voltage of 0.2 and 0.8-V, the proposed amplifier architecture achieves a thermal noise of 28 nV/  $\sqrt{\text{Hz}}$ , an input-related noise (IRN) of 0.9  $\mu$ V<sub>rms</sub> over a bandwidth of 1 kHz, a closed-loop gain of 40 dB, a power supply rejection ratio (PSRR) of 87.6 dB, and a common-mode rejection ratio (CMRR) of 117.7 dB according to post-simulation data. The proposed CCIA compares well with the latest research results, with a noise efficiency factor (NEF) of 1.47 and a power efficiency factor (PEF) of 0.56.

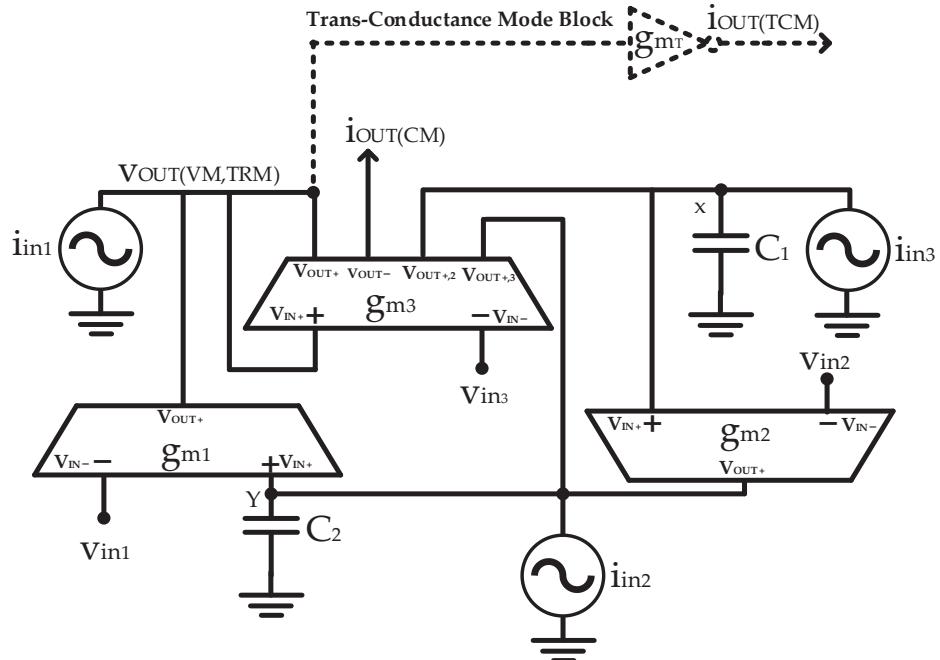

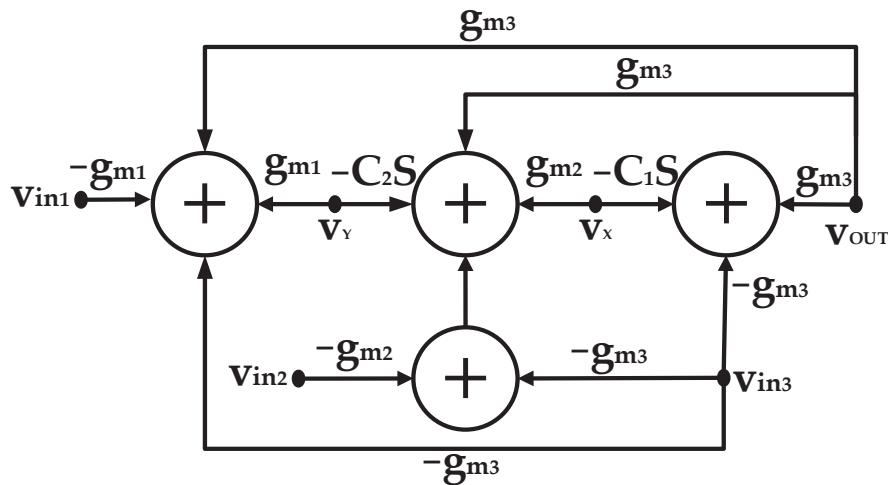

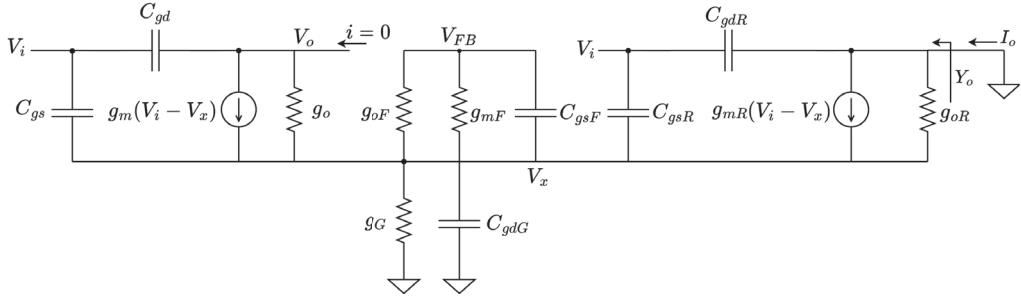

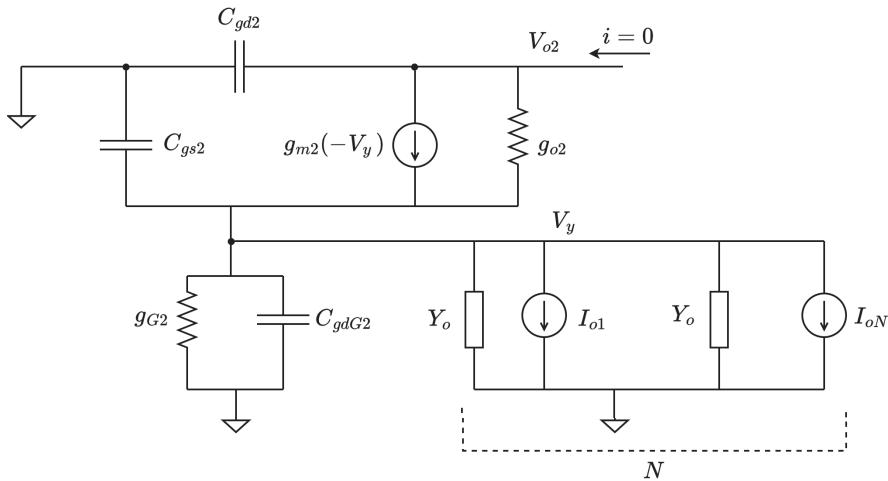

## 2. Design

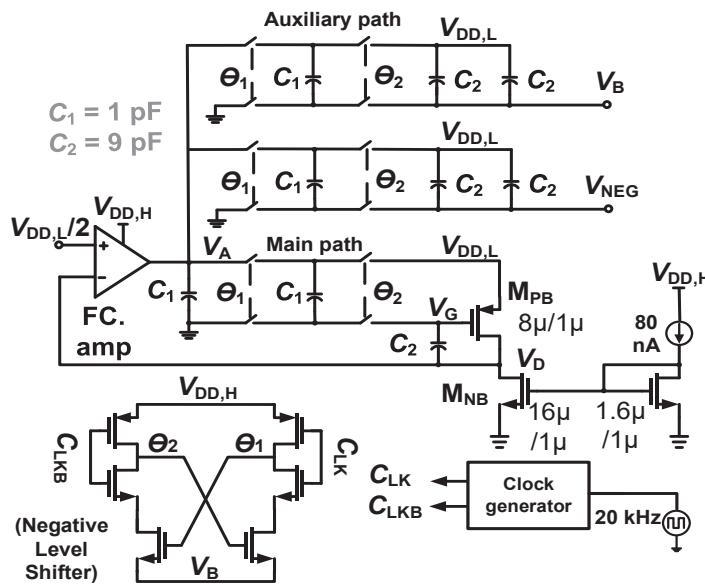

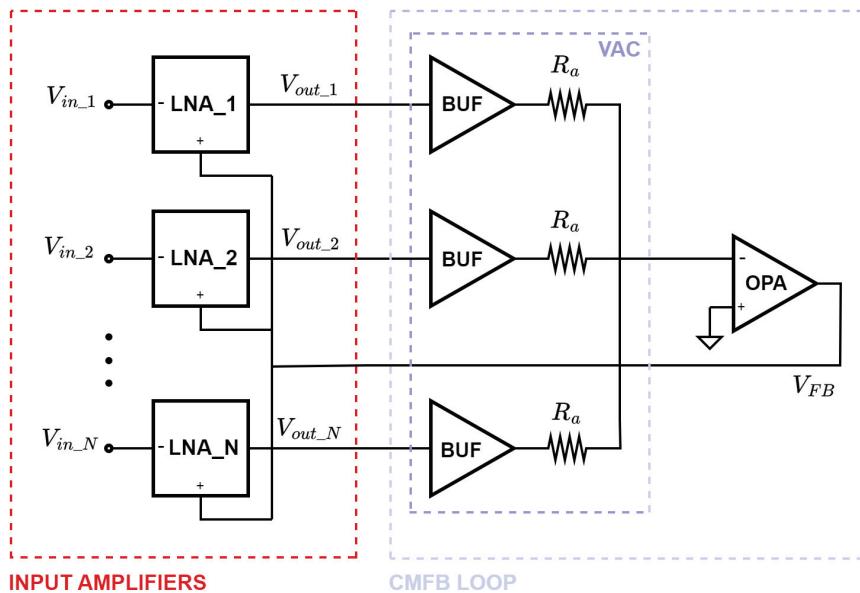

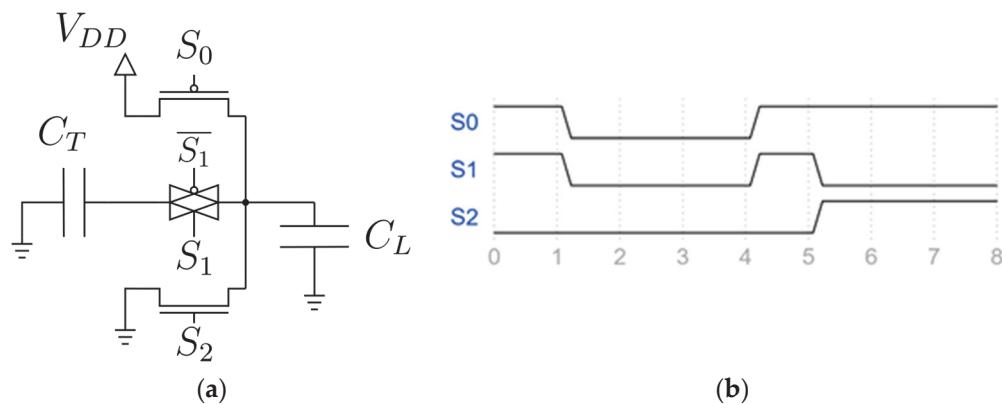

As we know, to reduce the thermal noise, there are two approaches: (1) The transistors of the amplifier are enlarged, resulting in an increase in chip area; (2) The DC current bias for the amplifier must be increased [8]. However, to achieve low power consumption, the supply voltage must be reduced to a minimum so that the transistor still works well. This is the biggest challenge in designing an amplifier. Therefore, the Squeeze inverter amplifier (SQI) with a supply voltage of 0.2 V is dropped in the proposed design. The multistage capacitively coupled chopper amplifier (CCIA) is shown schematically in Figure 2. Since the input stage ( $G_{m1}$ ) causes most of the input noise, the low-power and low-noise SQI amplifier is implemented in the first stage to mitigate the noise. To achieve high transconductance, the CMOS transistors are operated at a comparatively high current of 800 nA in the subthreshold region. A low supply voltage  $V_{DD,L}$  of 0.2-V is used to power the high-current input stage  $G_{m1}$ , which corresponds to two drain-source saturation voltages ( $V_{DSAT}$ ) of both the PMOS and NMOS transistors in the SQI to reduce power consumption to only about 320 nW. The combination of the output stage of an amplifier with a common source (CS) is used to achieve a large output swing with the middle stage using a folded-cascode amplifier (FC) to achieve high gain. Since the output common mode voltage of the first stage is only 0.1 V, the FC stage must be used with PMOS transistor input pairs. To handle the low-frequency flicker noise (1/f), the chopper  $CH_I$  is connected before the input capacitor to modulate the input signal  $V_{in}$  to the chopper frequency  $f_{CH} = 10$  kHz, which is then modulated down to the baseband by the chopper  $CH_O$ . The proposed multistage CCIA

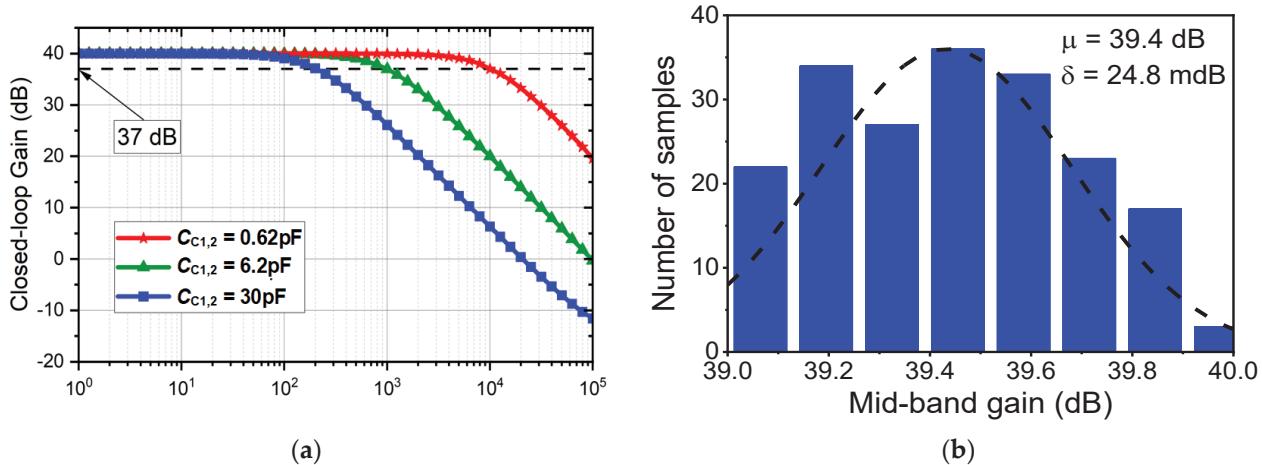

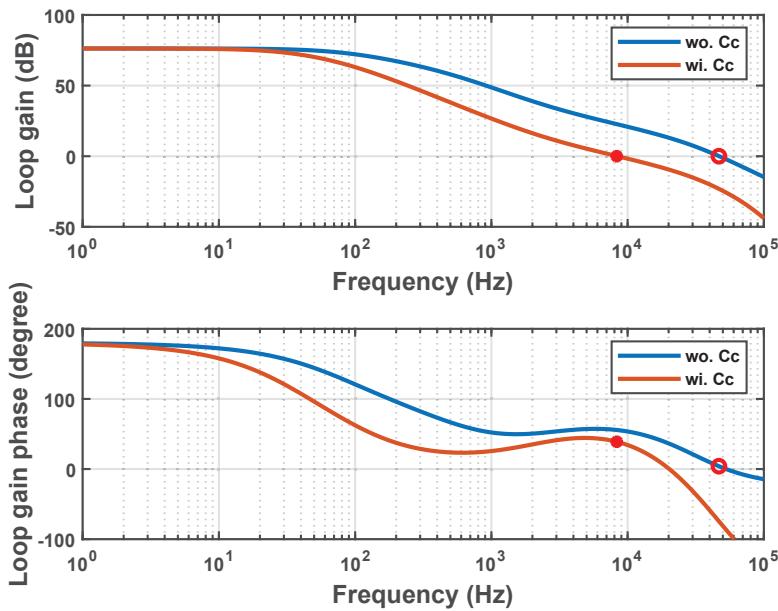

creates multiple poles, which reduce the stabilization of the circuit. To ensure stability while maintaining bandwidth, Miller compensation capacitors  $C_{C1,2}$  and resistors  $R_{Z1,2}$  are added to the last stage feedback loop.

**Figure 2.** Schematic of the proposed CCIA with  $C_{in1,2} = 4 \text{ pF}$ ,  $C_{fb1,2} = 40 \text{ fF}$ ,  $R_{Z1,2} = 0.9 \text{ M}\Omega$ ,  $C_{C1,2} = 0.62/6.2/30 \text{ pF}$ .

As we know, the amplifier is stable when the phase at the loop gain crossover is higher than  $-180$  degrees when the loop gain is  $0 \text{ dB}$ . By moving either the loop gain crossover or the phase crossover point, i.e., the point where the phase reaches  $-180$  degrees, away from the origin, you can increase the stability. Thus, decreasing  $C_{C1,2}$  causes the loop gain crossover of CCIA to move away from the origin, increasing the bandwidth of CCIA. Moreover, the serial nulling resistors  $R_{Z1,2}$  are used to reduce the null in the right half plane (RHP) caused by the feedforward using the compensation capacitors. The multi-stage CCIA proposed in this work has a flexible bandwidth from  $0.2$  to  $10 \text{ kHz}$  thanks to the programmable Miller compensation capacitors  $C_{C1,2}$ . In contrast, previous designs [16,17], which also use a multi-stage circuit in the main path, use fixed values of the Miller compensation components so that the bandwidth of these designs is  $0.67$  and  $0.8 \text{ kHz}$ , respectively. The midband gain of the CCIA is determined by the ratio of the input capacitances  $C_{in1,2}$  and the feedback capacitances  $C_{fb1,2}$ . In this work,  $C_{in1,2} = 4 \text{ pF}$ ,  $C_{fb1,2} = 40 \text{ fF}$  are realized by the metal-insulator-metal (MIM) capacitor technique to reduce the active chip area so that the midband gain of the CCIA reaches  $40 \text{ dB}$ .

### 3. Circuit Implementation

#### 3.1. Squeezed-Inverter Amplifier

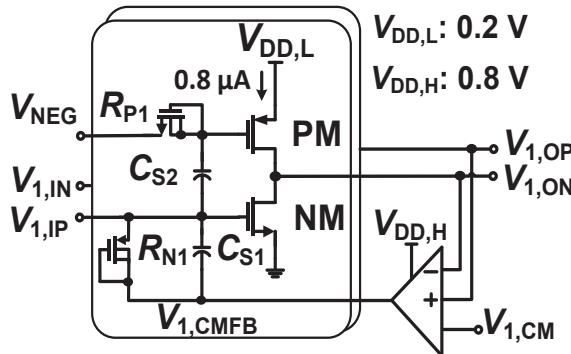

As shown in Figure 3, the first stage uses the scheme of SQI with a common mode feedback circuit (CMFB) sharing to increase the CMRR. By using an ultra-low voltage supply  $V_{DD,L} = 0.2\text{-V}$ , the CMOS transistors in the SQI operate in the subthreshold region. The IRN of the first stage can be calculated as follows:

$$\overline{V_{n,in,Gm1}^2} = \frac{8kT}{g_{m,n} + g_{m,p}} \cong \frac{4kTnV_T}{I_{BIAS}} \quad (1)$$

where  $g_{m,n}$  and  $g_{m,p}$  are the transconductance of the NMOS NM and PMOS PM transistors, respectively, the bias current  $I_{BIAS}$  is  $0.8 \mu\text{A}$ , thermal voltage  $V_T = 26 \text{ mV}$ , and the subthreshold factor [18]  $n = 1.5$ . The SQI stage operates with low noise by increasing the

bias current. Moreover, due to using an ultra-low-voltage supply of 0.2 V, SQI achieves high noise power efficiency.

Figure 3. Schematic of SQI  $C_{S1} = 1 \text{ pF}$ ,  $C_{S2} = 4 \text{ pF}$ .

The input stage  $G_{m1}$  is the main source of noise in the design and requires a large bias current to limit the output noise with  $1/f$  noise and thermal noise [15]. The chopping approach can be used to remove the flicker noise while the thermal noise is not compatible with the bias current. Therefore, an acceptable bias current of  $0.8 \mu\text{A}$  was chosen to compensate for an extremely low supply voltage of  $0.2 \text{ V}$  to reduce noise floor while keeping power dissipation low. To operate at the  $0.2 \text{ V}$  supply voltage, the negative bias voltages of the input PM and NM transistors in SQI are regulated by a negative bias generator and a CMFB loop. A negative voltage  $V_{\text{NEG}}$  generated by the negative bias generator (see Figure 3) is used to bias the PM input transistor via a pseudo-resistor  $R_{P1,2}$ . The gate voltage of the transistor NM is controlled by a common CMFB loop [10] driven by a high voltage source  $V_{\text{DD},H} = 0.8\text{-V}$  to maintain the common output voltage of SQI at  $V_{\text{DD},L}/2$ . Capacitors  $C_{S1,2}$  are used for AC coupling. Since the subthreshold transistors operate without a tail current source, it is challenging to balance the bias current for the input pairs using the CM voltage. Therefore, a common CMFB circuit, as shown in Figure 4, is required for the SQI differential branches to solve this problem. By using a voltage of  $V_{1,\text{CM}} = 0.1\text{-V}$  as a reference, a negative feedback loop is created to monitor and adjust the output common mode voltage of the SQI. The output of the CMFB,  $V_{1,\text{CMFB}}$ , is used to control the gate voltage of the transistor NM in each SQI branch through a pair of pseudo-resistors  $R_{N1,2}$ . This approach provides balanced bias currents for the SQI stage since any change in  $V_{1,\text{CMFB}}$  affects the input pair by the same amount.

Figure 4. Schematic of CMFB circuit of the SQI.

### 3.2. Bias Circuit for Squeezed-Inverter Amplifier

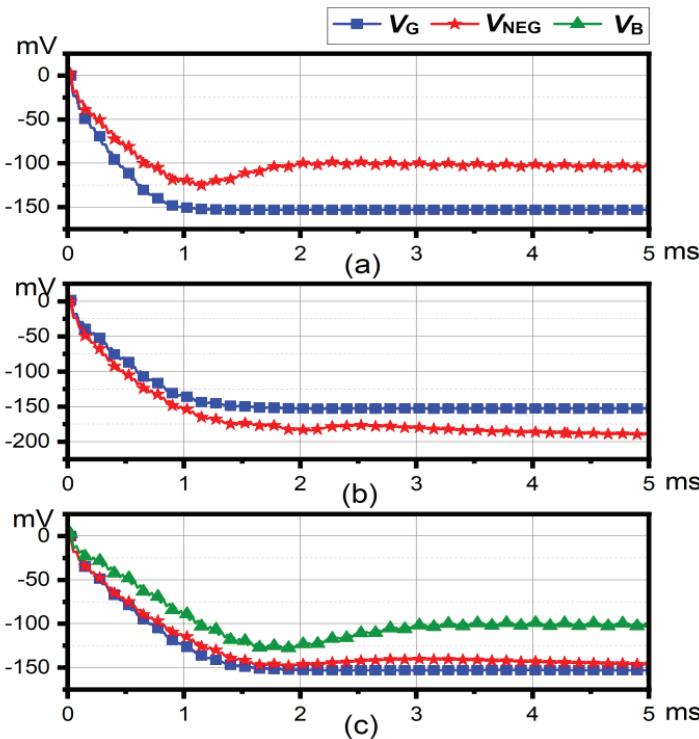

As we know, CMOS transistors must be biased in SQI, but the extremely low supply voltage  $V_{DD,L} = 0.2\text{-V}$  makes this difficult. While PM transistors need a negative bias voltage lower than ground, the voltage drives the gate of the NM transistors using a CMFB through the high voltage supply  $V_{DD,H} = 0.8\text{-V}$ . In the conventional negative voltage generator [16], a switched capacitor loop (SC) is used, in which a 1/10 scaled replica  $M_{PB}$  of the PMOS input transistor is used to generate the negative voltage to regulate the bias current of the SQI.  $M_{PB}$  and the FC work together to provide a negative feedback loop that continuously regulates  $V_G$  during the time that the drain voltage is held at  $V_{DD,L}/2$ . An SC network is also used by the feedback loop to hold  $V_G$  below ground. A low-noise copy of  $V_G$  is created using a low-pass filter replica ( $V_{NEG}$ ). To prevent switching spikes from affecting the desired signals, a frequency of 20 kHz is used by this SC. To turn off the switches completely, a negative level shifter is driven by  $V_G$  or  $V_{NEG}$ . However, after each switching period, the level shifter supplies its “ground” rail, increasing the voltage differences between  $V_G$  and  $V_{NEG}$  during startup. The negative feedback loop has  $V_G$  fixed, so inaccurate replication of  $V_{NEG}$  will result in an unexpected bias current.  $V_{NEG}$  will be higher than  $V_G$ , when the level shifter uses  $V_{NEG}$ . As a result, the bias current of SQI will be reduced, which will increase the input noise. On the other hand, the bias current will be lower than predicted when this level shifter is driven by  $V_G$ , which drastically increases the power consumption. Therefore, an auxiliary path is needed to generate a voltage  $V_B$ , a replica of the voltage  $V_G$  to supplement the negative voltage generator circuit. The proposed negative bias voltage generator is shown in Figure 5. The  $V_B$ -fed negative voltage for the level shifter does not affect  $V_G$  and  $V_{NEG}$ . Therefore, the bias current of SQI is set to the appropriate value, and  $V_{NEG}$  is an exact duplicate of  $V_G$ . According to the simulation results shown in Figure 6, the expected level of  $V_{NEG}$  is about  $-150\text{ mV}$  after  $V_G$  or  $V_{NEG}$  is used by the level shifter but is changed to about  $-100\text{ mV}$  or  $-210\text{ mV}$  accordingly after the start time. Since only  $V_B$  is supplied by the dynamic current of the level shifter,  $V_G$  and  $V_{NEG}$  are controlled by an equal voltage of  $-150\text{ mV}$  when  $V_B$  is injected. The improved negative bias generator in the SQI circuit achieves a bias current of  $1.56\text{ }\mu\text{A}$  or an almost theoretical value of  $1.6\text{ }\mu\text{A}$ .

Figure 5. Schematic of negative voltage bias generator circuit.

**Figure 6.** Simulated results of the negative voltage generator when the level shifter is powered by (a)  $V_{NEG}$ , (b)  $V_G$ , (c)  $V_B$ .

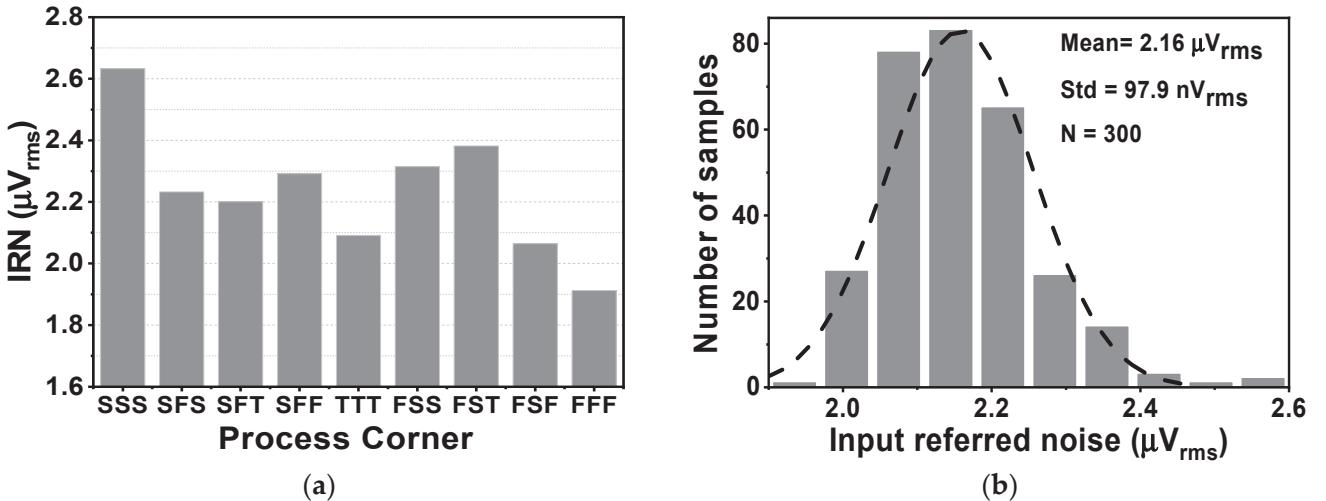

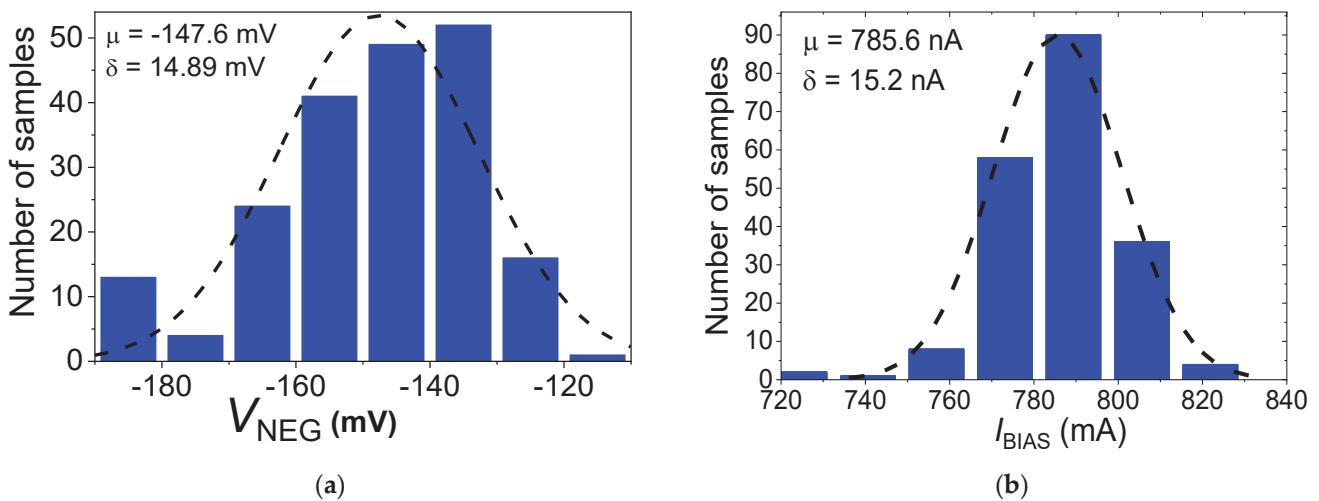

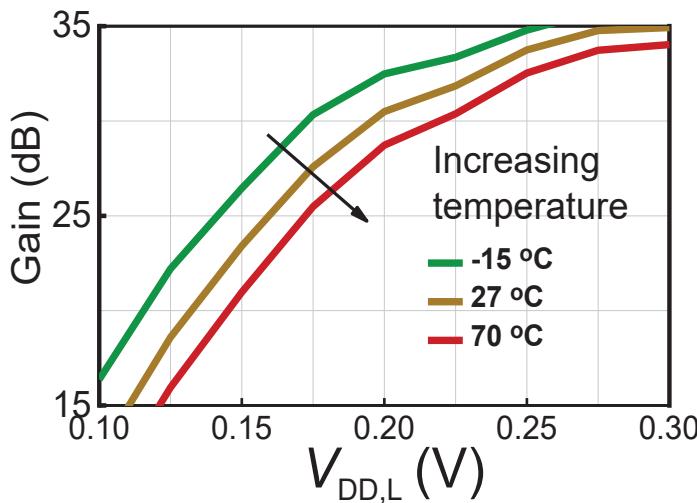

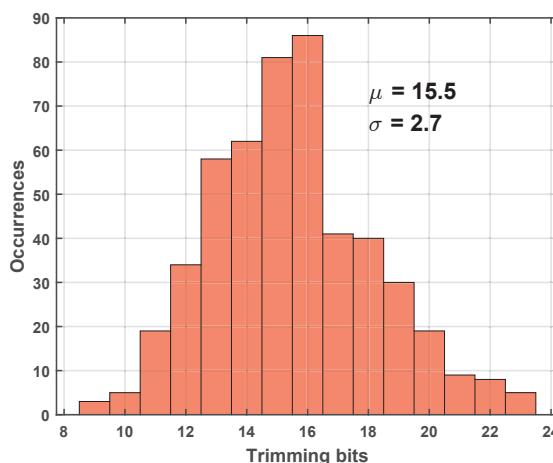

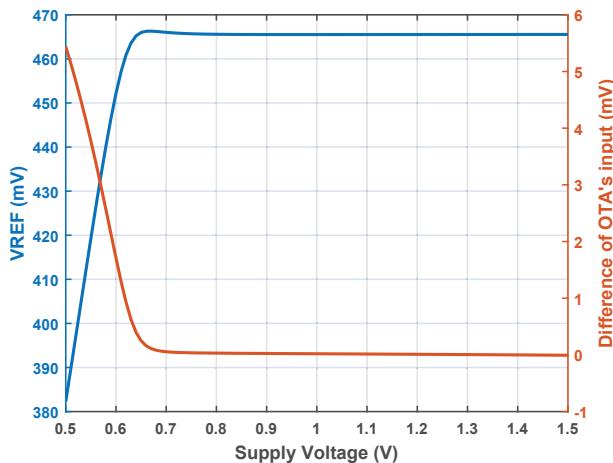

Monte Carlo simulation results of the negative voltage  $V_{NEG}$  and bias current of SQI (one branch) are shown in Figure 7, where both random process variations and mismatches were considered. The results of the Monte Carlo simulation with 200 samples show that the average value of  $V_{NEG}$  is  $-147.6$  mV and the bias current of SQI is  $785.6$  nA with a standard deviation of  $14.9$  mV and  $15.2$  nA, respectively. The effect of temperature and variable  $V_{DD,L}$  on the open-loop gain of SQI is shown in Figure 8. The temperature and variable  $V_{DD,L}$  are examined from  $-15$  to  $70$  degrees Celsius and  $0.1$  to  $0.3$ -V, respectively. At a temperature of  $27$  degrees Celsius and a  $V_{DD,L}$  of  $0.2$ -V, the open-loop gain of the SQI reaches about  $30$  dB.

**Figure 7.** The result of Monte Carlo simulation of (a) negative voltage  $V_{NEG}$  (b) the bias current of SQI.

Figure 8. Simulated gain of the SQI stage depending on  $V_{DD,L}$  and temperature.

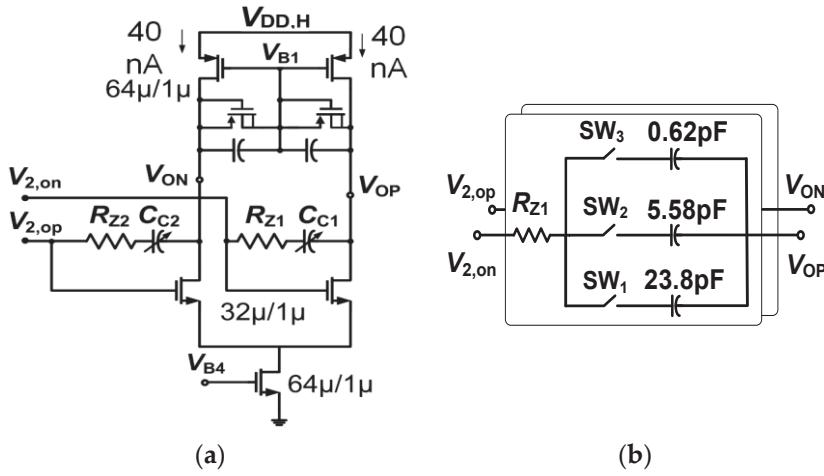

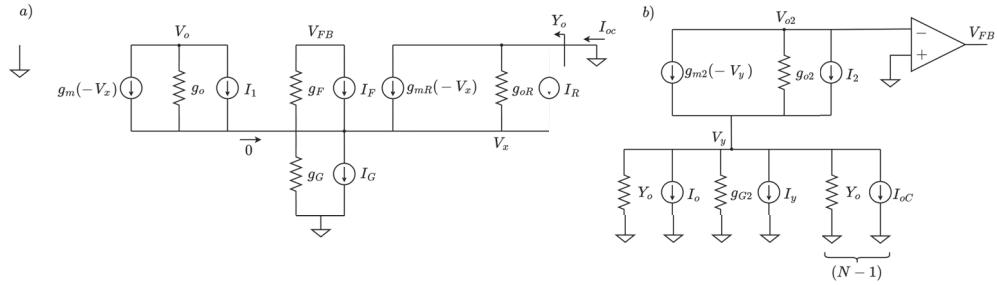

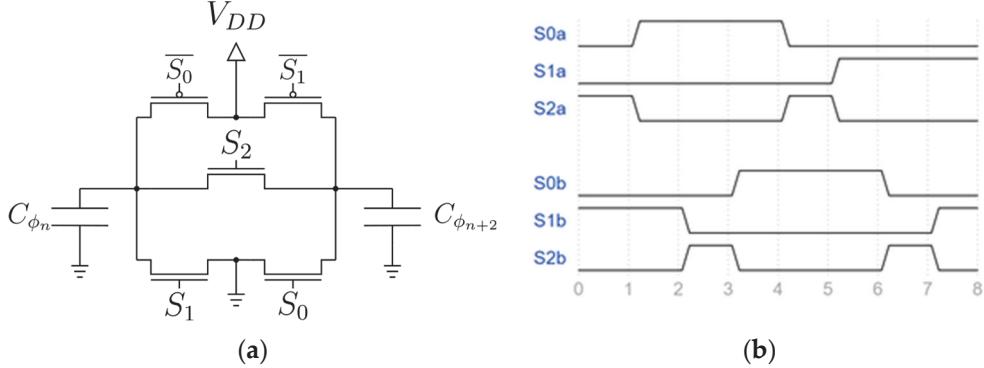

### 3.3. Middle and Output Stage

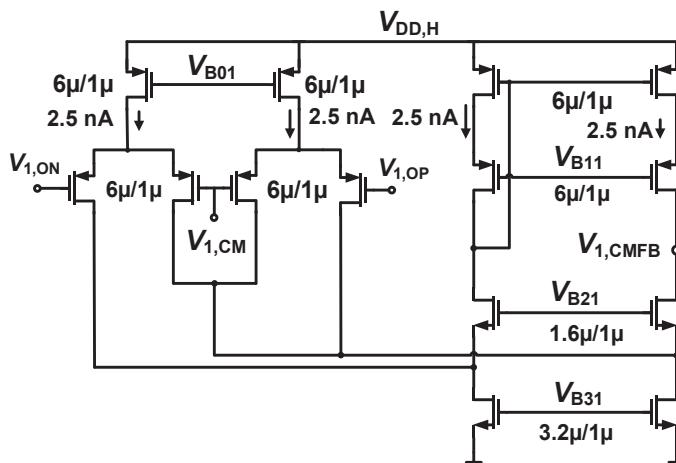

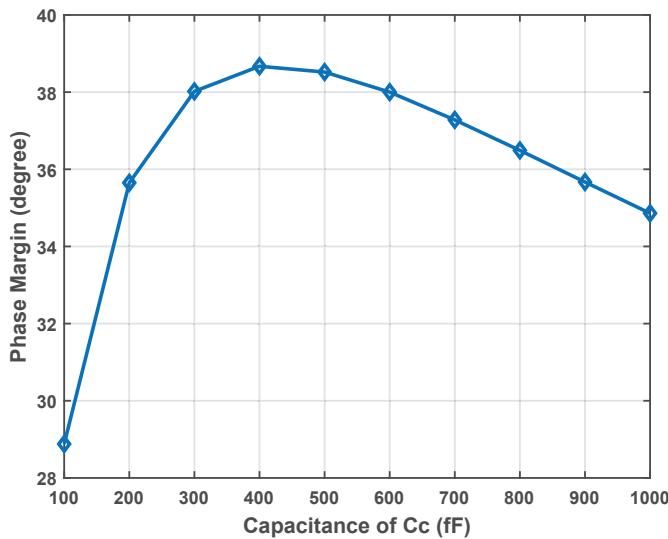

To obtain high gain and output swing, the middle and last stage of CCIA employs the FC and the CS amplifiers, respectively. The schematic of FC is shown in Figure 9, while the schematic of CS with the phase margin compensation circuit is shown in Figure 10. Using a supply voltage  $V_{DD,H}$  of 0.8-V, the FC is biased a DC current of 40 nA while CS draws a DC current of 80 nA. Although the current consumption is much lower than SQI's current drawing, the effect that the noise of the  $G_{m2}$  and  $G_{m3}$  have on the input is very small because it is divided into the gain of  $G_{m1}$  (normally 30 dB). The FC input pair must use PMOS transistors interfacing to SQI's low output voltage of around 0.1-V. The  $G_{m3}$  that employs CS with a passive CMFB circuit built by the pseudo resistors in parallel with MIM capacitors is also shown in Figure 10a. The network compensation capacitor  $C_{C1,2}$  is shown in Figure 10b.  $C_{C1,2}$  is built from three parallel capacitors (0.62 pF, 5.58 pF, and 23.8 pF); therefore, the value of  $C_{C1,2}$  can be changed from 0.62 pF to 30 pF by the controlling switches  $SW_{1,2,3}$ .

Figure 9. The schematic of the FC amp circuit.

**Figure 10.** (a) The schematic of CS amp circuit, (b) the schematic of phase margin compensation circuit.

The IRN of the proposed CCIA,  $\overline{V_{n,in}^2}$  can be calculated as

$$\begin{aligned}\overline{V_{n,in}^2} &= \left( \frac{C_{\text{tot}}}{C_{\text{in}1,2}} \right)^2 \left( \overline{V_{n,in,Gm1}^2} + \frac{\overline{V_{n,in,Gm2}^2}}{A_{V1}} \right) \\ &= \left( \frac{C_{\text{tot}}}{C_{\text{in}1,2}} \right)^2 \left[ \frac{4kTnV_{\text{th}}}{I_{\text{BIAS}}} + \frac{8kTn}{A_{V1}g_{m1,2}} \left( 1 + \frac{g_{m3,4} + g_{m9,10}}{g_{m1,2}} \right) \right]\end{aligned}\quad (2)$$

where  $C_{\text{tot}} = C_{\text{in}1,2} + C_{\text{fb}1,2} + C_p$ ,  $C_p$  is the parasitic capacitance of the first stage,  $\overline{V_{n,in,Gm1}^2}$  and  $\overline{V_{n,in,Gm2}^2}$  are the IRN of  $G_{m1}$  and  $G_{m2}$ , respectively.

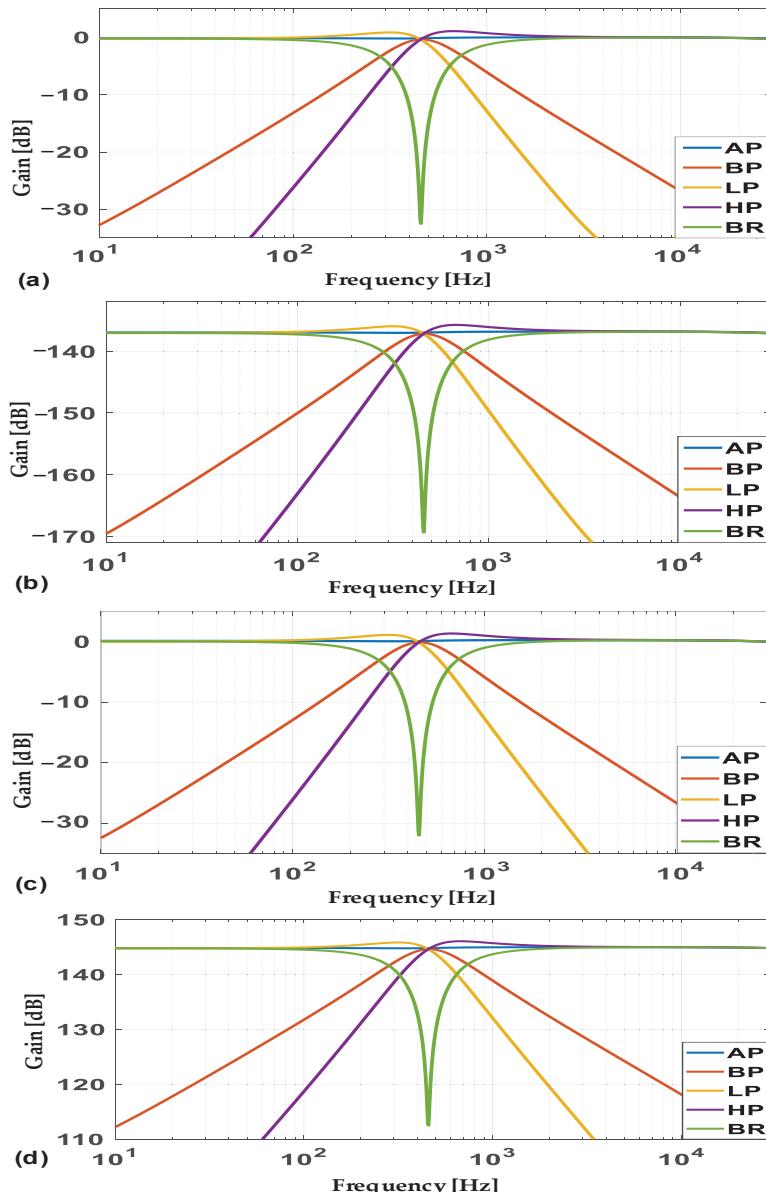

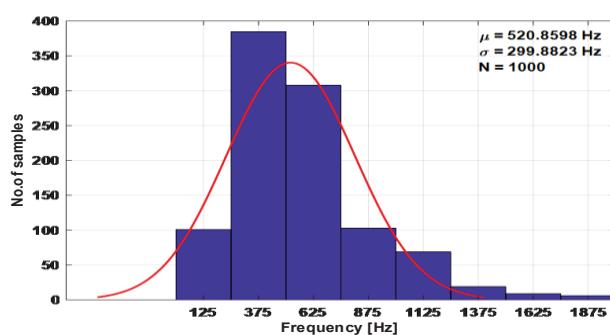

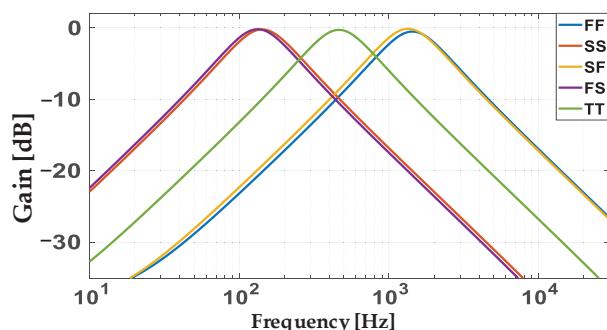

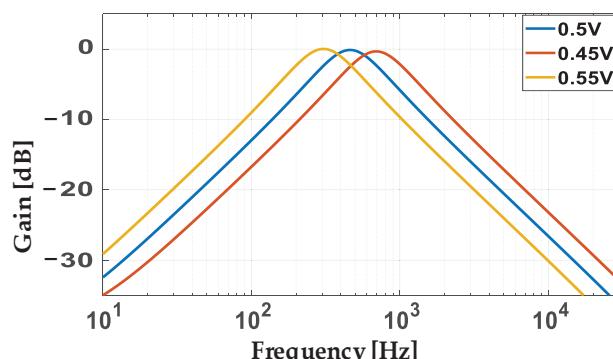

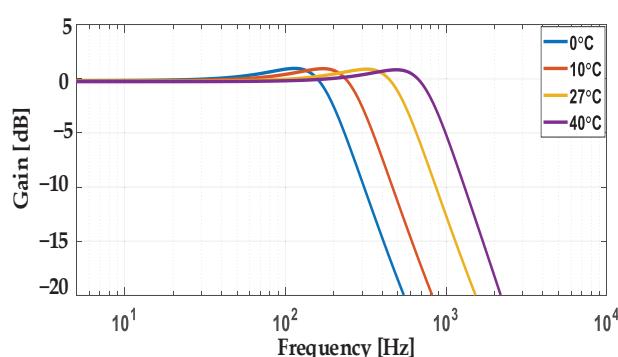

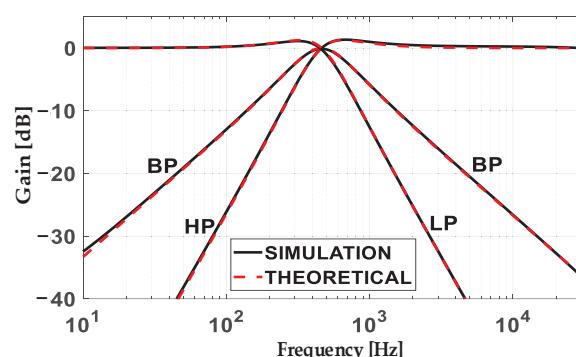

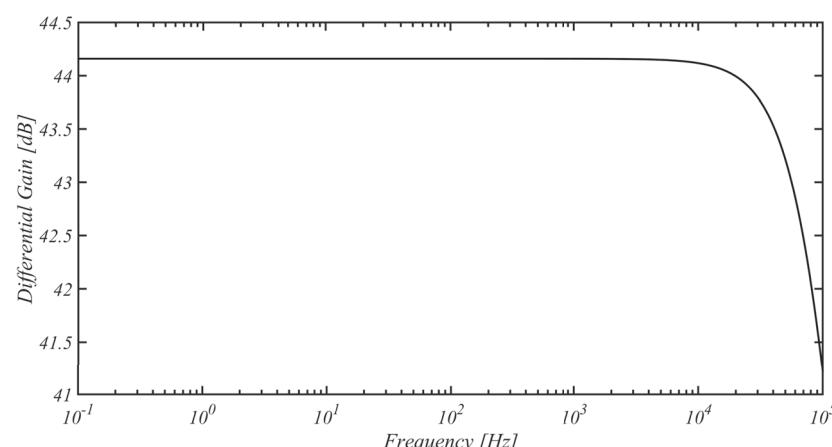

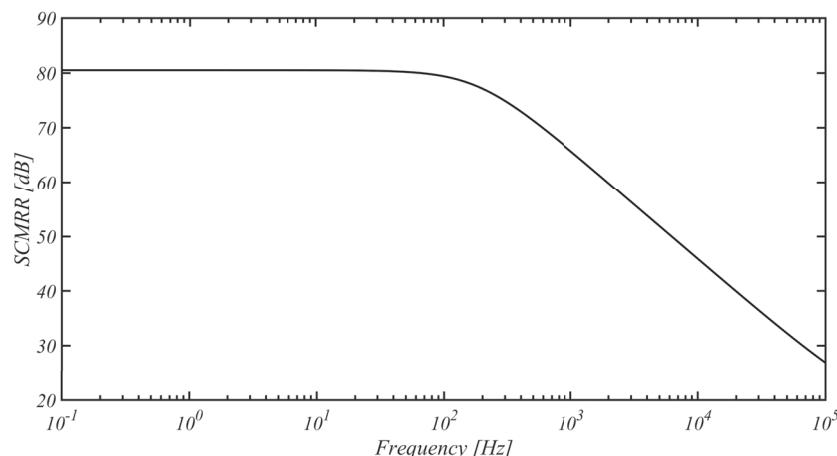

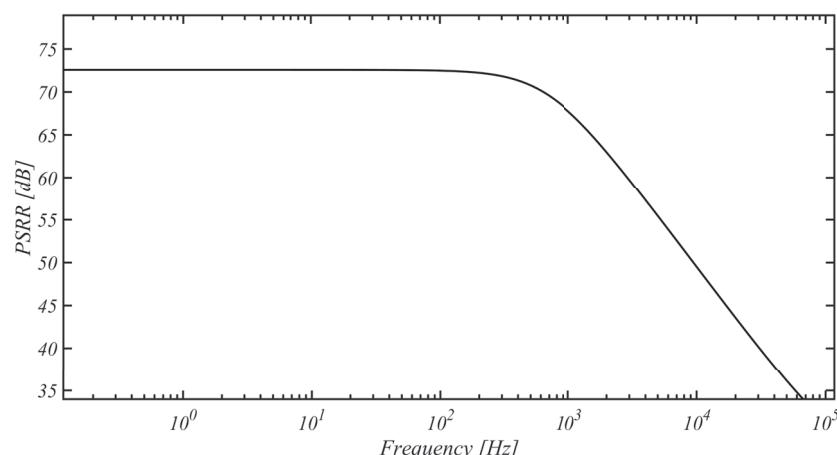

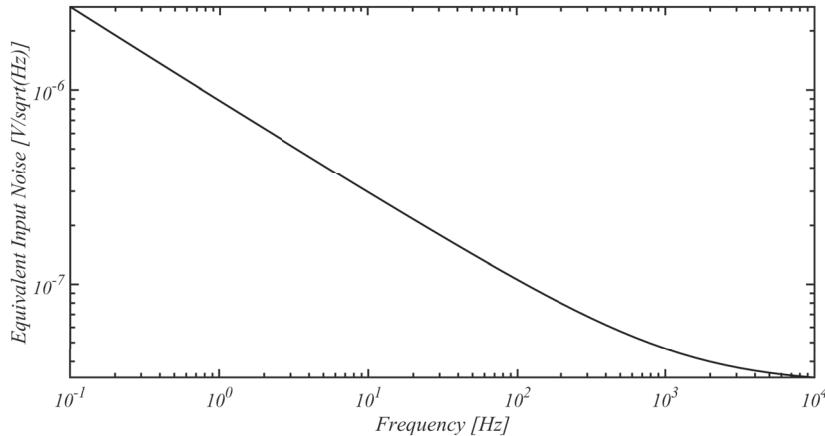

#### 4. Simulation Results