Volume 1

# Applications of Power Electronics

Edited by

Frede Blaabjerg, Tomislav Dragičević and Pooya Davari Printed Edition of the Special Issue Published in *Electronics*

### **Applications of Power Electronics**

# **Applications of Power Electronics Volume 1**

Special Issue Editors

Frede Blaabjerg

Tomislav Dragičević

Pooya Davari

Special Issue Editors

Frede Blaabjerg Tomislav Dragičević Pooya Davari Aalborg University Aalborg University Aalborg University

Denmark Denmark Denmark

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Electronics* (ISSN 2079-9292) from 2018 to 2019 (available at: https://www.mdpi.com/journal/electronics/special\_issues/appli\_power\_elec)

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Article Number*, Page Range.

Volume 1 Volume 1-2

ISBN 978-3-03897-974-6 (Pbk) ISBN 978-3-03921-148-7 (Pbk) ISBN 978-3-03897-975-3 (PDF) ISBN 978-3-03921-149-4 (PDF)

Cover image courtesy of Frede Blaabjerg.

© 2019 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

#### **Contents**

| About the Special Issue Editors                                                                            |

|------------------------------------------------------------------------------------------------------------|

| Frede Blaabjerg, Tomislav Dragicevic and Pooya Davari                                                      |

| Applications of Power Electronics                                                                          |

| Reprinted from: Electronics 2019, 8, 465, doi:10.3390/electronics8040465                                   |

| Hong Cheng, Wenbo Chen, Cong Wang and Jiaqing Deng                                                         |

| Open Circuit Fault Diagnosis and Fault Tolerance of Three-Phase Bridgeless Rectifier                       |

| Reprinted from: Electronics 2018, 7, 291, doi:10.3390/electronics7110291                                   |

| Jordi Burriel-Valencia, Ruben Puche-Panadero, Javier Martinez-Roman, Angel Sapena-Bano,                    |

| Manuel Pineda-Sanchez, Juan Perez-Cruz, Martin Riera-Guasp                                                 |

| Automatic Fault Diagnostic System for Induction Motors under Transient Regime Optimized                    |

| with Expert Systems                                                                                        |

| Reprinted from: Electronics 2019, 8, 6, doi:10.3390/electronics8010006                                     |

| Sonali Chetan Rangari, Hiralal Murlidhar Suryawanshi and Mohan Renge                                       |

| New Fault-Tolerant Control Strategy of Five-Phase Induction Motor with Four-Phase and                      |

| Three-Phase Modes of Operation                                                                             |

| Reprinted from: Electronics 2018, 7, 159, doi:10.3390/electronics7090159                                   |

| Zachary Bosire Omariba, Lijun Zhang and Dongbai Sun                                                        |

| Review on Health Management System for Lithium-Ion Batteries of Electric Vehicles                          |

| Reprinted from: Electronics 2018, 7, 72, doi:10.3390/electronics7050072                                    |

| R. Balasubramanian, K. Parkavikathirvelu, R. Sankaran and Rengarajan Amirtharajan                          |

| Design, Simulation and Hardware Implementation of Shunt Hybrid Compensator Using                           |

| Synchronous Rotating Reference Frame (SRRF)-Based Control Technique                                        |

| Reprinted from: Electronics 2019, 8, 42, doi:10.3390/electronics8010042                                    |

| Haider Zaman, Xiancheng Zheng, Xiaohua Wu, Shahbaz Khan and Husan Ali                                      |

| A Fixed-Frequency Sliding-Mode Controller for Fourth-Order Class-D Amplifier                               |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 261, doi:10.3390/electronics7100261                    |

| Rui Zhang, Wei Ma, Lei Wang, Min Hu, Longhan Cao, Hongjun Zhou and Yihui Zhang                             |

| Line Frequency Instability of One-Cycle-Controlled Boost Power Factor Correction Converter                 |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 203, doi:10.3390/electronics7090203                    |

| Yifan Zhang, Xiaodon Li, Chuan Sun and Zhanhong He                                                         |

| Improved Step Load Response of a Dual-Active-Bridge DC-DC Converter                                        |

| Reprinted from: <i>Electronics</i> <b>2018</b> , <i>7</i> , 185, doi:10.3390/electronics7090185            |

| Ming Lu, Xiaodong Li                                                                                       |

| Performance Evaluation of a Semi-Dual-Active-Bridge with PPWM Plus SPS Control                             |

| Reprinted from: Electronics 2018, 7, 184, doi:10.3390/electronics7090184                                   |

| Sohaib Tahir, Jie Wang, Mazhar Hussain Baloch and Ghulam Sarwar Kaloi                                      |

| Digital Control Techniques Based on Voltage Source Inverters in Renewable Energy<br>Applications: A Review |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 18, doi:10.3390/electronics7020018                     |

| Arthur H. R. Rosa, Matheus B. E. Silva, Marcos F. C. Campos, Renato A. S. Santana, Welbert A. Rodrigues, Lenin M. F. Morais and Seleme I. Seleme Jr.  SHIL and DHIL Simulations of Nonlinear Control Methods Applied for Power Converters |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Using Embedded Systems                                                                                                                                                                                                                    |

| Reprinted from: Electronics 2018, 7, 241, doi:10.3390/electronics7100241                                                                                                                                                                  |

| Alberto Sanchez, Elías Todorovich and Angel De Castro                                                                                                                                                                                     |

| Exploring the Limits of Floating-Point Resolution for Hardware-In-the-Loop Implemented with FPGAs                                                                                                                                         |

| Reprinted from: Electronics 2018, 7, 219, doi:10.3390/electronics7100219                                                                                                                                                                  |

| Seok-Kyoon Kim and Kyo-Beum Lee                                                                                                                                                                                                           |

| Robust DC-Link Voltage Tracking Controller with Variable Control Gain for Permanent Magnet                                                                                                                                                |

| Synchronous Generators                                                                                                                                                                                                                    |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 339, doi:10.3390/electronics7110339                                                                                                                                                   |

| Muhammad Ahmad, Zhixin Wang, Sheng Yan, Chengmin Wang, Zhidong Wang,                                                                                                                                                                      |

| Chenghzi Zhu and Hua Qin                                                                                                                                                                                                                  |

| Comparative Analysis of Two and Four Current Loops for Vector Controlled Dual-Three Phase                                                                                                                                                 |

| Permanent Magnet Synchronous Motor Reprinted from: Electronics 2018, 7, 269, doi:10.3390/electronics7110269                                                                                                                               |

| Tounsi Kamel, Djahbar Abdelkader, Barkat Said, Sanjeevikumar Padmanaban and                                                                                                                                                               |

| Atif Iqbal                                                                                                                                                                                                                                |

| Extended Kalman Filter Based Sliding Mode Control of Parallel-Connected Two Five-Phase                                                                                                                                                    |

| PMSM Drive System Reprinted from: Electronics 2018, 7, 14, doi:10.3390/electronics7020014                                                                                                                                                 |

| Reprinted from: Liectionics 2016, 7, 14, doi:10.3390/ejectronics/020014                                                                                                                                                                   |

| Ahmet Aksoz, Yipeng Song, Ali Saygin, Frede Blaabjerg and Pooya Davari                                                                                                                                                                    |

| Improving Performance of Three-Phase Slim DC-Link Drives Utilizing Virtual Positive                                                                                                                                                       |

| Impedance-Based Active Damping Control                                                                                                                                                                                                    |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 234, doi:10.3390/electronics7100234                                                                                                                                                   |

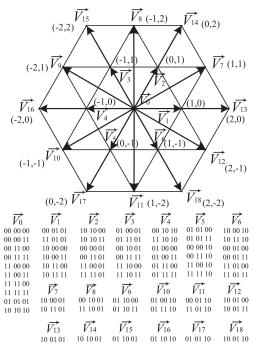

| Tianqing Yuan and Dazhi Wang                                                                                                                                                                                                              |

| Performance Improvement for PMSM DTC System through Composite Active                                                                                                                                                                      |

| Vectors Modulation                                                                                                                                                                                                                        |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 263, doi:10.3390/electronics7100263                                                                                                                                                   |

| Berkan Zöhra, Mehmet Akar and Mustafa Eker                                                                                                                                                                                                |

| Design of A Novel Line Start Synchronous Motor Rotor                                                                                                                                                                                      |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 25, doi:10.3390/electronics8010025                                                                                                                                            |

| Miles Condenie Beatle Fixen and Cabriele Counti                                                                                                                                                                                           |

| Milan Srndovic, Rastko Fišer and Gabriele Grandi  Analysis of Equivalent Inductance of Three-Phase Induction Motors in the Switching                                                                                                      |

| Frequency Range                                                                                                                                                                                                                           |

| Reprinted from: Electronics 2019, 8, 120, doi:10.3390/electronics8020120                                                                                                                                                                  |

| Emrah Cetin and Ferhat Daldaban                                                                                                                                                                                                           |

| Analyzing the Profile Effects of the Various Magnet Shapes in Axial Flux PM Motors by Means                                                                                                                                               |

| of 3D-FEA Reprinted from: Electronics 2018. 7, 13. doi:10.3390/electronics7020013                                                                                                                                                         |

|                                                                                                                                                                                                                                           |

#### **About the Special Issue Editors**

Frede Blaabjerg (professor) worked with ABB-Scandia, Randers, Denmark, from 1987 to 1988. He obtained his Ph.D. in electrical engineering at Aalborg University in 1995. He became an assistant professor in 1992, an associate professor in 1996, and a full professor of power electronics and drives in 1998. In 2017, he became a Villum Investigator. He is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn Technical University (TTU) in Estonia. His current research interests include power electronics and its applications, such as in wind turbines, PV systems, reliability, harmonics, and adjustable-speed drives. He has published more than 600 journal papers in the field of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications. He has received 29 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award in 2014, and the Villum Kann Rasmussen Research Award in 2014. He was the Editor-in-Chief of IEEE Transactions on Power Electronics from 2006 to 2012. He was a distinguished lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011, as well as from 2017 to 2018. In 2018, he became the president elect of the IEEE Power Electronics Society. He serves as vice-president of the Danish Academy of Technical Sciences. He was nominated in 2014, 2015, 2016, and 2017 by Thomson Reuters as one of the world's 250 most cited researchers in engineering.

Tomislav Dragičević (associate professor) received his M.Sc. degree in 2009 and his industrial Ph.D. degree in electrical engineering in 2013 from the Faculty of Electrical Engineering and Computing, University of Zagreb, Zagreb, Croatia. From 2013 to 2016, he was a postdoctoral research associate at Aalborg University, Aalborg, Denmark. Since March 2016, he has been an associate professor at Aalborg University. He was a visiting guest professor at Nottingham University, Nottingham, U.K., during the spring/summer of 2018. His principal fields of interest include overall system design of autonomous and grid-connected dc and ac microgrids and application of advanced modeling and control concepts to power electronic systems. Dr. Tomislav has authored and coauthored more than 140 technical papers (more than 55 of them are published in international journals, mostly *IEEE Transactions*) in his domain of interest, eight book chapters, and a book. His research interests include overall system design of autonomous and grid-connected dc and ac microgrids and application of advanced modeling and control concepts to power electronic systems. Dr. Dragičević is the recipient of the Končar Prize for the best industrial Ph.D. thesis in Croatia and the Robert Mayer Energy Conservation Award. He serves as an associate editor for the *IEEE Transactions on Industrial Electronics* and for the *Journal of Power Electronics*.

**Pooya Davari** (associate professor) received B.Sc. and M.Sc. degrees in electronic engineering from the University of Mazandaran, Babolsar, Iran, in 2004 and 2008, respectively, and a Ph.D. degree in power electronics from Queensland University of Technology (QUT), Brisbane, Australia, in 2013. From 2005 to 2010, he was involved in several electronics and power electronics projects as a development engineer. From 2010 to 2014, he investigated and developed high-power high-voltage power electronic systems for multidisciplinary projects, such as ultrasound application, exhaust gas emission reduction, and tissue-materials sterilization. From 2013 to 2014, he was a lecturer with QUT. He joined the Department of Energy Technology, Aalborg University, Aalborg, Denmark, in 2014, as a

postdoctoral researcher and he is currently an associate professor there. His current research interests include EMI/EMC in power electronics, WBG-based power converters, active frontend rectifiers, harmonic mitigation in adjustable-speed drives, and pulsed power applications. Dr. Davari received a research grant from the Danish Council of Independent Research in 2016.

Editoria

#### **Applications of Power Electronics**

Frede Blaabjerg, Tomislav Dragicevic and Pooya Davari \*

Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark; fbl@et.aau.dk (F.B.); tdr@et.aau.dk (T.D.)

\* Correspondence: pda@et.aau.dk

Received: 19 April 2019; Accepted: 22 April 2019; Published: 25 April 2019

#### 1. Introduction

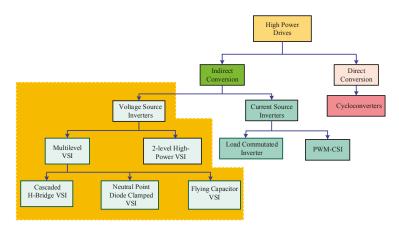

Power electronics technology is still an emerging technology, and it has found its way into many applications, from renewable energy generation (i.e., wind power and solar power) to electrical vehicles (EVs), biomedical devices, and small appliances such as laptop chargers. In the near future, electrical energy will be provided and handled by power electronics and consumed through power electronics; this not only will intensify the role of power electronic technology in power conversion processes, but also implies that power systems are undergoing a paradigm shift, from centralized distribution to distributed generation. Today, more than 1000 gigawatts (GW) renewables (photovoltaic (PV) and wind) have been installed, all of which are handled by power electronics technology. However, areas such as energy saving and electrification transportation are booming, creating a huge market not only for power devices but also for packaging technology and power converter design. Some of the driving forces of the technology are their cost, volume, weight, functionality as well as reliability. At the moment, the technology is seeing a change from being purely silicon-based to being built upon wide bandgap (WBG) technology, such as silicon carbide (SiC) and gallium nitride (GaN), which demands a completely new paradigm in power converter design and layout, as those devices can operate at least an order of magnitude faster.

The main aim of this Special Issue was to seek high-quality submissions that highlight and address recent breakthroughs over the whole range of emerging applications of power electronics, the harmonic and electromagnetic interference (EMI) issues of the devices and system levels, as also discussed in [1–4], robust and reliable power electronics technologies, including fault prognosis and diagnosis techniques [5–7], the stability of grid-connected converters [8,9], and the smart control of power electronics for devices, microgrids and at system levels [10–13].

#### 2. The Present Special Issue

This special issue with 49 published articles has gained a great deal of attention from both academia and industry, clearly showing the growth in significance of "Applications of Power Electronics" in the current research and development arena. The accepted articles cover broad topics in the field of power electronics, and they are categorized into seven different focus areas:

1

```

T1: Fault Diagnosis, Reliability and Condition Monitoring [14–17];

```

T2: Modeling, Control and Design of Power Electronic Converters [18–25];

T3: Electrical Machines, Drives and Traction Systems [26–34];

T4: Distributed Power Generation and e-Grid [35-46];

T5: Emerging Power Electronic Technologies (Pulsed Power, Energy Storage, Others) [47–51];

T6: Energy Access and Micro-Grids [52–56];

T7: Wireless Power Transfer Systems [57–62].

#### 2.1. Fault Diagnosis, Reliability and Condition Monitoring (T1)

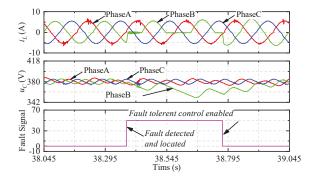

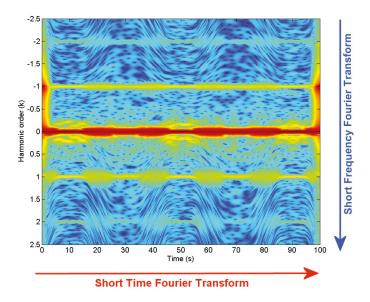

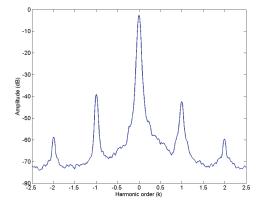

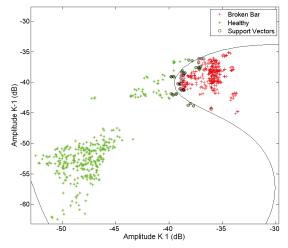

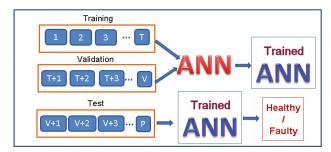

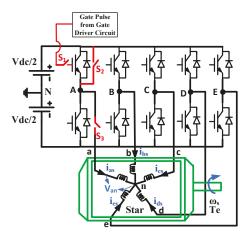

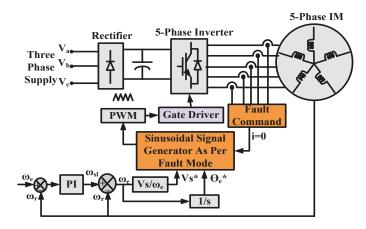

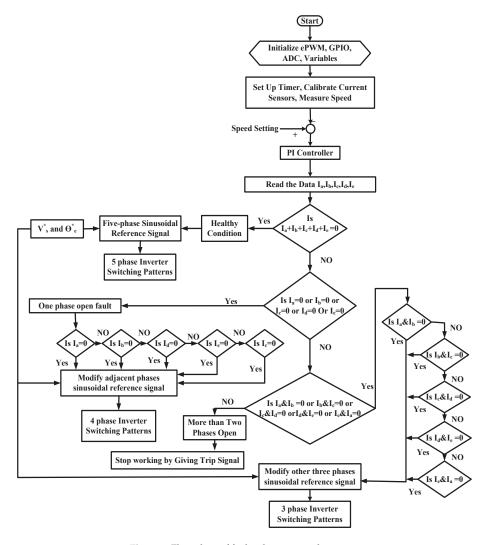

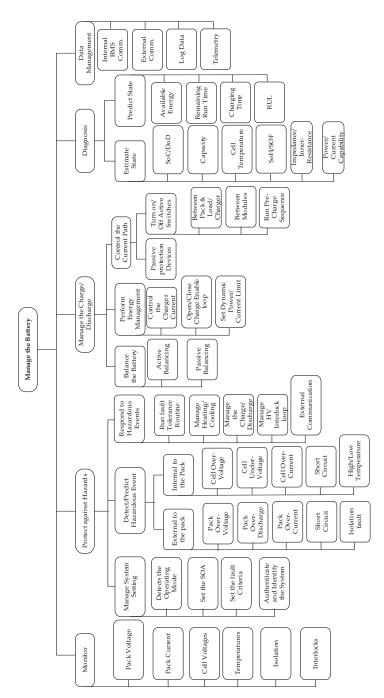

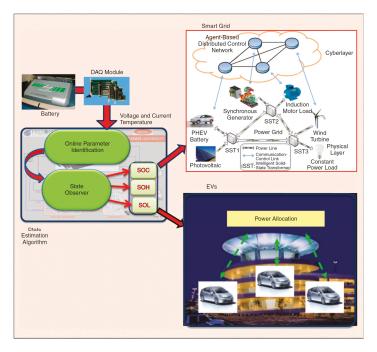

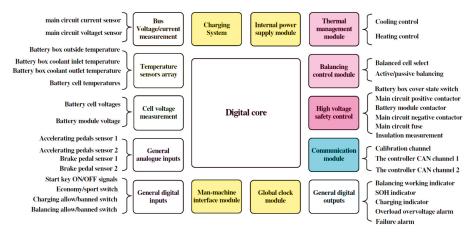

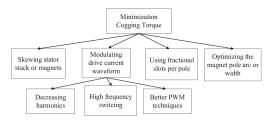

In order to extend overall system lifetimes, fault diagnosis, fault-tolerant control and health management systems are of significant importance, and these have been one of the major focus areas in the power electronics field in the last decades. Open circuit fault diagnosis and the fault tolerance control of three-phase active rectifiers as an inherent stage of many power electronics applications have been addressed in [14]. For induction motors, an automatic fault diagnosis system under a transient situation is developed in [15] and a fault-tolerant control strategy for five-phase induction motors under four and three-phase operation is addressed in [16]. Lastly, in [17], a review is provided on a health management system for lithium-ion batteries with a specific focus on electric vehicle applications.

#### 2.2. Modeling, Control and Design of Power Electronic Converters (T2)

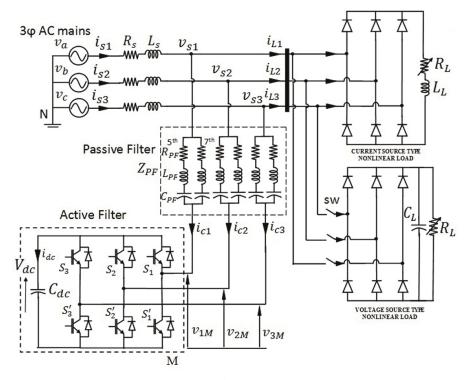

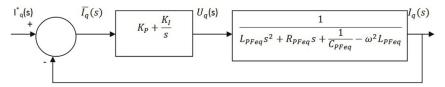

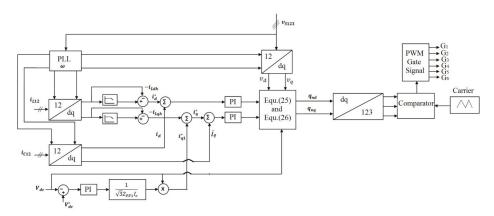

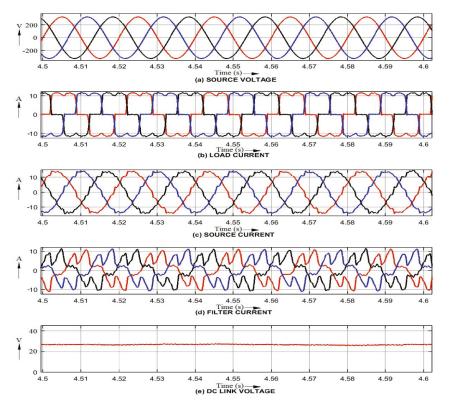

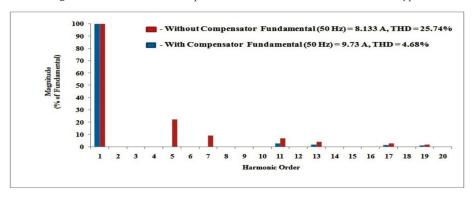

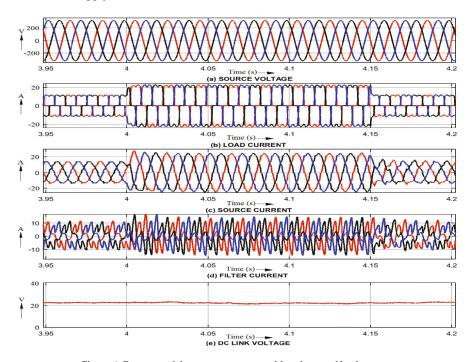

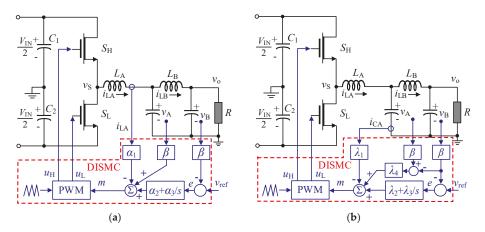

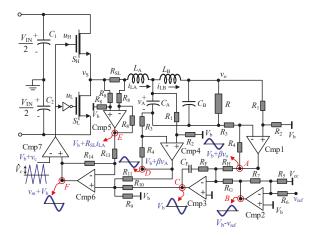

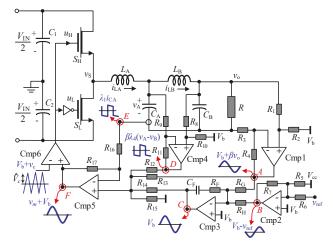

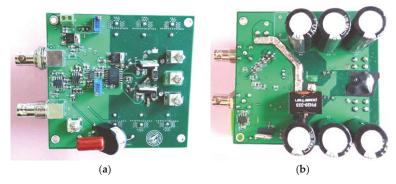

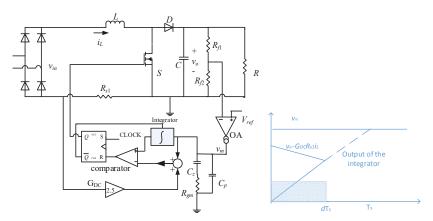

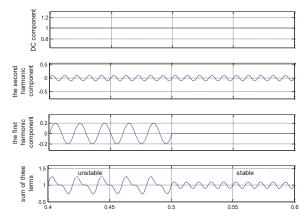

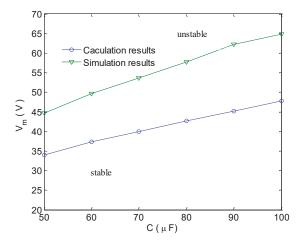

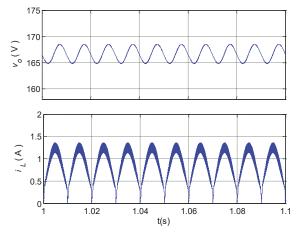

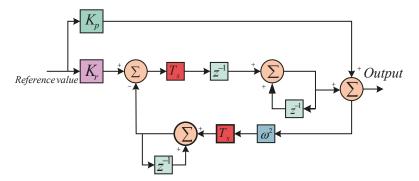

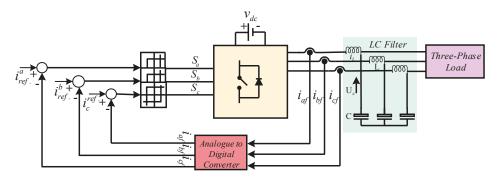

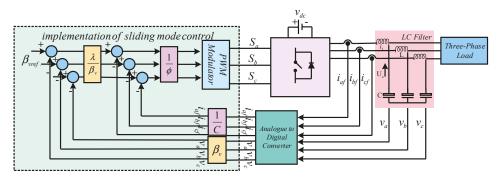

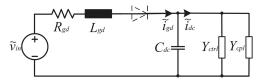

In [18], a synchronous reference frame control design methodology is provided for shunt power filters, while the sliding mode control and one-cycle controller design and stability performance of a class-D amplifier and boost power factor correction are discussed in [19,20], respectively.

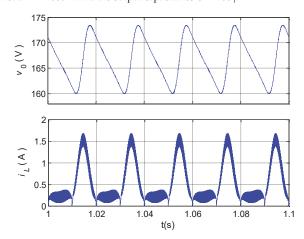

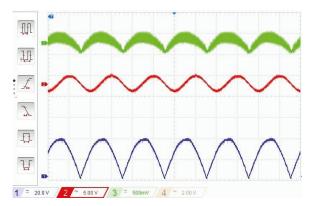

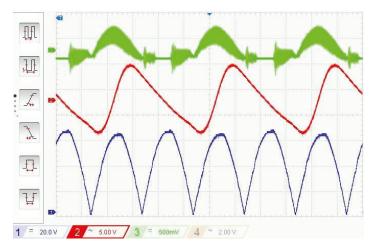

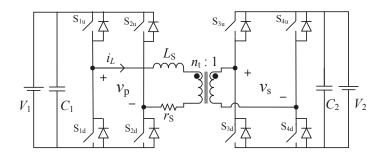

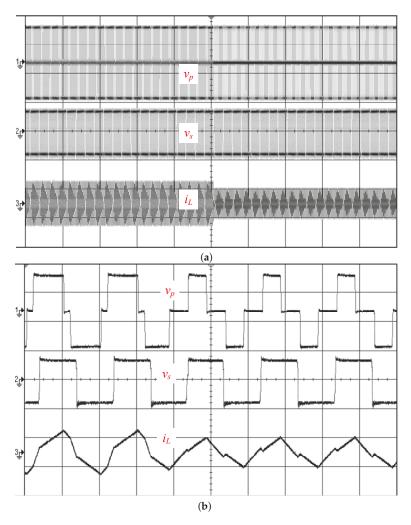

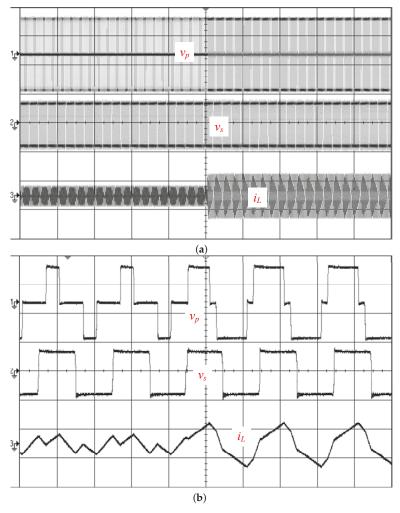

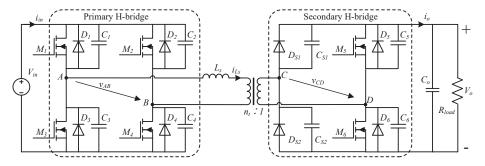

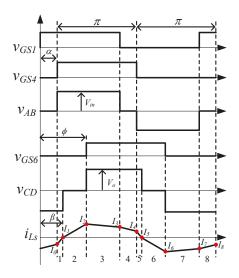

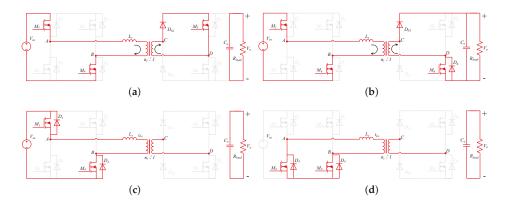

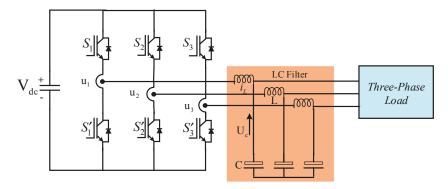

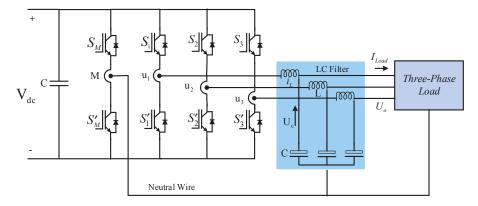

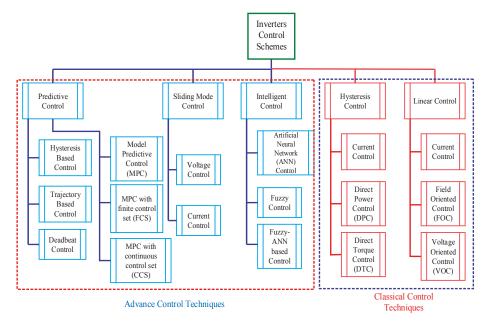

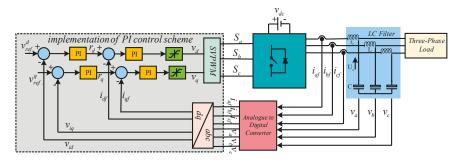

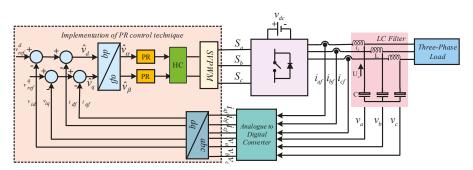

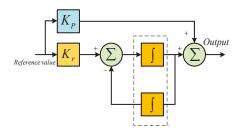

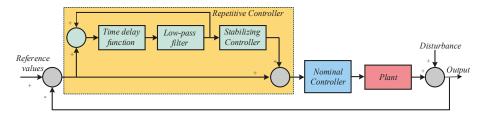

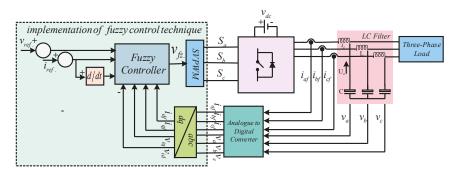

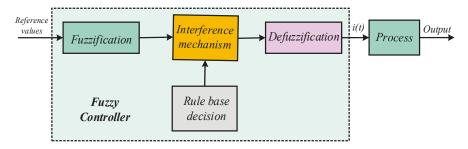

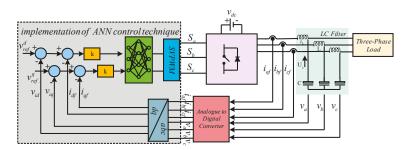

Performance evaluation and the improvement of a dual active bridge converter as one of the suitable topologies for isolated power converters are discussed in [21,22]. Lastly, digital control techniques for voltage source inverters in renewable energy applications are summarized in [23].

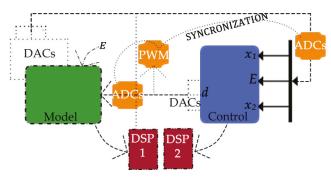

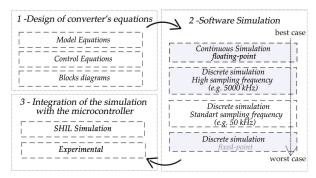

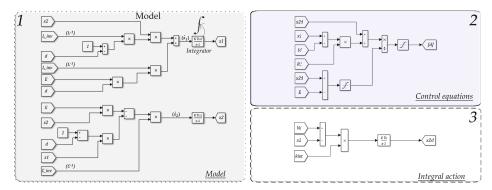

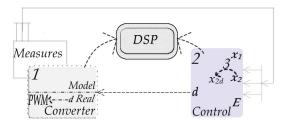

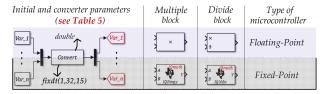

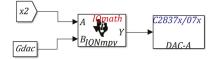

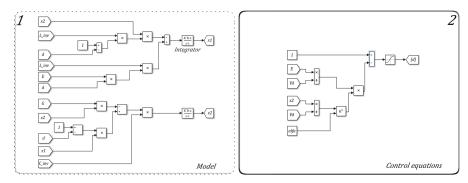

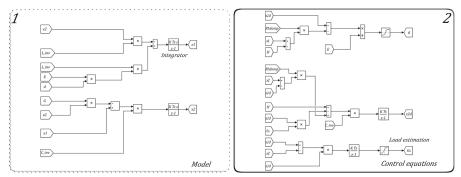

Hardware-in-the-loop (HIL) techniques are identified as effective methods for validation of power converter and/or its controller prior to full system implementation. In [24], two different HIL implementation methods suitable for nonlinear control methods are addressed, while the application of FPGA for HIL implementation and its limitations are discussed in [25].

#### 2.3. Electrical Machines, Drives and Traction Systems (T3)

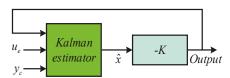

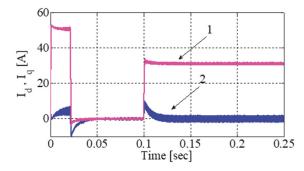

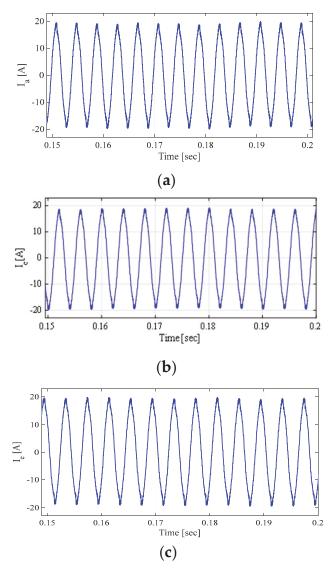

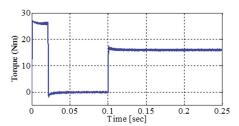

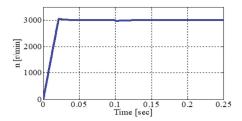

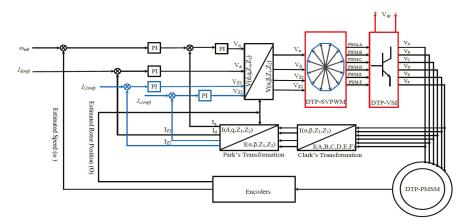

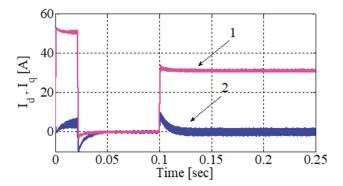

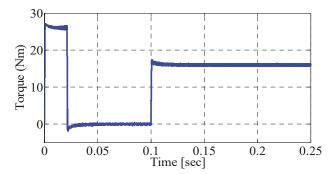

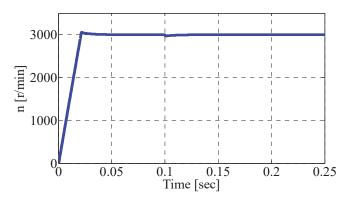

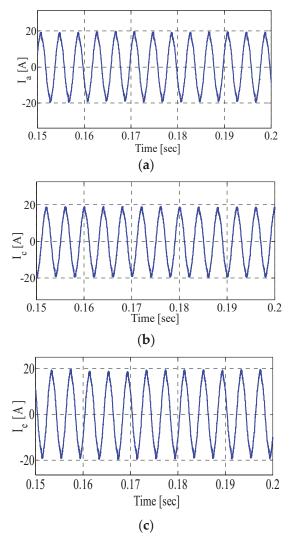

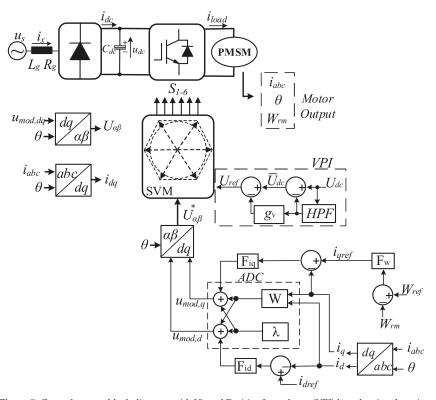

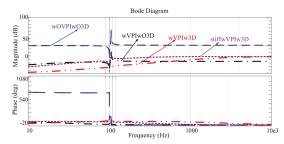

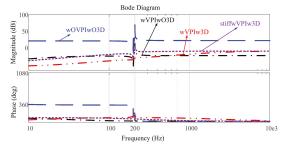

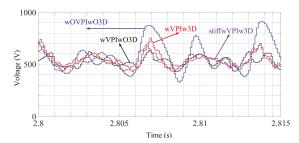

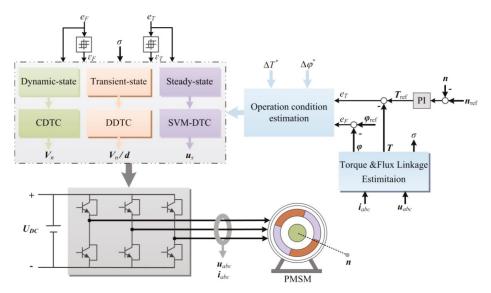

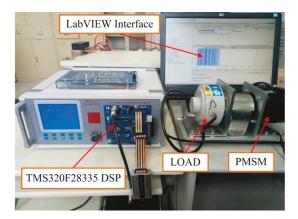

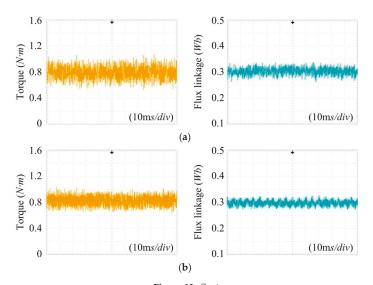

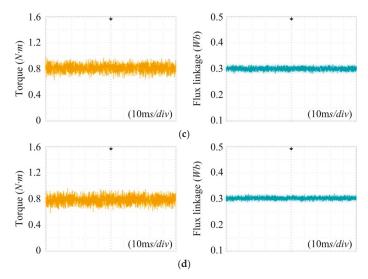

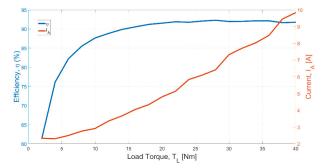

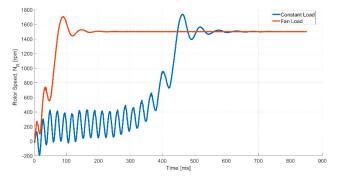

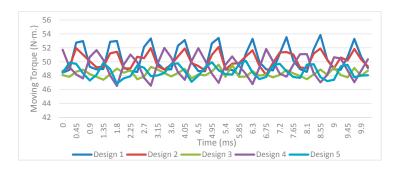

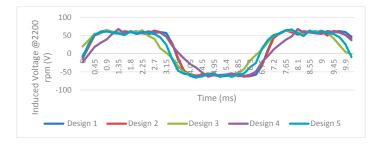

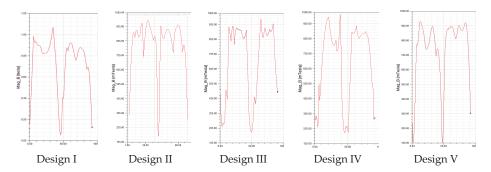

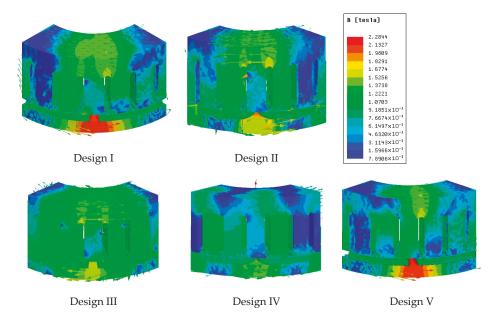

With the continuous cost reduction of power semiconductor devices, and due to be controllability of power electronics-based systems, more and more motor-driven applications are being equipped with power electronics. Thereby, there is a focus on improving the performance and stability of motor drive systems through control, utilizing multi-phase motors and the proper modeling of motors over a wide range of loading conditions. A robust control with auto-tuned closed loop control is discussed in [26]. In [27], a comparative analysis of different control structures in improving the performance of dual three-phase permanent magnet synchronous motors (PMSM) is addressed. Extending the Kalman filter-based sliding mode control of a parallel-connected two five-phase PMSM drive system is explained in [28]. Since a slim DC-link drive provides a compact drive system, improving the motor drive performance and control stability through modulation and active damping is proposed in [29]. Utilizing composite active vector modulation in improving a direct torque control scheme for PMSM is introduced in [30]. Lastly, the suitability of utilizing a line starter PMSM for industrial applications from the efficiency point of view is discussed in [31].

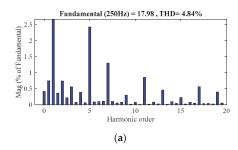

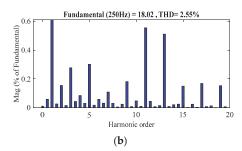

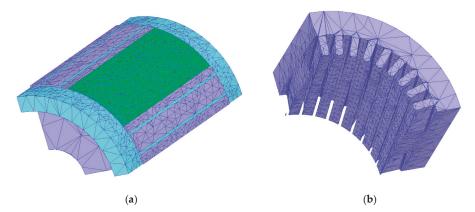

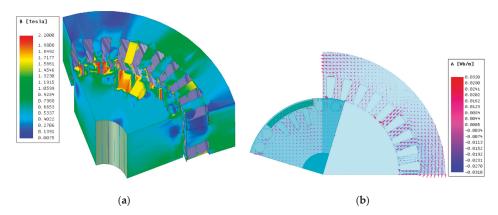

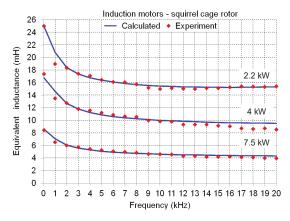

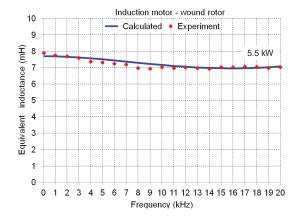

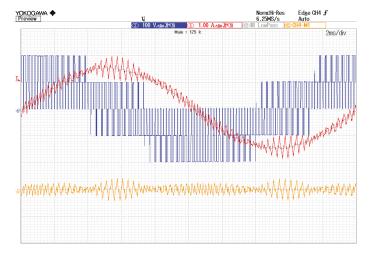

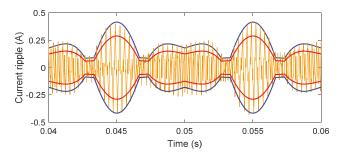

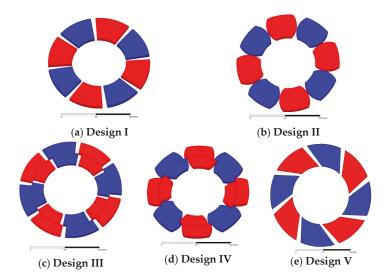

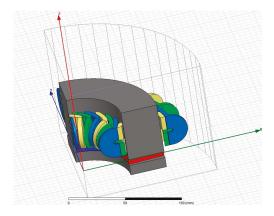

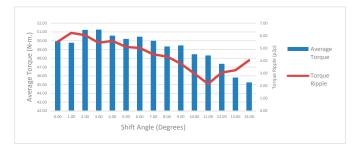

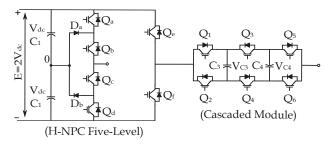

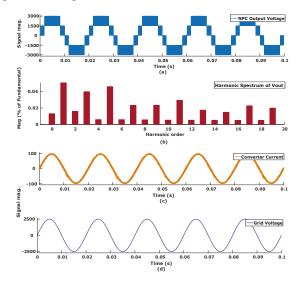

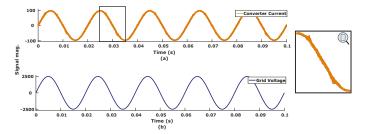

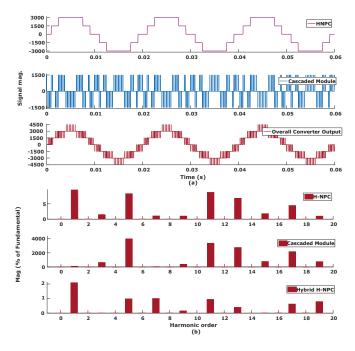

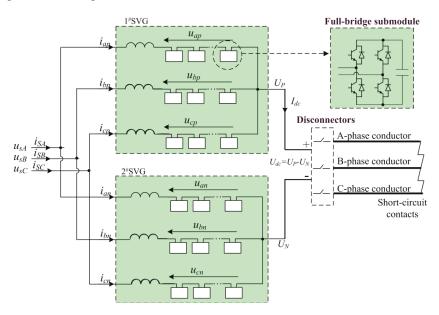

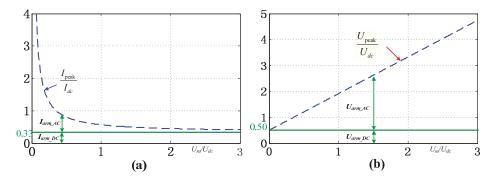

The knowledge of motor behavior through proper modeling plays an important role for motor drive system design and control. The frequency-dependent behavior of an induction motor's equivalent inductance and its importance on the output current ripple and total harmonic distortion (THD) is analyzed in [32]. In [33], 3D finite element analysis (FEA) is used to analyze the profile effect of various magnet shapes in axial flux PM motors to obtain higher efficiency. Finally, a series active filter design based on a hybrid modular multi-level converter (MMC) suitable for traction systems is introduced and analyzed in [34].

#### 2.4. Distributed Power Generation and e-Grid (T4)

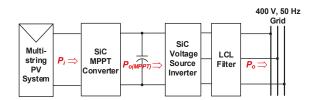

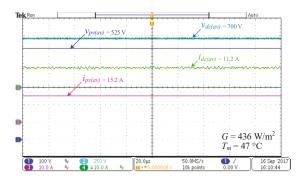

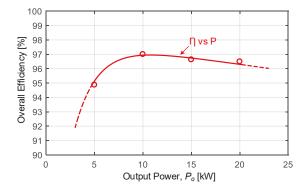

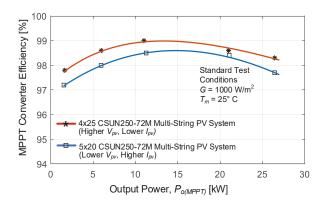

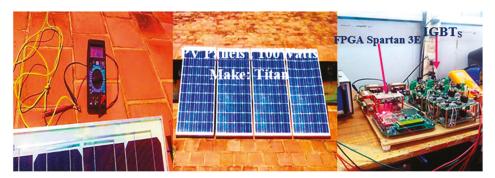

Photovoltaic (PV) applications, as they utilize renewable energy resources to reduce the carbon footprint, are being employed more and more for distributed power generation. Applying the power electronics technique for PV application is the main focus in [35–37], covering different design aspects. While [35] addresses the practical implementation of a three-level boost converter using FPGA,

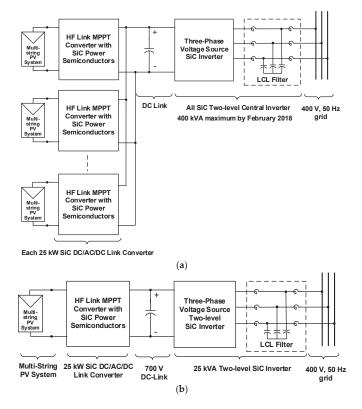

in [36], the importance of using wide band-gap devices such as silicon carbide (SiC) to achieve better performance and power density is addressed. Lastly, the application of a modular multi-level converter (MMC) based on a cascaded connection is described in [37] for PV applications. The application and optimal design of MMC is further extended in [38] for high voltage direct current (HVDC) systems. Another design aspect which has attracted attention is efficiency. In [39], the possibility of improving voltage source converter efficiency through optimal switching frequency selection is discussed. In [40], a new technique to improve power converter efficiency by reducing the switching count for a distribution static compensator (DSTATCOM) and induction motor drive applications is addressed.

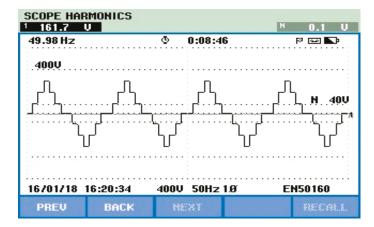

With the high penetration of power electronic systems, another aspect that again is attracting increased attention is the mitigation and control of the harmonics and EMI noise emissions of power converters. In [41], the utilization of an online selective harmonic elimination (SHE) method and particle swarm optimization to reduce harmonics is addressed, while in [42], a comprehensive review on control strategies for mitigating the dead-time effect on power converters to improve the total harmonic distortion of output waveforms is presented. With respect to EMI, modeling and proper EMI filter design in order to comply with international standards, which is of high importance, is addressed in [43,44]. Furthermore, applying active spectral shaping can maintain the generated EMI noise while reducing the size of an EMI filter in an effective method presented in [45]. Finally, applying optimization techniques for EMI filter design that not only increase the converter power density but also can make the design process automatic (reducing the time-to-market, to name one benefit) is addressed in [46].

#### 2.5. Emerging Power Electronic Technologies (Pulsed Power, Energy Storage, Others) (T5)

In this sub-topic, the first article addresses the 10 kV high-frequency switching power supply known as a pulsed power supply for plasma generation [47]. In this article, a pulsed power supply is developed for water purification.

As the second focus of this sub-topic in the energy storage area, four articles were accepted and published. The first one provides a review of the electrical circuit modeling of double layer capacitors for energy storage [48]. The reduction of battery cell inconsistency using a composite equalizer to improve overall system performance is addressed in [49]. Improvements of state-of-charge (SoC) estimation using optimization and proper filtering methods are introduced in [50]. Lastly, a review and future challenges of SoC estimation for lithium—ion batteries are provided in [51].

#### 2.6. Energy Access and Micro-Grids (T6)

Five articles have been accepted in the area of microgrids. In all of these articles, innovative control strategies have been proposed for AC, DC and hybrid AC–DC microgrids. In [52], a harmonic linearization technique has been deployed to analyze the stability of the AC microgrid in the sequence domain. Focusing more on the higher-level control, an innovative switching control strategy has been developed for EV charging stations to minimize their effect on the performance of a hybrid microgrid system in [53]. In [54], a power electronic converter interface has been used to allow for the variable-speed operation of hydro-pumped energy storage. On the grid side, this achieved better frequency and voltage regulation compared to scenarios without power electronic interfaces. An islanding mechanism has been proposed for renewable-based microgrids in [55], while an accurate load-sharing even in the presence of faulty communication links was developed for DC microgrids in [56].

#### 2.7. Wireless Power Transfer Systems (T7)

Wireless power transfer (WPT) has emerged as an innovative technology to simplify the charging process, and this is the focus of the last four articles. The importance of synchronization in mitigating power oscillations and ensuring system stability is introduced in [57]. In [58], WPT system efficiency

improvement and size reduction is considered by adding a single-switch boost stage at the secondary side, while in [59], the possibility of efficiency improvement using a current-fed inverter is discussed. The simulation modeling of an induction power transfer (IPT) as a replica of a 2-kW IPT charger for an electric vehicle battery charger is addressed in [60,61]. Lastly, in [62], a comprehensive review of WPT system topologies, structures and EMI diagnostics is presented.

#### 3. Concluding Remarks

Although the 21st century can be identified as the golden age of power electronics applications, more in-depth research and development still need to be carried out in this area in order to accelerate the deployment of power electronics applications. This requires further improvements in the areas of power converter reliability, control stability and efficiency, and also the proper modeling of the system itself as well as the system around the application. Furthermore, providing electromagnetic compatibility at both the device level and system level is necessary to ensure interoperability and compatibility, which can be a challenging issue with WBG-based power electronic systems, as mentioned in the Introduction. In addition, the interactions among multitude power converters and the presence of non-ideal conditions, which may lead to instability issues, especially in distributed generation systems, call for further investigation. Combined multi-disciplinary efforts from both academia and industry are essential to provide a brighter future for power electronics applications and enable smarter and carbon-free future power grids.

**Author Contributions:** The authors worked together and contributed equally during the editorial process of this special issue.

Funding: This research received no external funding.

**Acknowledgments:** The guest editors would like to thank all authors for their excellent contribution to this Special Issue on Applications of Power Electronics. They are also thanful for the dedicated effort of all the reviewers who contributed to the reviewing process. Finally, our gratitude goes to the editorial board of MDPI *Electronics* journal for giving us the opportunity to host this special issue, and to the *Electronics* editorial office staff for their hard and precise work.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Davari, P.; Yang, Y.; Zare, F.; Blaabjerg, F. A Multipulse Pattern Modulation Scheme for Harmonic Mitigation in Three-Phase Multimotor Drives. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 174–185. [CrossRef]

- Zare, F.; Soltani, H.; Kumar, D.; Davari, P.; Delpino, H.A.M.; Blaabjerg, F. Harmonic Emissions of Three-Phase Diode Rectifiers in Distribution Networks. *IEEE Access* 2017, 5, 2819–2833.

- Davari, P.; Yang, Y.; Zare, F.; Blaabjerg, F. Predictive Pulse-Pattern Current Modulation Scheme for Harmonic Reduction in Three-Phase Multidrive Systems. IEEE Trans. Ind. Electron. 2016, 63, 5932–5942. [CrossRef]

- Davari, P.; Blaabjerg, F.; Hoene, E.; Zare, F. Improving 9–150 kHz EMI Performance of Single-Phase PFC Rectifier. In Proceedings of the CIPS 2018, 10th International Conference on Integrated Power Electronics Systems, Stuttgart, Germany, 20–22 March 2018; pp. 1–6.

- Wang, H.; Davari, P.; Wang, H.; Kumar, D.; Zare, F.; Blaabjerg, F. Lifetime Estimation of DC-Link Capacitors in Adjustable Speed Drives Under Grid Voltage Unbalances. *IEEE Trans. Power Electron.* 2019, 34, 4064–4078. [CrossRef]

- Dragicevic, T.; Wheeler, P.; Blaabjerg, F. Artificial Intelligence Aided Automated Design for Reliability of Power Electronic Systems. *IEEE Trans. Power Electron.* 2019. [CrossRef]

- Davari, P.; Kristensen, O.; Iannuzzo, F. Investigation of acoustic emission as a non-invasive method for detection of power semiconductor aging. *Microelectron. Reliab.* 2018, 88–90, 545–549. [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. An overview of assessment methods for synchronization stability of grid-connected converters under severe symmetrical grid faults. *IEEE Trans. Power Electron.* 2019. [CrossRef]

- Dragicevic, T.; Novak, M. Weighting Factor Design in Model Predictive Control of Power Electronic Converters: An Artificial Neural Network Approach. IEEE Trans. Ind. Electron. 2019. [CrossRef]

- Peyghami, S.; Davari, P.; Mokhtari, H.; Blaabjerg, F. Decentralized Droop Control in DC Microgrids Based on a Frequency Injection Approach. *IEEE Trans. Smart Grid* 2019. [CrossRef]

- 11. Heydari, R.; Gheisarnejad, M.; Khooban, M.H.; Dragicevic, T.; Blaabjerg, F. Robust and Fast Voltage-Source-Converter (VSC) Control for Naval Shipboard Microgrids. *IEEE Trans. Power Electron.* **2019.** [CrossRef]

- Dragičević, T. Dynamic Stabilization of DC Microgrids with Predictive Control of Point-of-Load Converters. IEEE Trans. Power Electron. 2018, 33, 10872–10884. [CrossRef]

- Dragičević, T. Model Predictive Control of Power Converters for Robust and Fast Operation of AC Microgrids. IEEE Trans. Power Electron. 2018, 33, 6304–6317. [CrossRef]

- 14. Cheng, H.; Chen, W.; Wang, C.; Deng, J. Open Circuit Fault Diagnosis and Fault Tolerance of Three-Phase Bridgeless Rectifier. *Electronics* **2018**, 7, 291. [CrossRef]

- Burriel-Valencia, J.; Puche-Panadero, R.; Martinez-Roman, J.; Sapena-Bano, A.; Pineda-Sanchez, M.; Perez-Cruz, J.; Riera-Guasp, M. Automatic Fault Diagnostic System for Induction Motors under Transient Regime Optimized with Expert Systems. *Electronics* 2019, 8, 6. [CrossRef]

- Rangari, S.; Suryawanshi, H.; Renge, M. New fault-tolerant control strategy of five-phase induction motor with four-phase and three-phase modes of operation. *Electronics* 2018, 7, 159. [CrossRef]

- 17. Omariba, Z.; Zhang, L.; Sun, D. Review on health management system for lithium-ion batteries of electric vehicles. *Electronics* 2018, 7, 72. [CrossRef]

- Balasubramanian, R.; Parkavikathirvelu, K.; Sankaran, R.; Amirtharajan, R. Design, Simulation and Hardware Implementation of Shunt Hybrid Compensator Using Synchronous Rotating Reference Frame (SRRF)-Based Control Technique. *Electronics* 2019, 8, 42. [CrossRef]

- Zaman, H.; Zheng, X.; Wu, X.; Khan, S.; Ali, H. A fixed-frequency sliding-mode controller for fourth-order class-D amplifier. *Electronics* 2018, 7, 261. [CrossRef]

- Zhang, R.; Ma, W.; Wang, L.; Hu, M.; Cao, L.; Zhou, H.; Zhang, Y. Line Frequency Instability of One-Cycle-Controlled Boost Power Factor Correction Converter. *Electronics* 2018, 7, 203. [CrossRef]

- 21. Zhang, Y.; Li, X.; Sun, C.; He, Z. Improved Step Load Response of a Dual-Active-Bridge DC–DC Converter. *Electronics* **2018**, *7*, 185. [CrossRef]

- 22. Lu, M.; Li, X. Performance Evaluation of a Semi-Dual-Active-Bridge with PPWM Plus SPS Control. *Electronics* **2018**, *7*, 184. [CrossRef]

- 23. Tahir, S.; Wang, J.; Baloch, M.; Kaloi, G. Digital control techniques based on voltage source inverters in renewable energy applications: A review. *Electronics* **2018**, *7*, 18. [CrossRef]

- 24. Rosa, A.; Silva, M.; Campos, M.; Santana, R.; Rodrigues, W.; Morais, L. Shil and dhil simulations of nonlinear control methods applied for power converters using embedded systems. *Electronics* **2018**, *7*, 241. [CrossRef]

- Sanchez, A.; Todorovich, E.; de Castro, A. Exploring the limits of floating-point resolution for hardware-in-the-loop implemented with fpgas. *Electronics* 2018, 7, 219. [CrossRef]

- Kim, S.K.; Lee, K.B. Robust DC-Link Voltage Tracking Controller with Variable Control Gain for Permanent Magnet Synchronous Generators. *Electronics* 2018, 7, 339. [CrossRef]

- Ahmad, M.; Wang, Z.; Yan, S.; Wang, C.; Wang, Z.; Zhu, C.; Qin, H. Comparative Analysis of Two and Four Current Loops for Vector Controlled Dual-Three Phase Permanent Magnet Synchronous Motor. *Electronics* 2018, 7, 269. [CrossRef]

- 28. Kamel, T.; Abdelkader, D.; Said, B.; Padmanaban, S.; Iqbal, A. Extended Kalman filter based sliding mode control of parallel-connected two five-phase PMSM drive system. *Electronics* **2018**, 7, 14. [CrossRef]

- Aksoz, A.; Song, Y.; Saygin, A.; Blaabjerg, F.; Davari, P. Improving Performance of Three-Phase Slim DC-Link Drives Utilizing Virtual Positive Impedance-Based Active Damping Control. *Electronics* 2018, 7, 234. [CrossRef]

- Yuan, T.; Wang, D. Performance Improvement for PMSM DTC System through Composite Active Vectors Modulation. *Electronics* 2018, 7, 263. [CrossRef]

- 31. Zöhra, B.; Akar, M.; Eker, M. Design of A Novel Line Start Synchronous Motor Rotor. *Electronics* **2019**, *8*, 25. [CrossRef]

- 32. Srndovic, M.; Fišer, R.; Grandi, G. Analysis of Equivalent Inductance of Three-phase Induction Motors in the Switching Frequency Range. *Electronics* **2019**, *8*, 120. [CrossRef]

- 33. Cetin, E.; Daldaban, F. Analyzing the profile effects of the various magnet shapes in axial flux PM motors by means of 3D-FEA. *Electronics* **2018**, *7*, 13. [CrossRef]

- Ali, M.; Khan, M.; Xu, J.; Faiz, M.; Ali, Y.; Hashmi, K.; Tang, H. Series Active Filter Design Based on Asymmetric Hybrid Modular Multilevel Converter for Traction System. *Electronics* 2018, 7, 134. [CrossRef]

- Sulake, N.; Devarasetty Venkata, A.; Choppavarapu, S. FPGA Implementation of a Three-Level Boost Converter-fed Seven-Level DC-Link Cascade H-Bridge inverter for Photovoltaic Applications. *Electronics* 2018, 7, 282. [CrossRef]

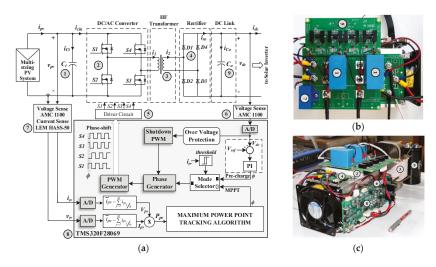

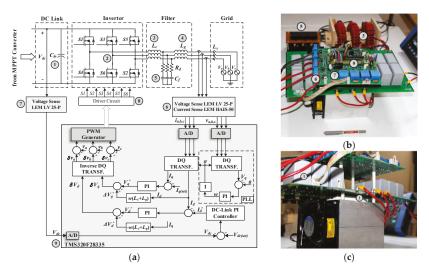

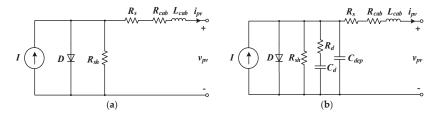

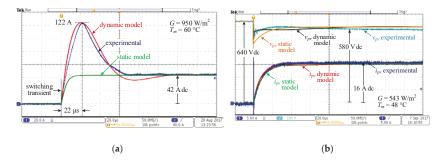

- 36. Öztürk, S.; Canver, M.; Çadırcı, I.; Ermiş, M. All SiC grid-connected PV supply with HF link MPPT converter: System design methodology and development of a 20 kHz, 25 kVA prototype. *Electronics* **2018**, 7, 85. [CrossRef]

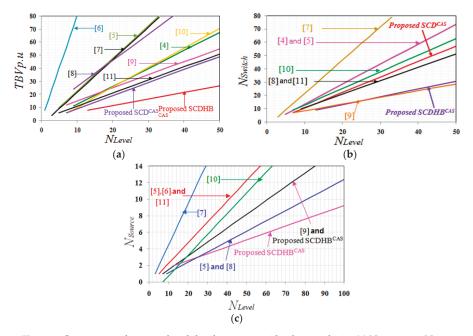

- Karthikeyan, D.; Vijayakumar, K. Generalized Cascaded Symmetric and Level Doubling Multilevel Converter Topology with Reduced THD for Photovoltaic Applications. *Electronics* 2019, 8, 161.

- Lu, J.; Huang, Q.; Mao, X.; Tan, Y.; Zhu, S.; Zhu, Y. Optimized Design of Modular Multilevel DC De-Icer for High Voltage Transmission Lines. *Electronics* 2018, 7, 204. [CrossRef]

- 39. Albatran, S.; Smadi, I.; Ahmad, H.; Koran, A. Online optimal switching frequency selection for grid-connected voltage source inverters. *Electronics* **2017**, *6*, 110. [CrossRef]

- 40. Jibhakate, C.; Chaudhari, M.; Renge, M. A Reduced Switch AC-AC Converter with the Application of D-STATCOM and Induction Motor Drive. *Electronics* 2018, 7, 110. [CrossRef]

- Güvengir, U.; Çadırcı, I.; Ermiş, M. On-Line Application of SHEM by Particle Swarm Optimization to Grid-Connected, Three-Phase, Two-Level VSCs with Variable DC Link Voltage. *Electronics* 2018, 7, 151.

- 42. Ji, Y.; Yang, Y.; Zhou, J.; Ding, H.; Guo, X.; Padmanaban, S. Control Strategies of Mitigating Dead-time Effect on Power Converters: An Overview. *Electronics* **2019**, *8*, 196. [CrossRef]

- 43. Varajão, D.; Esteves Araújo, R.; Miranda, L.; Peças Lopes, J. EMI Filter Design for a Single-stage Bidirectional and Isolated AC–DC Matrix Converter. *Electronics* **2018**, 7, 318. [CrossRef]

- 44. Zhu, H.; Liu, D.; Zhang, X.; Qu, F. Reliability of Boost PFC Converters with Improved EMI Filters. *Electronics* **2018**, *7*, 413. [CrossRef]

- 45. Nguyen, V.; Huynh, H.; Kim, S.; Song, H. Active EMI Reduction Using Chaotic Modulation in a Buck Converter with Relaxed Output LC Filter. *Electronics* **2018**, *7*, 254. [CrossRef]

- 46. Giglia, G.; Ala, G.; Di Piazza, M.; Giaconia, G.; Luna, M.; Vitale, G.; Zanchetta, P. Automatic EMI filter design for power electronic converters oriented to high power density. *Electronics* **2018**, *7*, 9. [CrossRef]

- 47. Krishna, T.; Sathishkumar, P.; Himasree, P.; Punnoose, D.; Raghavendra, K.; Naresh, B.; Rana, R.; Kim, H.J. 4T Analog MOS Control-High Voltage High Frequency (HVHF) Plasma Switching Power Supply for Water Purification in Industrial Applications. *Electronics* 2018, 7, 245. [CrossRef]

- 48. Jiya, I.; Gurusinghe, N.; Gouws, R. Electrical circuit modelling of double layer capacitors for power electronics and energy storage applications: A review. *Electronics* **2018**, 7, 268. [CrossRef]

- 49. Lai, X.; Jiang, C.; Zheng, Y.; Gao, H.; Huang, P.; Zhou, L. A novel composite equalizer based on an additional cell for series-connected lithium-ion cells. *Electronics* **2018**, *7*, 366. [CrossRef]

- 50. Lai, X.; Yi, W.; Zheng, Y.; Zhou, L. An all-region state-of-charge estimator based on global particle swarm optimization and improved extended kalman filter for lithium-ion batteries. *Electronics* **2018**, *7*, 321. [CrossRef]

- 51. Rivera-Barrera, J.; Muñoz-Galeano, N.; Sarmiento-Maldonado, H. SoC estimation for lithium-ion batteries: Review and future challenges. *Electronics* **2017**, *6*, 102. [CrossRef]

- 52. Rahman, A.; Syed, I.; Ullah, M. Small signal stability of a balanced three-phase ac microgrid using harmonic linearization: Parametric-based analysis. *Electronics* **2019**, *8*, 12. [CrossRef]

- 53. Kamal, T.; Karabacak, M.; Hassan, S.; Fernández-Ramírez, L.; Riaz, M.; Khan, M.; Khan, L. Energy management and switching control of PHEV charging stations in a hybrid smart micro-grid system. *Electronics* **2018**, *7*, 156. [CrossRef]

- 54. Bitew, G.; Han, M.; Mekonnen, S.; Simiyu, P. A Variable Speed Pumped Storage System Based on Droop-Fed Vector Control Strategy for Grid Frequency and AC-Bus Voltage Stability. *Electronics* **2018**, 7, 108. [CrossRef]

- 55. Hashmi, K.; Mansoor Khan, M.; Jiang, H.; Umair Shahid, M.; Habib, S.; Talib Faiz, M.; Tang, H. A virtual micro-islanding-based control paradigm for renewable microgrids. *Electronics* **2018**, *7*, 105. [CrossRef]

- Shahid, M.; Khan, M.; Hashmi, K.; Habib, S.; Jiang, H.; Tang, H. A control methodology for load sharing system restoration in islanded DC micro grid with faulty communication links. *Electronics* 2018, 7, 90. [CrossRef]

- 57. Liu, X.; Jin, N.; Yang, X.; Wang, T.; Hashmi, K.; Tang, H. A Novel Synchronization Technique for Wireless Power Transfer Systems. *Electronics* **2018**, *7*, 319. [CrossRef]

- 58. Liu, X.; Jin, N.; Yang, X.; Hashmi, K.; Ma, D.; Tang, H. A Novel Single-switch Phase Controlled Wireless Power Transfer System. *Electronics* **2018**, 7, 281. [CrossRef]

- 59. Wang, T.; Liu, X.; Jin, N.; Tang, H.; Yang, X.; Ali, M. Wireless Power Transfer for Battery Powering System. *Electronics* **2018**, *7*, 178. [CrossRef]

- Vázquez, J.; Roncero-Sánchez, P.; Parreño Torres, A. Simulation Model of a 2-kW IPT Charger with Phase-Shift Control: Validation through the Tuning of the Coupling Factor. *Electronics* 2018, 7, 255. [CrossRef]

- 61. Vázquez, J.; Roncero-Sánchez, P.; Parreño Torres, A. Correction: Vázquez, J. et al. Simulation Model of a 2-kW IPT Charger with Phase-Shift Control: Validation through the Tuning of the Coupling Factor. *Electronics* 2018, 7, 255. *Electronics* 2018, 7, 385. [CrossRef]

- 62. Abou Houran, M.; Yang, X.; Chen, W. Magnetically coupled resonance WPT: Review of compensation topologies, resonator structures with misalignment, and EMI diagnostics. *Electronics* **2018**, 7, 296. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

## Open Circuit Fault Diagnosis and Fault Tolerance of Three-Phase Bridgeless Rectifier

#### Hong Cheng, Wenbo Chen \*, Cong Wang and Jiaqing Deng

School of Mechanical Electronic & Information Engineering, China University of Mining and Technology Beijing, Ding No. 11 Xueyuan Road, Haidian District, Beijing 100083, China; chengh@cumtb.edu.cn (H.C.); wangc@cumtb.edu.cn (C.W.); dengjiaqingrae@163.com (J.D.)

\* Correspondence: sglm.chen@gmail.com; Tel.: +86-176-0013-1007

Received: 5 October 2018; Accepted: 30 October 2018; Published: 1 November 2018

Abstract: Bridgeless rectifiers are widely used in many applications due to a unity power factor, lower conduction loss and high efficiency, which does not need bidirectional energy transmission. In this case, the potential failures are threatening the reliability of these converters in critical applications such as power supply and electric motor driver. In this paper, open circuit fault is analyzed, taking a three-phase bridgeless as an example. Interference on both the input and output side are considered. Then, the fault diagnosis method including detection and location, and fault tolerance through additional switches are proposed. At last, simulation and experiments based on the hardware in loop technology are used to validate the feasibility of fault diagnosis and fault tolerance methodology.

Keywords: three-phase bridgeless rectifier; fault diagnosis; fault tolerant control; hardware in loop

#### 1. Introduction

Multilevel converters have been widely used in middle- and high-voltage application fields in the past decades, such as renewable energy, adjustable speed drive, power transmission network, electric vehicle [1] etc. Topologies of these converters including H Bridge-based, neutral point clamping-based and bridgeless-based are most popular in literatures. Recently, bridgeless-based topologies have drawn increasing attention from industry and academia due to its high efficiency, low loss and simplification control strategy [2–6]. Compared with H Bridge-based converters, these bridgeless-based converters cannot work as inverters. However, considering that the applications are mostly pumps, fans and compressors which only need the power flowing unidirectionally [7], H-bridge-based converter has gradually been substituted by bridgeless-based converters as a pulse width modulation (PWM) rectifier in these fields. The bridgeless-based converter as a rectifier provides a sinusoidal input current at unity power factor and a controllable dc output voltage.

With the growing power switch numbers and power density, reliability of power electronic converters is increasingly important because the malfunctions are unacceptable and cause serious losses (e.g., nonscheduled downtime) in the critical applications. As a kind of electric energy conversion device, three-phase bridgeless converter (3-BLC) also endures high frequency voltage shock, over temperature impact, overload and improper driving signal. Semi-conductor devices, especially power switches, will fail more easily than other components. As discussed in Reference [8], the power switches contribute to 31% of failures, which are the most fragile components among capacitors, gate drivers, resistors and inductors. Power switches faults are usually caused by bond-wire lift-off or solder cracking, which will lead to an open circuit or short circuit of converters. The faults are named open circuit faults (OCF) and short circuit faults (SCF) respectively. An SCF will cause a large current and result in system shutdown, so hardware-based approaches such as fast fuses or breakers to transfer an SCF to an OCF are generally used. An OCF will not shutdown a system immediately but it degrades

the performance inconspicuously. These may, in turn, cause secondary faults. Therefore, it is necessary to study a fault diagnosis and tolerance method for power switches OCF of the rectifier in this article.

In the past decade, numerous fault diagnosis and tolerance methods have been proposed for power electronic converters in the literature [9–16]. However, there are a few research works for ac-dc rectifiers, especially bridgeless rectifiers. For example, a diagnosis method based on a mixed logical dynamic model and residual generation was applied to a single-phase rectifier in a railway electrical traction drive system [17]. This method was fast, simple and stable, but it does not suit three-phase systems. For three-phase conditions, a current waveforms-based similarity analysis method for a three-phase PWM rectifier was proposed in Reference [18]; current waveforms were analyzed pairwise to diagnose an open circuit fault. There was a critical drawback of this method that it ignored the three-phase voltage imbalance, which is often seen for grid. In Reference [19], a fault tolerance control with additional devices for three-phase soft-switching mode rectifier is proposed. The circuit configuration had two extra center-tapped autotransformers and three more toggle switches compared with the traditional system. This method was more suitable for new design, but more retrofit cost was demanded for the existing systems. Considering the dc voltage decrease by OCF, Reference [20] proposed a fault tolerant method for the three-level rectifier in a wind turbine system, which was implemented by adding a compensation value to the reference voltages. The proposed method preserved the power factor under faulty conditions utilizing the redundancy of the switching devices, where the 3-BLC does not have such ability.

This study aims for an OCF diagnosis and tolerance method for bridgeless-based rectifiers [21–23], especially the 3-BLC. The contribution of this paper is to propose a fault feature extraction method for 3-BLC, and a fault tolerant method based on an extra two switches. The fault features were extracted from the three-phase currents. Load sudden change, source voltage imbalance or fluctuation and harmonic interference have been considered to prevent the impact on the proposed method. After that, the OCF is identified by a mixed logical model-based algorithm. When a fault was diagnosed, the drive signals of the faulty phase were redistributed artificially by the additional switches. Thus, it will maintain the current path in failure condition and make the 3-BLC still work as normal.

The rest of this paper is organized as follows. In Section 2, the mathematical model of single and three-phase bridgeless converters are analyzed. In Section 3, the fault diagnosis with an improvable feature extraction method is proposed. Section 4 details the fault tolerant implementation through additional devices. System validation using simulation and experiment data is provided in Section 5. Finally, conclusions are drawn in Section 6.

#### 2. Basic Principles of Three-Phase Bridgeless Converters

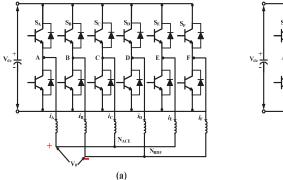

#### 2.1. Structure and Operation of 3-BLC

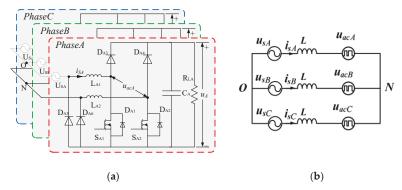

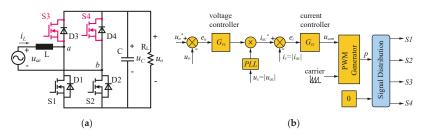

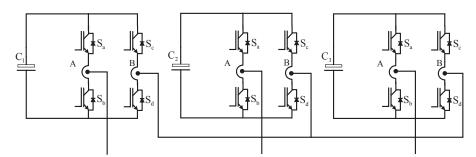

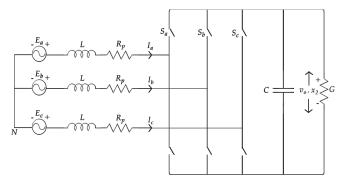

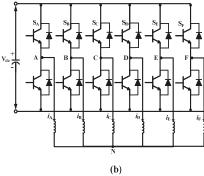

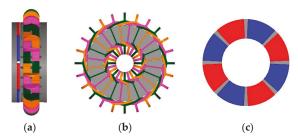

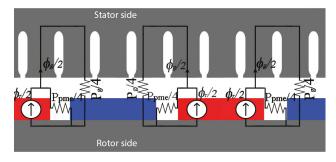

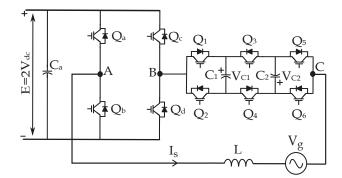

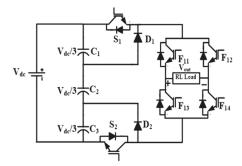

A three-phase bridgeless converter (3-BLC) is shown in Figure 1a. As can be seen, this three-phase converter is expanded from a single-phase dual-boost bridgeless structure, which has additional slow-recovery diodes D5 & D6 and two boost inductors L1 & L2 to reduce common mode noise [24,25]. Compared to the H bridge structure, bridgeless structure reduces 50% of fully controlled switches. Therefore, the control circuits, gate drivers, as well as protection units are greatly reduced, thus decreasing the system complexity and switching losses drastically [26]. The equivalent ac side circuit is depicted in Figure 1b and the mathematical model of 3-BLC can be expressed as

$$\begin{cases} L\frac{di_{sA}}{dt} = u_{sA} - u_{acA} - u_{NO} \\ L\frac{di_{sB}}{dt} = u_{sB} - u_{acB} - u_{NO} \\ L\frac{di_{sC}}{dt} = u_{sC} - u_{acC} - u_{NO} \end{cases}$$

(1)

where  $u_{acA}$ ,  $u_{acB}$ ,  $u_{acC}$  are the ac voltages of phase A, B and C;  $u_{NO}$  is the neutral point voltage; L is the inductance of L1 and L2.

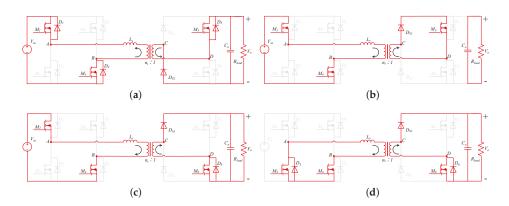

**Figure 1.** Three-phase bridgeless converter topology and equivalent ac side circuit. (a) Circuit topology; (b) the equivalent ac side circuit.

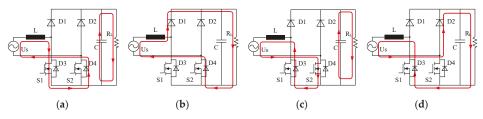

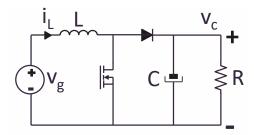

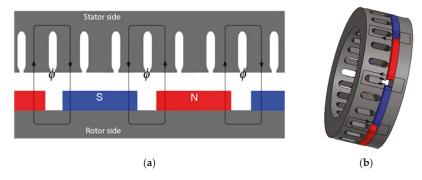

In order to clarify the analysis process, in this study, the slow-recovery diodes are temporarily substituted by the body diodes and the boost inductors are equivalent to an inductor L. Therefore, taking a single-phase bridgeless rectifier as an example, Figure 2 shows its principles on four operating modes. In this study, the power switches S1 and S2 are synchronously turned ON and OFF, which is named synchronous control scheme. Define S as a switch function of this converter. When S=1, S1 and S2 are both turned ON, the power is transferred to power storage inductor L as shown in Figure 2a,c. When S=0, S1 and S2 are both turned OFF, the power stored in inductor L is transferred to the load side as shown in Figure 2b,d. Then, a bulky electrolytic capacitor C is employed to buffer the power and, hence, smooth the output voltage. Thus, the steady-state mathematic model can be yielded by applying KVL and KCL as following.

where L is the inductance of the power storage inductor, C is the capacitance of the output capacitor,  $R_L$  is the resistance of load,  $i_L$  is the input current,  $u_C$  is the capacitor voltage,  $u_S$  is the ac voltage, and  $S^* = 1 - S$ .

Applying the volt-second balance and ampere-second balance principles to Equation (2) derives

$$\begin{cases}

i_{L} = \frac{u_{s}}{R_{L}(1-d)^{2}} \\

u_{C} = \frac{u_{s}}{1-d}

\end{cases}$$

(3)

where d is the duty cycle.

**Figure 2.** Basic bridgeless PFC rectifier topology and operating mode. (a) Mode 1 in positive ac cycle; (b) Mode 2 in positive ac cycle l; (c) Mode 3 in negative ac cycle; (d) Mode 4 in negative ac cycle.

#### 2.2. Open Circuit Fault Analysis

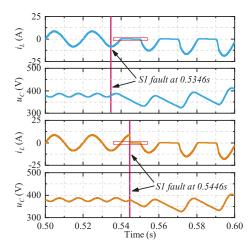

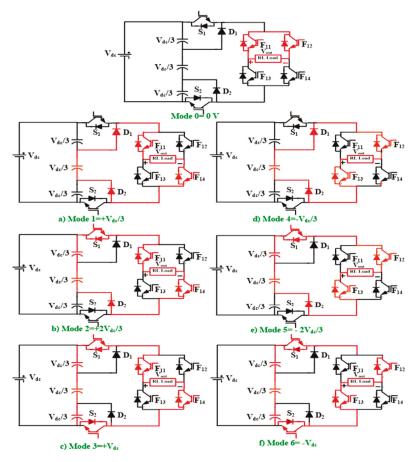

As described above, there are four operating modes which generate through the ac voltage polarity and the switching states. When a switch fails due to physical damage or improperly driving signal, the corresponding operating mode no longer exists. This will cause changes on the related signals, which is called fault features, and is the theoretical foundation of fault detection and location. In the rest of this section, fault features of S1 OCF were analyzed as an example. Because power switches are the most fragile component and an SCF can be converted to an OCF by fast fuses immediately, the current and voltage waveforms shown in this section were acquired by simulations. The fault times were set in the positive and negative ac cycle of the input voltage respectively.

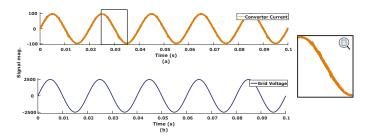

When an OCF occurs on switch S1, the power storage path as shown in Figure 2a is disconnected. Therefore, the converter works only in power discharging mode as shown in Figure 2b. However, in the negative ac cycle, the converter works properly because S1 is not in both a power charging and discharging path. The waveform of the input current and capacitor voltage during S1 open circuit fault at different half cycles are shown in Figure 3. Because it is a non-resonant circuit, the large impedance makes the input current fell into nearly zero after S1 failed in negative ac cycle, but it seems normal in positive ac cycles. The capacitor voltage resembles the input current which double frequency ripple disappears obviously after 0.5446 s, but it seems no change after 0.5346s until a positive ac cycle. The features of input current and capacitor voltage before and after switch S2 fails are just like S1.

Figure 3. Input current and capacitor voltage waveforms at the time of S1 fault in positive and negative cycles.

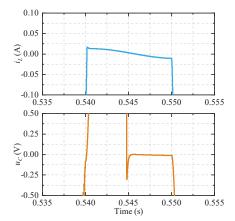

The dynamic details of the input current inside the red frame of Figure 3 are also shown in Figure 4. According to Equation (3), the duty cycle of one switch will mutate to zero when it occurred an OCF. Since the switching period no longer existed, the assumption that the input voltage is constant during the switching cycle was no longer valid. Due to the impedance of the inductor to the low frequency signal, the input current became zero after the energy in the inductor was released. The load voltage was maintained by the DC capacitor until another ac cycle which was not affected by the fault.

Figure 4. Dynamic details of input current and capacitor voltage waveforms at the time of S2 fault.

#### 2.3. Input Side Interferences

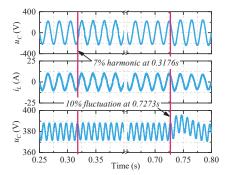

Voltage fluctuations and harmonic pollution are unavoidable on the input side. They will affect the characteristics of current and voltage signals which have an impact on the diagnosis of the fault. Thus, this study discusses the features of input current and capacitor voltage under input voltage fluctuation and harmonic pollution, which are shown in Figure 5. About 7% harmonic was injected to input voltage at 0.3176 s, consequently, the THD of the input current increased from 4% to 8% but the impact on the capacitor voltage was limited. Still, from this figure, the input voltage fluctuated about 10% higher at 0.7273 s. The input current decreased a little and the capacitor voltage jittered rapidly at the same time. Different from the failure conditions, these varieties recovered in a short time. The features are significantly different from those failures discussed in the previous paragraphs.

Figure 5. Input current and capacitor voltage waveforms on input voltage fluctuation and harmonic injection.

#### 2.4. Load Side Interferences7

During the operation of the converters, the power on the load side was not always constant. The load sudden changed sometimes and the reference dc voltage also changed when transmitting different powers on the three-phase imbalance condition. This will lead to failure of fault diagnosis. In this study, output power variations due to reference voltage changed and load sudden change were also involved.

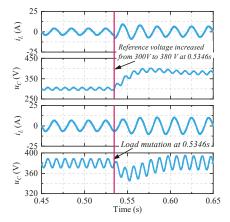

As shown in Figure 6, the reference output voltage increased from 300~V to 380~V at 0.5346~s, then the magnitude of the input current and capacitor voltage rose rapidly and became stable in two

ac cycles. The output power saw a 60% growth from 400 W to 640 W. Still, in this figure, the load became heavier abruptly at the same time, which resulted in output power rising up to 1000 W with a 56% increment. The input current increased smoothly and rapidly, meanwhile the capacitor voltage decreased a little but restored fast with a higher ripple.

**Figure 6.** Input current and capacitor voltage during the time of load sudden change and reference voltage change.

In summary, an OCF will result in input current falling to about zero and increasing ripple of the capacitor voltage. The intensity of current oscillation depended on the values of L and C. The features of input or load side interferences were essentially similar, and did not affect the sinusoidal characteristic of the input current and capacitor voltage signals. It has to be noticed that in these analyses, when switch S1 failed in a negative ac cycle, the converter maintained regular operation until a positive ac cycle, and vice versa for switch S2. The duration of this condition lasted up to a half ac cycle, which is related to the time of failures.

#### 3. Fault Diagnosis Technique

Fault diagnosis is the basis of fault tolerant control and consisted of fault detection and fault location [27]. It is important to detect and locate a malfunction switch rapidly, taking into account the fault features. In addition, the performance within fault tolerant behavior, such as redundancy control, is not only affected by fault diagnosing time directly, but also fault diagnosing accuracy including misdiagnosis and missed diagnosis [28]. Therefore, the fault diagnosis algorithm needs to be simple and effective.

#### 3.1. Fault Features Extraction

As aforementioned, the sinusoidal characteristic of input current is damaged when an OCF occurs, but is reserved under other interferences. Therefore, it is feasible to select the input current as the characteristic signal of fault diagnosis. Generally, it is straightforward to utilize frequency domain characteristics as fault features [29]. However, most of the frequency domain methods require Fast Fourier Transform (FFT), which costs large amounts of computation. In order to improve the diagnostic efficiency and reduce the computational cost, this study used a direct time domain analysis method. Considering a three-phase converter, an  $abc - \alpha\beta$  transformation, named Concordia transformation,

is applied to analyze conveniently in a two-phase stationary coordinate system. This transformation can be expressed as

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} = \begin{bmatrix} \sqrt{\frac{2}{3}} & -\frac{1}{\sqrt{6}} & -\frac{1}{\sqrt{6}} \\ 0 & \frac{1}{\sqrt{2}} & -\frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} i_{A} \\ i_{B} \\ i_{C} \end{bmatrix}$$

(4)

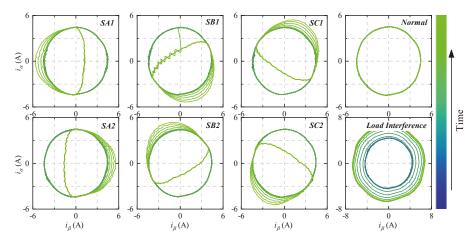

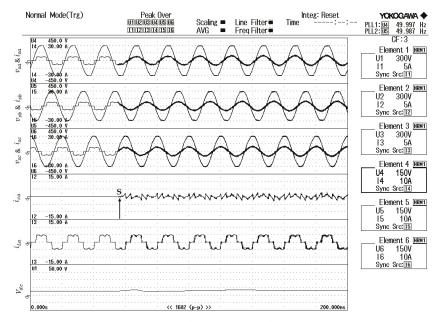

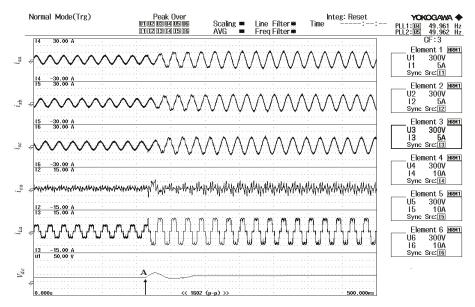

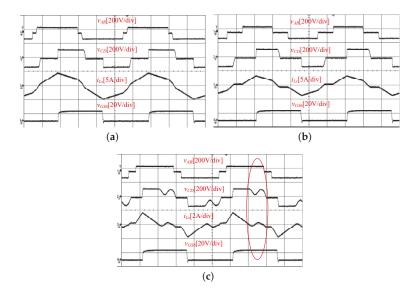

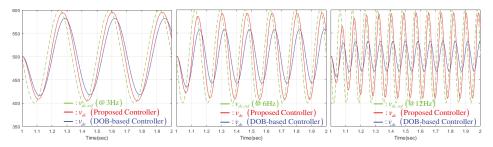

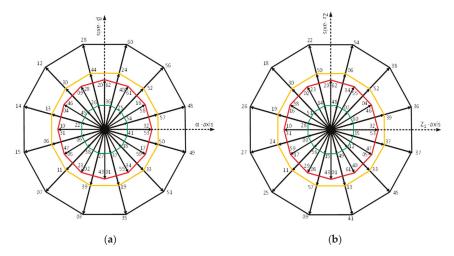

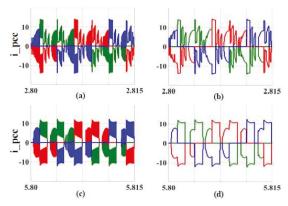

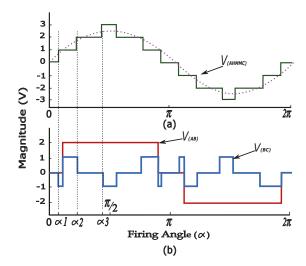

Transformed input current signals are shown in Figure 7, which took  $i_{\alpha}$  as the abscissa and  $i_{\beta}$  as the ordinate. The gradient of color represented the increase of time; therefore, the characteristics of  $i_{\alpha}$  and  $i_{\beta}$  before and after failure were revealed in these figures. Single switch failures of each switch were shown in Figure 7, as well as normal and load side interference conditions. Input side interference was similar with the load side.

Figure 7. Input current features in a two-phase coordinate system under eight conditions.

#### 3.2. Fault Detection and Location Method

According to the features shown in the above figure,  $i_{\alpha}$  and  $i_{\beta}$  constitute a circular trajectory under normal and interference conditions. However, an OCF will change the trajectory and different fault location will result in different trajectories. In other words, vectors from (0,0) to  $(i_{\alpha},i_{\beta})$  contain distinguished features of OCFs. Define R as the length of this vector, an interval increment-based fault detection method was proposed and can be expressed as

$$S = \int_{t-t_s}^{t} |R_0 - R(t)| dt$$

if  $S - S_{th} > res$ , then an OCF occurred (5)

where *S* is the accumulative bias of *R*,  $S_{th}$  is a reference value for detecting an OCF, *res* is the threshold of residual for decision, and  $t_s$  is the length of the interval.  $R_0 = \frac{1}{T} \int_{t-2T}^{t-T} R(t) dt$  is the reference of *R* which lags one ac cycle to increase the sensitivity, and *T* is the power frequency cycle.

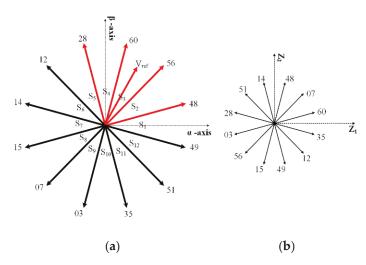

Review the angle between this vector and the positive direction of the abscissa axis. It can be found that the abnormal R occurred at a specific angular interval corresponding to different fault locations. The central values of these intervals, defined as  $\theta_{th}$ , are ideally taken as  $\left(0,\pi,\frac{2\pi}{3},\frac{5\pi}{3},\frac{4\pi}{3},\frac{\pi}{3}\right)$  corresponding to SA1, SA2, SB1, SB2, SC1, SC2 OCFs one by one. Then, a fault location method after fault detection was proposed based on this vector. It selected the minus central value between the angle when a fault was detected and  $\theta_{th}$  as the location judgment, which can be expressed as

$$\min_{i} |\theta_{th}(i) - \theta_{d}| \quad \theta \in [0, 2\pi]$$

(6)

where  $i = 1, 2, \dots, 6$ , which represents SA1, SA2, SB1, SB2, SC1, and SC2 respectively.  $\theta_d$  is the angle when an OCF was detected.

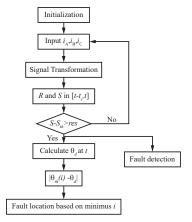

The flow chart including fault detection and fault location algorithm are shown in Figure 8.

Figure 8. Fault detection and location algorithm flow chart based on current residual.

#### 4. Fault Tolerance Method

An OCF will not cause the converter to shutdown immediately, but it slowly degrades the performance and reliability. Actually, a converter is desired to have the capability to operate in a quasi-normal condition in the post-failure period. Therefore, a fault tolerance method includes two aspects: fault tolerant topology with an extra two switches and a corresponding fault tolerant control method were proposed.

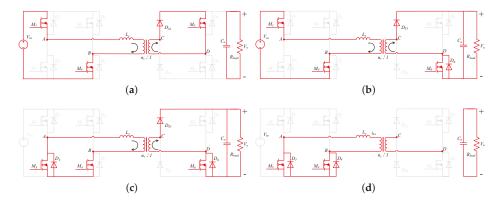

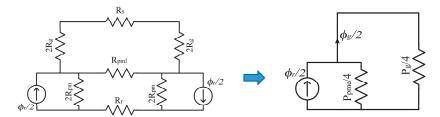

Also in the case of a single phase, the converter consists of two fast recovery diodes and two power switches with body diodes [25]. A current loop is broken due to an open circuit fault. Therefore, in order to obtain fault tolerant capability, additional devices must be added to restore the original current loop in the fault state. A fault tolerant topology with an additional two power switch which connected in parallel across the two fast recovery diodes is shown in Figure 9a. As aforementioned, more than two-thirds of ac-dc rectifiers in motor drives of industry only require a single direction for energy transmission. Therefore, considering the efficiency, loss, and control algorithms, this topology still operates as a bridgeless converter in the normal state, although it is similar to the H-bridge structure. The fault tolerant control diagram with drive signal distribution is shown in Figure 9b.

Figure 9. Fault tolerant control topology and control method. (a) Proposed fault tolerant topology with two additional switches; (b) block diagram of the fault tolerant control method with signal distribution.

The control method diagram includes two control loops: an inner current loop and an outer voltage loop. The role of the inner loop is to realize a unity power factor, and the role of the outer loop

is to provide a controllable output DC voltage. The voltage controller  $G_{vc}$  and current controller  $G_{cc}$  are obtained as

$$G_{vc} = \frac{K_{Pv}s + K_{Iv}}{s}$$

$$G_{cc} = \frac{K_{Pi}s + K_{Ii}}{s}$$

(7)

The output of the double PI loop was compared with the carrier. Hence, in turn, the PWM signal was generated for signal distribution. At the same time, constant zero which means low level driving signal, was also generated.

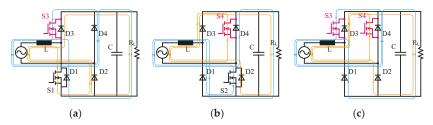

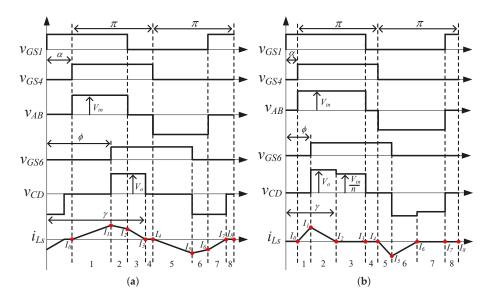

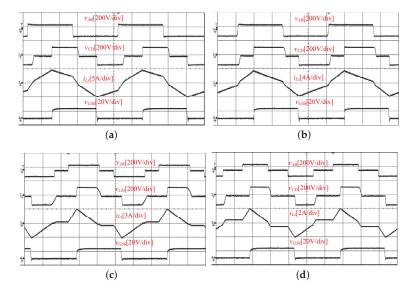

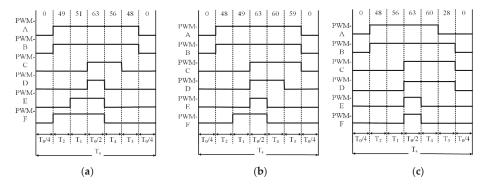

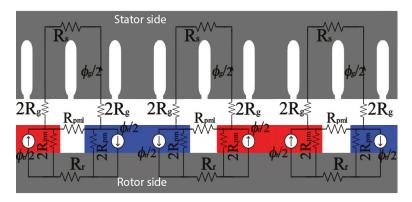

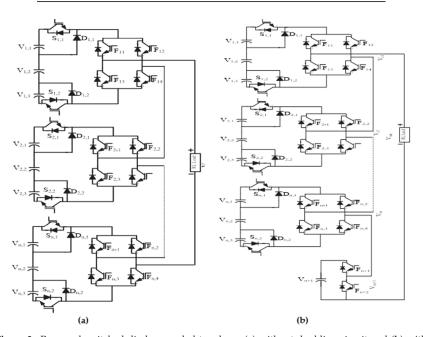

The converter achieved fault tolerance through dynamic structure reconfiguration [30,31]. According to the location of the faulty device, there are three substructure types after an OCF. Each of them has a corresponding drive signal distribution rule to maintain the normal operation of the converter. The circuit reconfigurations are shown in Figure 10.

**Figure 10.** Circuit type reconfigurations. (a) Totem pole bridgeless; (b) Symmetry totem pole bridgeless; (c) Symmetry boost bridgeless.

In normal operation, both S3 and S4 are driven off by the low level, and S1 and S2 are driven by the PWM signal p in a synchronous drive mode. When it is detected that an open circuit fault occurs in S2, S3 will be driven by -p which means S1 and S3 are driven by complementary signals. At this point, the circuit topology is converted into a totem pole bridgeless structure, as shown in Figure 10a. When an open circuit fault occurs in S1, the drive signal of S4 will also be replaced by -p, and S2 and S4 will continue to operate in a complementary signal drive mode. At this point, the circuit topology is converted to a symmetry totem pole bridgeless structure, as shown in Figure 10b. If an open circuit fault occurs in both S1 and S2, the circuit will be converted into a symmetry boost bridgeless structure consisting of S3 and S4, which will be driven by p synchronously. This situation is shown in Figure 10c. The current path for the different topologies is also shown in Figure 10, with orange representing the path for the positive ac cycle and blue for the negative. The drive signal distribution table corresponding to each fault state is shown in Table 1.

**Table 1.** Drive signal distribution of different fault switch.

| Faulty Switch - | Drive Signal |    |    |    |  |  |

|-----------------|--------------|----|----|----|--|--|

| raulty Switch - | S1           | S2 | S3 | S4 |  |  |

| None            | р            | р  | 0  | 0  |  |  |

| S1              | /            | p  | 0  | -p |  |  |

| S2              | p            | /  | -p | Ó  |  |  |

| S1&S2           | /            | /  | p  | р  |  |  |

<sup>&</sup>quot;0" respects low level, "p" respects the PWM signal, "/" respects an OCF.

#### 5. Simulation and Experiment Results

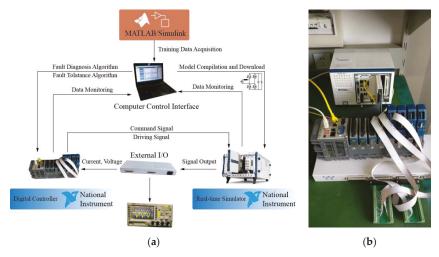

It is essential to demonstrate the proposed fault diagnosis and tolerant control method function as expected in a real converter. However, failures of a real device will lead to uncontrollable consequences such as burning or explosion. Therefore, hardware in loop (HIL) simulation technology is suitable for device failure experiments. In this study, simulation and experiment-based MATLAB/Simulink

and NI platform were realized, as can be seen in Figure 11a; and the details concerning the equipment used in this setup are shown in Figure 11b.

Figure 11. Diagram of simulation and experiment setup.

The simulation model of the three-phase bridgeless converter was built in MATLAB/Simulink and used to verify the proposed fault diagnosis and tolerant control method. Then HIL simulation based on NI-PXI platform was employed to emulate physical experiment, which is widely recognized and adopted in the field of power electronic device failure researches [32]. The power system model was set up as shown in Figure 1, and the parameters are presented in Table 2. The simulation and experiment results are revealed in two aspects: fault diagnosis results and fault tolerant control results. It is noticed that there was no real fault and all the OCFs were emulated by focusing the low level drive signal of specific switches.

| Tab | le 2. | Specif | fication | of | Simu | lation | and | Experin | nent. |

|-----|-------|--------|----------|----|------|--------|-----|---------|-------|

|-----|-------|--------|----------|----|------|--------|-----|---------|-------|

| Parameter            | Value       |  |  |

|----------------------|-------------|--|--|

| Input ac voltage     | 220 V 50 Hz |  |  |

| Reference dc voltage | 380 V       |  |  |

| Boost inductor       | 5 mH        |  |  |

| dc capacitor         | 330 μF      |  |  |

| Normal power         | 2000 W      |  |  |

| Switching frequency  | 10 kHz      |  |  |

| Sampling frequency   | 10 kHz      |  |  |

| $K_{Pv}, K_{Iv}$     | 0.021, 0.55 |  |  |

| $K_{Pi}, K_{Ii}$     | 10.1, 200   |  |  |

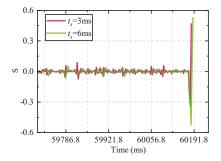

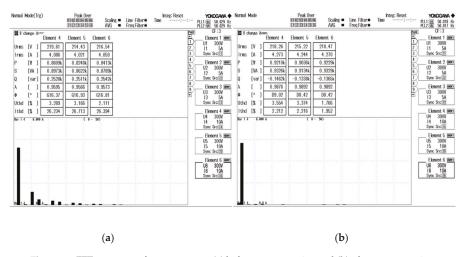

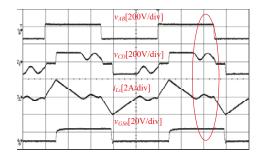

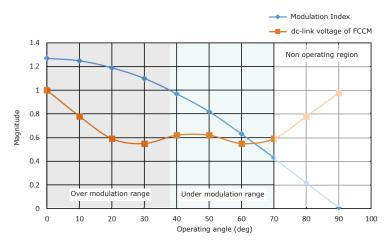

For the diagnostic algorithm proposed in this paper, the selection of  $t_s$  has a direct impact on diagnostic resolution and diagnostic performance. Figure 12 shows the value of S when  $t_s$  is equal to 3 ms and 6 ms, plotted in red and green, respectively. Obviously, the diagnostic frequency (or resolution) of the proposed online real-time fault diagnosis is positively correlated with  $t_s$ . In the normal state, the value of S was about zero. When a fault occurred, S began to fluctuate greatly. The amplitude was also positively correlated with  $t_s$ . That is to say, a larger  $t_s$  meaning larger diagnostic interval or lower diagnostic frequency can make it easier to identify a fault trigger, reduce misdiagnosis or missed diagnosis.

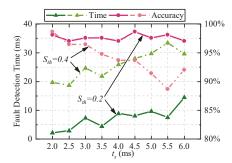

**Figure 12.** Plot of S with two different  $t_S$  until fault detection.

In order to make the method proposed in this study applicable with different system parameters, both  $i_{\alpha}$  and  $i_{\beta}$  were normalized in the actual process. Furthermore, Figure 13 shows the results of 200 samples with different  $t_s$  from 2 to 6 ms, where the average detection time is connected in green and the average accuracy rates in red. In this figure, the influence of different  $S_{th}$  are also shown, in which the solid line represents  $S_{th}=0.2$  and the dashed dotted line represents  $S_{th}=0.4$ . When  $S_{th}=0.2$ , as can be seen, the fault detection time increased as  $t_s$  grew because it slowed down the diagnostic frequency, and the accuracy rates were maintained at around 98%. When  $S_{th}=0.4$ , the detection time generally increased by about 20 ms, but there was greater decline in accuracy rates with  $t_s$  growing. The reason is that longer integration time makes the value of S closer to zero, and the larger threshold is gradually more unsuitable, resulting in a drop in the accuracy rate.

**Figure 13.** Detection time and accuracy with two  $S_{th}$ .

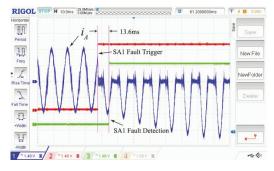

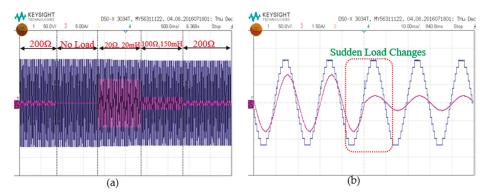

After selecting the appropriate parameters, the current signal  $i_A$  and corresponding trigger signals collected by the oscilloscope were as shown in Figure 14.

Figure 14. Input current and SA1 fault trigger and detection signals of phase A.

After a fault was detected, the fault location algorithm needed to be employed to locate the fault. Since the detected time  $t_d$  was not the actual time  $t_f$  at which a failure occurred. The  $\theta_d$  calculated using  $i_\alpha(t_d)$  and  $i_\beta(t_d)$  was disorderly, and therefore, it was impossible to locate the failure in practice. In this study, this problem was solved by sacrificing a certain fault tolerant time that the value of  $\theta_d$  was taking as the time minimizing R within a power cycle after  $t_d$ . It can be expressed as

$$\theta_d = \theta(t_{\min})$$

$$t_{\min} = \min_t R(t), t \in [t_d, t_d + T]$$

(8)

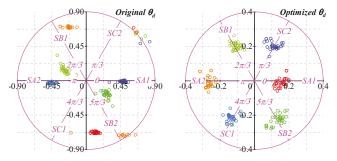

Figure 15 shows the scatter plots of  $i_{\alpha}(t_d)$  and  $i_{\beta}(t_d)$  for each of the 30 samples. The pink auxiliary line identifies the angles corresponding to each fault under ideal conditions. The data points generated by original  $\theta_d$  were scattered and could not be used for fault location. The optimized data points were concentrated in the vicinity of the ideal values which could be used for accurate fault location.

**Figure 15.** Fault location data distribution with original and optimized  $\theta_d$ .

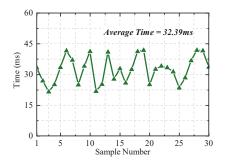

Under the condition of  $t_s = 5$  ms,  $S_{th} = 0.5$ , 30 fault tolerance experiments were implemented where the faulty switch was randomly selected. The times from fault occurrence to fault tolerant control execution are shown in Figure 16. It can be found that the fault tolerance time increased by 20 ms relative to the detection time from Figure 13, where the delay of one ac cycle is caused by Equation (8).

Figure 16. Fault tolerance times of thirty samples.

An example of fault diagnosis and tolerant control is shown in Figure 17. The signals were monitored by the host computer of the system built in this study.

Figure 17. Signals collected by the host computer.

In summary, the proposed fault diagnosis and fault tolerant control method were verified in simulation and experimentation. An OCF will be detected within at least 20 ms in general conditions, and tolerated with a 20 ms delay. Various interferences have limited impact on this algorithm. The accuracy of fault diagnosis was over 98%, and the error rate of the fault location and fault tolerance was zero.

#### 6. Conclusions

Reliability is one of the primary concerns for the three-phase bridgeless converter. This paper presented an open circuit fault diagnosis and tolerant control method to maintain the converter running. As the basis for fault tolerance, the open circuit fault is detected and located accurately within a few milliseconds, thus, the abnormal operation time is reduced. Only two additional switches are needed to maintain the normal operation by structure reconfiguration. A lookup table is built for switch drive signals reconfiguration. Finally, the feasibility and effect of the proposed method on reliability promotion was verified by simulations and experiments. Furthermore, the interference analysis in this paper is still insufficient that the proposed method is not robust enough in practice. This requires further work.

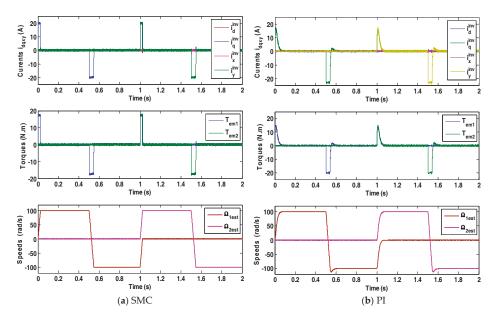

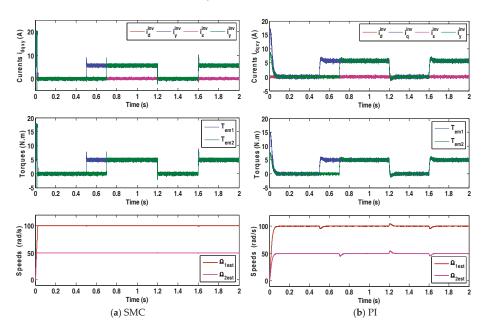

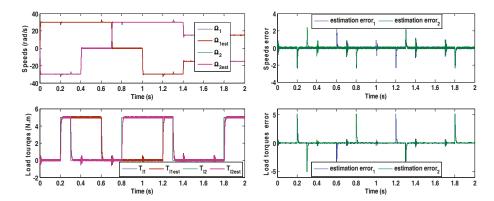

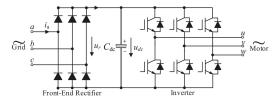

**Author Contributions:** W.C., H.C. and C.W. conceptualized the main idea of this project; W.C. proposed the methods and designed the work; W.C. conducted the experiments and analyzed the data; J.D. checked the results; W.C. wrote the whole paper; and H.C., C.W., and J.D. reviewed and edited the paper.