# Radiation Tolerant Electronics

Edited by Paul Leroux Printed Edition of the Special Issue Published in *Electronics*

www.mdpi.com/journal/electronics

# **Radiation Tolerant Electronics**

# **Radiation Tolerant Electronics**

Special Issue Editor

Paul Leroux

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade

Special Issue Editor Paul Leroux KU Leuven ESAT-ADVISE Belgium

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Electronics* (ISSN 2079-9292) from 2018 to 2019 (available at: https://www.mdpi.com/journal/electronics/ special\_issues/Radiation\_Tolerant\_Electronics)

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, Article Number, Page Range.

ISBN 978-3-03921-279-8 (Pbk) ISBN 978-3-03921-280-4 (PDF)

© 2019 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## Contents

| About the Special Issue Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Paul Leroux         Radiation Tolerant Electronics         Reprinted from: Electronics 2019, 8, 730, doi:10.3390/electronics8070730         1                                                                                                                                                                                                                                                                                                                                                                   |

| Teng Wang, Xin Wan, Hu Jin, Hao Li, Yabin Sun, Renrong Liang, Jun Xu and Lirong Zheng         Optimization of the Cell Structure for Radiation-Hardened Power MOSFETs         Reprinted from: <i>Electronics</i> 2019, 8, 598, doi:10.3390/electronics8060598                                                                                                                                                                                                                                                   |

| <b>Mohan Liu, Wu Lu, Xin Yu, Xin Wang, Xiaolong Li, Shuai Yao and Qi Guo</b><br>Mechanism of Degradation Rate on the Irradiated Double-Polysilicon Self-Aligned<br>Bipolar Transistor                                                                                                                                                                                                                                                                                                                           |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 657, doi:10.3390/electronics8060657                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Kyungsoo Jeong, Duckhoon Ro, Gwanho Lee, Myounggon Kang and Hyung-Min Lee</b><br>A Radiation-Hardened Instrumentation Amplifier for Sensor Readout Integrated Circuits in<br>Nuclear Fusion Applications                                                                                                                                                                                                                                                                                                     |

| Reprinted from: <i>Electronics</i> <b>2018</b> , <i>7</i> , 429, doi:10.3390/electronics7120429                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Jan Budroweit, Mattis Paul Jaksch Maciej Sznajder         Proton Induced Single Event Effect Characterization on a Highly Integrated RF-Transceiver         Reprinted from: Electronics 2019, 8, 519, doi:10.3390/electronics8050519                                                                                                                                                                                                                                                                            |

| Bjorn Van Bockel, Jeffrey Prinzie and Paul Leroux         Radiation Assessment of a 15.6 ps Single-Shot Time-to-Digital Converter in Terms of TID         Reprinted from: Electronics 2019, 8, 558, doi:10.3390/electronics8050558                                                                                                                                                                                                                                                                              |

| Charalambos M. Andreou, Diego M. González-Castaño, Simone Gerardin, Marta Bagatin,<br>Faustino Gómez, Alessandro Paccagnella, Alexander V. Prokofiev, Arto Javanainen,<br>Ari Virtanen, Valentino Liberali, Cristiano Calligaro, Daniel Nahmad and Julius Georgiou<br>Low-Power, Subthreshold Reference Circuits for the Space Environment: Evaluated with<br>$\gamma$ -rays, X-rays, Protons and Heavy Ions<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 562, doi:10.3390/electronics8050562 |

| Jeffrey Prinzie and Valentijn De Smedt         Single Event Transients in CMOS Ring Oscillators         Reprinted from: Electronics 2019, 8, 618, doi:10.3390/electronics8060618         88                                                                                                                                                                                                                                                                                                                     |

| V. Díez-Acereda, Sunil L. Khemchandani, J. del Pino and S. Mateos-Angulo<br>RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 690, doi:10.3390/electronics8060690                                                                                                                                                                                                                                                           |

| Maria Munoz-Quijada, Samuel Sanchez-Barea, Daniel Vela-Calderon,Hipolito Guzman-Miranda<br>Fine-Grain Circuit Hardening Through VHDL Datatype Substitution<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 24, doi:10.3390/electronics8010024                                                                                                                                                                                                                                                    |

| <b>Jeffrey Prinzie , Karel Appels, Szymon Kulis</b><br>Optimal Physical Implementation of Radiation Tolerant High-Speed Digital Integrated Circuits<br>in Deep-Submicron Technologies<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 432, doi:10.3390/electronics8040432                                                                                                                                                                                                                        |

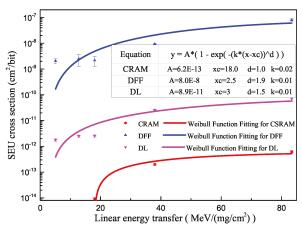

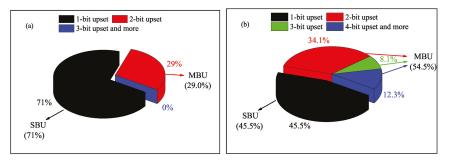

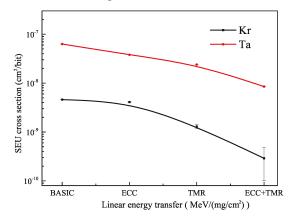

| Chang Cai, Xue Fan, Jie Liu, Dongqing Li, Tianqi Liu, Lingyun Ke, Peixiong Zhao and Ze He<br>Heavy-Ion Induced Single Event Upsets in Advanced 65 nm Radiation Hardened FPGAs<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 323, doi:10.3390/electronics8030323 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Solomon Banteywalu, Baseem Khan, Valentijn De Smedt and Paul Leroux</b><br>A Novel Modular Radiation Hardening Approach Applied to a Synchronous Buck Converter                                                                                                               |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 513, doi:10.3390/electronics8050513                                                                                                                                                                                  |

| Leonardo Maria Reyneri, Alejandro Serrano-Cases, Yolanda Morilla, Sergio Cuenca-Asensi,<br>Antonio Martínez-Álvarez<br>A Compact Model to Evaluate the Effects of High Level C++ Code Hardening in                                                                               |

| Radiation Environments<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 653, doi:10.3390/electronics8060653                                                                                                                                                        |

| Reprinted nom. <i>Littlonics</i> 2019, <i>0</i> , 053, doi:10.3390/ Electronics0000035 100                                                                                                                                                                                       |

| Honorio Martin, Pedro Martin-Holgado, Yolanda Morilla, Luis Entrena and                                                                                                                                                                                                          |

| Enrique San Millan<br>Total Ionizing Dose Effects on a Delay-Based Physical Unclonable Function Implemented<br>in FPGAs                                                                                                                                                          |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 163, doi:10.3390/electronics7090163                                                                                                                                                                                          |

| Luis Alberto Aranda, Pedro Reviriego and Juan Antonio Maestro                                                                                                                                                                                                                    |

| Protecting Image Processing Pipelines against Configuration Memory Errors in SRAM-Based FPGAs                                                                                                                                                                                    |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 322, doi:10.3390/electronics7110322                                                                                                                                                                                          |

### About the Special Issue Editor

**Paul Leroux** is Professor in the Department of Electrical Engineering (ESAT) of KU Leuven (University of Leuven), Belgium. He received M.Sc. and Ph.D. degrees in electronic engineering from KU Leuven in 1999 and 2004, respectively. From November 2011 to July 2016, he headed the Electrical Engineering Technology Cluster. Since August 2016 he had been the Campus Chair of KU Leuven, Geel Campus. His current research activities within the ESAT-ADVISE research group focus on radiation-hardened analog, mixed-signal, and RF IC design for communication and instrumentation in space, high-energy physics, and nuclear energy applications. His group is part of the CERN CMS collaboration, where Prof. Leroux is the KU Leuven team leader. Prof. Leroux has (co-)authored over 200 papers in international journals and conference proceedings. In 2010, he received the SCK-CEN Prof. Roger Van Geen Award from the FWO/FNRS for his highly innovative work on IC design for harsh radiation environments.

# **Radiation Tolerant Electronics**

#### Paul Leroux

KU Leuven, Dept. Electrical Engineering (ESAT) - ADVISE, 2440 Geel, Belgium; paul.leroux@kuleuven.be Received: 20 June 2019; Accepted: 25 June 2019; Published: 27 June 2019

#### 1. Introduction

Research on radiation tolerant electronics has increased rapidly over the last few years, resulting in many interesting approaches to model radiation effects and design radiation hardened integrated circuits and embedded systems. This research is strongly driven by the growing need for radiation hardened electronics for space applications, high-energy physics experiments such as those on the large hadron collider at CERN, and many terrestrial nuclear applications including nuclear energy and safety management. With the progressive scaling of integrated circuit technologies and the growing complexity of electronic systems, their ionizing radiation susceptibility has raised many exciting challenges, which are expected to drive research in the coming decade. Even though total ionizing dose effects in bulk CMOS are well known, little is still known on the radiation performance of advanced (FD-)SOI and FinFET technologies. Regarding single-event effects, the continued scaling has drastically increased the number of multiple-transistor or multiple-cell upsets, which requires not only new solutions to reduce the error rate in digital and mixed-signal ASICs, but also for FPGAs. The radiation hardness assurance of complex systems with multiple components in mixed technologies also necessitates new testing paradigms and verification methodologies to limit the time and cost for evaluation.

#### 2. The Present Issue

This Special Issue features fifteen articles highlighting recent breakthroughs in modeling radiation effects for the design of radiation hardened integrated circuits, radiation hardening in embedded systems, and radiation hardening assurance. The contents of these papers are introduced here.

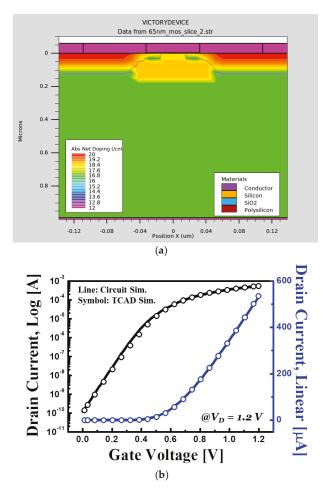

Two papers discuss the effect of radiation on advanced semiconductor devices such as dedicated power MOSFETs and double-polysilicon self-aligned bipolar transistors. In [1], the effects of cell structure adjustment on the performance of a power MOSFET were examined by first analyzing the design parameters. Next, a SEE- and TID-hardened power MOSFET was designed and fabricated. Results of the investigation confirmed the achievement of excellent radiation hardness and decent specific on-resistance for the device. Article [2] discussed the mechanism of degradation on the Irradiated Double-Polysilicon Self-Aligned Bipolar Transistor with a dose rate of 50 rad (Si)/s and 0.05 rad (Si)/s. The comparison of the high and low dose rate showed that the increase of the base current caused by low dose rate irradiation was larger than that caused by high dose rate irradiation, resulting in greater current gain degradation than that caused by the high dose rate, highlighting that the ELDRS effect may occur.

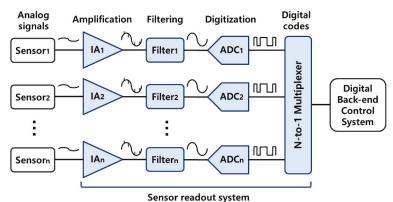

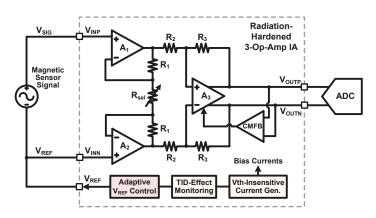

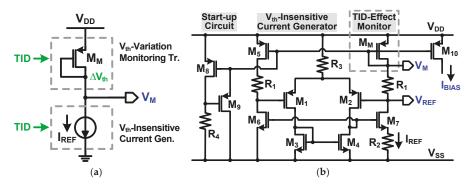

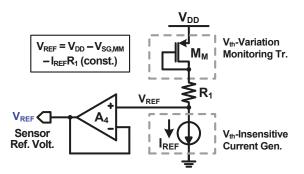

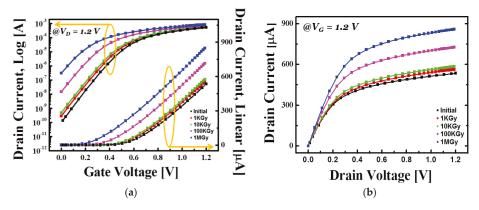

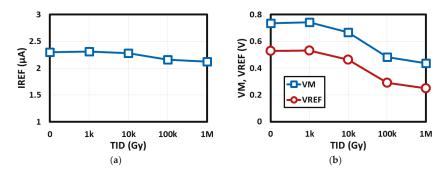

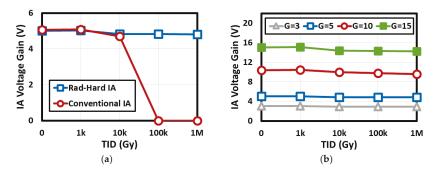

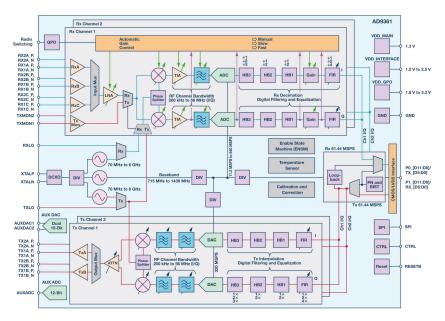

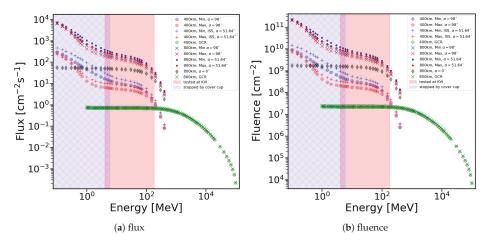

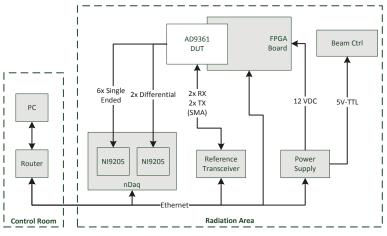

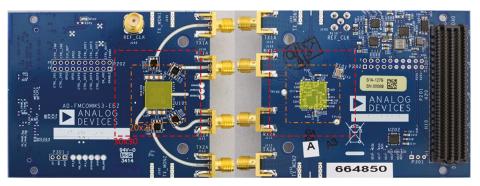

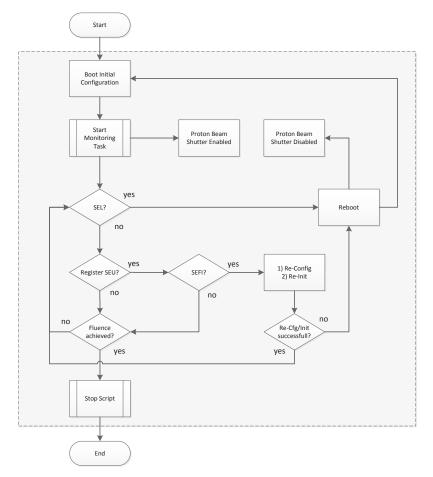

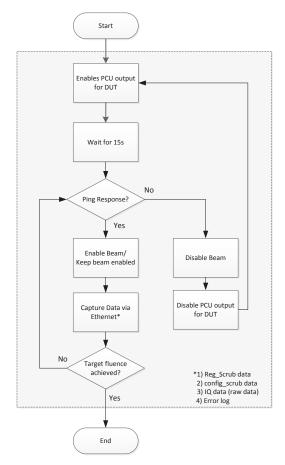

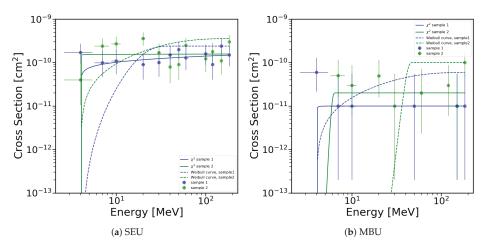

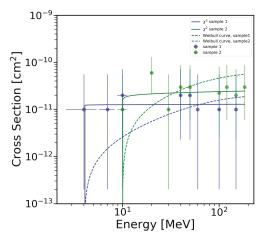

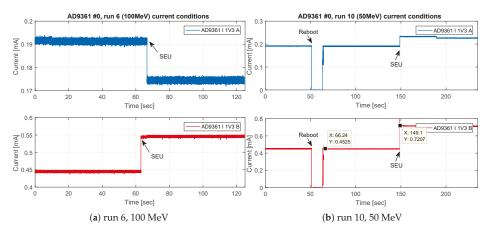

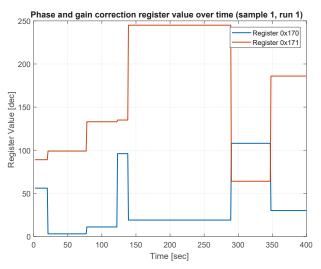

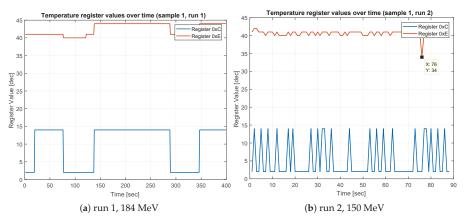

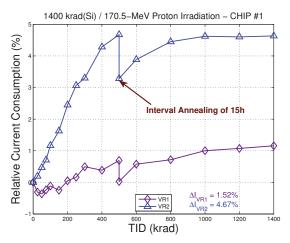

Several papers discuss the total-dose and/or single-event radiation effects on custom designed analog, mixed signal, and RF integrated circuits. A radiation-hardened instrumentation amplifier for sensor readout integrated circuits was presented in [3] to target nuclear fusion applications. The circuit boasts TID effect monitoring and adaptive reference control functions. The radiation tolerance was verified through SPICE simulations with radiation-aware transistor models. In [4], the authors presented the proton induced SEE characterization of a highly integrated RF transceiver in 65 nm CMOS. The exposed proton energies were split into two test campaigns to induce high energy protons

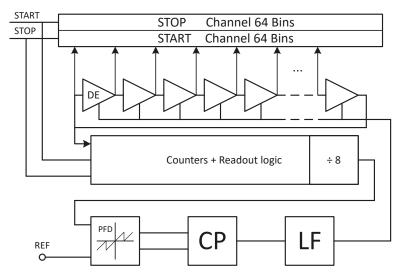

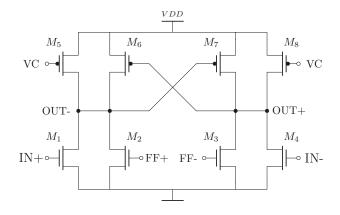

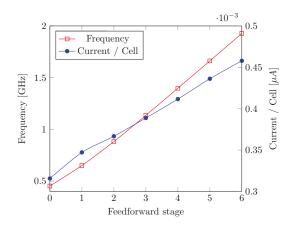

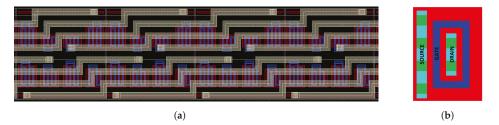

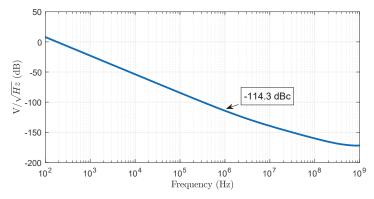

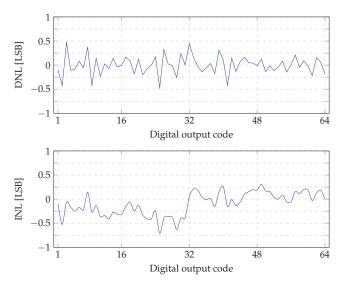

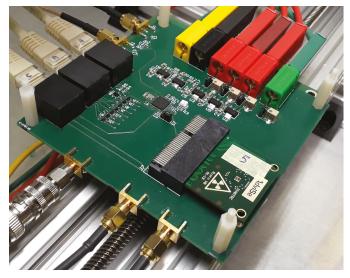

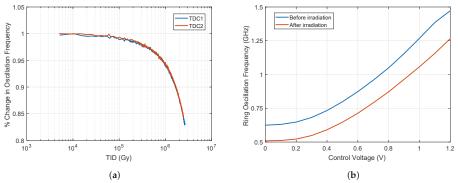

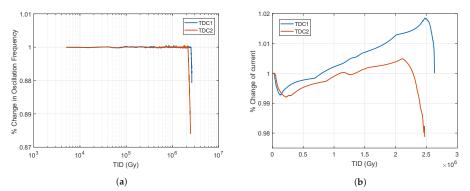

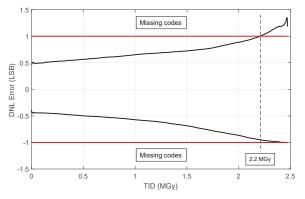

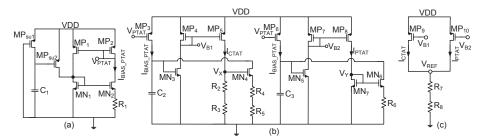

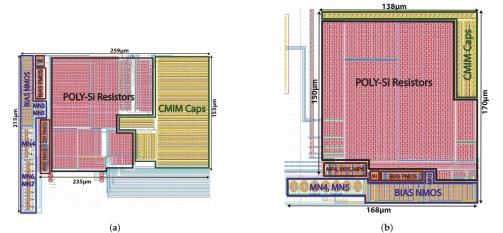

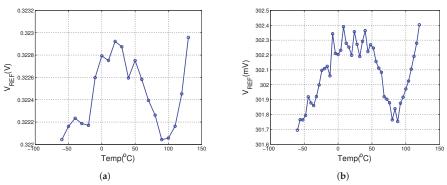

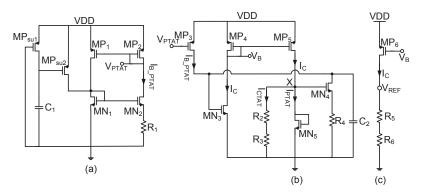

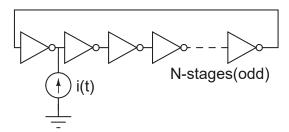

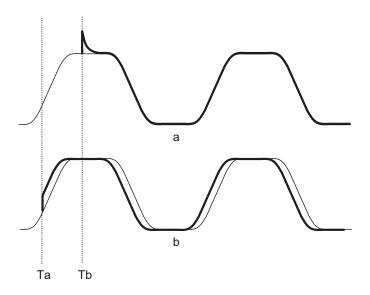

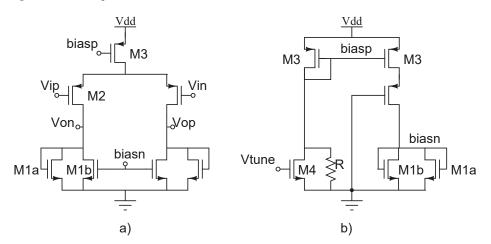

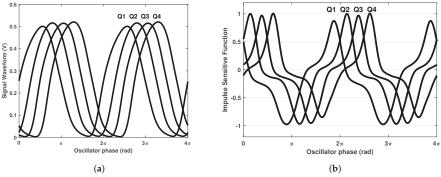

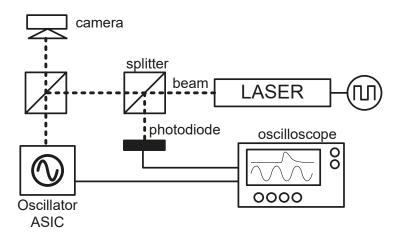

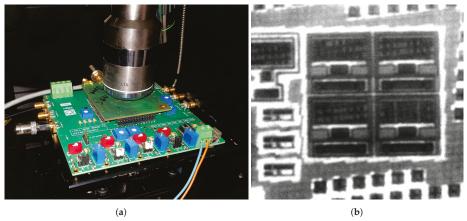

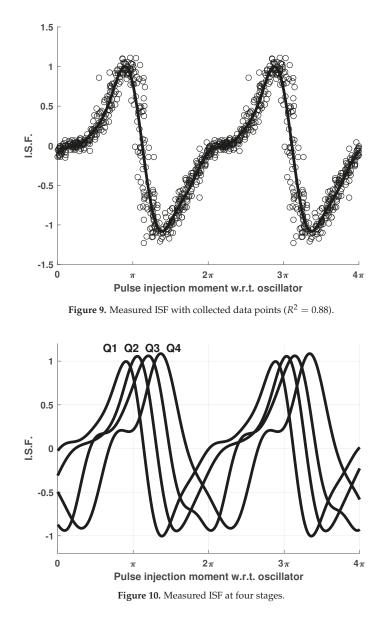

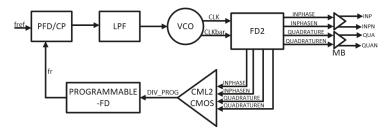

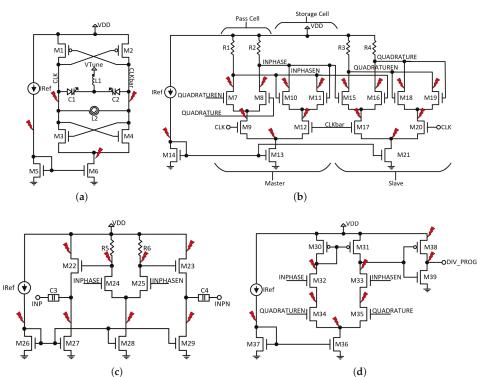

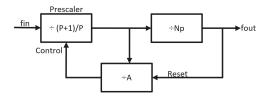

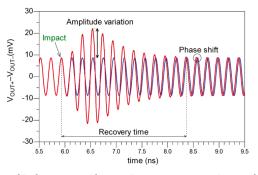

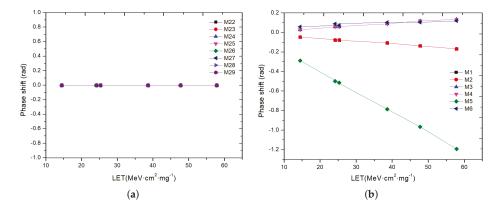

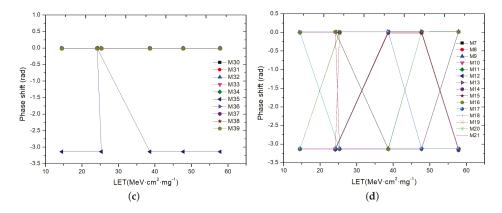

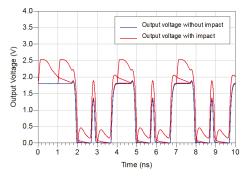

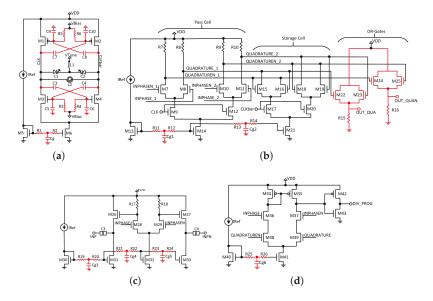

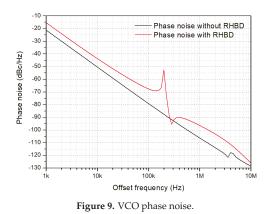

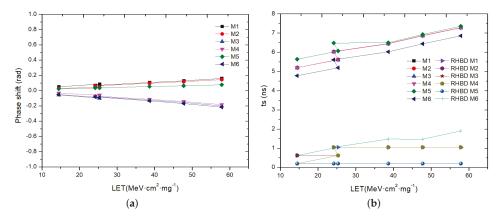

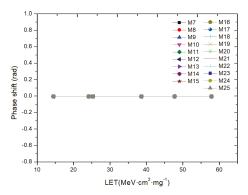

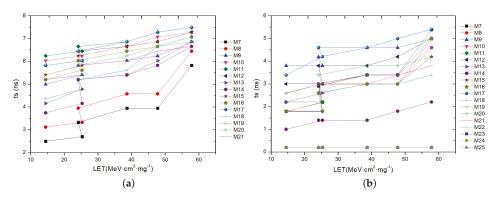

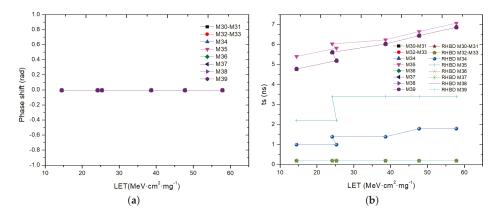

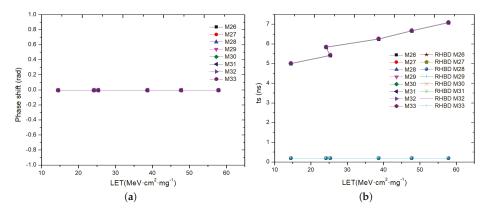

(up to 184 MeV) and low energy protons down to 4 MeV. The results showed a very low sensitivity to proton irradiation, independent of the proton energy. The total ionizing dose radiation assessment of a 15.6 ps single-shot Time-to-Digital Converter was presented in [5]. Two samples were irradiated and were able to reach a dose of 2.2 MGy before failing to meet specification due to an increased non-linearity error, originating from the increased mismatch in the charge-pump of the sampling circuit. A comprehensive evaluation of two subthreshold voltage reference circuits with respect to their resilience to SEE, TID, and TID/DD was performed in [6]. The evaluation was supported by measured results with  $\gamma$ -rays, x-rays, protons, and heavy ions. The high total doses applied in this range of experiments provide a complete evaluation of subthreshold circuits in the whole range of space applications, radiation physics instruments, and medical applications. The authors in [7] discussed a time-variant on Single-Event Transients (SETs) in integrated CMOS ring oscillators. The Impulse Sensitive Function (ISF) of the oscillator was used to analyze the impact of the relative moment when a particle hit the circuit. The analysis was based on simulations and verified experimentally with a Two-Photon Absorption (TPA) laser setup. Article [8] presented a comprehensive study of the effects of SETs and SEUs on a frequency synthesizer for the IEEE 802.15.4 standard. The blocks that work at low frequencies were not affected by ion impacts. However, high frequency circuits such as the VCO were more vulnerable. The VCO's radiation tolerance was improved by using RC-filtering and a capacitive divider was introduced to improve the degraded phase noise.

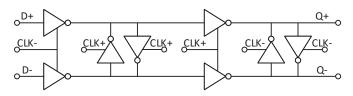

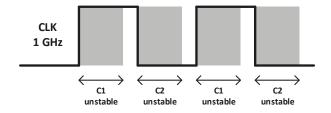

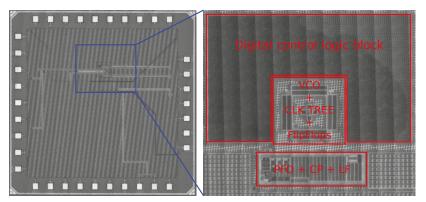

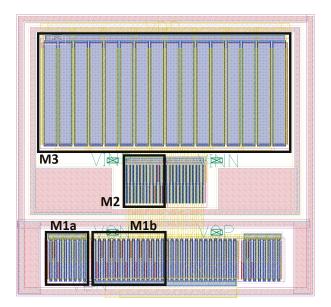

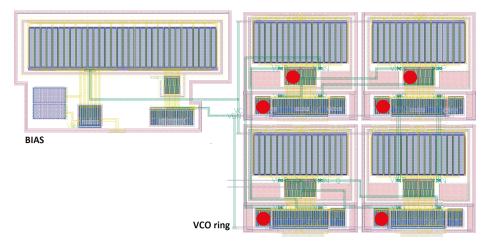

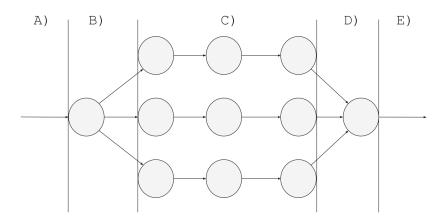

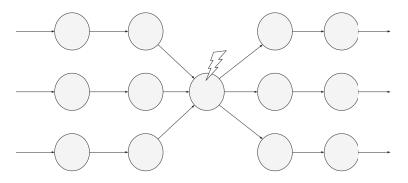

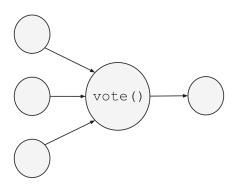

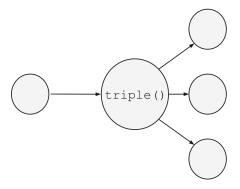

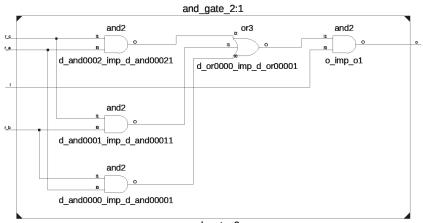

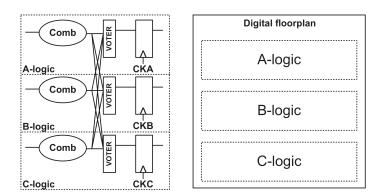

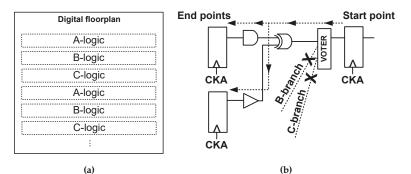

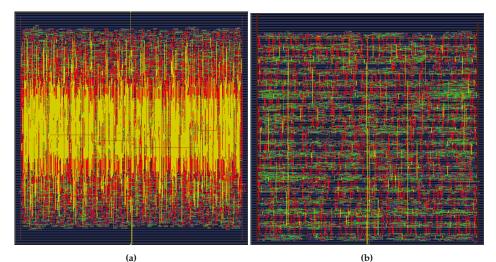

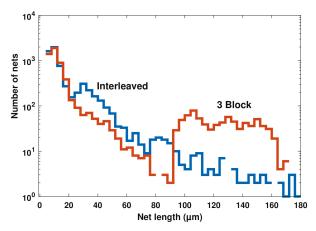

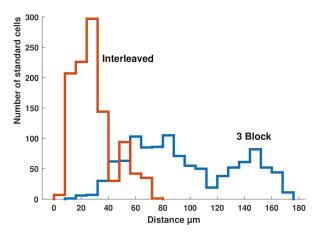

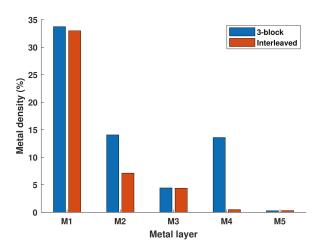

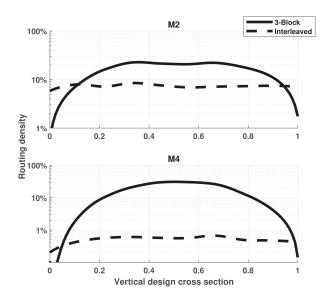

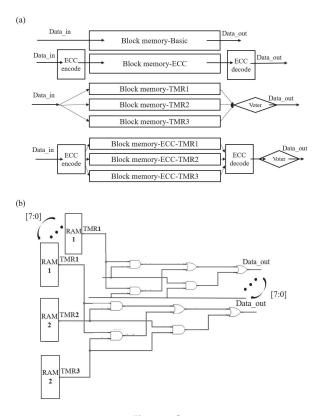

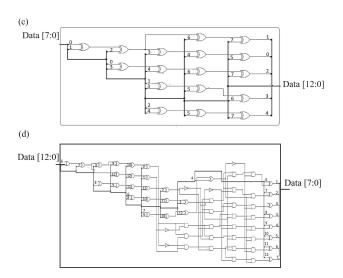

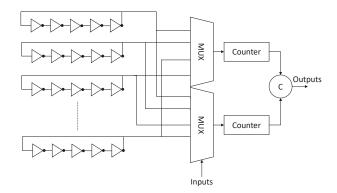

Two articles focus on the radiation hardening of digital circuits. A new approach to implement fine-grain circuit hardening was developed and validated in [9]. This offers a dedicated VHDL package as a new tool for mitigating soft errors on digital circuits, with minimal code modifications as the designer only has to select which signals or ports should be hardened and then change their datatype accordingly. Article [10] presented a novel method for the physical implementation of Triple Modular Redundant high-speed digital circuits. The method uses a distributed constraining approach for TMR branches to avoid long interconnects between voters. The method was tested with increasingly complex digital modules and showed results that improved as the design size increased.

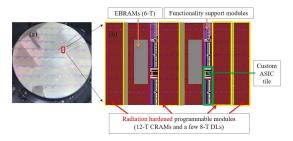

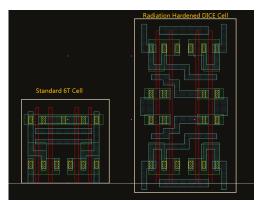

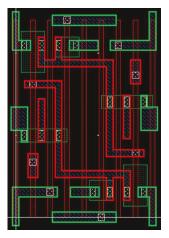

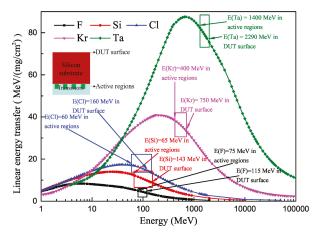

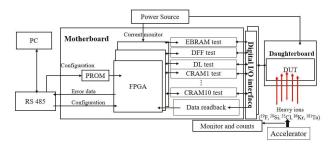

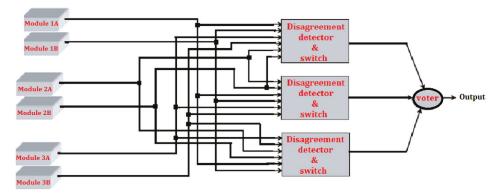

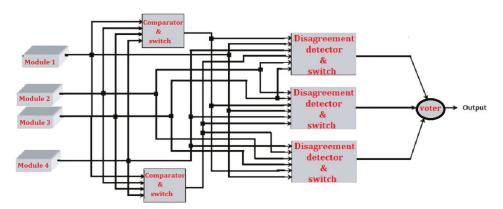

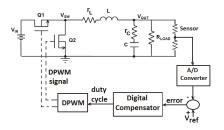

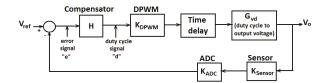

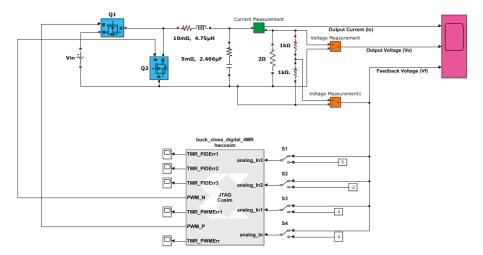

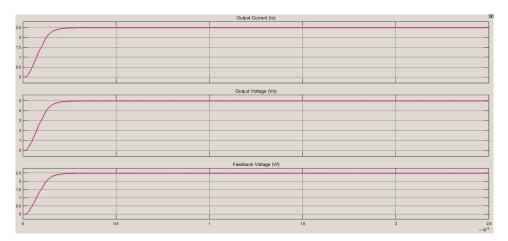

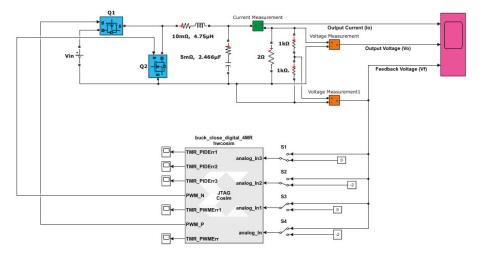

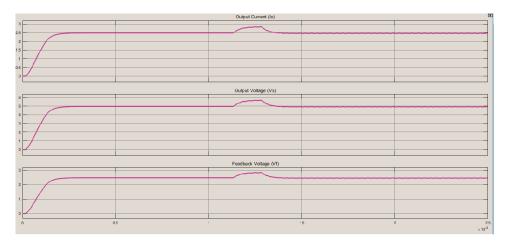

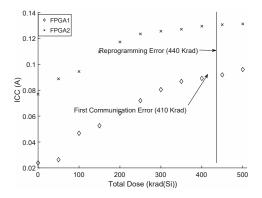

Three papers of this Special Issue target embedded radiation hardening in FPGA or microcontroller systems. In [11] single-event radiation hardening techniques for SRAM-based FPGAs in 65 nm CMOS technology were discussed. Both layout hardening techniques and configuration hardening techniques including ECC and TMR were employed for this FPGA. The heavy-ion results indicated a satisfactory radiation tolerance, especially for the DICE CRAMs. A novel four module radiation hardening approach for FPGA was presented in [12]. This was implemented on a zynq-7000 development board (Zybo) and it was shown that the proposed method could be used for a radiation tolerant synchronous buck converter design for applications requiring a relatively longer mission time, compared to the TMR and FMR techniques. In [13], a compact model was presented to evaluate the effects of high-level C++ code radiation hardening. The use of appropriate C++ classes facilitated the use of TMR. Additionally, the availability of an easy-to-use performance estimation model could be used for quick and effective radiation tolerance optimization of microcontroller systems.

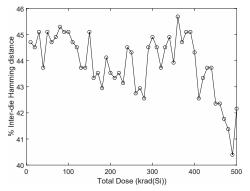

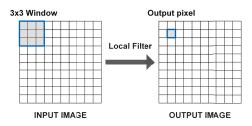

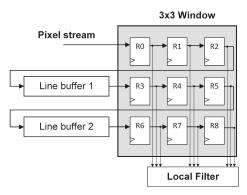

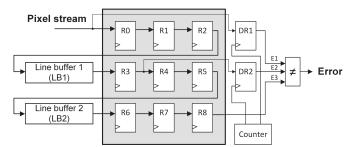

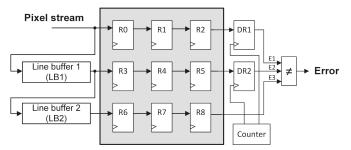

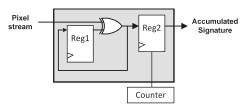

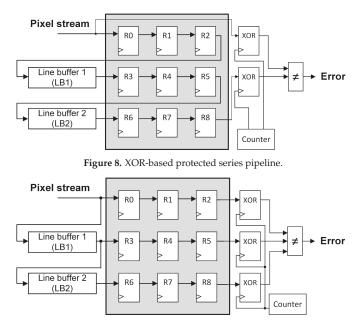

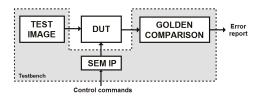

Finally, two articles presented a link between the research fields of cryptography and image processing, respectively. In [14] the authors presented the total ionizing dose effects on a delay-based physical unclonable function implemented in FPGAs for authentication and key generation in space systems. Article [15] discussed a novel method to protect series and parallel line-buffer-based image processing pipelines against configuration memory errors in SRAM-Based FPGAs. The proposed technique presented lower FPGA resource usage, and fewer false positive detections than the other techniques; moreover, the image processing system did not have to be stopped and rebooted upon errors due to the partial reconfiguration.

#### 3. Future

The wide range of articles in this Special Issue exemplifies the broadness of the field of radiation hardened micro-electronics. The dream to enable high performance computing, signal processing,

and communication in the harshest and most diverse radiation environments presents the community with many research challenges. It inevitably brings researchers together from several disciplines ranging from nuclear and solid-state physics over advanced modeling approaches and creative circuit design techniques to the application of progressive algorithms and deep learning to optimize system performance for the most diverse applications under the harshest of conditions.

Acknowledgments: I would like to thank all of the researchers who submitted articles to this Special Issue for their excellent contributions. I am also grateful to all of the reviewers who helped in the evaluation of the manuscripts and made very valuable suggestions to improve the quality of the contributions. I would like to acknowledge the editorial board of MDPI Electronics, who invited me to guest edit this Special Issue. I am also grateful to the Electronics Editorial office staff who worked thoroughly to maintain the rigorous peer-review schedule and timely publication.

#### References

- Wang, T.; Wan, X.; Jin, H.; Li, H.; Sun, Y.; Liang, R.; Xu, J.; Zheng, L. Optimization of the Cell Structure for Radiation-Hardened Power MOSFETs. *Electronics* 2019, *8*, 598. [CrossRef]

- 2. Liu, M.; Lu, W.; Yu, X.; Wang, X.; Li, X.; Yao, S.; Guo, Q. Mechanism of Degradation Rate on the Irradiated Double-Polysilicon Self-Aligned Bipolar Transistor. *Electronics* **2019**, *8*, 657. [CrossRef]

- 3. Jeong, K.; Ro, D.; Lee, G.; Kang, M.; Lee, H.-M. A Radiation-Hardened Instrumentation Amplifier for Sensor Readout Integrated Circuits in Nuclear Fusion Applications. *Electronics* **2018**, *7*, 429. [CrossRef]

- 4. Budroweit, J.; Jaksch, M.P.; Sznajder, M. Proton Induced Single Event Effect Characterization on a Highly Integrated RF-Transceiver. *Electronics* **2019**, *8*, 519. [CrossRef]

- 5. Van Bockel, B.; Prinzie, J.; Leroux, P. Radiation Assessment of a 15.6ps Single-Shot Time-to-Digital Converter in Terms of TID. *Electronics* **2019**, *8*, 558. [CrossRef]

- Andreou, C.M.; González-Castaño, D.M.; Gerardin, S.; Bagatin, M.; Gómez Rodriguez, F.; Paccagnella, A.; Prokofiev, A.V.; Javanainen, A.; Virtanen, A.; Liberali, V.; et al. Low-Power, Subthreshold Reference Circuits for the Space Environment: Evaluated with γ-rays, X-rays, Protons and Heavy Ions. *Electronics* 2019, *8*, 562. [CrossRef]

- 7. Prinzie, J.; Smedt, V.D. Single Event Transients in CMOS Ring Oscillators. Electronics 2019, 8, 618. [CrossRef]

- 8. Díez-Acereda, V.L.; Khemchandani, S.; del Pino, J.; Mateos-Angulo, S. RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers. *Electronics* **2019**, *8*, 690.

- 9. Muñoz-Quijada, M.; Sanchez-Barea, S.; Vela-Calderon, D.; Guzman-Miranda, H. Fine-Grain Circuit Hardening Through VHDL Datatype Substitution. *Electronics* **2019**, *8*, 24. [CrossRef]

- 10. Prinzie, J.; Appels, K.; Kulis, S. Optimal Physical Implementation of Radiation Tolerant High-Speed Digital Integrated Circuits in Deep-Submicron Technologies. *Electronics* **2019**, *8*, 432. [CrossRef]

- 11. Cai, C.; Fan, X.; Liu, J.; Li, D.; Liu, T.; Ke, L.; Zhao, P.; He, Z. Heavy-Ion Induced Single Event Upsets in Advanced 65 nm Radiation Hardened FPGAs. *Electronics* **2019**, *8*, 323. [CrossRef]

- 12. Banteywalu, S.; Khan, B.; De Smedt, V.; Leroux, P. A Novel Modular Radiation Hardening Approach Applied to a Synchronous Buck Converter. *Electronics* **2019**, *8*, 513. [CrossRef]

- Reyneri, L.M.M.; Serrano-Cases, A.; Morilla, Y.; Cuenca-Asensi, S.; Martínez-Álvarez, A. A Compact Model to Evaluate the Effects of High Level C++ Code Hardening in Radiation Environments. *Electronics* 2019, *8*, 653. [CrossRef]

- 14. Martin, H.; Martin-Holgado, P.; Morilla, Y.; Entrena, L.; San-Millan, E. Total Ionizing Dose Effects on a Delay-Based Physical Unclonable Function Implemented in FPGAs. *Electronics* **2018**, *7*, 163. [CrossRef]

- 15. Aranda, L.A.; Reviriego, P.; Maestro, J.A. Protecting Image Processing Pipelines against Configuration Memory Errors in SRAM-Based FPGAs. *Electronics* **2018**, *7*, 322. [CrossRef]

© 2019 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

### Article Optimization of the Cell Structure for Radiation-Hardened Power MOSFETs

# Teng Wang <sup>1</sup>, Xin Wan <sup>2,3,\*</sup>, Hu Jin <sup>2</sup>, Hao Li <sup>2</sup>, Yabin Sun <sup>4</sup>, Renrong Liang <sup>5</sup>, Jun Xu <sup>3,5</sup> and Lirong Zheng <sup>1</sup>

- <sup>1</sup> School of Information Science and Technology, Fudan University, Shanghai 200433, China; tengwang13@fudan.edu.cn (T.W.); Irzheng@fudan.edu.cn (L.Z.)

- <sup>2</sup> Aurorachip Co. Ltd., Zhejiang 314000, China; h.jin@aurorachip.com (H.J.); h.li@aurorachip.com (H.L.)

- <sup>3</sup> Center for High Reliability Power Semiconductor, Yangtze Delta Region Institute of Tsinghua University, Zhejiang 314000, China; junxu@tsinghua.edu.cn

- <sup>4</sup> School of Information Science Technology, East China Normal University, Shanghai 200241, China; ybsun@ee.ecnu.edu.cn

- <sup>5</sup> Institute of Microelectronics, Tsinghua University, Beijing 100084, China; liangrr@tsinghua.edu.cn

- \* Correspondence: x.wan@aurorachip.com; Tel.: +86-151-2000-1156

Received: 16 March 2019; Accepted: 25 May 2019; Published: 28 May 2019

**Abstract:** Power MOSFETs specially designed for space power systems are expected to simultaneously meet the requirements of electrical performance and radiation hardness. Radiation-hardened (rad-hard) power MOSFET design can be achieved via cell structure optimization. This paper conducts an investigation of the cell geometrical parameters with major impacts on radiation hardness, and a rad-hard power MOSFET is designed and fabricated. The experimental results validate the devices' total ionizing dose (TID) and single event effects (SEE) hardness to suitably satisfy most space power system requirements while maintaining acceptable electrical performance.

Keywords: radiation-hardened; single event gate rupture (SEGR); SEB; power MOSFETs

#### 1. Introduction

Power MOSFETs are widely applied in space power systems [1]. However, they are vulnerable to particle from galactic cosmic rays, solar flares, and radiation belts, which may cause total ionizing dose effects, single event gate rupture (SEGR) effects and single event burnout (SEB) effects [2,3]. There has been a substantial research on such radiation effects [4–7], whereas radiation hardening on power MOSFETs, the more necessary resolve, has only been discussed in a few articles [8–12] whose content mostly focused on a single hardening issue, such as SEB, SEGR, and TID. Apparently, these radiation effects, along with electrical performance, are essential considerations during the design and fabrication stage of a power MOSFET; moreover, many trade-offs should be decided when balancing between several electrical parameters and radiation survivability. This paper entails a description of the design and fabrication of TID-, SEB-, and SEGR-hardened power MOSFETs, on the basis of a careful optimization of the devices' cell structure and doping profile. Experimental verifications conducted show excellent radiation hardness and acceptable electrical performance of such devices for space power systems.

#### 2. Design Considerations

#### 2.1. Cell Structure

A power MOSFET chip is composed of several regions, including cell region, termination structure, gate bus, and gate pad. Of these, the cell region determines many electrical parameters and typically

accounts for the majority of the chip area. However, it is also the most vulnerable region to irradiation. Normally, SEGR, SEB, and TID effects should be simultaneously mitigated in the cell region, whereas in other regions, only one of these effects is considered.

The cell structures and geometrical parameters of a power MOSFET are detailed in classic textbooks on power semiconductors [13,14]. Such geometrical parameters, together with the doping profiles, determine most of the device's electrical parameters, such as on-resistance ( $R_{on}$ ), threshold voltage ( $V_{th}$ ), and breakdown voltage ( $BV_{ds}$ ). Nonetheless, the present study does not consider detailed discussions regarding the effect of these parameters on the performance of the device. However, the electrical performance must be reasonably reserved when radiation-hardened power MOSFETs are designed.

#### 2.2. Oxide Thickness

Gate oxide thickness is affected by three major factors, namely threshold voltage, SEGR effects and TID effects, and secondary factors as device capacitance and electro-static discharge (ESD) robustness. TID effects are mitigated by keeping the gate oxide as thin as possible [15]. Conversely, a thin gate oxide exhibits a reduced ability to withstand the SEGR effects [16]. Most power MOSFETs are designed within a pre-irradiation threshold voltage ( $V_{ih}$ ) of 2–4 V. Certain radiation hardness requires  $V_{th}$  to remain within such specifications after receiving a specified dose, followed by high-temperature annealing. On this basis, the chosen  $V_{th}$  is greatly influenced by the shifting behaviors. The shifts could be negative or positive, depending on the dominant type of radiation-induced charge [15]. For negative-shifting-dominated cases, a higher  $V_{th}$  can save additional room for  $V_{th}$  shifting and is thus preferred. By contrast, for positive-shifting-dominated cases, a lower  $V_{th}$  is preferred for the same reason. Once the gate oxide  $t_{OX}$  is given,  $V_{th}$  can be adjusted by changing the doping density in the channel region.

Likewise, SEGR effects are mitigated by keeping the  $t_{OX}$  large enough to avoid dielectric breakdown. During a heavy ion strike, the dielectric strength is temporarily reduced. Models with more physical insight were proposed by Javanainen et al. [17], although a simple empirical expression with little physical justification is adopted in this work, as follows [16]:

$$E_{CRIT} = \frac{V_{GS}}{t_{OX}} = \frac{E_{BD}}{\left(1 + \frac{Z}{44}\right)},\tag{1}$$

where  $E_{CRIT}$  is the critical electric field of gate oxide that must withstand heavy-ion injection;  $E_{BD}$  is the intrinsic dielectric breakdown strength of gate oxide, which is 10<sup>7</sup> V/cm for most thermal oxides; and Z is the atomic number of the injected heavy ions.

In rad-hard power MOSFETs' datasheets, SEE resistance ability is illustrated as a safe operating area under certain heavy-ion injection (SEE SOA) [18,19]. In principle, SEE SOA is expressed as a series of gate and drain voltage bias conditions. The negative gate bias is directly applied to the gate to contribute all its value to the gate dielectrics, whereas only a portion of the drain bias is coupled to the gate dielectrics after heavy-ion injection [20]. Therefore, the minimum gate oxide bounded by SEGR effects can be calculated as follows:

$$t_{OX,min} = \frac{\left(\alpha V_{DS} - V_{GS}\right)\left(1 + \frac{Z}{44}\right)}{E_{BD}},$$

(2)

where  $\alpha$  is the coupled ratio of drain voltage related to the device design, as discussed later. Note that the bias conditions considered here are the worst bias conditions for SEGR production and are, hence, used for SEGR testing. The shift in the threshold voltage due to TID effects is a major problem for all metal-oxide-semiconductor (MOS) devices. For power MOSFETs, the relatively thick gate oxide makes this issue more severe. The  $V_{th}$  shift has been attributed to two kinds of radiation-induced charges, namely oxide charges and interface traps [15]. Therefore, the  $V_{th}$  shift ( $\Delta V_{th}$ ) is the sum of the oxide-charge-induced negative shift, named  $\Delta V_{ot}$ , and the interface-trap-induced positive shift, named  $\Delta V_{it}$ . Both  $\Delta V_{ot}$  and  $\Delta V_{it}$  are strongly related to  $t_{OX}$ . The relationship can be expressed as follows [21]:

$$\Delta V_{ot,it} = \frac{1}{C_{OX}} \times \frac{-1}{t_{OX}} \int_0^{t_{OX}} \rho_{ot,it}(x) x dx, \tag{3}$$

where  $\rho_{ot,it}$  is the charge distribution of radiation-induced oxide-trapped or interface-trapped charge. Reduction of  $t_{OX}$  entails a two-fold effect. First, reducing  $t_{OX}$  can reduce the  $V_{th}$  shift for a given charge density, which is attributed to a larger  $C_{OX}$  resulting from a thinner  $t_{ox}$ . Second, it can reduce charge generation for a given dose, as shown in Equation (3). The integration term can be simplified by introducing a uniform charge generation for the oxide charge, resulting in the expression [22]:

$$\Delta V_{ot} = -\frac{\Delta Q_{ot}}{C_{OX}} = -\frac{qg_0 D t_{OX} Y_h \sigma_h}{C_{OX}} = -\frac{qg_0 D Y_h \sigma_h}{\varepsilon_{OX}} t_{OX}^2, \tag{4}$$

where *q* is the electric charge (expressed in Coulomb),  $g_0$  is the electron–hole pair generation rate in SiO<sub>2</sub> (in pairs/cm<sup>3</sup>/rad(SiO<sub>2</sub>)), *D* is the total dose level in units of rad(SiO<sub>2</sub>),  $Y_h$  is charge yield of holes,  $\sigma_h$  is trapping cross section for holes captured by hole traps in oxide, and  $\varepsilon_{OX}$  is the dielectric constant of SiO<sub>2</sub>. Note that *Y* and  $\sigma$  are affected by the electric field presented during irradiation, and the trapped charges can also be annealed with elevated temperature.

Interface traps generation is much more complicated. However, protons are considered to play a key role in the formation of interface traps. Moreover, the process of proton generation in the oxide is intimately related to the transport of holes. By introducing the parameter  $Y_p$ , which is the product of  $N_{D'H}$  (concentration of hydrogen-containing defects) and  $\sigma_{D'H}$  (cross section for proton release from these defects) [23],  $\Delta V_{it}$  can be expressed in a similar manner as  $\Delta V_{ot}$ , as follows:

$$\Delta V_{it} = \frac{\Delta Q_{it}}{C_{OX}} = \frac{qg_0 D t_{OX} Y_h Y_p \sigma_p}{C_{OX}} = \frac{qg_0 D Y_h Y_p \sigma_p}{\varepsilon_{OX}} t_{OX'}^2$$

(5)

where  $\sigma_p$  is the cross section of protons captured by the traps at interface. Note that for one to get a relatively simple solution, a uniform distribution of  $N_{D'H}$  (and, hence, the  $Y_p$ ) in terms of space has been assumed, which may not be true for all cases. Moreover,  $N_{D'H}$  is space-and-time-dependent and  $\sigma_p$  is field-dependent. Therefore, a simple method for quantitatively calculating the radiation-induced interface traps for all cases seems impractical, if not impossible. However, as an analytical model, Equation (5) does reflect the relationship of the interface trap generation with the hole transport, as widely accepted by society. Combining Equations (4) and (5) allows the maximum  $t_{OX}$  bounded by the TID effects to be expressed as follows:

$$t_{OX,max} = \sqrt{\frac{\Delta V_{th,max} \times \varepsilon_{OX}}{qg_0 D Y_h | Y_p \sigma_p - \sigma_h|}},\tag{6}$$

where  $\Delta V_{th,max}$  is the maximum allowed threshold shift. Note that even for a given dose,  $|Y_p\sigma_p - \sigma_h|$  varies with dose rate, bias condition, and temperature and is strongly related to the fabrication process. Given this limitation and the uncertainties,  $|Y_p\sigma_p - \sigma_h|$  remains a useful parameter to be extracted from the experimental perspective and can thus be used as a starting point in the device's design. Manipulating Equations (2) and (6) yields the lower and upper bounds of  $t_{OX}$ . Once  $t_{OX}$  is chosen, channel doping density can be fixed with equations governing  $V_{th}$ .

#### 2.3. JFET Region Width

Parameter  $\alpha$  has been introduced in Section 2.2 to account for the coupling of drain voltage to the gate dielectric. Based on Equation (2), the lower bound of  $t_{OX}$  can be reduced with reduced  $\alpha$ , which means that a larger range of  $t_{OX}$  is available at the design stage. Moreover,  $\alpha$  has been

demonstrated to correlate with JFET region width ( $L_{JFET}$ ) and thus can be reduced, with a reduced  $L_{JFET}$  [10], as illustrated in Figure 1.

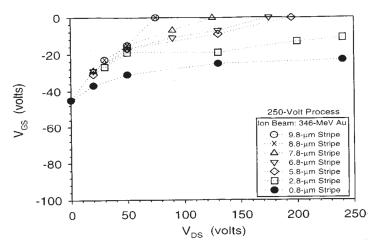

**Figure 1.** Single event gate rupture (SEGR) failure threshold responses for various  $L_{JFET}$ , after Reference [10].

Although it greatly improves SEGR hardness, a small  $L_{JFET}$  creates a negative impact on  $R_{on}$ . The specific resistance contributed by the JFET region ( $R_{IFET,SP}$ ) can be expressed as follows:

$$R_{JFET,SP} = \rho_{JFET} H_{JP} \frac{L_{CELL}}{L_{JFET}},$$

(7)

where  $\rho_{JFET}$  is the resistivity of the JFET region, which is inversely proportional to JFET region doping;  $H_{JP}$  is body junction depth;  $L_{CELL}$  is the cell pitch; and  $L_{JFET}$  is the JFET region width. According to Equation (7),  $R_{JFET,SP}$  is inversely proportional to  $L_{JFET}$ ; thus, decreasing  $L_{JFET}$  will greatly increase  $R_{JFET,SP}$ , leading to worse resistance. Fortunately, the JFET region's resistance is only a portion of the total resistance. Therefore, the increasing on-resistance can be tolerated, as long as  $L_{JFET}$  is not extremely small. Nevertheless, the chosen  $L_{JFET}$  remains a critical element. A previous study [10] asserted that for 250 V power MOSFETs,  $L_{JFET}$  should be less than 5.8 µm to achieve a full  $V_{DS}$  range under zero gate bias. The JFET region should be carefully designed for SEGR-hardened devices.

#### 2.4. P Body and P+ Well Doping

Several models have been proposed to describe the SEB process [24–26]. For instance, the parasitic BJT has been postulated to play a key role in SEB production. With the P-body region of the power MOSFET acting as the base region of the parasitic BJT, the body's doping profile becomes essential for hardening the device against SEB effects. In general, larger P-body depth ( $H_{JP}$ ) and higher doping concentrations ( $N_{BODY}$ ), as well as a reduced length between N+ source edge and P+ well edge ( $L_{BODY}$ ), are desirable for an SEB-hardened cell design. However, as expressed in Equation (7), a deeper P-body has negative effects on  $R_{JFET,SP}$ , whereas a high  $N_{BODY}$  or a short  $L_{BODY}$  may affect the channel doping concentration.

#### 3. Results

TID- and SEE-hardened power MOSFETs were designed on account of the trade-offs mentioned above. The key geometrical parameters and doping concentrations essential for the design are summarized in Table 1. Buffer layer technology was employed to improve SEB hardness [11]. The values of other parameters were chosen as common non-rad-hard power MOSFET designs. The whole chip

area was 12 mm<sup>2</sup>, whereas the active area (cell region) was approximately 8.5 mm<sup>2</sup>. Stripe cell topology [10] was considered.

| Symbol in Figure 1 | Value                               | Unit             |

|--------------------|-------------------------------------|------------------|

| $t_{ox}$           | 80                                  | nm               |

| $H_{IP}$           | 3                                   | μm               |

| L <sub>CELL</sub>  | 10                                  | μm               |

| $L_{BODY}$         | ~2                                  | μm               |

| $L_{JFET}$         | $^{\sim 3}_{\sim 5 \times 10^{16}}$ | μm               |

| N <sub>BODY</sub>  | $\sim 5 \times 10^{16}$             | cm <sup>-3</sup> |

Table 1. Key geometrical parameters and doping concentrations for device design.

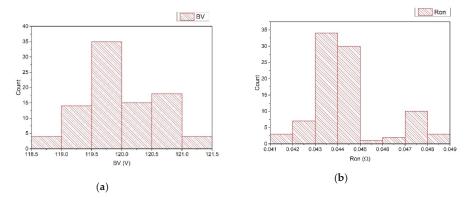

The designed power MOSFETs were fabricated by Tianjin Zhonghuan Semiconductor Co., Ltd., with 6-inch wafers. Processes with high thermal budget, such as the P-body driven process, were adjusted prior to gate oxidation to improve TID hardness. Diced devices were packaged in TO-220. Ninety devices were randomly selected for testing under a Keysight B1506 power semiconductor analyzer. Figure 2 illustrates the distributions of the testing results, with median  $BV_{ds}$  around 120 V and median  $R_{on}$  around 44 m $\Omega$ . For this cell design, for a 120 V maximum blocking ability, the specific resistance was 3.74 m $\Omega$ -cm<sup>2</sup>. All the  $V_{th}$  values fell in the range of 2.36–2.62 V, of which more than 80% were roughly 2.40–2.50 V (not depicted in the figure). The ESD endurance exceeded 2000 V in human body model (HBM) mode, and the maximum avalanche energy was 662.5 mJ.

Figure 2. Test results for 90 randomly selected devices: (a) Breakdown voltage results; (b) On-resistance results.

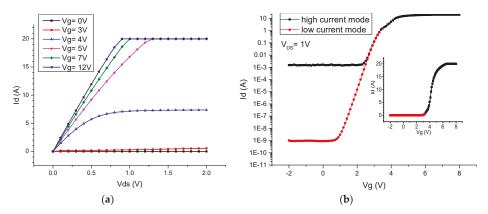

Figure 3 illustrates the typical output and transfer curves, as measured with the Keysight B1506. The B1506 testing system has two modes, namely high-current and low-current modes. On the one hand, the high-current mode is able to test current up to 20 A; the plateau is caused by this limitation. However, this mode is not suitable for testing low current because of the leakage issue. On the other hand, the low-current mode is able to test current under a picoampere, although the maximum current in this mode is 1 A. The transfer curves in Figure 3 combined the results for both testing modes.

The fabricated devices were irradiated with Co-60 at the Shanghai Institute of Applied Physics, Chinese Academy of Sciences. The devices were placed on especially designed PCB boards, allowing separately the gate and drain node biases. The PCB boards were separated from the radiation source by approximately 30 cm, thus yielding a calculated dose rate of 100 rad(Si)/s. Additionally, the PCB boards were made to be as small as possible to minimize the dose rate inhomogeneous. Subsequently, the devices were irradiated under room temperature and then annealed at 100 °C for 168 h under the

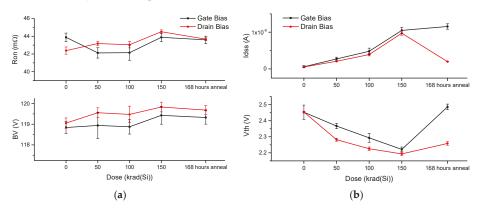

same bias condition after irradiation. For the gate bias condition (GB), the gate was biased at 12 V, with the drain and the source connected to ground. For the drain biased condition (DB), the drain was biased at 80 V, with the gate and the source connected to ground. Three devices were tested under each bias condition. Results of the TID experiment are displayed in Figure 4.

Figure 3. (a) Output curves and (b) transfer curves for the fabricated devices.

**Figure 4.** Parameters change with total ionizing dose (TID) dose and annealing time: (**a**)  $R_{on}$  and  $BV_{dss}$ ; (**b**)  $I_{dss}$  and  $V_{th}$ .

Based on the figure, the on-resistance and breakdown voltage indicated negligible change after 150 krad(Si) TID irradiation and 168 h annealing, for both bias conditions.  $I_{dss}$  also increased with the dose for GB and DB, whereas  $I_{dss}$  increased after annealing under GB and consequently decreased under DB. For the threshold voltage,  $V_{th}$  decreased with the dose for both bias conditions, but with different annealing behavior. More specifically,  $V_{th}$  rebounded to a value slightly higher than its initial value under GB, whereas the rebound was much less under DB. Nonetheless, for each bias condition, at 150 krad(Si) dose, the annealing-induced  $V_{th}$  shift was less than 0.25 V. The shift behaviors of  $V_{th}$  during irradiation and annealing are described further under the discussion section. The terminations used in these devices included a traditional floating ring and filed plate structure, with optimized parameters [9]. The small  $BV_{ds}$  and  $I_{dss}$  change (Figure 4) indicate that the design of the termination was also radiation-hardened.

SEE experiments were conducted at Institute of Modern Physics, Chinese Academy of Sciences. The chips were packaged in TO-39, with the cap removed. 794 MeV Xe ions with a surface linear energy transfer (LET) of approximately 66 MeV·cm<sup>2</sup>/mg were used. During the experiment,  $V_{GS}$  was set to 0 V, and  $V_{DS}$  was increased in steps of 10 V. The flux was roughly within 5000–10,000 ions/cm<sup>2</sup>s; the pass criteria was both gate and drain leakage current stay within the specification value after  $2 \times 10^6$  ions/cm<sup>2</sup> irradiation [19]. Neither SEB nor SEGR was observed under  $V_{DS} = 100$  V with a  $V_{GS} = 0$  V bias condition.

#### 4. Discussion

In space applications, the dose rate is much lower than the high-dose rate (HDR) experiment typically performed in laboratory. Such disparity may cause a significant difference of  $|Y_p \sigma_p - \sigma_h|$ used in Equation (6) in the two cases. However, low-dose rate (LDR) experiments are relatively time-consuming and expensive. Therefore, the present study adopted an accelerated aging test to estimate the worst-case degradation of MOS devices [27,28], as it has been proven applicable to power MOSFETs [29]. Initially, the devices were irradiated with HDR for a relatively short time. Since the interface traps took a longer time to form, hole trapping in oxide defects dominated in this stage, thereby yielding  $|Y_p\sigma_p - \sigma_h| \approx \sigma_h$  and a negative  $\Delta V_{th}$ . In the annealing stage, the build-up of interface traps dominated while the trapped oxide charges decreased with time, yielding a recovery or even a rebound of  $\Delta V_{th}$ . Therefore, the HDR+ high-temperature annealing procedure eliminated charge compensation in the LDR environment and produced worse (conserved) results. To further investigate the details of the behavior of radiation-induced charges, a mid-gap method was used to separate these two charges [30,31], where  $V_T$  is the threshold voltage extracted by using the maximum transconductance method. Here, note that  $V_T$  was different from  $V_{th}$  in Figure 4b, which was basically the gate voltage as the drain current reached 1 mA. Therefore, it was convenient for the engineer to monitor  $V_{th}$ . On the other hand,  $V_T$  has a physical meaning and is more accurate for parameter calculation. The mobility was extracted as follows:

$$\sqrt{I_D(sat)} = \sqrt{\frac{W\mu_n C_{OX}}{2L}} (V_{GS} - V_T), \tag{8}$$

where  $I_{D(sat)}$  is drain current in the saturation region, *W* is the total channel width, *L* is the channel length, and  $C_{OX}$  is the gate oxide capacitance. Since Figure 4 depicts that the sample-to-sample variations were acceptable, a single device was randomly selected to perform extraction for each bias condition. Table 2 presents the extracted parameters of the device pre-irradiation, at 150 krad(Si) irradiation, and after annealing.

|                 | Unit                 | Vii       | rgin       | 150 ki                | rad(Si)             | An                    | neal                  |

|-----------------|----------------------|-----------|------------|-----------------------|---------------------|-----------------------|-----------------------|

|                 | Unit                 | Gate Bias | Drain Bias | Gate Bias             | Drain Bias          | Gate Bias             | Drain Bias            |

| $V_T$           | V                    | 3.75      | 3.82       | 3.61                  | 3.68                | 3.88                  | 3.66                  |

| $V_{ot}$        | V                    | 0.96      | 0.99       | 0.45                  | 0.30                | 0.68                  | 0.69                  |

| $\mu_n$         | cm <sup>2</sup> /V⋅s | 319.34    | 339.00     | 273.30                | 252.45              | 219.05                | 279.15                |

| $\Delta V_T$    | V                    | 0.00      | 0.00       | -0.14                 | -0.14               | 0.13                  | -0.15                 |

| $\Delta V_{ot}$ | V                    | 0.00      | 0.00       | -0.51                 | -0.69               | -0.28                 | -0.30                 |

| $\Delta V_{it}$ | V                    | 0.00      | 0.00       | 0.37                  | 0.55                | 0.41                  | 0.14                  |

| $\Delta N_{ot}$ | cm <sup>-2</sup>     | 0.00      | 0.00       | $1.37 \times 10^{11}$ | $1.86\times10^{11}$ | $0.76 \times 10^{11}$ | $0.80 \times 10^{11}$ |

| $\Delta N_{it}$ | cm <sup>-2</sup>     | 0.00      | 0.00       | $1.00\times10^{11}$   | $1.48\times10^{11}$ | $1.11\times10^{11}$   | $0.39 	imes 10^{11}$  |

| $\Delta \mu_n$  | cm <sup>2</sup> /V⋅s | 0.00      | 0.00       | -46.05                | -86.85              | -100.29               | -59.85                |

Table 2. Extracted parameters for device pre-irradiation.

The TID-induced oxide-charge density was  $1.86 \times 10^{11}$  cm<sup>-2</sup> for the drain bias condition, whereby such oxide charges should lead to a -0.69 V  $V_T$  shift. However, the negative shift was partially compensated by an interface-trap-induced positive shift, resulting in a net shift of -0.14 V. For the GB, both  $\Delta N_{ot}$  and  $\Delta N_{it}$  were 30% less than those for the DB. During the annealing process, almost half the generated oxide charges were reduced for both bias conditions. Nevertheless, the annealing behaviors of  $N_{it}$  for both conditions were different;  $N_{it}$  increased by approximately 10% for the GB

and reduced by roughly 75% for the DB. Such similarity between  $N_{it}$  and  $I_{dss}$  during the annealing stage indicates that the increasing trend for  $I_{dss}$  might be related to the generation of interface traps. Moreover, as expected, the  $N_{it}$  generation and annealing was qualitatively consistent with the extracted mobility value [32]. The data in Table 2 can be used to calculate  $Y_p\sigma_p$  and  $\sigma_h$ , as a starting point in the device design. However, these parameters are highly process-dependent and are, therefore, only valid for this specific process flow.

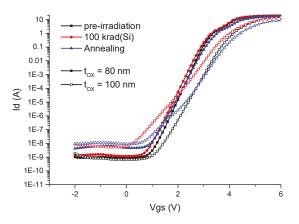

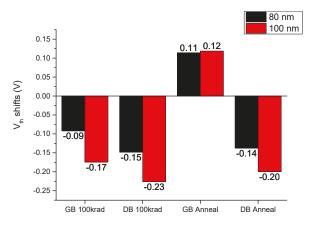

The parameter selection was further evaluated through fabrication of devices with  $t_{OX} = 100$  nm, which were later subjected to TID experiments. For the other geometric parameters, the process flow and TID experiment setups were kept the same as those for the 80 nm samples. However, note that the oxidation time for the 100 nm samples was longer; thus, worse TID hardness could be expected because of the larger thermal budget and thicker  $t_{OX}$ , as illustrated in Figure 5. Here, the bias condition was the same as the gate bias condition described in Section 3. Much larger negative shifts and significant twists in the figure indicate both oxide charges and interface traps being much more in the 100 nm oxide thickness. Figure 6 illustrates the  $V_T$  shifts under the two bias conditions after 100 krad irradiation and annealing, where the shifts were higher with thicker  $t_{OX}$ , thus reflecting better SEGR hardness. A comparison of SEGR hardness of these devices is a future direction relative to the present study.

Figure 5. Subthreshold characteristics of power devices with 80 nm and 100 nm gate oxides pre- and post-irradiation and post-annealing.

Figure 6. Threshold voltage shifts for 80 nm and 100 nm gate oxide devices under gate bias and drain bias (RB) conditions, after receiving 100-krad(Si) TID and annealing.

#### 5. Conclusions

A rad-hard power MOSFET is appropriately designed through consideration of several radiation effects as TID, SEB, and SEGR, as well as a balance among electrical parameters as  $R_{on}$ ,  $V_{th}$  and  $BV_{ds}$ . In this work, the effects of cell structure adjustment on the performance of a power MOSFET were examined, by first analyzing the design parameters. Next, a SEE- and TID-hardened power MOSFET was designed and fabricated by implementing the accompanying design rules. Results of the investigation confirmed the achievement of excellent radiation hardness and decent specific on-resistance for the device. Technically, the  $V_{th}$  shifts were less than 0.25 V for 150 krad(Si) irradiation and 168 h annealing. No SEE was observed under  $V_{GS} = 0$  V and the  $V_{DS} = 100$  V bias condition with LET = 66 MeV·cm<sup>2</sup>/mg under Xe ion irradiation. Further investigation on the TID experimental results indicated the estimated charge density induced by radiation and annealing. Moreover, devices with thicker gate oxide were fabricated as the counterpart for the parameter selection evaluation. Experiments with these devices showcased their great potential for application in space power systems.

As a general rule, radiation environments are different for various mission orbits. Notably, a spacecraft in van-Allen belts would suffer more from a TID effect, whereas a deep space mission would require high SEE-hardness devices. Additionally, devices in low-Earth orbits requires lower radiation hardness while they are expected to exhibit better electrical parameters. Hence, various devices with different electrical parameters and radiation hardness are required for different missions. The results in the present study provide an insight for the power semiconductor designer to balance the parameters involved and to design power MOSFET devices based on the application requirements.

Author Contributions: Conceptualization, methodology, writing—original draft preparation, T.W. and X.W.; Chip design, H.J.; Chip fabrication, H.L.; TID and SEE experiment, T.W.; Data analysis, Y.S.; Writing—review and editing, R.L. and J.X.; Supervision, J.X. and L.Z.; Resources and funding acquisition, L.Z.

Funding: This research received no external funding.

Acknowledgments: The authors would like to thank Wanli Wang and Xiaofang Li from Tianjin Zhonghuan Semiconductor Co., Ltd. for their help on device fabrication.

**Conflicts of Interest:** The authors declare no conflicts of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

| Symbol              | Description                                                                            | Equation |

|---------------------|----------------------------------------------------------------------------------------|----------|

| E <sub>CRIT</sub>   | Critical electric field of gate oxide that must withstand heavy-ion injection          | (1)      |

| $V_{GS}$            | Applied gate voltage                                                                   | (1)      |

| $t_{OX}$            | Gate oxide thickness                                                                   | (1)      |

| $E_{BD}$            | Intrinsic dielectric breakdown strength                                                | (1)      |

| Ζ                   | The atomic number of the injected heavy ions                                           | (1)      |

| t <sub>OX,min</sub> | The minimum gate oxide bounded by single event gate rupture (SEGR) effects             | (2)      |

| α                   | The coupled ratio of drain voltage                                                     | (2)      |

| $V_{DS}$            | Applied drain voltage                                                                  | (2)      |

| $\Delta V_{ot,it}$  | Threshold shifts induced by oxide-charge or interface traps                            | (3)      |

| $C_{OX}$            | Gate capacitance                                                                       | (3)      |

| ρ <sub>ot,it</sub>  | The charge distribution of radiation-induced oxide-trapped or interface-trapped charge | e (3)    |

| $\Delta Q_{ot}$     | Radiation-induced charges in oxide                                                     | (4)      |

| q                   | Electric charge                                                                        | (4)      |

| 80                  | Electron-hole pair generation rate in SiO <sub>2</sub>                                 | (4)      |

| D                   | The total dose level                                                                   | (4)      |

| $Y_h$               | Charge yield of holes                                                                  | (4)      |

| $\sigma_h$          | Trapping cross section for holes captured by hole traps in oxide                       | (4)      |

| $\varepsilon_{OX}$  | The dielectric constant of $SiO_2$                                                     | (4)      |

#### Nomenclature

| Symbol               | Description                                                                                                     | Equation |

|----------------------|-----------------------------------------------------------------------------------------------------------------|----------|

| $\Delta Q_{it}$      | Radiation-induced interface trap charges                                                                        | (5)      |

| $Y_p$                | Product of concentration of hydrogen-containing defects and cross section for proton release from these defects | (5)      |

| $\sigma_p$           | The cross section of protons captured by the traps at interface                                                 | (5)      |

| t <sub>OX,max</sub>  | The maximum gate oxide bounded by total ionizing dose (TID) effects                                             | (6)      |

| $\Delta V_{th,max}$  | The maximum allowed threshold shift                                                                             | (6)      |

| R <sub>IFET,SP</sub> | Specific resistance contributed by the JFET region                                                              | (7)      |

| $\rho_{IFET}$        | The resistivity of the JFET region                                                                              | (7)      |

| $H_{IP}$             | Body junction depth                                                                                             | (7)      |

| L <sub>CELL</sub>    | Cell pitch                                                                                                      | (7)      |

| $L_{JFET}$           | JFET region width                                                                                               | (7)      |

#### References

- Adell, P.C.; Scheick, L.Z. Radiation Effects in Power Systems: A Review. *IEEE Trans. Sci.* 2013, 60, 1929–1952. [CrossRef]

- 2. Barth, J.; Gee, G.; Adolphsen, J.W. First observation of proton induced power MOSFET burnout in space: The CRUX experiment on APEX. *IEEE Trans. Sci.* **1996**, *43*, 2921–2926.

- George, J.S.; Clymer, D.A.; Turflinger, T.L.; Mason, L.W.; Stone, S.; Koga, R.; Beach, E.; Huntington, K.; Lauenstein, J.-M.; Titus, J.; et al. Response Variability in Commercial MOSFET SEE Qualification. *IEEE Trans. Sci.* 2017, 64, 317–324. [CrossRef]

- Kuboyama, S.; Mizuta, E.; Nakada, Y.; Shindou, H. Physical analysis of damage sites introduced by SEGR in silicon vertical power MOSFETs and implications for post-irradiation gate-stress test. *IEEE Trans. Nucl. Sci.* 2019, in press. [CrossRef]

- Singh, G.; Galloway, K.F.; Russell, T.J. Radiation-Induced Interface Traps in Power Mosfets. *IEEE Trans. Sci.* 1986, 33, 1454–1459. [CrossRef]

- Picard, C.; Brisset, C.; Hoffmann, A.; Charles, J.-P.; Joffre, F.; Adams, L.; Siedle, A.H. Use of electrical stress and isochronal annealing on power MOSFETs in order to characterize the effects of 60 Co irradiation. *Microelectron. Reliab.* 2000, 40, 1647–1652. [CrossRef]

- Titus, J.L. An Updated Perspective of Single Event Gate Rupture and Single Event Burnout in Power MOSFETs. *IEEE Trans. Sci.* 2013, 60, 1912–1928. [CrossRef]

- Roper, G.B.; Lowis, R. Development of a radiation hard n-channel power MOSFET. *IEEE Trans. Nucl. Sci.* 1983, 30, 4110–4115. [CrossRef]

- 9. Davis, K.; Schrimpf, R.; Cellier, F.; Galloway, K.; Burton, D.; Wheatley, C. The effects of ionizing radiation on power-MOSFET termination structures. *IEEE Trans. Sci.* **1989**, *36*, 2104–2109. [CrossRef]

- Savage, M.; Burton, D.; Wheatley, C.; Titus, J.; Gillberg, J. An improved stripe-cell SEGR hardened power MOSFET technology. *IEEE Trans. Sci.* 2001, 48, 1872–1878. [CrossRef]

- Liu, S.; Titus, J.L.; Boden, M. Effect of Buffer Layer on Single-Event Burnout of Power DMOSFETs. IEEE Trans. Sci. 2007, 54, 2554–2560. [CrossRef]

- 12. Wan, X.; Zhou, W.S.; Ren, S.; Liu, D.G.; Xu, J.; Bo, H.L.; Zhang, E.X.; Schrimpf, R.D.; Fleetwood, D.M.; Ma, T. SEB Hardened Power MOSFETs With High-K Dielectrics. *IEEE Trans. Sci.* **2015**, *62*, 2830–2836. [CrossRef]

- 13. Baliga, B.J. Advanced Power MOSFET Concepts; Springer: New York, NY, USA, 2010; pp. 23-61.

- 14. Grant, D.A.; Gowar, J. *Power MOSFETs: Theory and Applications*, 1st ed.; Wiley-Interscience: New York, NY, USA, 1989.

- 15. Schrimpf, R.; Wahle, P.; Andrews, R.; Cooper, D.; Galloway, K. Dose-rate effects on the total-dose threshold-voltage shift of power MOSFETs. *IEEE Trans. Sci.* **1988**, *35*, 1536–1540. [CrossRef]

- Titus, J.; Wheatley, C.; Van Tyne, K.; Krieg, J.; Burton, D.; Campbell, A. Effect of ion energy upon dielectric breakdown of the capacitor response in vertical power MOSFETs. *IEEE Trans. Sci.* 1998, 45, 2492–2499. [CrossRef]

- Javanainen, A.; Ferlet-Cavrois, V.; Jaatinen, J.; Kettunen, H.; Muschitiello, M.; Pintacuda, F.; Rossi, M.; Schwank, J.R.; Shaneyfelt, M.R.; Virtanen, A. Semi-Empirical Model for SEGR Prediction. *IEEE Trans. Sci.* 2013, 60, 2660–2665. [CrossRef]

- STMicroelectronics. STRH8N10 Datasheets. Available online: https://www.st.com/resource/en/datasheet/ strh8n10.pdf (accessed on 3 May 2019).

- Iakovlev, S.A.; Anashin, V.S.; Chubunov, P.A.; Koziukov, A.E.; Bu-Khasan, K.B.; Maksimenko, T.A.; Chlenov, A.M. MOSFETs SEB & SEGR qualification results with SOA estimation. In Proceedings of the 17th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Geneva, Switzerland, 2–6 October 2017.

- 20. Wheatley, C.; Titus, J.; Burton, D. Single-event gate rupture in vertical power MOSFETs; an original empirical expression. *IEEE Trans. Sci.* **1994**, *41*, 2152–2159. [CrossRef]

- 21. Schwank, J.R.; Shaneyfelt, M.R.; Fleetwood, D.M.; Felix, J.A.; Dodd, P.E.; Paillet, P.; Ferlet-Cavrois, V. Radiation effects in MOS oxides. *IEEE Trans. Nucl. Sci.* **2008**, *55*, 1833–1853. [CrossRef]

- 22. Fleetwood, D.; Meisenheimer, T.; Scofield, J. 1/f noise and radiation effects in MOS devices. *IEEE Trans. Electron Devices* **1994**, *41*, 1953–1964. [CrossRef]

- Rashkeev, S.; Cirba, C.; Fleetwood, D.; Schrimpf, R.; Witczak, S.; Michez, A.; Pantelides, S. Physical model for enhanced interface-trap formation at low dose rates. *IEEE Trans. Sci.* 2002, 49, 2650–2655. [CrossRef]

- Hohl, J.H.; Galloway, K.F. Analytical model for single event burnout of power MOSFETs. *IEEE Trans. Electron Devices* 1994, 41, 1953–1964. [CrossRef]

- 25. Wrobel, T.; Beutler, D. Solutions to heavy ion induced avalanche burnout in power devices. *IEEE Trans. Sci.* **1992**, *39*, 1636–1641. [CrossRef]

- Johnson, G.H.; Palau, J.M.; Dachs, C.; Galloway, K.F.; Schrimpf, R.D. A review of the techniques used for modeling single-event effects in power MOSFET's. *IEEE Trans. Nucl. Sci.* 1996, 43, 546–560. [CrossRef]

- 27. Department of Defense. *MIL-STD-883E, Test Method 1019.4. Ionizing Radiation (Total Dose) Test Procedure;* Defense Supply Center Columbus: Columbus, OH, USA, 1996.

- Department of Defense. MIL-STD-750E, Test Method 1019.5 Steady-State Total Dose Irradiation Procedure; Defense Supply Center Columbus: Columbus, OH, USA, 2006.

- 29. Khosropour, P.; Galloway, K.F.; Zupac, D.; Schrimpf, R.D.; Calvel, P. Application of test method 1019.4 to non-hardened power MOSFETs. *IEEE Trans. Nucl. Sci.* **1994**, *41*, 555–560. [CrossRef]

- 30. Winokur, P.S.; Schwank, J.R.; McWhorter, P.J.; Dressendorfer, P.V.; Turpin, D.C. Correlating the Radiation Response of MOS Capacitors and Transistors. *IEEE Trans. Sci.* **1984**, *31*, 1453–1460. [CrossRef]

- 31. McWhorter, P.J.; Winokur, P.S. Simple technique for separating the effects of interface traps and trapped-oxide charge in metal-oxide-semiconductor transistors. *Appl. Phys. Lett.* **1986**, *48*, 133–135. [CrossRef]

- Zupac, D.; Galloway, K.; Khosropour, P.; Anderson, S.; Schrimpf, R.; Calvel, P. Separation of effects of oxide-trapped charge and interface-trapped charge on mobility in irradiated power MOSFETs. *IEEE Trans. Sci.* 1993, 40, 1307–1315. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

### Article Mechanism of Degradation Rate on the Irradiated Double-Polysilicon Self-Aligned Bipolar Transistor

Mohan Liu<sup>1,2,\*</sup>, Wu Lu<sup>1,\*</sup>, Xin Yu<sup>1,2</sup>, Xin Wang<sup>1</sup>, Xiaolong Li<sup>1</sup>, Shuai Yao<sup>1,2</sup> and Qi Guo<sup>1</sup>

- Key Laboratory of Functional Materials and Devices for Special Environments, Xinjiang Technical Institute of Physics and Chemistry, Chinese Academy of Sciences, Urumqi 830011, China; yuxin@ms.xjb.ac.cn(X.Y.); wangxin210@ms.xjb.ac.cn(X.W.); lixl@ms.xjb.ac.cn (X.L.); yaoshuai15@mails.ucas.edu.cn(S.Y.); guoqi@ms.xjb.ac.cn(Q.G.)

- <sup>2</sup> University of Chinese Academy of Sciences, Beijing 100049, China

- \* Correspondence: liumh@ms.xjb.ac.cn (M.L.); luwu@ms.xjb.ac.cn (W.L.); Tel.: +86-15894697376 (M.L.); +86-13659906670 (W.L.)

Received: 8 April 2019; Accepted: 27 May 2019; Published: 11 June 2019

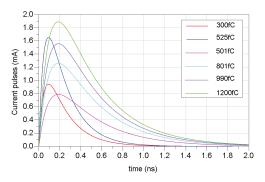

Abstract: The latent enhanced low dose rate sensitivity (ELDRS) effect is observed in the double-polysilicon self-aligned (DPSA) technology PNP bipolar junction transistor (BJT) irradiated with a high and low dose rate gamma ray, which is discussed from the perspective of the three-stage degradation rate of the excess base current. The great degradation rate as a result of the high dose irradiation of the first stage is dominantly ascribed to the positive oxide trap charges accumulated during a short irradiation, and then due to the competition between the recombination of electrons and capture of the hole by the traps. It declined sharply into a degradation rate saturated region of the second stage. However, for the low dose rate, the small increase in the degradation rate in the first stage is caused by the holes escaping from the initial recombination and being transported to the interface to form the interface states. Then, the competition between the steadily increasing interfacial trap charge and the continuously annealed shallow level oxide trap charge leads to the stable increase of degradation under low dose irradiation. Finally, in stage three, the increases of the degradation rates for high and low dose irradiation result from the different amounts of the hydrogen molecules generated by the hole reactive with depassiviated Si suspended bonds, which can interact with the deep level defects and release protons, causing an increase of interfacial trap charges with prolonged irradiation.

Keywords: saturation effect; gain degradation; total ionizing dose; gamma ray; bipolar transistor

#### 1. Introduction

As a state-of-the-art high speed bipolar complementary process, double-polysilicon self-aligned (DPSA) technology has been widely used in high-speed analog integrated circuits. Compared with the traditional bipolar junction transistors (BJTs), DPSA BJTs have a smaller linewidth due to the isolation of local oxidation of silicon (LOCOS) combined with deep trench isolation (DTI). The use of polysilicon emitters can increase the current gain so that the device can achieve vertical scale down without reducing the punch-through voltage of the emitter-collector junction and the loss of the current gain [1–3]. The self-aligning structure and DTI can realize the lateral scale down of the device, greatly reduce the area of the device, the circuit, and the corresponding parasitic capacitance, significantly reduce the power consumption delay product of the circuit, and improve the integration level of the bipolar circuit [4,5]. Therefore, the high performance and speed of the analog integrated circuit made by this technology have wide application prospects in space RF(radio frequency)/microwave communication and other extreme environments [6].

The previous total dose irradiation test results in the literature [6,7] have shown that the direct current gain is the most sensitive parameter of the bipolar device under total ionizing dose radiation,

and most of the devices and circuits fabricated by bipolar technology suffer from the so-called enhanced low dose rate sensitivity (ELDRS) effect. For decades, most of the total ionizing dose research was focused on the radiation response and the damage mechanism of the traditional bipolar technology; only a few reports were related to the DPSA technology. In 1999, Flamen et.al presented research about the radiation tolerance on quasi-self aligned (QSA) single polysilicon emitter bipolar technology. The experimental results have shown that this bipolar technology is superior to traditional bipolar technology in structure and related function, and that is has a good tolerance of the radiation without adding special manufacturing steps [8]. Graves investigated the radiation and hot-carrier stress response on polysilicon emitter NPN BJTs fabricated in a bipolar-complementary-metal-oxide-semiconductor (BiCMOS) process [9]. More recently, Zhang et al. presented the radiation response on the DPSA NPN BJTs with Si and silicon-on-insulator (SOI) substrate at high and low injection levels [10–14]. However, all of the above research was focused on the preliminary total ionizing dose response on the NPN BJTs. Studies on the dose rate response and the degradation rate of the electrical parameters are still not enough to apply it to real space applications. Thus, in this paper, the dose rate response on the DPSA BJT has been investigated under high and low dose rate gamma ray irradiation and a preliminary analysis of the radiation effect and the damage mechanism is made from the perspective of the degradation rate of the excess base current.

Based on the understanding of the comprehensive research on the radiation damage effect of bipolar transistors, the current gain degradation saturation phenomenon and generation mechanism of the devices at the total dose of 100 krad (Si) were investigated by using a bipolar transistor which is very resistant to total ionizing dose radiation. Section 2 of the paper introduces the devices and the methods used in the experiments. Detailed experimental results are presented in Section 3. Section 4 explains the experimental results and discusses their effects on practical future space applications. Finally, Section 5 concludes the article.

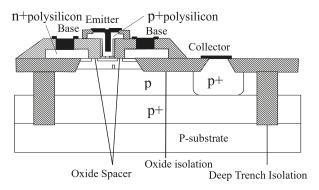

#### 2. Experimental Devices and Methods

DPSA PNP BJTs studied in this paper adopted a standard bipolar process with the trench isolation technology and the cross-section of the device being depicted in Figure 1. The devices presented here were irradiated with a <sup>60</sup>Co gamma ray at the Xinjiang Technical Institute of Physics & Chemistry of Chinese, Academy of Sciences. The devices were exposed at the high and low dose rate of 50 rad (Si)/s and 0.05 rad (Si)/s with a reverse emitter-base bias voltage, which is usually recognized as the worst operation condition [6]. The electrical parameters were measured by the KEITHLEY 4200-SCS semiconductor parameter analyzer by removing the devices under test from the irradiation chamber within 20 minutes before and after the dose accumulated to about 100 krad (Si) at room temperature.

Figure 1. The cross-section of theDPSA BJT.

#### 3. Experimental Results

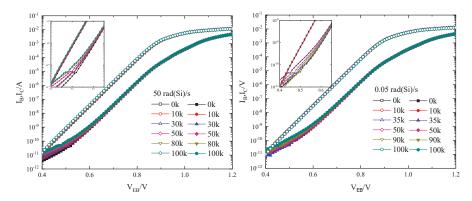

Figure 2 shows the changes in the Gummel curve of the experimental samples with the cumulative total dose before and after irradiation at dose rates of 50 rad (Si)/s and 0.05 rad (Si)/s to 100 krad (Si). As the dose accumulated, the collector current did not change significantly, while the base current increased slightly when biased at the emitter-base voltage lower than  $V_{EB} = 0.7$  V. However, the base current of the irradiated transistor is mainly composed of the initial current and the surface compound current. The oxide trap positive charge and the interface trap charge generated by the irradiation increases the surface recombination rate [7], so the increase of the surface recombination current leads to an increase of the base current, which then induced a declination of the current gain which is defined as the ratio of the collector current and the base current ( $\beta = I_C/I_B$ ).

**Figure 2.** Gummel characteristics of a DPSA BJT before and after irradiation at the dose rate of 50 rad (Si)/s and 0.05 rad (Si)/s.  $V_{EB}$  = emitter-base voltage;  $I_{C}$  = collector current;  $I_{B}$  = base current.

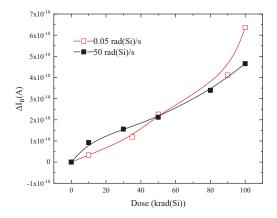

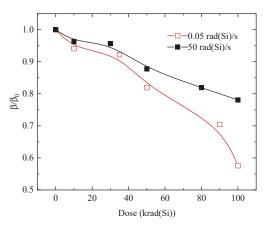

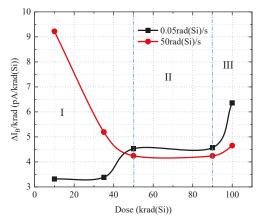

For comparison of the degradation level of the base current and the current gain under different dose rates, the excess base current  $\Delta I_B$  ( $\Delta I_B = I_B - I_{B0}$ ) and normalized current gain  $\beta/\beta_0$ , are introduced in the characterization analysis as shown in Figures 3 and 4, where  $I_{B0}$ ,  $\beta_0$ ,  $I_B$  and  $\beta$  are the base current and current gain before and after irradiation corresponding to  $V_{EB} = 0.6$  V, respectively. It can be seen in Figure 3 that when  $V_{EB} = 0.6 \text{ V}$ ,  $\Delta I_B$  is increasing continuously with the accumulating total dose. When the irradiation dose increases up to 100 krad (Si), the base current IB increases by a value of 465 pA ( $\Delta I_B$  = 465 pA) for the high dose irradiation, while the increment of  $\Delta I_B$  is about 636 pA for the low dose rate, which is greater than the degradation under the high dose rate. Therefore, this PNP BJT fabricated with the DPSA technology may suffer from the ELDRS effect in the real and lower dose rate space irradiation environment, although the total degradation of the base current is slight. What is notable in Figure 3 is that the decrease of the base current under the high dose rate is above that irradiated with the low dose rate before the total dose reached 50 krad (Si). Moreover, for the first 50 krad (Si) irradiation, the increasing rate of  $\Delta I_B$  at the high dose rate is more rapid than irradiating at a low dose rate. It also shows the opposite increasing trend above the 50 krad (Si). For the final 10 krad (Si), the increasing speed of  $\Delta I_B$  soars up under the low dose rate and creates a relatively big gap between the high and low dose rate. These phenomena prove that the amounts of the interface trap charges in the Si/SiO<sub>2</sub> interface dominate the attenuation of the base current under the long irradiation with a low dose rate condition [7].

Figure 3. The excess base current of DPSA BJTs irradiated at a dose rate of 50 rad (Si)/s and 0.05 rad (Si)/s for PNP.

Figure 4. The normalized current gain of a DPSA BJT irradiated at the dose rate of 50 rad (Si)/s and 0.05 rad (Si)/s for PNP.

As the base current increases after irradiation, while the collector current remains basically unchanged, the degradation of the normalized current gain is finally shown in Figure 4. It can be seen clearly from the Figure that with the increase of the accumulated total dose, the current gains of the PNP BJTs all decrease rapidly. However, the declination rates are different between the high and low dose rate and consistent with the  $\Delta I_B$  depicted in Figure 3. The gain after high and low dose rate irradiation is reduced to 57.6% and 78% of the initial value, respectively. The results also show that the damage of the current gain under low dose rate irradiation is greater than that under a high dose rate, and will hence result in a potential ELDRS effect.

#### 4. Discussion

Figure 5 plots the degradation curve of the excess base current per unit krad (Si) irradiation dose of the DPSA BJTs to explain the radiation response processes mentioned above. Obviously, the degradation rate of the base current can be divided into three stages all through the irradiation process. For the beginning of the first stage, the degradation of the base current up to 10 pA per unit krad (Si) when the dose is accumulated to the first 10 krad (Si) at the high dose rate, and then with the total dose increases to 50 krad (Si), the degradation rate of the base current gradually descends and stabilizes