# Signal Processing and Analysis of Electrical Circuit

### Edited by

Adam Glowacz, Grzegorz Królczyk and Jose Alfonso Antonino Daviu Printed Edition of the Special Issue Published in *Electronics*

www.mdpi.com/journal/electronics

# **Signal Processing and Analysis of Electrical Circuit**

# **Signal Processing and Analysis of Electrical Circuit**

Special Issue Editors

Adam Glowacz Grzegorz Królczyk Jose Alfonso Antonino Daviu

$\mathsf{MDPI} \bullet \mathsf{Basel} \bullet \mathsf{Beijing} \bullet \mathsf{Wuhan} \bullet \mathsf{Barcelona} \bullet \mathsf{Belgrade} \bullet \mathsf{Manchester} \bullet \mathsf{Tokyo} \bullet \mathsf{Cluj} \bullet \mathsf{Tianjin}$

| Special Issue Editors         |                                |                             |

|-------------------------------|--------------------------------|-----------------------------|

| Adam Glowacz                  | Grzegorz Królczyk              | Jose Alfonso Antonino Daviu |

| AGH University of Science and | Opole University of Technology | Universitat de València     |

| Technology                    | Poland                         | Spain                       |

| Poland                        |                                |                             |

*Editorial Office* MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Electronics* (ISSN 2079-9292) (available at: https://www.mdpi.com/journal/electronics/special\_issues/signal\_circuit).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, Article Number, Page Range.

ISBN 978-3-03928-294-4 (Pbk) ISBN 978-3-03928-295-1 (PDF)

© 2020 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

# Contents

| About the Special Issue Editors ix                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Adam Glowacz and Jose Alfonso Antonino Daviu<br>Signal Processing and Analysis of Electrical Circuit                                                              |

| Reprinted from: <i>Electronics</i> <b>2020</b> , <i>9</i> , 17, doi:10.3390/electronics9010017                                                                    |

| <b>Khaoula Ait Belaid, Hassan Belahrach and Hassan Ayad</b><br>Numerical Laplace Inversion Method for Through-Silicon Via (TSV) Noise Coupling in 3D-IC<br>Design |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 1010, doi:10.3390/electronics8091010                                                                  |

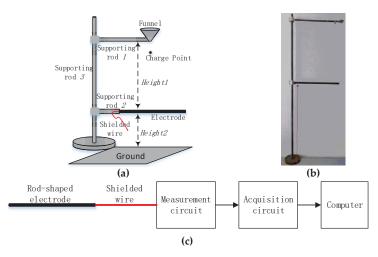

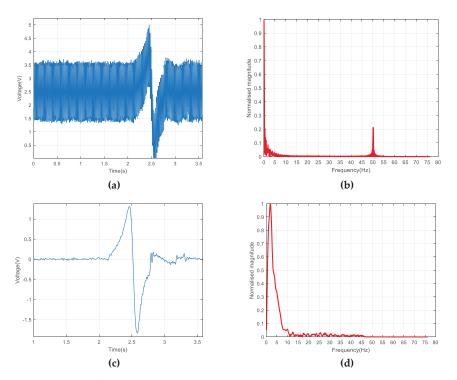

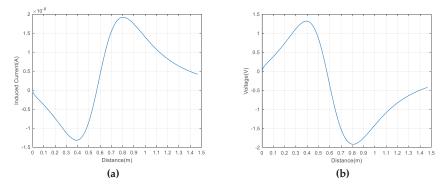

| Jiming Li, Jingyu Li, Xuezhen Cheng and Guojin Feng                                                                                                               |

| Investigation of Induced Charge Mechanism on a Rod Electrode                                                                                                      |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 977, doi:10.3390/electronics8090977 <b>27</b>                                                         |

| Jianhong Xiang, Pengfei Ye, Linyu Wang and Mingqi He                                                                                                              |

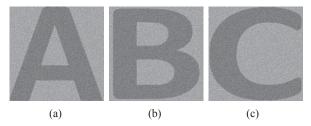

| A Novel Image-Restoration Method Based on High-Order Total Variation Regularization Term                                                                          |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 867, doi:10.3390/electronics8080867                                                                   |

| Ching-Nung Yang, Qin-Dong Sun, Yan-Xiao Liu and Ci-Ming Wu                                                                                                        |

| A n-out-of-n Sharing Digital Image Scheme by Using Color Palette                                                                                                  |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 802, doi:10.3390/electronics8070802                                                                   |

| Jincheng Liu, Jiguang Yue, Li Wang, Chenhao Wu and Feng Lyu                                                                                                       |

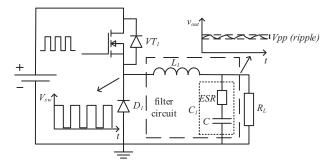

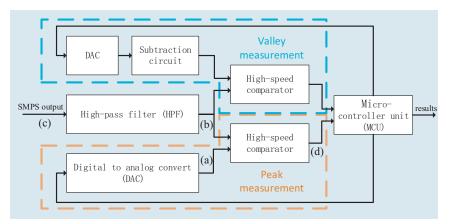

| A Low-Cost, High-Precision Method for Ripple Voltage Measurement Using a DAC and                                                                                  |

| Comparators                                                                                                                                                       |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 586, doi:10.3390/electronics8050586                                                                   |

| Meishan Guo and Zhong Wu                                                                                                                                          |

| Noise Reduction for High-Accuracy Automatic Calibration of Resolver Signals via DWT-SVD<br>Based Filter                                                           |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 516, doi:10.3390/electronics8050516                                                                   |

| Yuzhong Li, Wenming Tang and Guixiong Liud                                                                                                                        |

| HPEFT for Hierarchical Heterogeneous Multi-DAG in a Multigroup Scan UPA System                                                                                    |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 498, doi:10.3390/electronics8050498                                                                   |

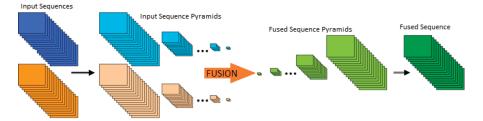

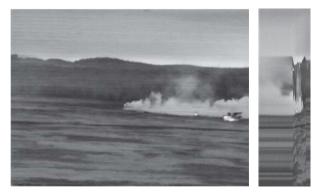

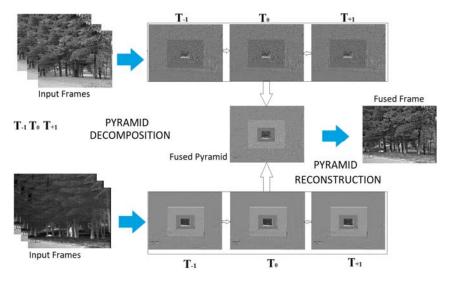

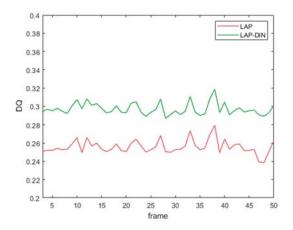

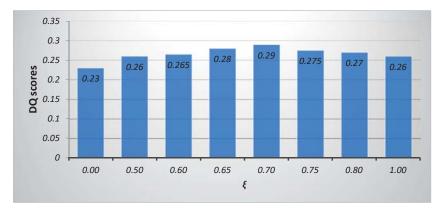

| Rade Pavlović and Vladimir Petrović                                                                                                                               |

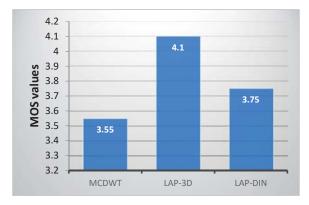

| Rolling 3D Laplacian Pyramid Video Fusion                                                                                                                         |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 447, doi:10.3390/electronics8040447                                                                   |

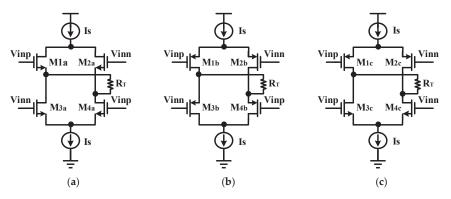

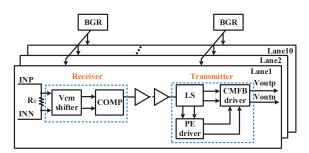

| Xu Bai, Jianzhong Zhao, Shi Zuo and Yumei Zhou                                                                                                                    |

| A 2.5 Gbps, 10-Lane, Low-Power, LVDS Transceiver in 28 nm CMOS Technology                                                                                         |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 350, doi:10.3390/electronics8030350                                                                   |

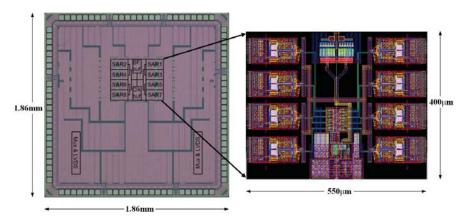

| Dong Wang, Xiaoge Zhu, Xuan Guo, Jian Luan, Lei Zhou, Danyu Wu, Huasen Liu, Jin Wu                                                                                |

| and Xinyu Liu<br>A 2.6 GS/s 8-Bit Time-Interleaved SAR ADC in 55 nm CMOS Technology                                                                               |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 305, doi:10.3390/electronics8030305                                                                   |

|                                                                                                                                                                   |

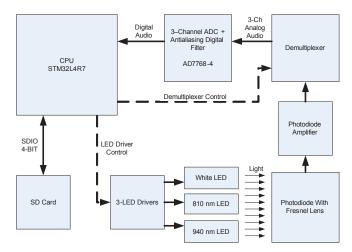

| Iraklis Rigakis, Ilyas Potamitis, Nicolaos-Alexandros Tatlas, Ioannis Livadaras and<br>Stavros Ntalampiras<br>A Multispectral Backscattered Light Recorder of Insects' Wingbeats      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 277, doi:10.3390/electronics8030277                                                                                       |

| Emmanuel Gómez-Ramírez, L. A. Maeda-Nunez, Luis C. Álvarez-Simón<br>and F. G. Flores-García                                                                                           |

| A Highly Robust Interface Circuit for Resistive Sensors                                                                                                                               |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 263, doi:10.3390/electronics8030263                                                                                       |

| Hyungyu Ju and Minjae Lee                                                                                                                                                             |

| A 13-bit 3-MS/s Asynchronous SAR ADC with a Passive Resistor Based Loop Delay Circuit Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 262, doi:10.3390/electronics8030262 |

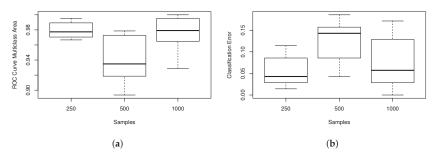

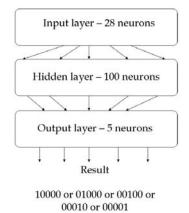

| Diana-Carolina Toledo-Pérez, Miguel-Angel Martínez-Prado, Juvenal Rodríguez-Reséndiz,<br>Roberto-Augusto Gómez-Loenzo and Wilfrido-Jacobo Paredes-García                              |

| A Study of Movement Classification of the Lower Limb Based on up to 4-EMG Channels                                                                                                    |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 259, doi:10.3390/electronics8030259                                                                                       |

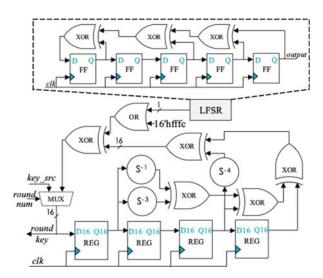

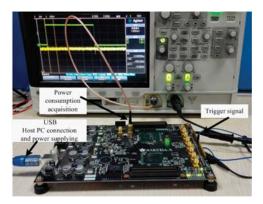

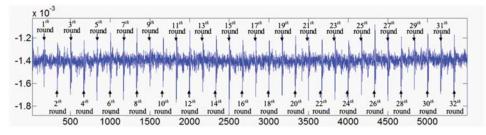

| Yuanyuan Zhang, Ning Wu, Fang Zhou, Jinbao Zhang and Muhammad Rehan Yahya                                                                                                             |

| A Countermeasure against DPA on SIMON with an Area-Efficient Structure                                                                                                                |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 240, doi:10.3390/electronics8020240                                                                                       |

| Tianzhu Qin, Bin Ba and Daming Wang                                                                                                                                                   |

| Performance Analysis of Single-Step Localization Method Based on Matrix Eigen-Perturbation                                                                                            |

| Theory with System Errors<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 235, doi:10.3390/electronics8020235 <b>259</b>                                               |

|                                                                                                                                                                                       |

| Liquan Zhao, Yunfeng Hu and Yulong Liu                                                                                                                                                |

| Stochastic Gradient Matching Pursuit Algorithm Based on Sparse Estimation<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 165, doi:10.3390/electronics8020165          |

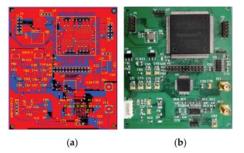

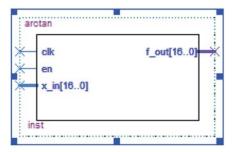

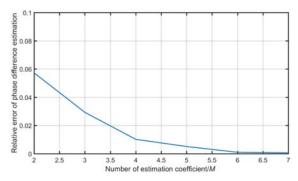

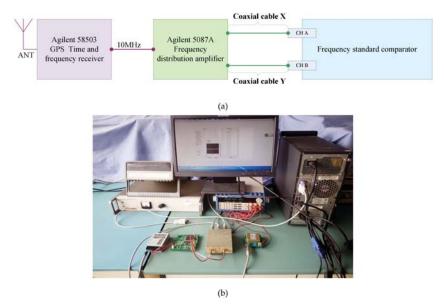

| Sheng Tang, Jing Ke, Tianxiang Wang and Zhouhu Deng                                                                                                                                   |

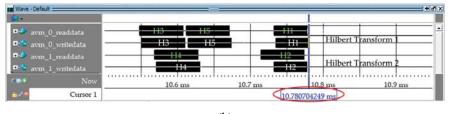

| Development of a Miniaturized Frequency Standard Comparator Based on FPGA                                                                                                             |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 123, doi:10.3390/electronics8020123                                                                                       |

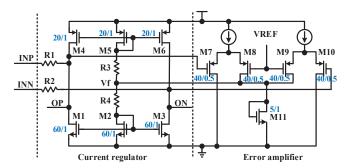

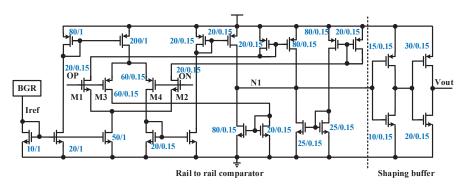

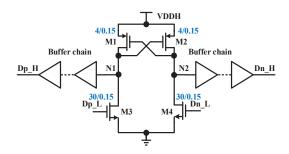

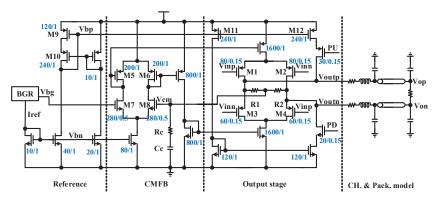

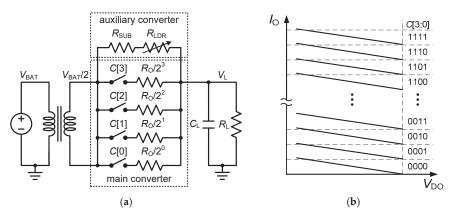

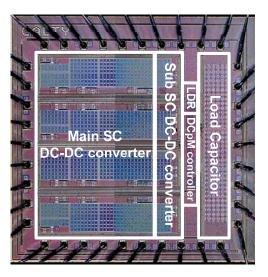

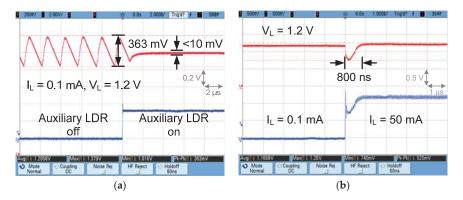

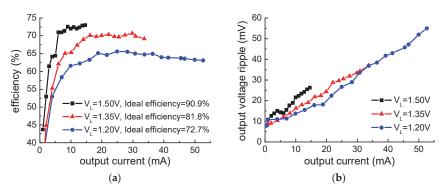

| <b>Jeong-Yun Lee, Gwang-Sub Kim, Kwang-II Oh and Donghyun Baek</b><br>Fully Integrated Low-Ripple Switched-Capacitor DC–DC Converter with Parallel Low-Dropout                        |

| Regulator<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 98, doi:/10.3390/electronics8010098                                                                          |

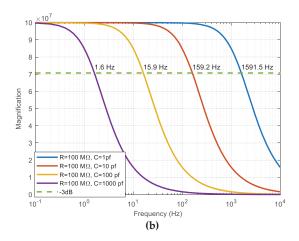

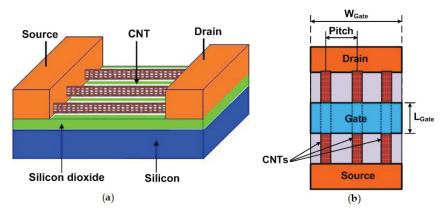

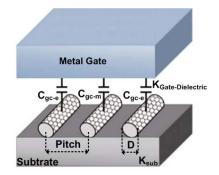

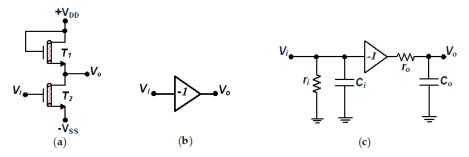

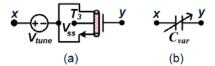

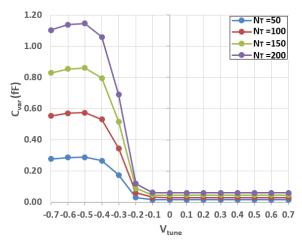

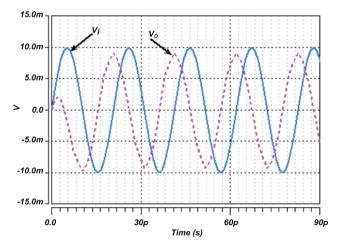

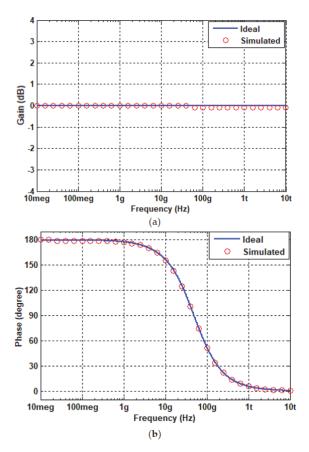

| Muhammad Masud, Abu A'ain, Iqbal Khan and Nasir Husin<br>Design of Voltage Mode Electronically Tunable First Order All Pass Filter in $\pm 0.7$ V 16 nm                               |

| CNFET Technology<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 95, doi:10.3390/electronics8010095                                                                    |

|                                                                                                                                                                                       |

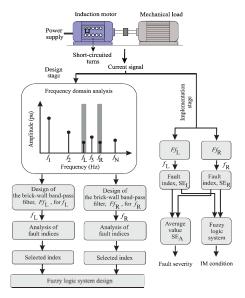

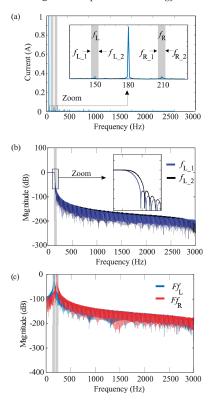

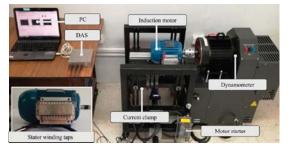

| Arturo Mejia-Barron, J. Jesus de Santiago-Perez, David Granados-Lieberman,<br>Juan P. Amezquita-Sanchez and Martin Valtierra-Rodriguez                                                |

| Shannon Entropy Index and a Fuzzy Logic System for the Assessment of Stator Winding Short-Circuit Faults in Induction Motors                                                          |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 90, doi:10.3390/electronics8010090                                                                                        |

| <b>Andrea De Marcellis, Càndid Reig and María-Dolores Cubells-Beltrán</b><br>A Capacitance-to-Time Converter-Based Electronic Interface for Differential Capacitive Sensors           |

| Yuxing Li, Xiao Chen, Jing Yu and Xiaohui Yang<br>A Fusion Frequency Feature Extraction Method for Underwater Acoustic Signal Based on<br>Variational Mode Decomposition, Duffing Chaotic Oscillator and a Kind of Permutation<br>Entropy                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 61, doi:10.3390/electronics8010061                                                                                                                                                                                            |

| Nicola Testoni, Federica Zonzini, Alessandro Marzani, Valentina Scarponi and<br>Luca De Marchi                                                                                                                                                                                            |

| A Tilt Sensor Node Embedding a Data-Fusion Algorithm for Vibration-Based SHM<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 45, doi:10.3390/electronics8010045                                                                                                            |

| Rendong Wang, Youchun Xu, Miguel Angel Sotelo, Yulin Ma, Thompson Sarkodie-Gyan,<br>Zhixiong Li and Weihua Li                                                                                                                                                                             |

| A Robust Registration Method for Autonomous Driving Pose Estimation in Urban Dynamic<br>Environment Using LiDAR<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 43, doi:10.3390/electronics8010043 <b>419</b>                                                              |

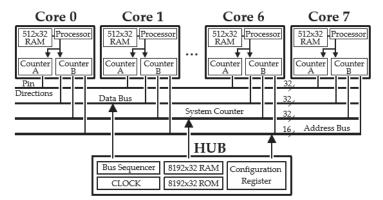

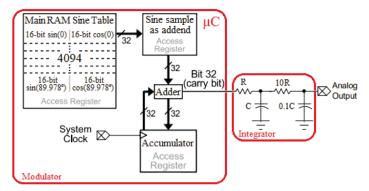

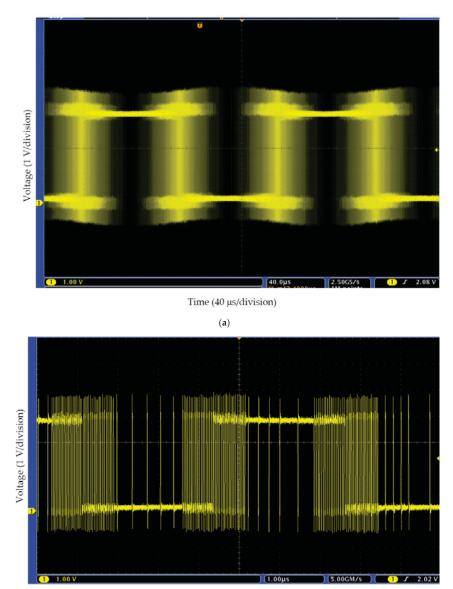

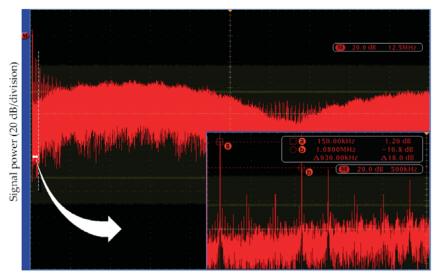

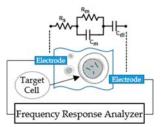

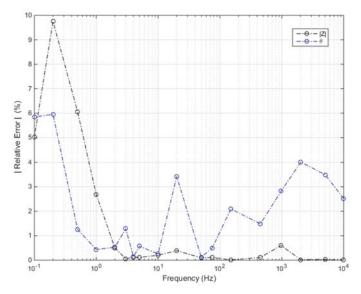

| Arturo Sanchez-Gonzalez, Nicolas Medrano, Belen Calvo and Pedro A. Martinez                                                                                                                                                                                                               |

| A Multichannel FRA-Based Impedance Spectrometry Analyzer Based on a Low-Cost Multicore<br>Microcontroller                                                                                                                                                                                 |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 38, doi:10.3390/electronics8010038                                                                                                                                                                                            |

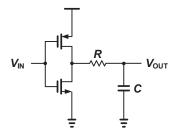

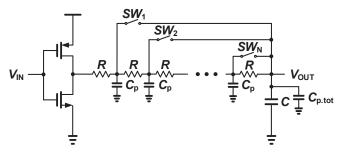

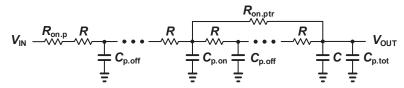

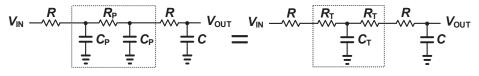

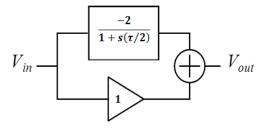

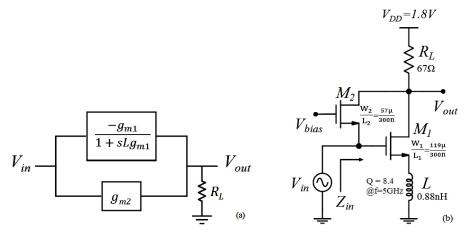

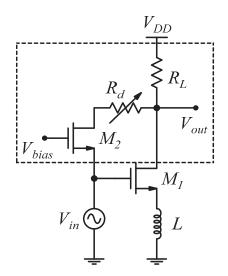

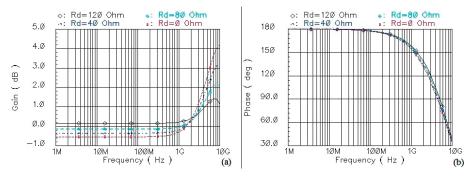

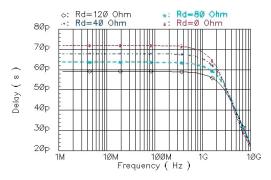

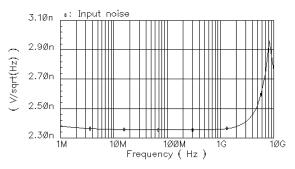

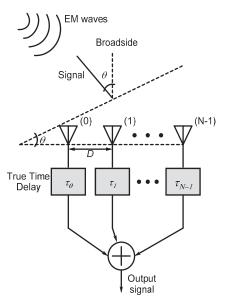

| Seyed Rasoul Aghazadeh, Herminio Martinez and Alireza Saberkari5GHz CMOS All-Pass Filter-Based True Time Delay CellReprinted from: Electronics 2019, 8, 16, doi:10.3390/electronics8010016                                                                                                |

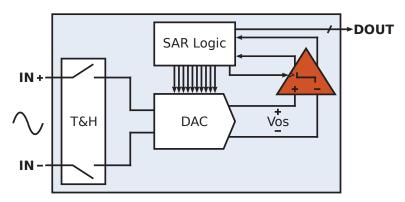

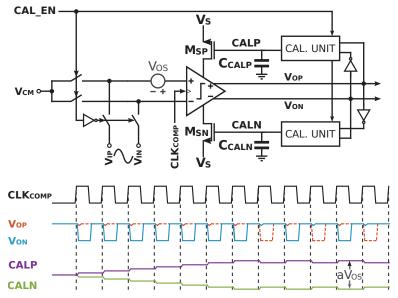

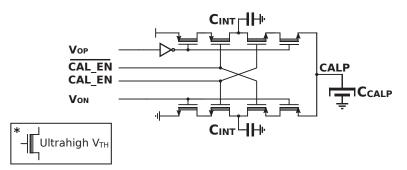

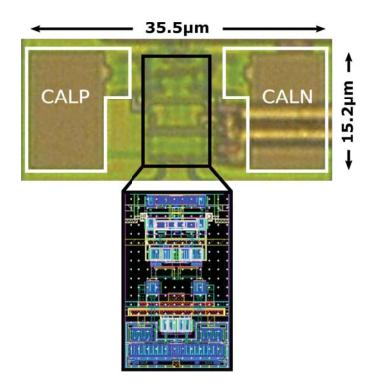

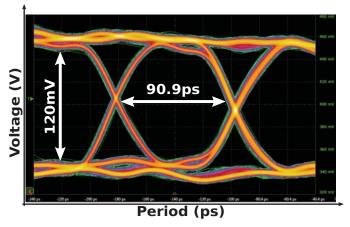

| Athanasios Ramkaj, Maarten Strackx, Michiel Steyaert and Filip Tavernier<br>An 11 GHz Dual-Sided Self-Calibrating Dynamic Comparator in 28 nm CMOS<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 13, doi:10.3390/electronics8010013                                      |

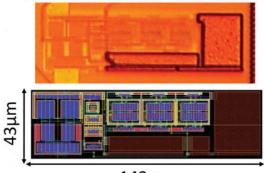

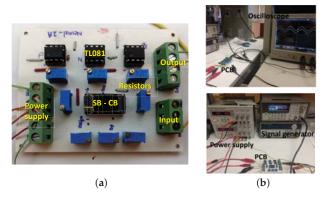

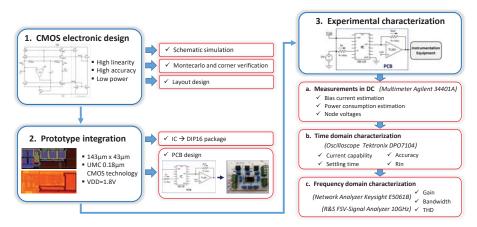

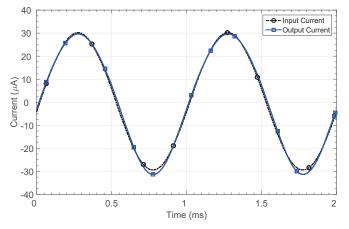

| Javier Alejandro Martínez-Nieto, María Teresa Sanz-Pascual, Nicolás Medrano-Marqués,<br>Belén Calvo-López and Arturo Sarmiento-Reyes<br>High-Linearity Self-Biased CMOS Current Buffer<br>Reprinted from: <i>Electronics</i> <b>2018</b> , <i>7</i> , 423, doi:10.3390/electronics7120423 |

| Huan Liu and Zhong Wu                                                                                                                                                                                                                                                                     |

| Demodulation of Angular Position and Velocity from Resolver Signals via Chebyshev<br>Filter-Based Type III Phase Locked Loop                                                                                                                                                              |

| Reprinted from: <i>Electronics</i> <b>2018</b> , 7, 354, doi:10.3390/electronics7120354                                                                                                                                                                                                   |

| Yuqing Hou, Changlong Li and Sheng Tang<br>An Accurate DDS Method Using Compound Frequency Tuning Word and Its FPGA<br>Implementation                                                                                                                                                     |

| Reprinted from: <i>Electronics</i> <b>2018</b> , <i>7</i> , 330, doi:10.3390/electronics7110330                                                                                                                                                                                           |

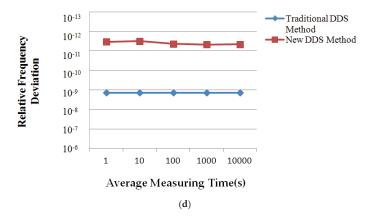

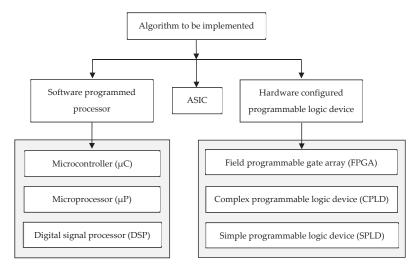

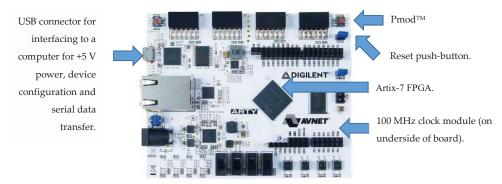

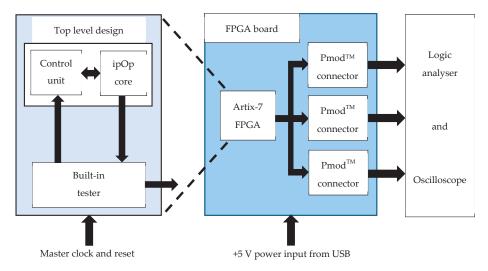

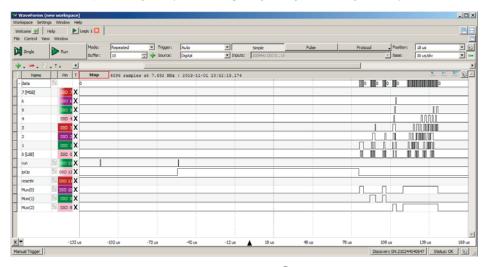

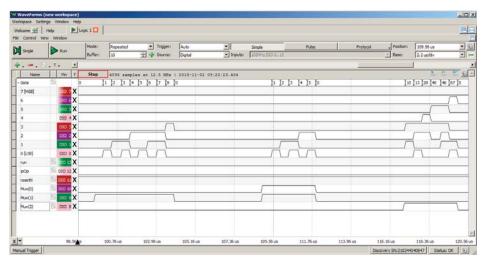

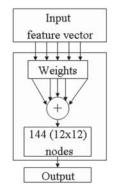

| Ian Grout and Lenore Mullin<br>Hardware Considerations for Tensor Implementation and Analysis Using the Field                                                                                                                                                                             |

| Programmable Gate Array<br>Reprinted from: <i>Electronics</i> <b>2018</b> , <i>7</i> , 320, doi:10.3390/electronics7110320                                                                                                                                                                |

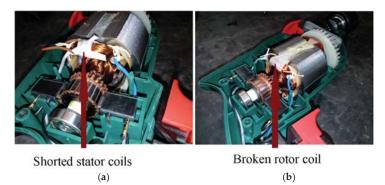

| Adam Glowacz                                                                                                                                                                                                                                                                              |

| Acoustic-Based Fault Diagnosis of Commutator Motor<br>Reprinted from: <i>Electronics</i> <b>2018</b> , <i>7</i> , 299, doi:10.3390/electronics7110299                                                                                                                                     |

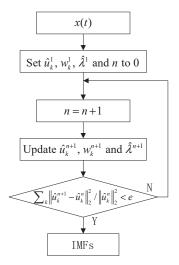

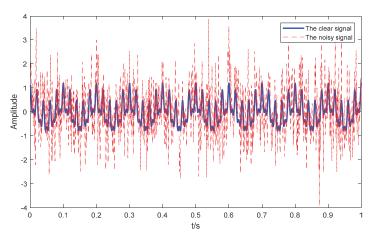

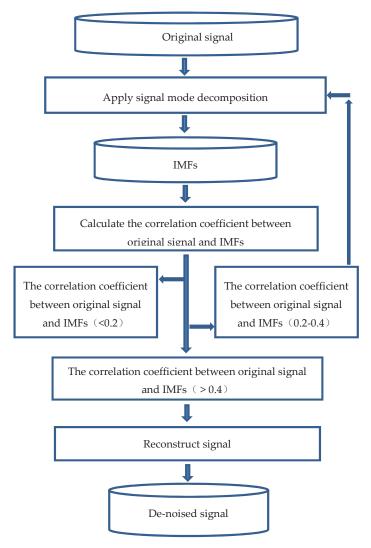

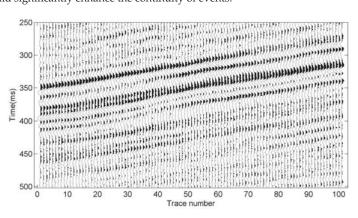

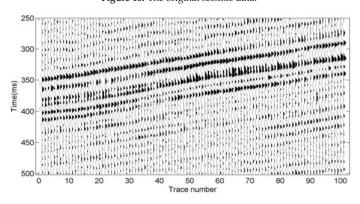

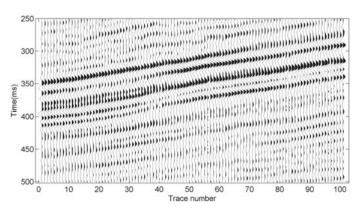

#### Yaping Huang, Hanyong Bao and Xuemei Qi

| Seismic Random Noise Attenuation Method Based on Variational Mode Decompositio                  | n and |   |

|-------------------------------------------------------------------------------------------------|-------|---|

| Correlation Coefficients                                                                        |       |   |

| Reprinted from: <i>Electronics</i> <b>2018</b> , <i>7</i> , 280, doi:10.3390/electronics7110280 | 57    | 9 |

# **About the Special Issue Editors**

Adam Glowacz received his Ph.D. in Computer Science from the AGH University of Science and Technology, Cracow, Poland, in 2013. Adam Glowacz is the author/coauthor of 106 scientific papers (58 papers indexed by Web of Science) that correspond to a h-index of 21 and 1026 citations in Web of Science and a h-index of 23 and 1407 citations in Google Scholar. He has supervised 30 B.Sc. and 12 M.Sc. theses. Adam Glowacz is an Associate Editor of Symmetry, Electronics, Measurement, and Advances in Mechanical Engineering and has also authored 300 scientific reviews.

**Grzegorz Krolczyk** is Professor and Vice-Rector for Research and Development at Opole University of Technology and uuthor and coauthor of 180 scientific publications (100 JCR papers), as well as around 30 studies and industrial applications. His main scientific activities are in the analysis and improvement of manufacturing processes, surface metrology, and surface engineering. His research focuses on sustainable manufacturing as a tool for the practical implementation of the concept of social responsibility in the area of machining. Grzegorz Krolczykis is a member of several scientific organizations, including an expert in the Section of Technology of the Committee on Machine Building of the Polish Academy of Sciences. In addition, he is a member of several editorial committees of scientific journals. He has participated in advisory and opinion-forming bodies, including the advisory team of the Minister of Science and Higher Education. The coauthor of two patent applications, Grzegorz Krolczyk has been awarded on numerous occasions for his scientific activities in Poland and around the world.

Jose A. Antonino-Daviu received his M.Sc. and Ph.D. degrees in Electrical Engineering, both from the Universitat Politècnica de València, Valencia, Spain, in 2000 and 2006, respectively. He has worked for IBM, where he was involved in several international projects. He is currently Full Professor in the Department of Electrical Engineering, Universitat Politècnica de València. He was an Invited Professor at Helsinki University of Technology, Finland, in 2005 and 2007; Michigan State University, USA, in 2010; Korea University, South Korea, in 2014; Université Claude Bernard Lyon 1, France; and Coventry University, U.K., in 2016. He is a coauthor of more than 200 papers published in technical journals and conference proceedings and one international patent. Dr. Antonino-Daviu is Associate Editor of IEEE Transactions on Industrial Informatics, IEEE Industrial Electronics Magazine, and IEEE Journal of Emerging and Selected Topics in Industrial Electronics. He received the IEEE Second Prize Paper Award from the Electric Machines Committee of the IEEE Industry Applications Society (2013). He also received the Best Paper Award in the conferences IEEE ICEM 2012, IEEE SDEMPED 2011, and IEEE SDEMPED 2019 and "Highly Commended Recognition" of the IET Innovation Awards in 2014 and in 2016. He was the General Co-Chair of SDEMPED 2013 and is a member of the Steering Committee of IEEE SDEMPED. In 2016, he received the Medal of the Spanish Royal Academy of Engineering (Madrid, Spain) for his contributions in new techniques for predictive maintenance of electric motors. In 2018, he was awarded the prestigious 'Nagamori Award' from the Nagamori Foundation (Kyoto, Japan). In 2019, he received the SDEMPED Diagnostic Achievement Award (Toulouse, France) for his contributions to advanced diagnosis of electric motors.

## **Editorial Signal Processing and Analysis of Electrical Circuit**

#### Adam Glowacz <sup>1,\*</sup> and Jose Alfonso Antonino Daviu <sup>2</sup>

- <sup>1</sup> Department of Automatic Control and Robotics, Faculty of Electrical Engineering, Automatics, Computer Science and Biomedical Engineering, AGH University of Science and Technology, al. A. Mickiewicza 30, 30-059 Kraków, Poland

- <sup>2</sup> Instituto Tecnológico de la Energía, Universitat Politècnica de València (UPV), Camino de Vera s/n, 46022 Valencia, Spain; joanda@die.upv.es

- \* Correspondence: adglow@agh.edu.pl

Received: 16 December 2019; Accepted: 20 December 2019; Published: 23 December 2019

#### 1. Introduction

The analysis of electrical circuits is an essential task in the evaluation of electrical systems. Electrical circuits are made up of interconnections of various elements, such as resistors, inductors, transformers, capacitors, semiconductor diodes, transistors and operational amplifiers. Electrical signals, acoustic and vibrations carry useful information. They are known as diagnostic signals. Electrical circuits are used for equipment, circuit protection, circuit control, computers, electronics, electrical engineering, cars, planes and trains.

The analysis of signals is also essential. It is used for electrical engineering, sound recognition, speaker recognition, fault diagnosis, image processing, fast Fourier transform (FFT), wireless communication, control systems, process control, genomics, economy, seismology, feature extraction and digital filtering.

#### 2. The Present Special Issue

This special issue with 34 published articles shows the significance of the topic "Signal Processing and Analysis of Electrical Circuit". The topic gained noticeable attention in recent time. The accepted articles are categorized into four different areas:

Signal processing and analysis methods of electrical circuits;

Electrical measurement technology;

- Applications of signal processing of electrical equipment;

- Fault diagnosis of electrical circuits;

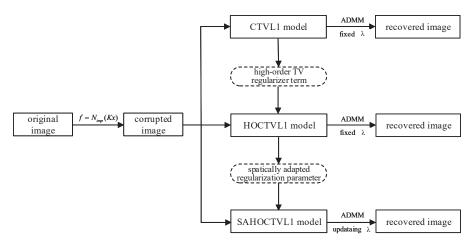

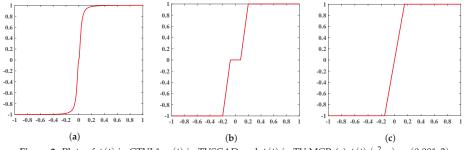

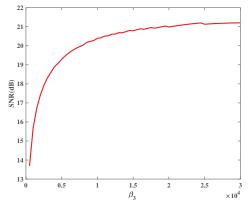

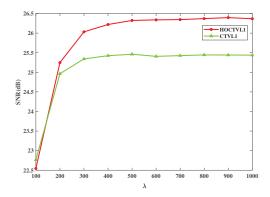

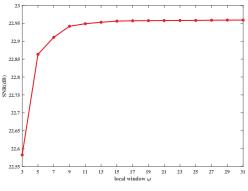

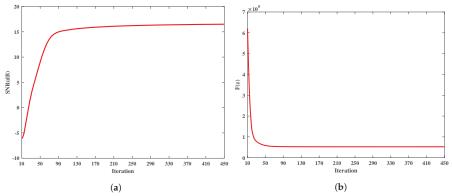

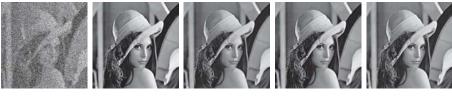

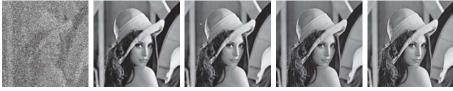

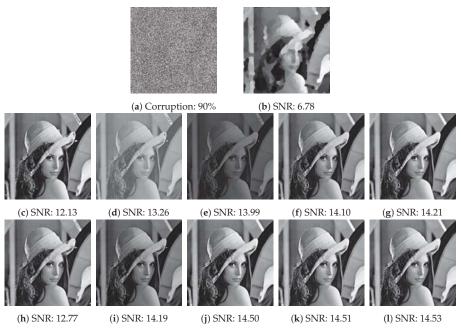

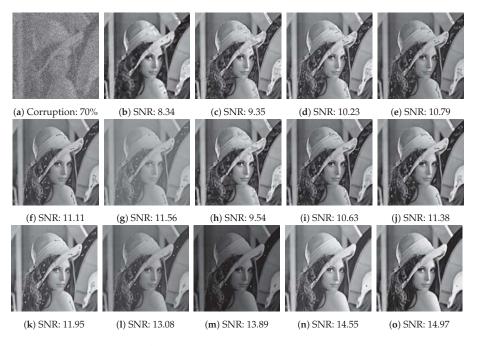

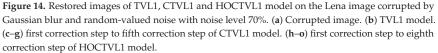

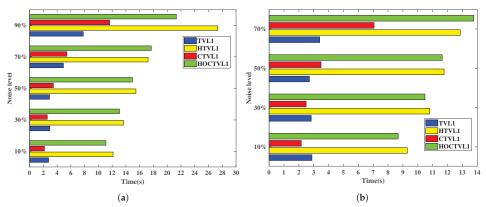

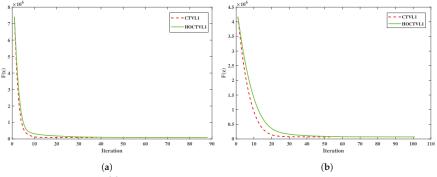

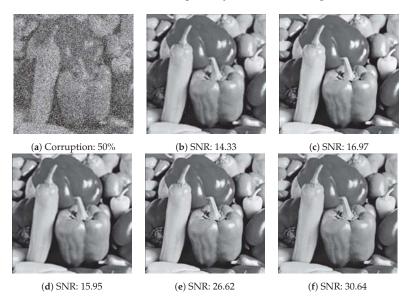

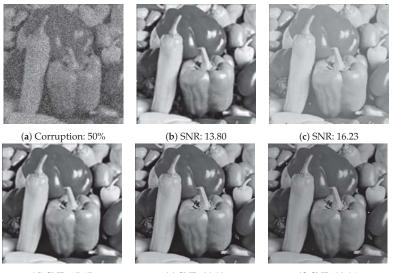

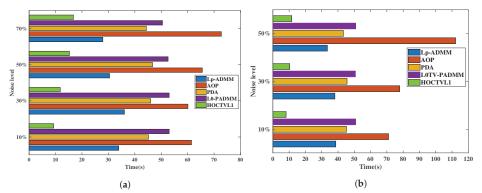

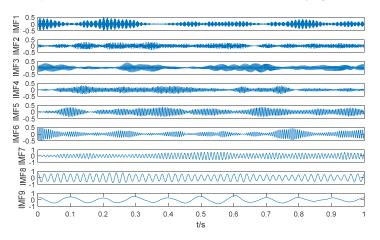

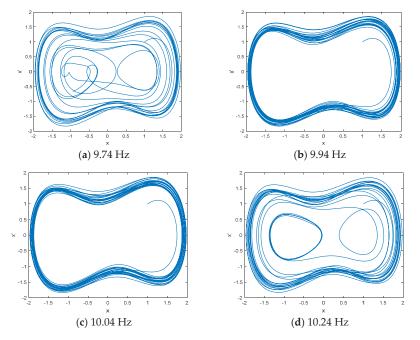

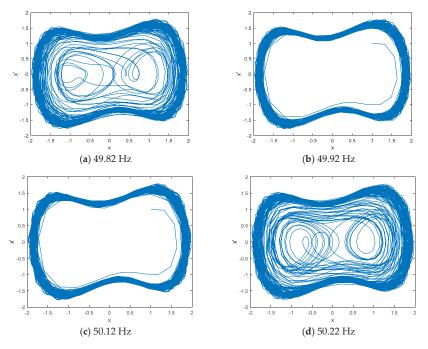

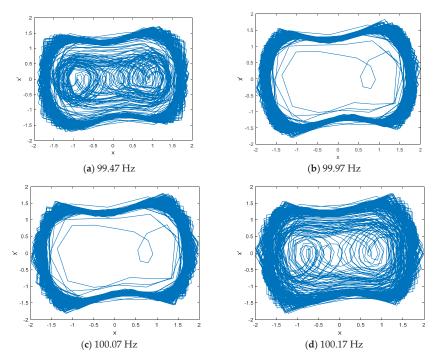

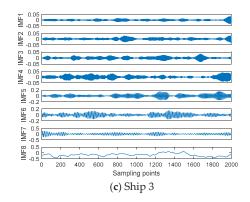

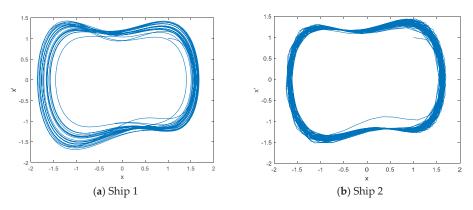

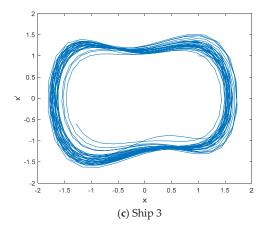

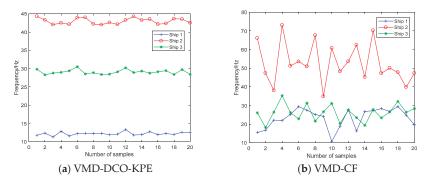

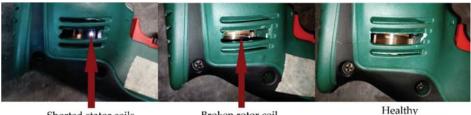

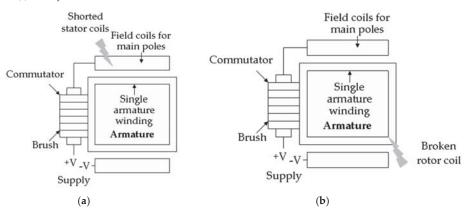

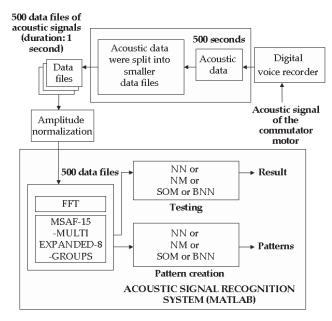

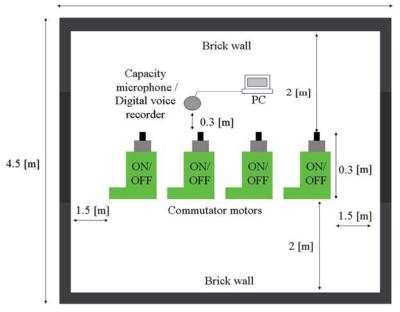

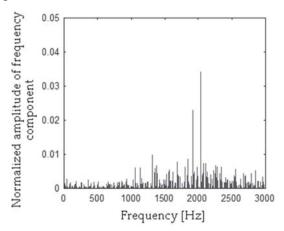

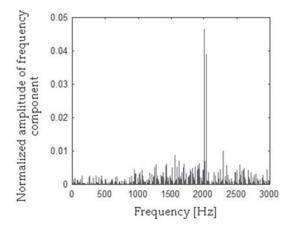

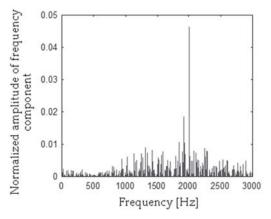

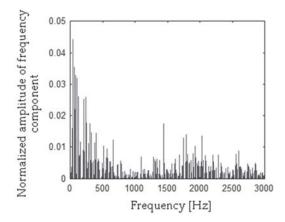

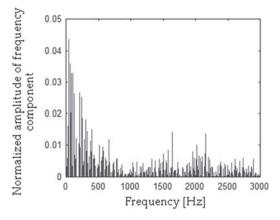

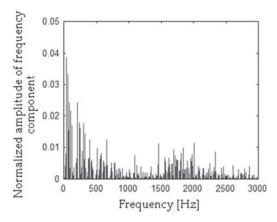

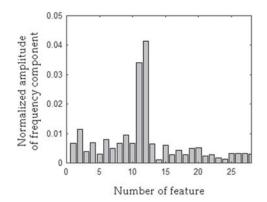

The paper [1] describes the fault diagnosis of a commutator motor using signal processing methods and acoustic signals. Five commutator motors were analyzed: a healthy commutator motor, a commutator motor with a broken rotor coil, a commutator motor with shorted stator coils, a commutator motor with a broken tooth on sprocket and a commutator motor with a damaged gear train. Feature extraction method MSAF-15-MULTIEXPANDED-8-GROUPS (Method of Selection of Amplitudes of Frequency Multiexpanded 8 Groups) was introduced [1]. Processing and feature extraction of an underwater acoustic signal was shown in the paper [2]. The authors proposed a feature extraction method for an underwater acoustic signal. It was based on VMD (variational mode decomposition), DCO (duffing chaotic oscillator) and KPE (kind of permutation entropy) [2]. The next paper [3] presented two models (HOCTVL1 model and SAHOCTVL1 model) for solving the problem of image deblurring under impulse noise. The proposed models are good for recovering the corrupted images [3].

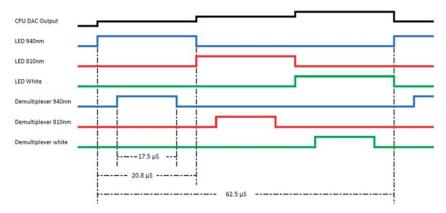

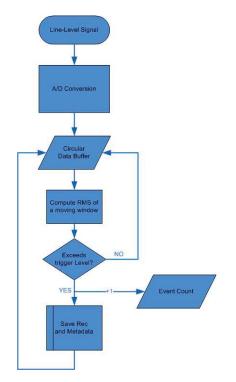

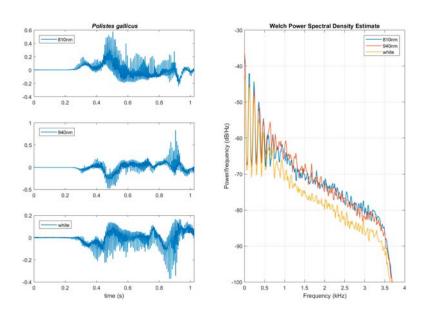

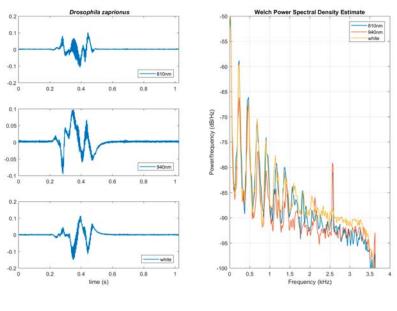

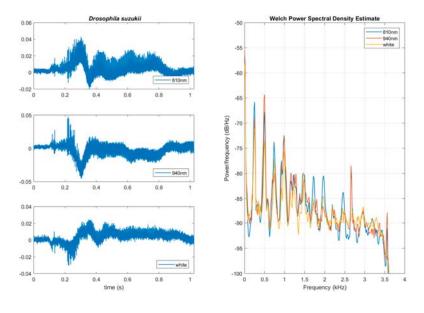

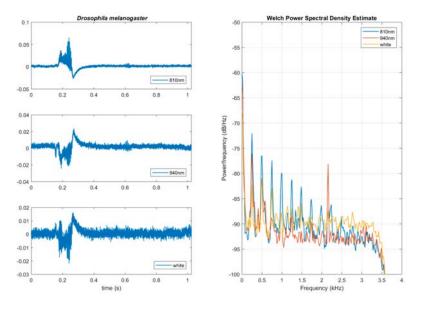

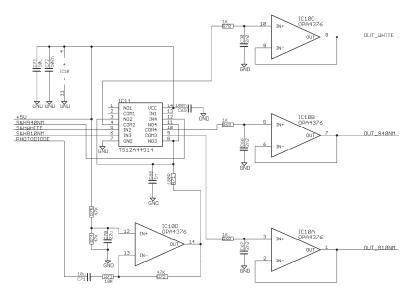

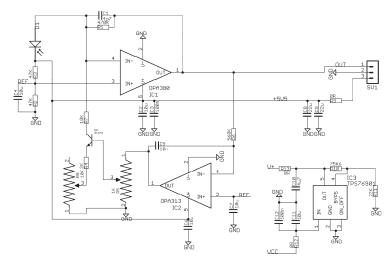

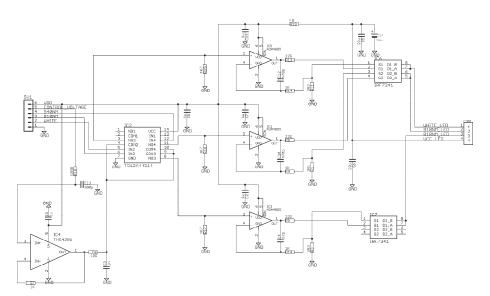

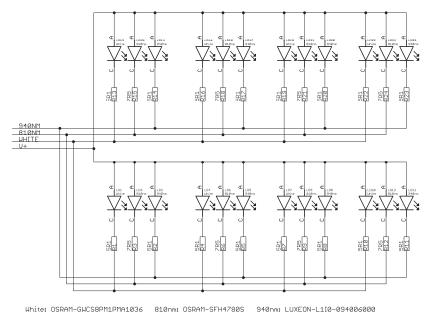

A multispectral backscattered light recorder of insects' wingbeats was presented in the paper [4]. The proposed device extracted a signal of the wingbeat event and color characterization of the insect. The authors of the paper analyzed the following insects: the bee (*Apis mellifera*) and the wasp (*Polistes*)

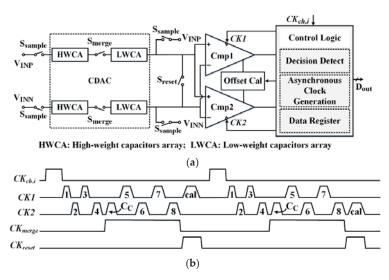

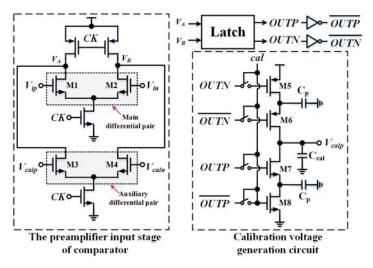

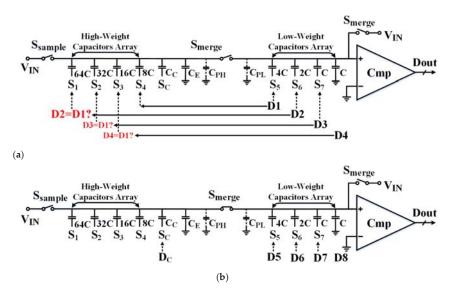

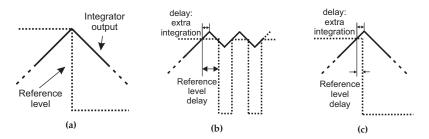

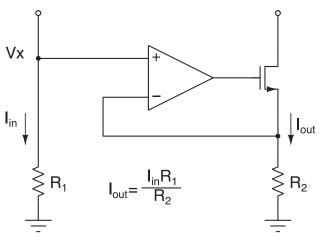

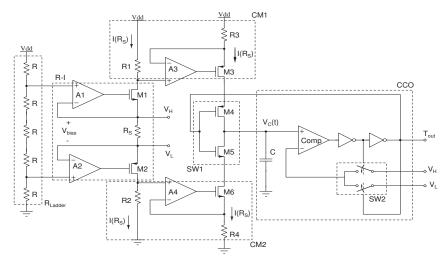

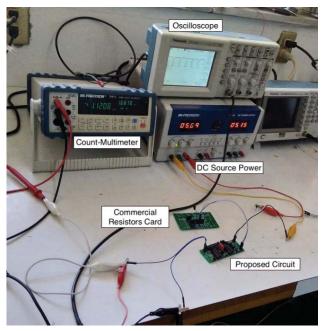

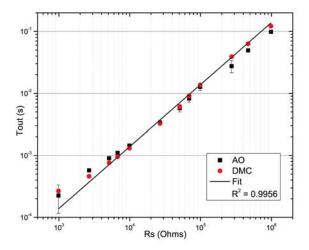

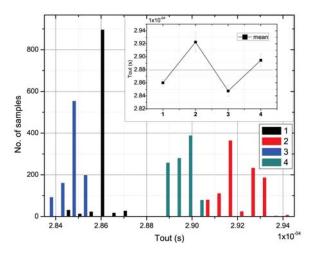

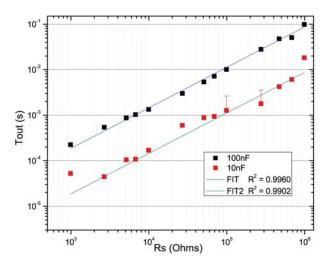

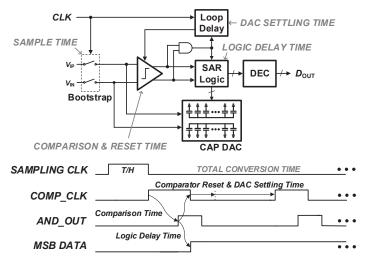

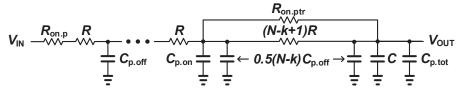

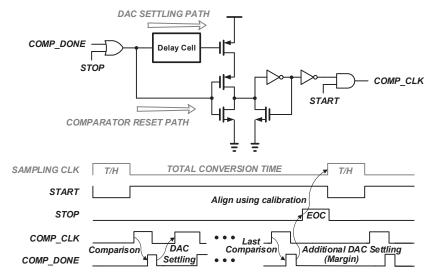

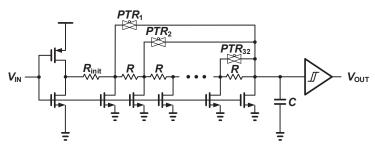

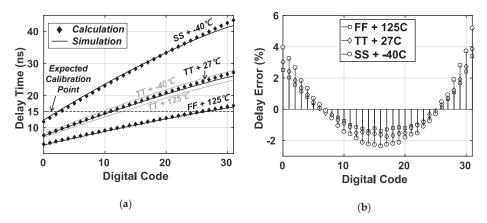

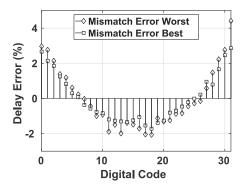

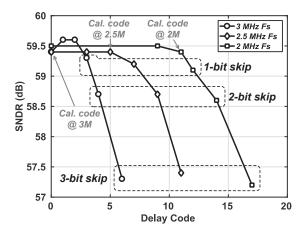

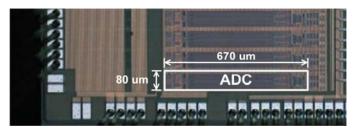

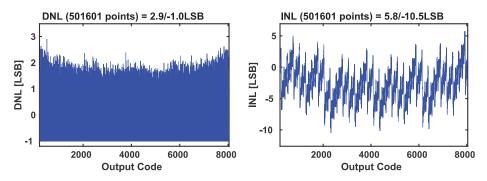

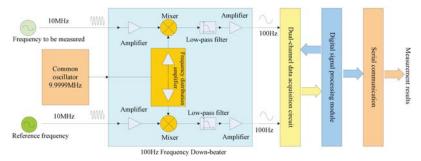

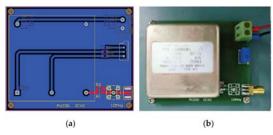

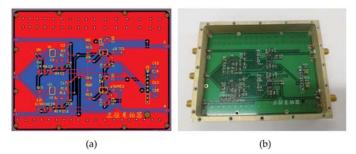

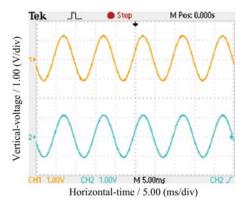

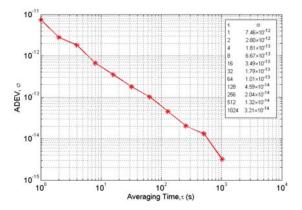

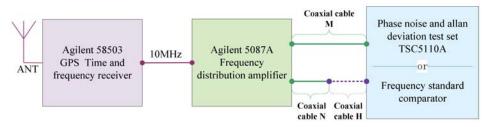

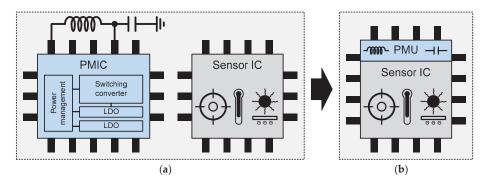

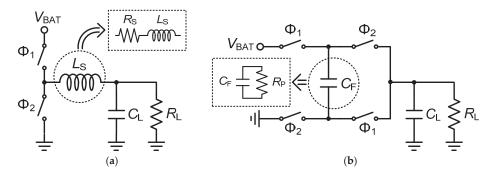

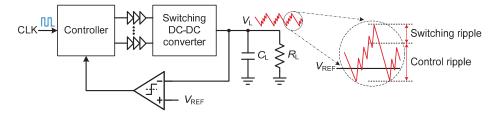

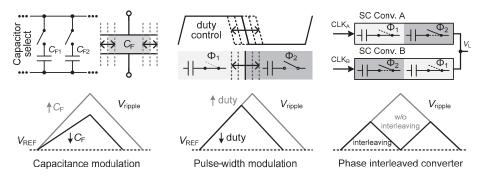

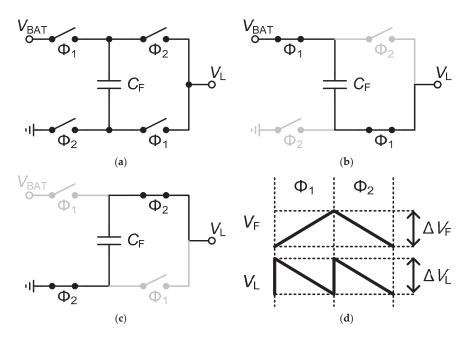

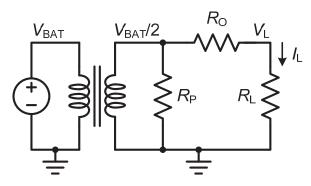

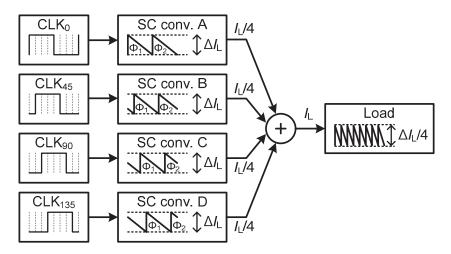

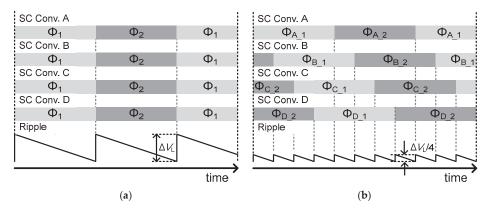

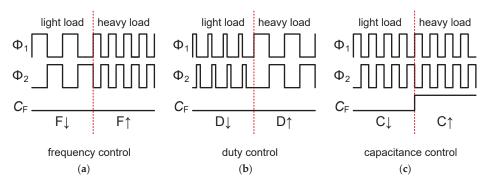

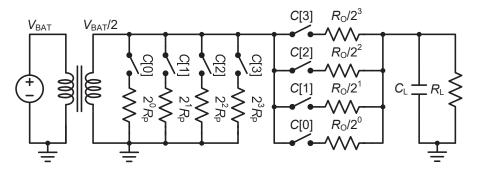

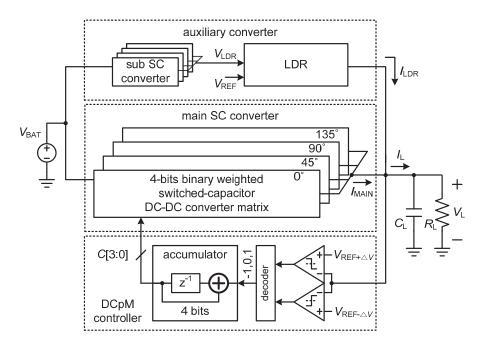

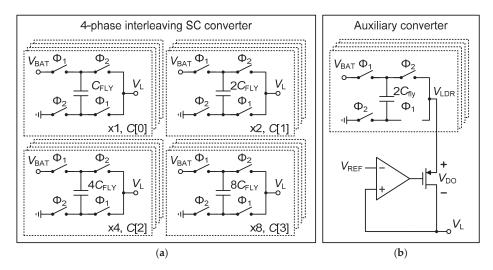

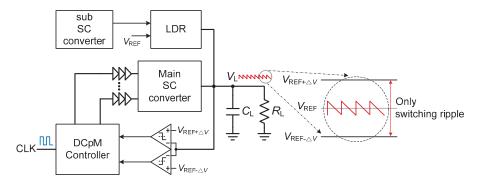

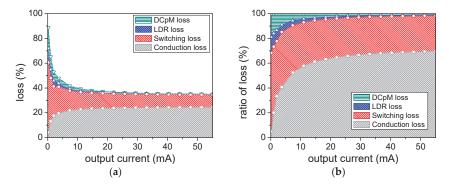

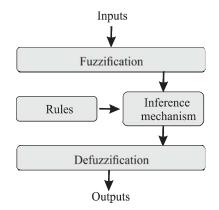

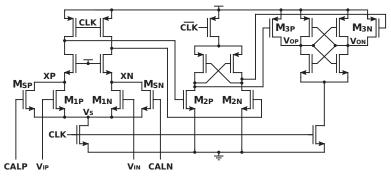

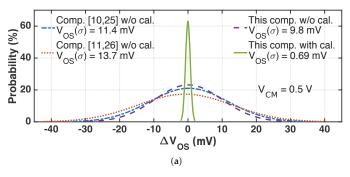

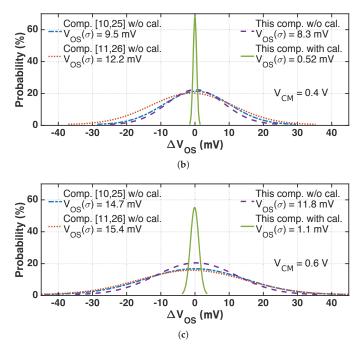

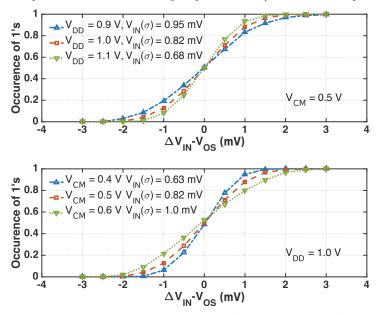

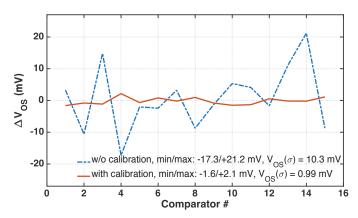

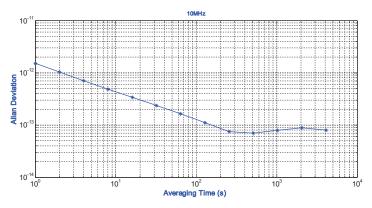

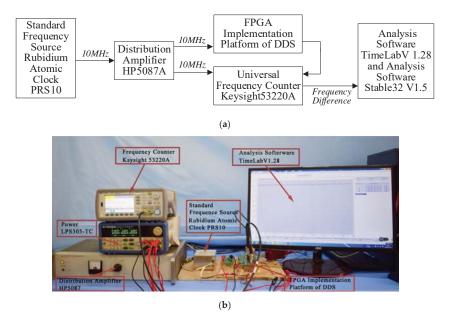

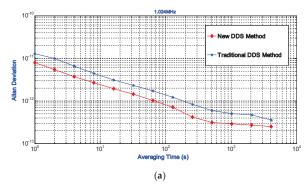

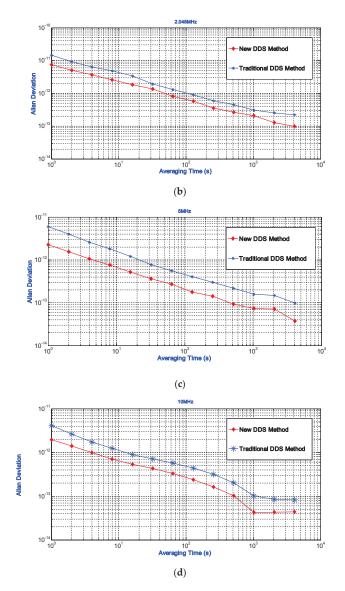

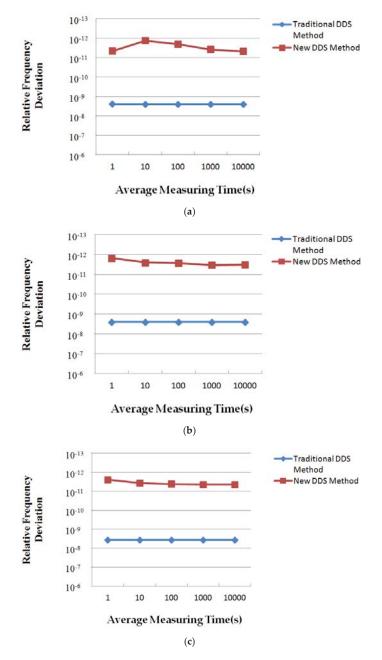

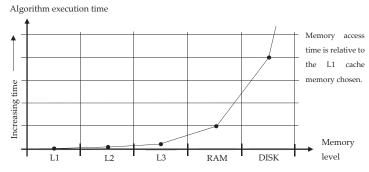

*gallicus*) [4]. A 13-bit 3 MS/s asynchronous SAR ADC with a passive resistor was described [5]. Passive resistors were adopted by the described delay cell. A delay error was less than 5 percent [5]. A miniaturized frequency standard comparator based on FPGA was presented. The noise floor of the analyzed comparator was better than  $7.50 * 10^{-12}$  (1/s) [6]. A low-ripple switched-capacitor DC–DC Converter with parallel low-dropout regulator was proposed. The converter used a four-bit DCpM control and parallel low-dropout regulator [7]. A fuzzy logic system was proposed for the assessment of stator winding short-circuit faults in induction motors. The proposed approach achieved a positive classification rate of 98% [8]. A capacitance-to-time converter-based electronic interface was designed. The proposed interface is suitable for on-chip integration with sensors of force, humidity, position etc. [9]. The self-calibrating dynamic comparator was developed. The presented approach reduced the input offset by  $10 \times [10]$ . There are also other interesting articles in the presented special issue. The proposed approaches and devices can be improved and used for the electrical systems in the future.

The proposed topics are essential for industry. Signal processing and analysis of diagnostic signals are used for fault diagnosis and monitoring systems [11–26]. Signal processing and image processing methods are used for many applications, for example medical applications [27–36]. Switched-Capacitor DC–DC converters are also an interesting topic of research [37–41].

#### 3. Concluding Remarks

Acceleration of the development of electrical systems, signal processing methods and circuits is a fact. Electronics applications related to electrical circuits and signal processing methods have gained noticeable attention in recent time. The methods of signal processing and electrical circuits are widely used by engineers and scientists all over the world.

The presented papers have made a contribution to electronics. The presented applications can be used in the industry. The presented approaches require further improvements for industry and other applications.

Author Contributions: A.G. wrote original draft preparation. He was responsible for editing. J.A.A.D. was also responsible for editing. He also supervised the paper. All authors have read and agreed to the published version of the manuscript.

Acknowledgments: The Guest Editors would like to thank all authors, reviewers and editorial board of MDPI Electronics journal for their valuable contributions to this special issue.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Głowacz, A. Acoustic-based fault diagnosis of commutator motor. *Electronics* 2018, 7, 299. [CrossRef]

- Li, Y.; Chen, X.; Yu, J.; Yang, X. A Fusion Frequency Feature Extraction Method for Underwater Acoustic Signal Based on Variational Mode Decomposition. Duffing Chaotic Oscillator and a Kind of Permutation Entropy. *Electronics* 2019, *8*, 61. [CrossRef]

- Xiang, J.; Ye, P.; Wang, L.; He, M. A Novel Image-Restoration Method Based on High-Order Total Variation Regularization Term. *Electronics* 2019, *8*, 867. [CrossRef]

- Rigakis, I.; Potamitis, I.; Tatlas, N.A.; Livadaras, I.; Ntalampiras, S. A Multispectral Backscattered Light Recorder of Insects' Wingbeats. *Electronics* 2019, *8*, 277. [CrossRef]

- Ju, H.; Lee, M. A 13-bit 3-MS/s Asynchronous SAR ADC with a Passive Resistor Based Loop Delay Circuit. Electronics 2019, 8, 262. [CrossRef]

- 6. Tang, S.; Ke, J.; Wang, T.; Deng, Z. Development of a Miniaturized Frequency Standard Comparator Based on FPGA. *Electronics* **2019**, *8*, 123. [CrossRef]

- Lee, J.Y.; Kim, G.S.; Oh, K.I.; Baek, D. Fully Integrated Low-Ripple Switched-Capacitor DC–DC Converter with Parallel Low-Dropout Regulator. *Electronics* 2019, *8*, 98. [CrossRef]

- Mejia-Barron, A.; de Santiago-Perez, J.J.; Granados-Lieberman, D.; Amezquita-Sanchez, J.P.; Valtierra-Rodriguez, M. Shannon Entropy Index and a Fuzzy Logic System for the Assessment of Stator Winding Short-Circuit Faults in Induction Motors. *Electronics* 2019, *8*, 90. [CrossRef]

- De Marcellis, A.; Reig, C.; Cubells-Beltran, M.D. A Capacitance-to-Time Converter-Based Electronic Interface for Differential Capacitive Sensors. *Electronics* 2019, 8, 80. [CrossRef]

- Ramkaj, A.; Strackx, M.; Steyaert, M.; Tavernier, F. An 11 GHz Dual-Sided Self-Calibrating Dynamic Comparator in 28 nm CMOS. *Electronics* 2019, *8*, 13. [CrossRef]

- Yan, X.P.; Xu, X.J.; Sheng, C.X.; Yuan, C.Q.; Li, Z.X. Intelligent wear mode identification system for marine diesel engines based on multi-level belief rule base methodology. *Meas. Sci. Technol.* 2018, 29. [CrossRef]

- Stief, A.; Ottewill, J.R.; Orkisz, M.; Baranowski, J. Two Stage Data Fusion of Acoustic. Electric and Vibration Signals for Diagnosing Faults in Induction Motors. *Elektron. Elektrotechnika* 2017, 23, 19–24. [CrossRef]

- Singh, G.; Naikan, V.N.A. Detection of half broken rotor bar fault in VFD driven induction motor drive using motor square current MUSIC analysis. *Mech. Syst. Signal Process.* 2018, 110, 333–348. [CrossRef]

- Zhang, C.; Peng, Z.X.; Chen, S.; Li, Z.X.; Wang, J.G. A gearbox fault diagnosis method based on frequencymodulated empirical mode decomposition and support vector machine. *Proc. Inst. Mech. Eng. Part C* 2018, 232, 369–380. [CrossRef]

- Michalak, M.; Sikora, B.; Sobczyk, J. Diagnostic Model for Longwall Conveyor Engines. In Man-Machine Interactions 4, ICMMI 2015, Book Series: Advances in Intelligent Systems and Computing, Proceedings of the Man-Machine Interactions 4—4th International Conference on Man-Machine Interactions, ICMMI 2015, Kocierz Pass, Poland, 6–9 October 2015; Springer: Berlin/Heidelberg, Germany, 2016; Volume 391, pp. 437–448. [CrossRef]

- Glowacz, A.; Glowacz, W. Vibration-Based Fault Diagnosis of Commutator Motor. Shock Vib. 2018, 7460419. [CrossRef]

- Glowacz, A.; Glowacz, Z. Recognition of rotor damages in a DC motor using acoustic signals. *Bull. Pol. Acad.* Sci. Tech. Sci. 2017, 65, 187–194. [CrossRef]

- Glowacz, A. Recognition of acoustic signals of induction motor using FFT. SMOFS-10 and LSVM. *Eksploat. Niezawodn.* 2015, 17, 569–574. [CrossRef]

- 19. Legutko, S. Development Trends in Machines Operation Maintenance. Eksploat. Niezawodn. 2009, 2, 8–16.

- Hreha, P.; Radvanska, A.; Knapcikova, L.; Krolczyk, G.M.; Legutko, S.; Krolczyk, J.B.; Hloch, S.; Monka, P. Roughness Parameters Calculation by Means of On-Line Vibration Monitoring Emerging from AWJ Interaction With Material. *Metrol. Meas. Syst.* 2015, *22*, 315–326. [CrossRef]

- 21. Liu, M.K.; Weng, P.Y. Fault Diagnosis of Ball Bearing Elements: A Generic Procedure based on Time-Frequency Analysis. *Meas. Sci. Rev.* **2019**, *19*, 185–194. [CrossRef]

- Sun, Y.; Zhang, Y.G. New Developments in Fault Analysis Based on Dynamical Perspective. *IETE J. Res.* 2016, 62, 500–506. [CrossRef]

- Krolczyk, G.M.; Krolczyk, J.B.; Legutko, S.; Hunjet, A. Effect of the disc processing technology on the vibration level of the chipper during operations. *Teh. Vjesn.* 2014, 21, 447–450.

- 24. Irfan, M.; Saad, N.; Ibrahim, R.; Asirvadam, V.S. Condition monitoring of induction motors via instantaneous power analysis. *J. Intell. Manuf.* 2017, *28*, 1259–1267. [CrossRef]

- Pandiyan, V.; Caesarendra, W.; Tjahjowidodo, T.; Tan, H.H. In-process tool condition monitoring in compliant abrasive belt grinding process using support vector machine and genetic algorithm. *J. Manuf. Process.* 2018, 31, 199–213. [CrossRef]

- Zmarzly, D.; Boczar, T.; Fracz, P.; Borucki, S. High Voltage Power Transformer Diagnostics using Vibroacoustic Method. In Proceedings of the 2014 IEEE International Power Modulator and High Voltage Conference (IPMHVC), Santa Fe, NM, USA, 1–5 June 2014; pp. 561–564.

- Kowalczyk, M.; Przewlocka, D.; Kryjak, T. Real-time implementation of contextual image processing operations for 4K video stream in Zynq UltraScale plus MPSoC. In Proceedings of the 2018 Conference on Design and Architectures for Signal and Image Processing (DASIP), 9–12 October 2018; pp. 37–42.

- Kryjak, T.; Komorkiewicz, M.; Gorgon, M. Real-time Implementation of Foreground Object Detection From a Moving Camera Using the ViBE Algorithm. *Comput. Sci. Inf. Syst.* 2014, 11, 1617–1637. [CrossRef]

- 29. Kurtasz, P.; Boczar, T.; Witkowski, P.; Lorenc, M. The application of the multicomparative algorithm for classifying acoustic signals coming from partial discharges. *Prz. Elektrotech.* **2010**, *86*, 125–127.

- 30. Boczar, T.; Lorenc, M. The application of the descriptive statistics for recognizing electrical discharge forms registered by the acoustic emission method. *Prz. Elektrotech.* **2008**, *84*, 6–9.

- Jablonski, M.; Tylek, P.; Walczyk, J.; Tadeusiewicz, R.; Pilat, A. Colour-Based Binary Discrimination of Scarified Quercus Robur Acorns under Varying Illumination. *Sensors* 2016, 16, 1319. [CrossRef]

- 32. Jaworek-Korjakowska, J.; Kleczek, P.; Tadeusiewicz, R. Detection and Classification of Pigment Network in Dermoscopic Color Images as One of the 7-Point Checklist Criteria. In *Recent Developments and Achievements in Biocybern. Biomed. Eng.* 2018, Book Series: Advances in Intelligent Systems and Computing, Proceedings of the 20th Polish Conference on Biocybernetics and Biomedical Engineering, Kraków, Poland, 20–22 September 2017; Springer: Berlin/Heidelberg, Germany, 2018; Volume 647, pp. 174–181. [CrossRef]

- 33. Glowacz, A.; Glowacz, Z. Recognition of images of finger skin with application of histogram, image filtration and K-NN classifier. *Biocybern. Biomed. Eng.* **2016**, *36*, 95–101. [CrossRef]

- Kantoch, E. Recognition of Sedentary Behavior by Machine Learning Analysis of Wearable Sensors during Activities of Daily Living for Telemedical Assessment of Cardiovascular Risk. Sensors 2018, 18, 3219. [CrossRef]

- 35. Proniewska, K. Data mining with Random Forests as a methodology for biomedical signal classification. *Bio-Algorithms Med-Syst.* **2016**, *12*, 89–92. [CrossRef]

- Proniewska, K.; Malinowski, K.; Pociask, E.; Proniewski, B. Classification of Sleep Disordered Breathing in the Evaluation of Acoustic Sound in Correlation with the ECG Signal. In Proceedings of the 2014 Computing in Cardiology Conference 2014 (CinC), Cambridge, MA, USA, 7–10 September 2014; Volume 41, pp. 153–156.

- Jiang, Y.; Law, M.K.; Chen, Z.Y.; Mak, P.I.; Martins, R.P. Algebraic Series-Parallel-Based Switched-Capacitor DC-DC Boost Converter With Wide Input Voltage Range and Enhanced Power Density. *IEEE J. Solid-State Circuits* 2019, 54, 3118–3134. [CrossRef]

- Mohey, A.M.; Ibrahim, S.A.; Hafez, I.M.; Kim, H. Design Optimization for Low-Power Reconfigurable Switched-Capacitor DC-DC Voltage Converter. *IEEE Trans. Circuits Syst. I-Regul. Pap.* 2019, 66, 4079–4092. [CrossRef]

- Xie, F.Y.; Wu, B.C.; Liu, T.T. A Ripple Reduction Method for Switched-Capacitor DC-DC Voltage Converter Using Fully Digital Resistance Modulation. *IEEE Trans. Circuits Syst. I-Regul. Pap.* 2019, 66, 3631–3641. [CrossRef]

- 40. Zeng, T.; Wu, Z.; He, L.Z. Bridge modular switched-capacitor DC-DC converter with soft switching operation and multilevel voltage-gain range. *IEEJ Trans. Electr. Electron. Eng.* **2019**, *14*, 1399–1408. [CrossRef]

- 41. Kumar, M.; Ramesh, S. Design and Implementation of Three-Winding Coupled Inductor and Switched Capacitor-Based DC-DC Converter Fed PV-TDVR. J. Circuits Syst. Comput. 2019, 28. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

# Article Numerical Laplace Inversion Method for Through-Silicon Via (TSV) Noise Coupling in 3D-IC Design

#### Khaoula Ait Belaid <sup>1</sup>,\*<sup>(D)</sup>, Hassan Belahrach <sup>1,2</sup><sup>(D)</sup> and Hassan Ayad <sup>1</sup>

- <sup>1</sup> Faculty of Science and Technology, Cadi Ayyad University, Marrakesh 40000, Morocco

- <sup>2</sup> Electrical Engineering Department, Royal School of Aeronautics, Marrakesh 40000, Morocco

- \* Correspondence: aitbelaid.khaoula@gmail.com

Received: 20 August 2019; Accepted: 29 August 2019; Published: 10 September 2019

**Abstract:** Typical 3D integrated circuit structures based on through-silicon vias (TSVs) are complicated to study and analyze. Therefore, it seems important to find some methods to investigate them. In this paper, a method is proposed to model and compute the time-domain coupling noise in 3D Integrated Circuit (3D-IC) based on TSVs. It is based on the numerical inversion Laplace transform (NILT) method and the chain matrices. The method is validated using some experimental results and the Pspice and Matlab tools. The results confirm the effectiveness of the proposed technique and the noise is analyzed in several cases. It is found that TSV noise coupling is affected by different factors such as source characteristics, horizontal interconnections, and the type of Inputs and Outputs (I/O) drivers.

Keywords: 3D-IC design; NILT; TSV noise coupling; RDL; chain matrix; interconnect line

#### 1. Introduction

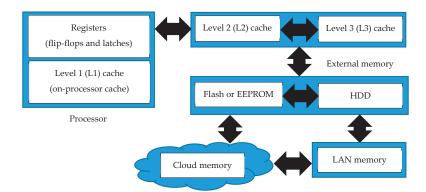

Over the last four decades, silicon semiconductor technology has advanced at exponential rates in terms of performance and productivity [1,2]. Analysis of the fundamentals, materials, devices, circuits, and system limits discloses that silicon technology still has colossal potential for achieving terascale integration (TSI) of a significant number of transistors per chip. Such large-scale integration is feasible by assuming the development and bulk economic production of metal-oxide-semiconductor double-gate field-effect transistors. The development of interconnect lines for these transistors is a major challenge for the realization of nanoelectronics for TSI. Employing systems with high performance requires using two approaches. The first consists of reducing the size of the transistors, to enhance IC reduction technologies, and assembling ICs on the same chip (SoC) [3]. The second consists of developing high-performance technologies for interconnections between chips (SiP). For proper functioning, the area occupied by interconnections, which sometimes exceeds that occupied by the main functional blocks or chips, as well as their lengths must be reduced. However, since the interconnections are required in electronic systems, the number of interconnections cannot be decreased adversely to the area which can be reduced using 3D technology based on vertical interconnections.

Three-dimensional technology is acknowledged as an effective solution to overcome the challenges of miniaturization and distribution density. It combines More Moore and More than Moore, which offers many benefits. Some advantages of this technology are power efficiency, performance enhancement, cost reduction, and modular design [4–6]. Three-dimensional technology allows vertical stacking of chips through vertical interconnections like Through-Silicon-Via. Three-dimensional architectures contain different elements, such as through-silicon vias (TSVs), the substrate, redistribution layers (RDLs), and active circuits, which makes them difficult to model and study. To model these structures, each element is modeled using lumped circuits, and the entire model is then constructed by combining these element models in an appropriate manner.

Several papers have discussed the issue of modeling TSVs. In [7,8], the authors proposed a methodology based on Radio Frequency (RF) characterizations and simulations, leading to a frequency-dependent analytical model including the metal-oxide-semiconductor (MOS) effect of high ratio TSVs. The authors of [9] gave an accurate electrical model of TSVs considering metal-oxide-semiconductor (MOS) capacitance effects. The MOS capacitance accurately solved Poisson's equation in cylindrical coordinates. Another compact wideband equivalent circuit model for electrical modeling of TSVs has been presented in [10]. In another previous work [11], the Resistance, Inductance and Capacitance (RLC) parameters of TSVs were modeled as a function of physical parameters and material characteristics. The RLC model is applied to predict the resistance, inductance, and capacitance of small-geometry TSV architectures. TSV impedance can also be extracted using a fully analytical and physical model in addition to Green's function in high frequency [12]. All these previous works have given models of one TSV without considering general multi-TSV architectures. Thus, in [3,13,14] a TSV noise coupling model and TSV-to-active circuit have been proposed based on a three-dimensional transmission line matrix method (3D-TLM). Using this method, the noise transfer functions in the frequency domain from TSV-to-TSV and TSV-to-active circuit can be estimated. Other analytical models, for vias and traces, have been proposed in [15]. Vias are modeled using an analytical formulation for the parallel-plate impedance and capacitive elements, whereas the trace-via transitions are described by modal decomposition. All these proposed models are validated against full-wave methods and measurements up to 40 GHz. An efficient method to model TSV interconnections is proposed in [16]. This technique is based on solving Maxwell's equation in integral form, the method uses a small number of global modal basis functions and can be much faster than discretization-based integral-equation methods. The models proposed in the literature differ; indeed, some models contain the depletion capacitance, TSV resistance, and TSV inductance, others neglect these elements, especially for frequencies below 20 GHs [3,13,14].

The TSV capacitance depends on both the oxide capacitance and the depletion capacitance [17]. As the TSV gate bias increases, the depletion region capacitance starts to increase, and it acts in series with oxide capacitance. Hence, a TSV capacitor,  $C_{TSV}$ , is modeled with a series connection of the oxide capacitors and a depletion region capacitor [18]. The width of the depletion region is calculated for every geometrical variation by means of the exact Poisson's equation for an average TSV voltage of 0.5 V, and modeled as an area where the substrate has no free charge carriers [19]. Consequently, an increasing average TSV voltage increases its isolation from the substrate [20]. Thus, a power  $V_{dd}$ -TSV generally draws less E-field lines than a ground GND-TSV. However, the influence of the depletion region can be neglected [19].

RDLs have an important role in TSV packaging applications, they are used to connect various elements in 3D-IC and to redistribute the signals between dies. Therefore, different works have proposed several models for these interconnections. In [3,21], the authors gave analytic RLGC equations for the equivalent circuit model of a single-ended signal RDL to estimate the electrical characteristics. For the substrate, which has a distribution nature, its model can be extracted from numerical techniques mentioned in [22,23]. By combining each partial model, the global model of 3D structures is obtained.

One of the 3D-architecture challenges is to avoid noise coupling, which is a significant problem and causes serious effects. This noise degrades system performance and makes it more sensitive. It can also be transmitted directly to an active circuit through the substrate; therefore, the signal and power are corrupted, the system reliability is reduced, and the bit error rate is increased [24,25].

The investigation of the noise coupling in 3D architecture based on TSVs is mainly done in the frequency domain. Yet, as far as we know, no technique has been proposed to compute these noises in the time domain. Hence, the objective of this paper is to propose a method to compute noise coupling in 3D-IC in the time domain. It is necessary to obtain the wave forms of these noises in the time domain in order to analyze them, since the transition effects can be better observed in the time domain. Time-domain noise coupling was obtained by the NILT method and chain matrices. First, the method

was applied to three different structures. Then, the TSV coupling noise was analyzed, for each structure, to deduce how the coupling between the horizontal interconnections affects it. Simulations in Pspice were done to validate the method.

The rest of the paper is organized as follows. The NILT method in addition to a chain matrix of many studied circuits are explained in Section 2. The results and simulations are analyzed in Section 3. The conclusions are drawn in the last section.

#### 2. Calculation of Time-Domain TSV Noise Coupling in 3D-IC Design with NILT

The use of the Laplace transform method has simplified the solution of transients on transmission lines (TL), of transients of dynamic systems, and other problems in electrical engineering. However, some difficulties appear when transforming solutions to the time domain. This makes researchers concerned to find accurate and precise numerical methods. One of these numerical methods is the numerical inverse Laplace transform (NILT) method, which can be used in cases when, for instance, the transform is a transcendental, irrational or some other complex function; then finding the solution in its analytical form is difficult and sometimes impossible [26,27].

The NILT method has been used in several works. In [28], NILT methods were selected to evaluate their performance for dealing with solution transportation in the subsurface under uniform or radial flow conditions. The authors of [29] evaluate and compare some numerical algorithms of the NILT method for the inversion accuracy of some fractional order differential equation solutions. In [30–35] the multidimensional NILT method has been explained in detail for electrical circuits.

In this paper, we were interested in 1D-NILT. Thus, a one-dimensional Laplace transform of a function f(t), with;  $t \ge 0$ , is defined as:

$$F(s) = \int_{0}^{\infty} f(t)e^{-st}dt$$

(1)

Under the assumption  $|f(t)| \le Me^{\alpha t}$ , M is real positive,  $\alpha$  is a minimal abscissa of convergence, and F(s) is defined on a region  $\{s \in C : \operatorname{Re}[s] > \alpha\}$ , with  $s = c + j\Omega$ , c is defined as an abscissa of convergence,  $\Omega = \frac{2\pi}{\tau}$  as the generalized frequency step, and  $\tau$  forms a region of the solutions  $t \in [0 \tau]$ .

The original function can be given using the Bromwich integral [36]:

$$f(t) = \frac{1}{2\pi j} \int_{c-j\infty}^{c+j\infty} F(s) e^{st} ds$$

<sup>(2)</sup>

By using a rectangular rule of integration as mentioned in [30], Equation (3) is found.

$$\tilde{f}(t) = \frac{\exp(ct)}{\tau} \sum_{n=0}^{\infty} F(s) \exp(jn\Omega t)$$

(3)

As explained in [30], by substituting  $s = c + jn\Omega$  into Equation (1), if the obtained function has integration ranges split into infinite numbers of steps of the length  $\tau$ , F(s) could be written as:

$$F_n = F(c+jn\Omega) = \sum_{l=0}^{\infty} \int_{l\tau}^{(l+1)\tau} g(t) \exp(-jn\Omega t) dt$$

(4)

g(t) is an exponentially damped object function. Then for  $t \in [l\tau, \tau(l+1)]$ , the functions  $g_l(t)$  and F(s) are given by:

$$g_l(t) = f(t) \exp(-ct) \tag{5}$$

Electronics 2019, 8, 1010

$$F(c+jn\Omega) = \tau \sum_{l=0}^{\infty} C_{l,n}$$

(6)

where:

$$C_{l,n} = \frac{1}{\tau} \int_{l\tau}^{(l+1)\tau} g_l(t) \exp(-jn\Omega t) dt$$

(7)

Applying complex Fourier series to Equation (5),  $g_l(t)$  could be found as:

$$g_l(t) = \sum_{n=-\infty}^{+\infty} C_{l,n} \exp(jn\Omega t)$$

(8)

Moreover, by substituting Equation (6) into Equation (3) and considering Equation (8), it is found that the approximate original function exponentially damped could be expressed as the infinite sum of the newly defined periodical function, Equation (5).

By exploiting all the previous equations, f(t) is obtained and the absolute error  $\varepsilon(t) = f(t) - f(t)$  can be computed.

$$\widetilde{f}(t) = f(t) + \sum_{l=1}^{\infty} f(l\tau + t) \cdot \exp(-cl\tau)$$

(9)

A limiting absolute error is determined as  $\varepsilon_M(t) \ge \varepsilon(t)$ , then  $|f(t)| \le Me^{\alpha t}$ , so a limiting relative error  $\delta_M$  could also be controlled, and a path of integration from a required limit relative error could be chosen using Equation (10).

$$c = \alpha - \frac{1}{\tau} \ln \left( 1 - \frac{1}{1 + \delta_M} \right) \approx \alpha - \frac{1}{\tau} \ln(\delta_M)$$

(10)

This formula is valid, with a relative error achieved by the NILT f(t), if infinite numbers of terms are used in series, and is a suitable technique for accelerating a convergence and for achieving the convergence of infinite series in a suitable way. Equation (3) can be rewritten using FFT and IFFT algorithms for an effective computation. Based on the experience of the authors of [31], the quotient-difference (q-d) algorithm of Rutishanser seems to give errors rather close to  $\delta_M$  predicted by Equation (10), while considering a relatively small number of additional terms.

While considering a discrete variable in the original domain,  $t_k = kT$ , where T is a sampling period,  $\tilde{f}(t)$  could be expressed as:

$$\widetilde{f}_{k} = \frac{\exp(ckT)}{\tau} \sum_{n=-\infty}^{\infty} \widetilde{F}\left(c + jn\frac{2\pi}{\tau}\right) \exp\left(j2\pi\frac{nkT}{\tau}\right)$$

(11)

The above stated formula could be decomposed as:

$$\tilde{f}_{k} = C_{k} \left[ \sum_{n=0}^{N-1} \tilde{F}^{(-n)} z_{-k}^{n} + \sum_{n=0}^{\infty} \tilde{G}^{(-n)} z_{-k}^{n} + \sum_{n=0}^{N-1} \tilde{F}^{(n)} z_{k}^{n} + \sum_{n=0}^{\infty} \tilde{G}^{(n)} z_{k}^{n} - \tilde{F}^{(0)} \right]$$

(12)

where  $N = 2^k$ , k integer,  $\tilde{F}^{(\pm n)} = \tilde{F}(c - jn\Omega)$ ,  $\tilde{G}^{(\pm n)} = \tilde{F}^{(\pm N \pm n)}$ ,  $z_{\pm k} = \exp(\pm j \frac{2\pi kT}{\tau})$ , and  $C_k = \frac{\exp(ckT)}{\tau}$ , while  $\tau = NT$ ,  $\forall k$ , and  $z_{\pm k}^N = \exp(\pm j 2\pi k) = 1$ .

In Equation (12), the first and the third sum are evaluated using the FFT and IFFT algorithms, respectively, while other parts, which present the infinite sum, are used as the input data in the q-d algorithm that uses a very small number of necessary additional terms, as explained in [24]. The computing region should be chosen as:  $O_{cal} = (0, t_{cal})$ , where  $t_{cal} = (\frac{N}{2} - 1).T$ .

Time-domain noise coupling could be easily obtained by the explained method in 3D technology based on TSVs.

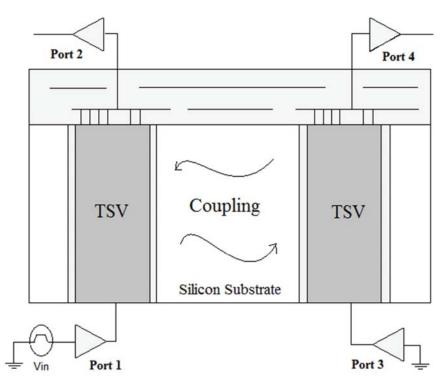

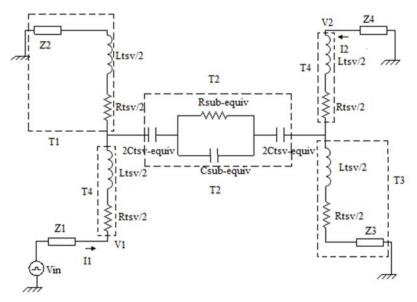

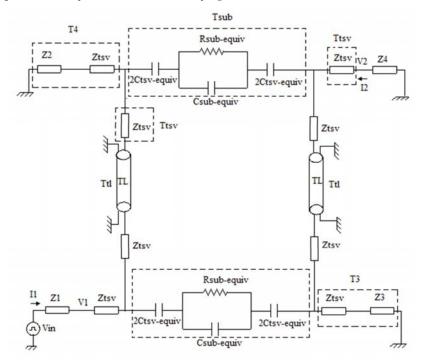

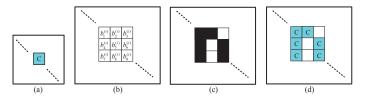

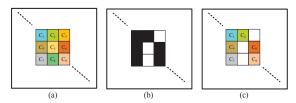

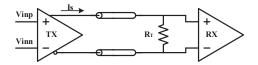

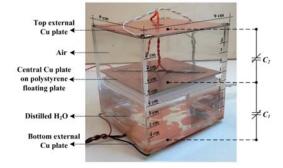

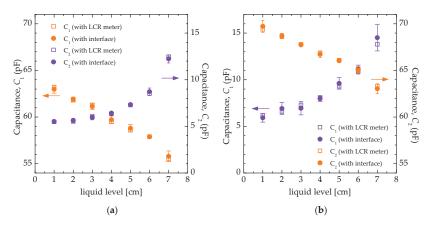

In order to compute the noise coupling, different circuits were treated. The first structure is illustrated in Figure 1. This figure represents a basic structure of the TSV–TSV noise coupling [3]. It is composed of two signal TSVs, two ground TSVs, and is terminated by I/O drivers. The simplified lumped circuit model of this structure is given in Figure 2, where  $C_{TSV-equiv}$  is the total equivalent TSV capacitance,  $R_{sub-equiv}$  is the substrate resistance, and  $C_{sub-equiv}$  is the substrate capacitance. In this simplified model, proposed in [3], the TSV resistance ( $R_{TSV}$ ), the TSV inductance ( $L_{TSV}$ ), and the depletion region are neglected, but in our work  $R_{TSV}$  and  $L_{TSV}$  are kept. In the study just mentioned, the authors assume that their effects appear in frequencies above 12 GHz. To consider the effect of the depletion region, which is modeled by a capacitance, it is enough to add its value to the TSV capacitance. The I/O drivers can be modeled as a resistor for the output driver and as a capacitor for the input driver that represents the MOS gate capacitance. The I/O drivers are presented by the impedances  $Z_1$ ,  $Z_2$ ,  $Z_3$ , and  $Z_4$ . To apply the NILT method, the conceptual structure can be modeled with a T-matrix, as illustrated in the figure. The entire matrix of the circuit is the product of  $T_1$ ,  $T_2$ , and  $T_3$ , as defined below.

$$\begin{pmatrix} V_1 \\ I_1 \end{pmatrix} = [T] \begin{pmatrix} V_2 \\ -I_2 \end{pmatrix}$$

(13)

where:

$$[T] = [T_4] [T_1] [T_2] [T_3] [T_4]$$

(14)

$$[T_1] = \begin{bmatrix} 1 & 0\\ 1/(Z_2 + \frac{R_{ISU}}{2} + s\frac{L_{ISU}}{2}) & 1 \end{bmatrix}$$

(15)

$$T_2] = \left[\begin{array}{cc} 1 & Z_{eq} \\ 0 & 1 \end{array}\right] \tag{16}$$

$$[T_3] = \begin{bmatrix} 1 & 0\\ 1/(Z_3 + \frac{R_{ISD}}{2}) + s\frac{L_{ISD}}{2} & 1 \end{bmatrix}$$

(17)

$$[T_4] = \begin{bmatrix} 1 & R_{tsv} + sL_{tsv} \\ 0 & 1 \end{bmatrix}$$

(18)

$$Z_{eq} = \frac{2}{2C_{TSV-equiv}s} + \frac{R_{sub-equiv}}{1 + R_{sub-equiv}C_{sub-equiv}s}$$

(19)

Observing the circuit, Equations (14) and (15) are found:

$$V_{in}(s) = Z_1(s)I_1(s) + V_1(s)$$

(20)

$$V_2(s) = -Z_4(s)I_2(s)$$

(21)

Figure 1. The through-silicon via (TSV)–TSV noise coupling structure with I/O termination.

Figure 2. Lumped circuit model of TSV–TSV noise coupling.

By exploiting Equations (13)–(15), the noise  $V_2$  could be expressed in the frequency domain according to  $V_{in}$ , then the NILT method can be applied, by replacing F(s) by  $V_2(s)$  in previous equations, to find the noise in the time domain. The voltage source  $V_{in}$  is a periodic trapezoidal signal switching expressed by Equation (16).

$$V_{in}(s) = \sum_{n=0}^{\infty} \exp(-snT) \cdot E(s)$$

(22)

where T is the period and E(s) represents the trapeze shape.

Then, while  $\frac{1}{1-x} = \sum_{n=0}^{\infty} x^n$ , Equation (16) could be written as:

$$V_{in}(s) = \frac{1}{1 - \exp(-Ts)} E(s)$$

(23)

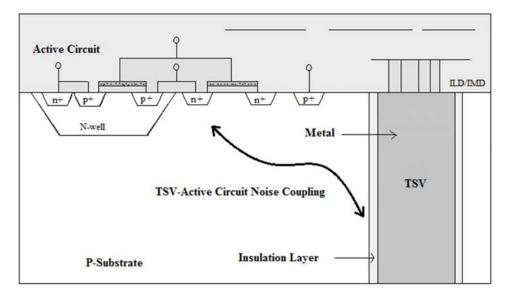

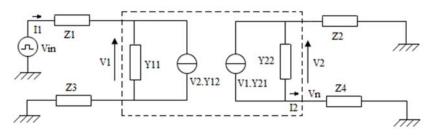

The second analyzed structure is given in Figure 3. It represents the conceptual view of TSV-active circuit noise coupling. The equivalent circuit model of this structure is similar to that in Figure 2, except that the capacity on the right is eliminated [3]. Consequently, the calculation was also done in the same way.

Figure 3. The conceptual view of TSV-active circuit noise coupling.

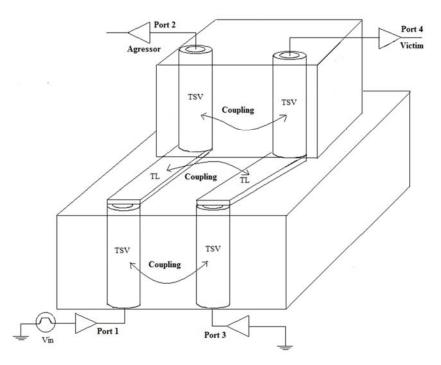

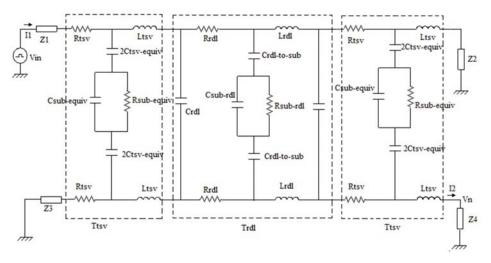

Because of the diversity of electronic devices, and the presence of many stacked dies in 3D technology, the second studied circuit contains two stacked dies with two interconnect lines. The concerned structure is presented in Figure 4. First, the noise coupling was calculated without taking into consideration the coupling between the two interconnect lines, only the coupling between the TSVs in each level was considered. This conceptual structure is modeled by a lumped circuit, as given in Figure 5.

Figure 4. The conceptual view of a TSV noise coupling structure with interconnect lines and I/O drivers.

Figure 5. The equivalent circuit model of TSV noise coupling with interconnect line.

Electronics 2019, 8, 1010

The electrical schema presented in Figure 5 is composed of a lumped circuit model of TSV–TSV noise coupling in each die, two interconnect lines to distribute signals between dies, and I/O drivers modeled by  $Z_1$ ,  $Z_2$ ,  $Z_3$ , and  $Z_4$ .

As explained above, before applying the NILT method, the global T-matrix of the circuit must be found. The matrices  $T_{sub}$ ,  $T_{tsv}$ ,  $T_{tl}$ ,  $T_3$ , and  $T_4$  were used. First,  $T_1$  and  $T_2$  were calculated using Equations (18) and (19), respectively, then a transformation to  $Y_1$  and  $Y_2$  of  $T_1$  and  $T_2$ , respectively, was made. This transformation was performed to find the global  $Y_g$  of the circuit without  $Z_1$ ,  $Z_4$ , and  $Z_{tsv}$  near  $Z_1$  and  $Z_4$ . Then another transformation from  $Y_g$  to  $T_g$  was performed. When finding  $T_g$ , it is multiplied by  $T_{tsv}$  on the left and right sides, and by using Equations (13), (14), and (21)  $V_2$  is found according to  $V_{in}$ .

$$[T_1] = [T_{sub}].[T_3].[T_{tsv}].[T_{tl}].[T_{tsv}]$$

(24)

$$[T_2] = [T_{tsv}].[T_{tl}].[T_{tsv}].[T_4].[T_{sub}]$$

(25)

$$[Y_g] = [Y_1] + [Y_2] \tag{26}$$

$$V_2 = -Z_4 I_2$$

(27)

where:

$$[T_{tl}] = \begin{bmatrix} \cos(\beta l) & jZ_0 \sin(\beta l) \\ j \sin(\beta l)/Z_0 & \cos(\beta l) \end{bmatrix}$$

(28)

where  $\beta$  is the propagation constant, *l* and *Z*<sub>0</sub> are the length and the characteristic impedance, respectively, of the interconnect line, and:

$$[T_{sub}] = \begin{bmatrix} 1 & Zeq \\ 0 & 1 \end{bmatrix}$$

(29)

$$[T_{tsv}] = \begin{bmatrix} 1 & Z_{tsv} \\ 0 & 1 \end{bmatrix}$$

(30)

$$[T_4] = \begin{bmatrix} 1 & 0\\ \frac{1}{Z_4 + Z_{lsv}} & 1 \end{bmatrix}$$

(31)

$$[T_3] = \begin{bmatrix} 1 & 0\\ \frac{1}{Z_{lsv} + Z_3} & 1 \end{bmatrix}$$

(32)

To consider the coupling between the interconnect lines, the conceptual structure presented in Figure 4 is modeled by the lumped circuit model shown in Figure 6. In the schema, the interconnect lines are presented by the equivalent circuit model of RDL [21]. As already explained above, to apply the NILT method, the total T-matrix of the circuit was calculated and then the noise  $V_n$  according to  $V_{in}$  was found.

Figure 6. The equivalent circuit model of TSV noise coupling with redistribution layers (RDLs).

First, the total T-matrix,  $T_g$ , was computed as in Equation (23), then a transformation to  $Y_g$  was done to find the equivalent circuit of Figure 7. Hence, exploiting this figure and Equations (24)–(26), the noise  $V_n$  was calculated according to  $V_{in}$ .

$$\begin{bmatrix} T_g \end{bmatrix} = \begin{bmatrix} T_{tsv} \end{bmatrix} \cdot \begin{bmatrix} T_{rdl} \end{bmatrix} \cdot \begin{bmatrix} T_{tsv} \end{bmatrix}$$

(33)

$$\begin{pmatrix} I_1 \\ I_2 \end{pmatrix} = \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix} \begin{pmatrix} V_1 \\ V_2 \end{pmatrix}$$

(34)

$$V_{in} = (Z_1 + Z_3) I_1 + V_1 \tag{35}$$

$$V_2 + \left(\frac{Z_4 + Z_2}{Z_4}\right) V_n = 0$$

(36)

Figure 7. The admittance equivalent circuit of TSV noise coupling with RDLs.

The total admittance of all previous circuits could also be calculated, as mentioned in [37], before applying the NILT method.

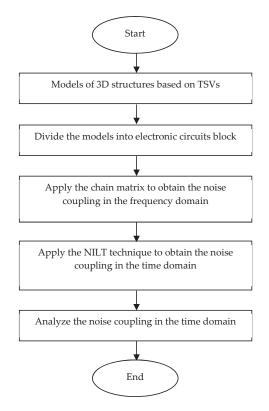

The proposed method can be summarized in the diagram of Figure 8.

Figure 8. Block diagram of the proposed method.

#### 3. Results and Discussions

In order to evaluate the effectiveness of the proposed method, simulation tests of the previous circuits were carried out. Simulations were performed with the Matlab and Pspice tools for all schemes, while the experimental tests of circuits 1 and 2 were taken from [13]. To take the measurements, the test vehicle in Figure 1 was fabricated using the Hynix via-last TSV process. The TSV circuit elements were calculated using the TLM-3D method; when the TSV diameter is 33  $\mu$ m, the TSV pitch is 250  $\mu$ m, the TSV dioxide thickness is 0.52  $\mu$ m, and the TSV height is 105.2  $\mu$ m. The RDL parameters were calculated using the method cited in [21]. Lumped circuit element values are listed in Tables 1–3. The accuracy and efficiency of the computing method were validated by simulations in Pspice and the measurements of [13].

Table 1. Lumped circuit elements of TSV-TSV noise coupling.

| Component              | Value    |

|------------------------|----------|

| C <sub>tsv-equi</sub>  | 201.3 fF |

| R <sub>tsv</sub>       | 0.001 Ω  |

| L <sub>tsv</sub>       | 20.7 pH  |

| R <sub>sub-equi</sub>  | 928.5 Ω  |

| C <sub>sub-equiv</sub> | 11.2 fF  |

| Component              | Value    |

|------------------------|----------|

| C <sub>tsv-equiv</sub> | 817.5 fF |

| Rtsv                   | 0.001 Ω  |

| Ltsv                   | 20.7 pH  |

| R <sub>sub-equiv</sub> | 879.5 Ω  |

| C <sub>sub-equiv</sub> | 12 fF    |

**Table 2.** Lumped circuit elements of TSV-active circuit noise coupling.

| Length of the Line        | Component               | Value     |

|---------------------------|-------------------------|-----------|

| l <sub>RDL</sub> = 200 μm | R <sub>rdl</sub>        | 0.00672 Ω |

|                           | L <sub>rdl</sub>        | 0.1664 nH |

|                           | C <sub>rdl</sub>        | 7.66 fF   |

|                           | C <sub>rdl-to-sub</sub> | 364.65 fF |

|                           | C <sub>sub-rdl</sub>    | 0.13 fF   |

|                           | R <sub>sub-rdl</sub>    | 836.12 fF |

| l <sub>RDL</sub> = 500 μm | R <sub>rdl</sub>        | 0.0168 Ω  |

|                           | L <sub>rdl</sub>        | 0.42 nH   |

|                           | C <sub>rdl</sub>        | 19.15 fF  |

|                           | C <sub>rdl-to-sub</sub> | 911.64 fF |

|                           | C <sub>sub-rdl</sub>    | 0.33 fF   |

|                           | R <sub>sub-rdl</sub>    | 334.44 Ω  |

Table 3. Lumped circuit elements of the RDL.

#### 3.1. Validation of the Proposed Method

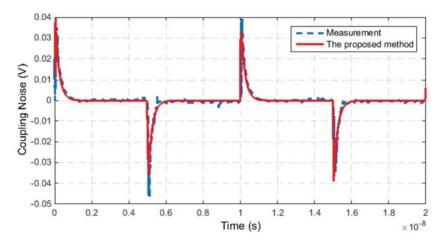

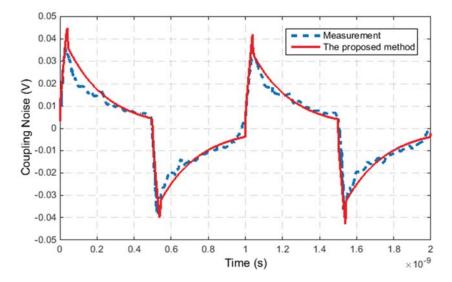

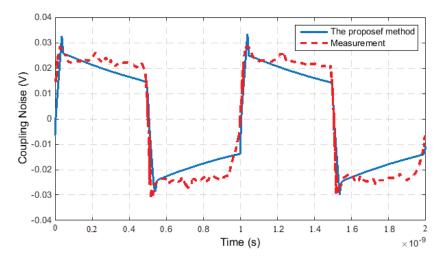

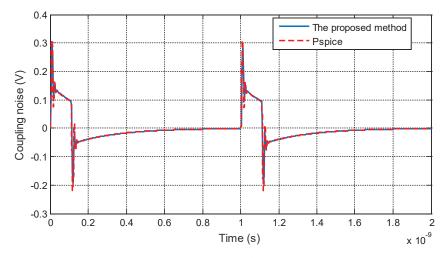

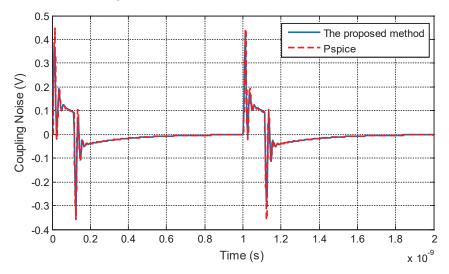

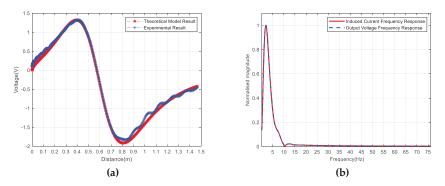

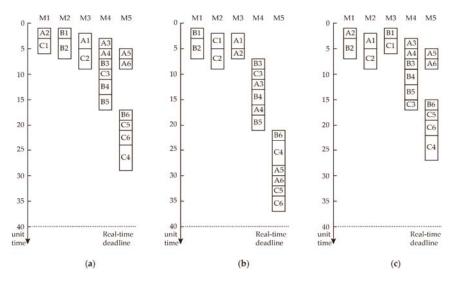

In order to verify the validity of the proposed method, it was applied first to the TSV–TSV and TSV–active circuit noise coupling circuits. The simulated waveforms of the electrical models of Figures 2 and 3 are shown in Figures 9–11. A trapezoidal signal switching from 0 to 1.8 V with a rising/falling time of 40 ps and a source resistance of 50  $\Omega$  at frequencies 100 MHz and 1 GHz is used. For a first test,  $Z_1$ ,  $Z_2$ ,  $Z_3$ , and  $Z_4$  were replaced by resistances of 50  $\Omega$ .

Figure 9. The proposed method and measured coupling of the TSV-TSV test vehicle (the input clock frequency is 100 MHz).

**Figure 10.** The proposed method and measured coupling of the TSV–TSV test vehicle (the input clock frequency at port 1 is 1 GHz).

**Figure 11.** The proposed method and measured coupling noise of the TSV–active circuit (the input clock frequency at port 1 is 1 GHz).

Based on the results reported in the figures, it can be seen that the proposed method is in good agreement with the experiments. By analyzing these results, one can see that the proposed method is valid.

#### 3.2. Time-Domain Analysis of the Coupling Noise with I/O Drivers Load

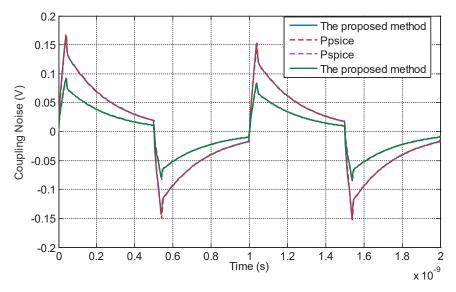

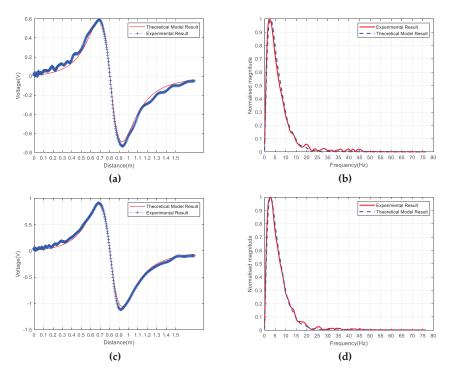

In Figures 9–11, the TSV coupling noise was computed based on the assumption that all TSVs are terminated with 50  $\Omega$ . However, TSVs are usually terminated with I/O drivers; therefore, the TSV I/O terminations must be considered as mentioned before. For the analysis,  $Z_2$  and  $Z_4$  were replaced by a capacitance of 10 fF. Figure 11 depicts the TSV–TSV noise coupling for a trapezoidal signal switching

from 0 to 1 V and from 0 to 1.8 V. The results show that the coupling noise increases when  $Z_2$  and  $Z_4$  are replaced by the capacitances. The peak-to-peak coupling noise increases from 80 mV (Figure 10) to 170 mV (Figure 12). The peak-to-peak coupling noise increases from 170 mV to 310 mV when the source changes from 1 V to 1.8 V. These results imply that the type of termination and the source significantly affects the coupling noise. The TSV I/O buffer size also influences TSV noise coupling and must be considered.

Figure 12. The proposed method and Pspice simulation of the coupling noise of TSV–TSV ( $V_{in} = 1 V$  and 1.8 V).

The RDL redistributes the signals to connect I/Os or power/ground when two different dies with via-last processed TSVs are integrated vertically. Therefore, for advanced 3D-IC design, analyzing TSV noise coupling with RDLs is very important.

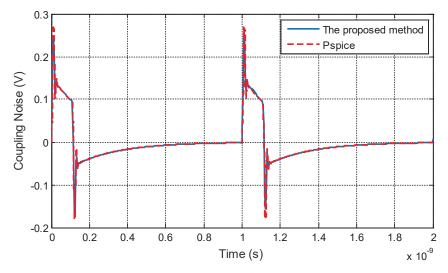

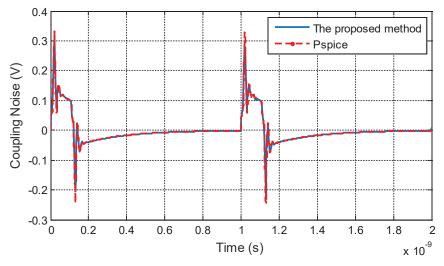

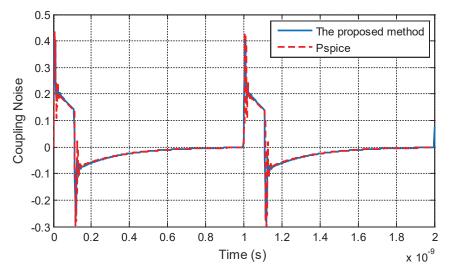

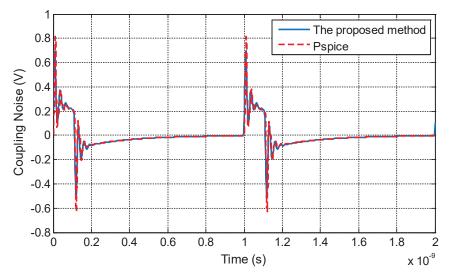

The results found for the circuit presented in Figure 5 are illustrated in Figures 13–16 separately for  $l_{\text{RDL}} = 200 \ \mu\text{m}$  and  $l_{\text{RDL}} = 500 \ \mu\text{m}$ . These results present the TSV noise coupling without the coupling among the RDLs. A trapezoidal signal switching from 0 to 1.8 V with a rising/falling time of 10 ps and a source resistance of 50  $\Omega$  at frequency 1 GHz was used,  $Z_1$  and  $Z_3$  were replaced by resistances of 50  $\Omega$ , and  $Z_2$  and  $Z_4$  were replaced by capacitances of 10 fF.

**Figure 13.** The proposed method and Pspice simulation of the TSV–TSV coupling noise with uncoupled RDLs ( $l_{\text{RDL}} = 200 \ \mu\text{m}$ ) at port 4.

Figure 14. The proposed method and Pspice simulation of the TSV–TSV coupling noise with uncoupled RDLs ( $l_{RDL}$  = 500 µm) at port 4.

**Figure 15.** The proposed method and Pspice simulation of the TSV–TSV coupling noise with uncoupled RDLs ( $l_{\text{RDL}} = 200 \ \mu\text{m}$ ) at port 3.

**Figure 16.** The proposed method and Pspice simulation of the TSV–TSV coupling noise with uncoupled RDLs ( $l_{\text{RDL}} = 500 \ \mu\text{m}$ ) at port 3.

It is observed that the coupling noise spreads on the stacked dies through used interconnections. The peak-to-peak coupling noise increases from 50 mV to 80 mV when the length of the interconnect line (RDL) changes. It is also observed that both ports 3 and 4, which represent, respectively, the input and the output drivers, are affected by the coupling noise. By analyzing the obtained results, the presence of horizontal interconnections can add the coupling noise.

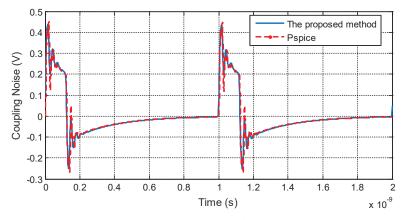

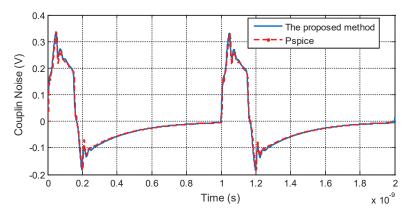

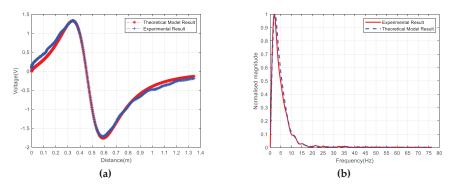

In high frequencies, coupling among the horizontal interconnections cannot be neglected. Indeed, a study including the coupling between the RDLs was done. The obtained results based on Figure 6 are depicted in Figures 17–19.

**Figure 17.** The proposed method and Pspice simulation of the TSV–TSV coupling noise with coupled RDLs ( $l_{RDL} = 200 \ \mu m$  and  $t_r = 10 \ ps$ ) at port 4.

**Figure 18.** The proposed method and Pspice simulation of the TSV–TSV coupling noise with coupled RDLs ( $l_{RDL} = 500 \ \mu m$  and  $t_r = 10 \ ps$ ) at port 4.

**Figure 19.** The proposed method and Pspice simulation of the TSV–TSV coupling noise with RDL ( $l_{RDL} = 500 \ \mu m$  and  $t_r = 20 \ ps$ ) at port 4.

The simulations were done for different RDL lengths and several rise/fall time values. The noise was studied only at port 4.

Observing Figures 13 and 17, the peak-to-peak coupling noise increases when the coupling between RDLs is added. In addition, comparing the results of Figures 17 and 18, the peak-to-peak coupling noise increases when the RDL length increases. Simulation results of these case studies imply that, when the RDL length increases, the effect of the substrate elements among RDLs increases, and R<sub>RDL</sub> and L<sub>RDL</sub> change. Thus, the losses from the RDL are significant.

In a similar manner to the previous analysis, the effect of the rise/fall time variation is depicted in Figures 18–20. The results show that, as  $t_r$  increases from 10 ps to 20 ps and from 20 ps to 50 ps, pick-to-pick coupling noise decreases, respectively, from 1400 mV to 700 mV and from 700 mV to 550 mV. As a result, the rise/fall time is one of the most important factors that affect the TSV–TSV noise coupling in 3D-IC design.

**Figure 20.** The proposed method and Pspice simulation of the TSV–TSV coupling noise with RDL ( $l_{RDL} = 500 \ \mu m$  and  $t_r = 50 \ ps$ ) at port 4.

In summary, the method proposed to compute the coupling noise was validated using measurements and the Pspice and Matlab tools. Then, the time-domain analysis for several factors that must be considered was done.

#### 4. Conclusions

In this paper, a method to compute the time-domain coupling noise in 3D-IC design has been proposed and explained in detail. The proposed method is based on 1D-NILT and chain matrices. It is effective and simple to apply. The used technique was validated using measurements of [13] and the Pspice tool.

The advantage of the proposed method is to compute the coupling noises of 3D structures based on TSVs, since transition phenomena are better observed in the time domain and not in the frequency domain.

A time domain analysis was done using several factors, such as different types of I/O drivers, the coupling between the horizontal interconnections, and the rise/fall time of the source. It was found that the type and the size of the TSV I/O buffer significantly influence the coupling noise. In addition, the presence of coupling between horizontal interconnections increases the noise at components of the 3D structures. These noises must be taken into consideration and must be minimized.

Author Contributions: Data curation, K.A.B.; Investigation, K.A.B. and H.B.; Methodology, K.A.B. and H.B.; Resources, K.A.B.; Supervision, H.B. and H.A.; Validation, H.B.; Writing—original draft, K.A.B.; Writing—review and editing, K.A.B. and H.B.

Funding: This research received no external funding.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Meindl, J.D.; Chen, Q.; Davis, J.A. Limits on Silicon Nanoelectronics for Terascale Integration. *Comput. Sci.* 2001, 293, 2044–2049. [CrossRef] [PubMed]

- 2. Borkar, S. Design Challenges of Technology Scaling. IEEE Micro. 1991, 19, 23–29. [CrossRef]

- 3. Lee, M.; Pak, J.S.; Kim, J. *Electrical Design of through Silicon Via*; Springer: Dordrecht, The Netherlands; Heidelberg, Germany; New York, NY, USA; London, UK, 2014.

- Koester, S.J.; Young, A.M.; Yu, R.R.; Purushothaman, S.; Chen, K.-N.; La Tulipe, D.C.; Rana, N.; Shi, L.; Wordeman, M.R.; Sprogis, E.J. Wafer-level 3D integration technology. *IBM J. Res. Dev.* 2008, 52, 583–597. [CrossRef]

- Knicherbacker, J.U.; Andry, P.S.; Dang, B.; Horton, R.R.; Interrante, M.J.; Patel, C.S.; Polastre, R.J.; Sakuma, K.; Sirdeshmukh, R.; Sprogis, E.J.; et al. Three-dimensional silicon integration. *IBM J. Res. Dev.* 2008, 52, 553–569. [CrossRef]

- 6. Garrou, P.E. Wafer-level 3D integration moving forward. Semicond. Int. 2006, 29, 12–17.

- Cadix, L.; Fuchs, C.; Rousseau, M.; LeDuc, P.; Chaabouni, H.; Thuaire, A.; Brocard, M.; Valentian, A.; Farcy, A.; Bermond, C.; et al. Integration and frequency dependent parametric modeling of Through Silicon Via involved in high density 3D chip stacking. *ECS Trans.* 2010, *33*, 1–21.

- Ryu, C.; Lee, J.; Lee, H.; Lee, K.; Oh, T.; Kim, J. High Frequency Electrical Model of through Wafer Via for 3D Stacked Chip Packaging. In Proceedings of the ESTC, Dresden, Germany, 5–7 September 2006; pp. 215–220.

- Bandyopadhyay, T.; Han, K.J.; Chung, D.; Chatterjee, R.; Swaminathan, M.; Tummala, R. Rigorous Electrical Modeling of TSVs with MOS Capacitance Effects. *IEEE Trans. Compon. Packag. Manuf. Technol.* 2011, 1, 893–903. [CrossRef]

- Liu, E.X.; Li, E.P.; Ewe, W.B.; Lee, H.M.; Lim, T.G.; Gao, S. Compact Wideband Equivalent Circuit Model for Electrical Modeling of TSV. *IEEE Trans. Microw. Theory Tech.* 2011, 59, 1454–1460.

- Katti, G.; Stucchi, M.; Meyer, K.D.; Dehaene, W. Electrical Modeling and Characterization of TSV for 3D-ICs. IEEE Trans. Electron Devices 2010, 57, 256–262. [CrossRef]

- Xu, C.; Kourkoulos, V.; Suaya, R.; Banerjee, K. A Fully Analytical Model for the Series Impedance of TSV with Consideration of Substrate Effects and Coupling with Horizontal Interconnects. *IEEE Trans. Electron Devices* 2011, 58, 3529–3540. [CrossRef]

- Cho, J.; Song, E.; Yoon, K.; Pak, J.S.; Kim, J.; Lee, W.; Song, T.; Kim, K.; Lee, J.; Lee, H.; et al. Modeling and Analysis of TSV Noise Coupling and Suppressing Using a Guard Ring. *IEEE Trans. Compon. Packag. Manuf. Technol.* 2011, 1, 220–233. [CrossRef]

- Lim, J.; Cho, J.; Jung, D.H.; Kim, J.J.; Choi, S.; Kim, D.H.; Lee, M.; Kim, J. Modeling and analysis of TSV noise coupling effects on RFLC-VCO and shielding structures in 3D-IC. *IEEE Trans. Electromagn. Compat.* 2018, 60, 1939–1947. [CrossRef]

- Rimolo-Donadio, R.; Gu, X.; Kwark, Y.; Ritter, M.; Archambeault, B.; De Paulis, F.; Zhang, Y.; Fan, J.; Bruns, H.-D.; Schuster, C. Physics-based via and trace models for efficient link simulation on multilayer structures up to 40 GHz. *IEEE Trans. Microw. Theory Tech.* 2009, *57*, 2072–2083. [CrossRef]

- Han, K.J.; Swaminathan, M.; Bandyopadhyay, T. Electromagnetic modeling of through-silicon via (TSV) interconnections using cylindrical modal basis functions. *IEEE Trans. Adv. Packag.* 2010, 33, 804–817. [CrossRef]

- 17. Beanato, G.; Gharibdoust, K.; Cevrero, A.; De Micheli, G.; Leblebici, Y. Design and analysis of jitter-aware low-power and high-speed TSV link for 3D-ICs. *Microelectron. J.* **2016**, *48*, 50–59. [CrossRef]

- Attarzadeh, H.; Lim, S.K.; Ytterdal, T. Design and Analysis of a Stochastic Flash Analog-to-Digital Converter in 3D-IC technology for integration with ultrasound transducer array. *Microelectron. J.* 2016, 48, 39–49. [CrossRef]

- Bamberg, L.; Najafi, A.; García-Ortiz, A. Edge effects on the TSV array capacitances and their performance influence. *Integration* 2018, *61*, 1–10. [CrossRef]

- 20. Xu, C.; Li, H.; Suaya, R.; Banerjee, K. Compact AC modeling and performance analysis of through-silicon vias in 3D-ICs. *IEEE Trans. Electron. Devices* **2010**, *57*, 3405–3417. [CrossRef]

- Kim, J.; Pak, J.S.; Cho, J.; Song, E.; Cho, J.; Kim, H.; Song, T.; Lee, J.; Lee, H.; Park, K.; et al. High-Frequency scalable electrical model and analysis of Through Silicon Via (TSV). *IEEE Trans. Compon. Packag. Manuf. Technol.* 2011, 1, 181–195.

- Kerns, K.J.; Wemple, I.L.; Yang, A.T. Stable and efficient reduction of substrate model networks using congruence transforms. In Proceedings of the IEEE/ACM International Conference Computer-Aided Design, San Jose, CA, USA, 5–9 November 1995; pp. 207–214.

- Verghese, N.K.; Allstot, D.J.; Masui, S. Rapid simulation of substrate coupling effects in mixed-mode ICs. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Diego, CA, USA, 9–12 May 1993; pp. 18.3.1–18.3.4.

- Shim, Y.; Park, J.; Kim, J.; Song, E.; Yoo, J.; Pak, J.; Kim, J. Modeling and analysis of simultaneous switching noise coupling for a CMOS negative-feedback operational amplifier in system-in-package. *IEEE Trans. Electromagn. Compat.* 2009, 51, 763–773. [CrossRef]

- Koo, K.; Shim, Y.; Yoon, C.; Kim, J.; Yoo, J.; Pak, J.S.; Kim, J. Modeling and analysis of power supply noise imbalance on ultra-high frequency differential low noise amplifiers in a system-in-package. *IEEE Trans. Adv. Packag.* 2010, 33, 602–616. [CrossRef]

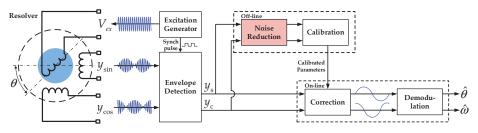

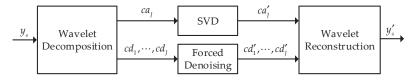

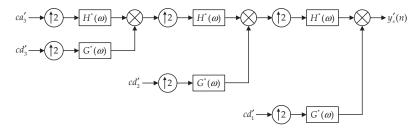

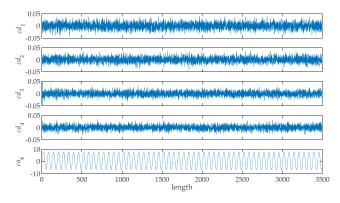

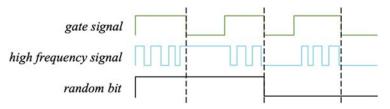

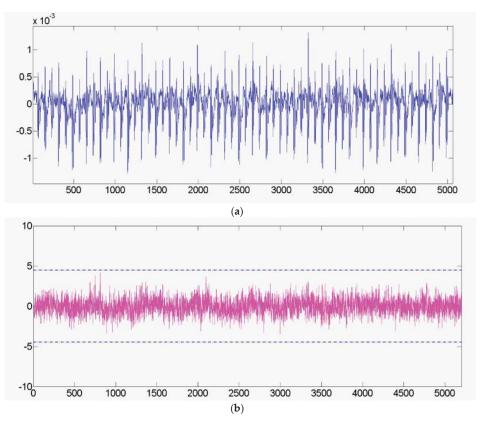

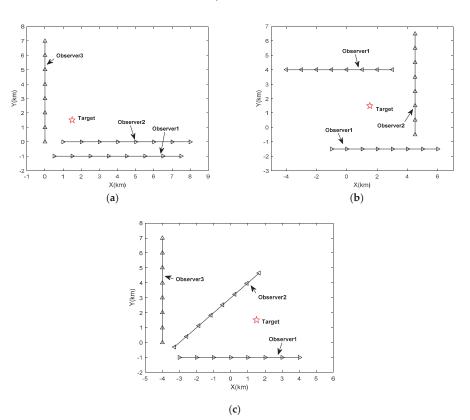

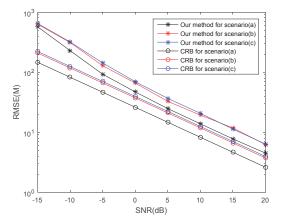

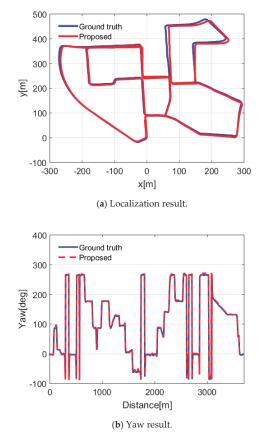

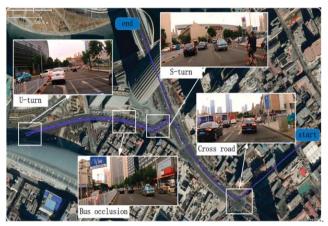

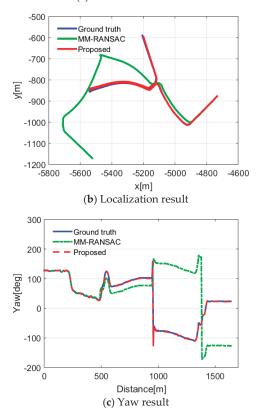

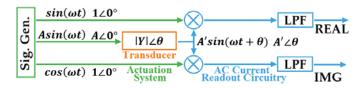

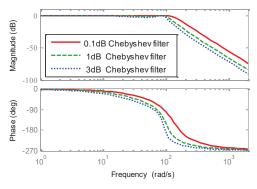

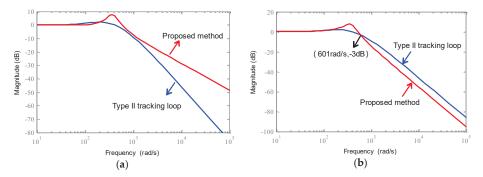

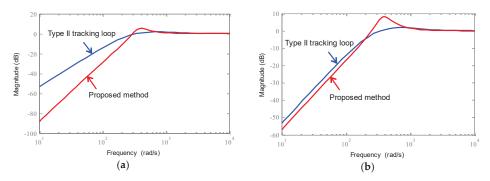

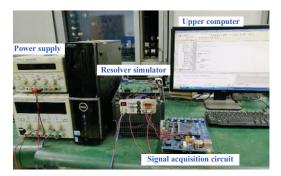

- 26. Li, J.; Farquharson, C.G.; Hu, X. Three effective inverse Laplace transform algorithms for computing time-domain electromagnetic responses. *Geophysics* **2016**, *81*, E113–E128. [CrossRef]