# Advances in High-Efficiency LLC Resonant Converters

Edited by Jeehoon Jung Printed Edition of the Special Issue Published in *Energies*

www.mdpi.com/journal/energies

# Advances in High-Efficiency LLC Resonant Converters

## Advances in High-Efficiency LLC Resonant Converters

Special Issue Editor Jeehoon Jung

$\mathsf{MDPI} \bullet \mathsf{Basel} \bullet \mathsf{Beijing} \bullet \mathsf{Wuhan} \bullet \mathsf{Barcelona} \bullet \mathsf{Belgrade} \bullet \mathsf{Manchester} \bullet \mathsf{Tokyo} \bullet \mathsf{Cluj} \bullet \mathsf{Tianjin}$

Special Issue Editor Jeehoon Jung Ulsan National Institute of Science and Technology (UNIST) Korea

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Energies* (ISSN 1996-1073) (available at: https://www.mdpi.com/journal/energies/special\_issues/LLC\_Resonant\_Converters).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, Article Number, Page Range.

ISBN 978-3-03928-386-6 (Hbk) ISBN 978-3-03928-387-3 (PDF)

© 2020 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## Contents

| About the Special Issue Editor                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "Advances in High-Efficiency LLC Resonant Converters"                                                                                                                                                                                                                                                                |

| HwaPyeong Park, DoKyoung Kim, SeungHo Baek and JeeHoon Jung         Extension of Zero Voltage Switching Capability for CLLC Resonant Converter         Reprinted from: Energies 2019, 12, 818, doi:10.3390/en12050818                                                                                                           |

| Yu-Chen Liu, Chen Chen, Kai-De Chen, Yong-Long Syu and Meng-Chi Tsai         High-Frequency LLC Resonant Converter with GaN Devices and Integrated Magnetics         Reprinted from: Energies 2019, 12, 1781, doi:10.3390/en12091781                                                                                            |

| Yann E. Bouvier, Diego Serrano, Uroš Borović, Gonzalo Moreno, Miroslav Vasić,Jesús A. Oliver, Pedro Alou, José A. Cobos and Jorge CarmenaZVS Auxiliary Circuit for a 10 kW Unregulated LLC Full-Bridge Operating at ResonantFrequency for Aircraft ApplicationReprinted from: Energies 2019, 12, 1850, doi:10.3390/en1210185035 |

| HwaPyeong Park, Mina Kim, HakSun Kim and JeeHoon JungDesign Methodology of Tightly Regulated Dual-Output LLC Resonant Converter UsingPFM-APWM Hybrid Control MethodReprinted from: Energies 2019, 12, 2146, doi:10.3390/en12112146Statement                                                                                     |

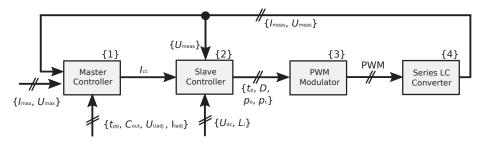

| Michael Heidinger, Qihao Xia, Rainer Kling and Wolfgang Heering<br>Current Mode Control of a Series LC Converter Supporting Constant Current, Constant Voltage<br>(CCCV)<br>Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 2793, doi:10.3390/en12142793                                                              |

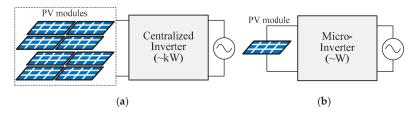

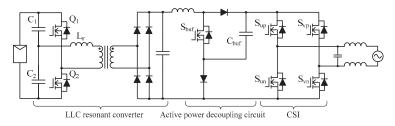

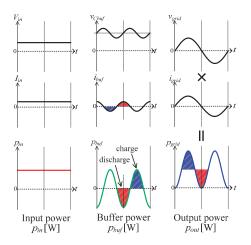

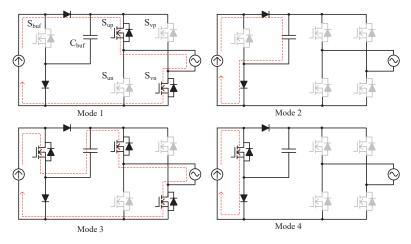

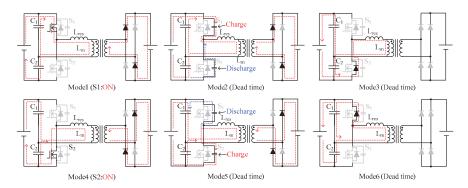

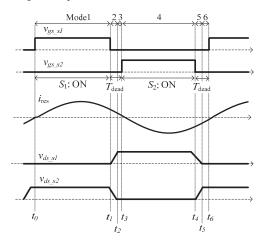

| Hiroki Watanabe, Jun-ichi Itoh, Naoki Koike and Shinichiro Nagai<br>PV Micro-Inverter Topology Using LLC Resonant Converter<br>Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 3106, doi:10.3390/en12163106                                                                                                           |

| Yuan-Chih Lin, Ding-Tang Chen and Ching-Jan Chen         Flux-Balance Control for LLC Resonant Converters with Center-Tapped Transformers         Reprinted from: Energies 2019, 12, 3211, doi:10.3390/en12173211                                                                                                               |

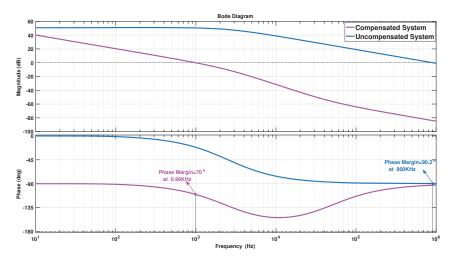

| Hussain Humaira, Seung-Woo Baek, Hag-Wone Kim and Kwan-Yuhl Cho<br>Circuit Topology and Small Signal Modeling of Variable Duty Cycle Controlled Three-Level<br>LLC Converter<br>Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 3833, doi:10.3390/en12203833                                                          |

| Dongkwan Yoon, Sungmin Lee and Younghoon ChoDesign Considerations of Series-Connected Devices Based LLC ConverterReprinted from: Energies 2020, 13, 264, doi:10.3390/en13010264Reprinted from: Energies 2020, 13, 264, doi:10.3390/en13010264                                                                                   |

### About the Special Issue Editor

Jeehoon Jung (Associate Professor, Ph.D.) received his B.S. degree in electronic and electrical engineering and his M.S. and Ph.D. degrees in electrical and computer engineering from the Department of Electronics and Electrical Engineering, Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 2000, 2002, and 2006, respectively. From 2006 to 2009, he was a Senior Research Engineer in the Digital Printing Division, Samsung Electronics Company Ltd., Suwon, South Korea. From 2009 to 2010, he was a Postdoctoral Research Associate in the Department of Electrical and Computer Engineering, Texas A&M University at Qatar (TAMUQ), Doha, Qatar. From 2011 to 2012, he was a Senior Researcher in the Power Conversion and Control Research Center, HVDC Research Division, Korea Electrotechnology Research Institute (KERI), Changwon, South Korea. From 2013 to 2016, he was an Assistant Professor in the School of Electrical and Computer Engineering, Ulsan National Institute of Science and Technology (UNIST), Ulsan, South Korea, where he is currently an Associate Professor. His research interests include dc-dc and ac-dc converters, switched-mode power supplies, motor diagnosis systems, digital control, and signal processing algorithms, power conversion for renewable energy, and real-time and power hardware-in-the-loop (HIL) simulations of renewable energy and power grids. Recently, he has been researching high-frequency power converters using wide bandgap devices, smart power transformers for smart grids, power control algorithms and power line communications for dc microgrids, and induction heating techniques for home appliances. Dr. Jung is a Senior Member of the IEEE Industrial Electronics Society, the IEEE Power Electronics Society, the IEEE Industry Applications Society, and the IEEE Power and Energy Society. He served as a Member of the Editorial Committee of the Korea Institute of Power Electronics (KIPE), Associate Editor of the Journal of Power Electronics (JPE), and now he serves as a Member of the Board of Directors in the KIPE. In addition, he is an Editorial Member of Energies in MDPI.

## Preface to "Advances in High-Efficiency LLC Resonant Converters"

LLC resonant converters have been widely used in industrial fields because of their high efficiency, simple structure, and cost-effectiveness. Many advanced technologies and approaches have been introduced and proposed to improve its power conversion efficiency, dynamic performance, stability, reliability, etc. using enhanced devices such as wide band-gap power switches and high-speed controllers. In addition, new and advanced control algorithms have been applied to the LLC resonant converters.

This book collects several research papers related to the LLC resonant converter, which were published in a Special Issue of *Energies* on the subject area of "Advances in High-Efficiency LLC Resonant converter". This Special Issue focused on emerging power electronic topologies related to the LLC resonant converter, and its design methodology and control algorithms. Topics of interest for publication include the following:

- LLC resonant topologies;

- Resonant tank design methodology for high efficiency;

- · Power loss analysis in LLC resonant converter;

- High-frequency magnetics in LLC resonant converter;

- · Wide band-gap devices applied to LLC resonant converter;

- · Advanced control algorithm for LLC resonant converter

I believe that all the papers in this book will inspire further research topics and other researchers who are participating in the research of the LLC resonant converter. It was my pleasure to contribute to the Special Issue of *Energies* as a Guest Editor.

Jeehoon Jung Special Issue Editor

Article

## **Extension of Zero Voltage Switching Capability for CLLC Resonant Converter**

#### HwaPyeong Park<sup>1</sup>, DoKyoung Kim<sup>2</sup>, SeungHo Baek<sup>2</sup> and JeeHoon Jung<sup>1,\*</sup>

- <sup>1</sup> Ulsan National Institute of Science and Technology (UNIST), Ulsan KS017, Korea; darkrla6@unist.ac.kr

- <sup>2</sup> LIG Nex1, Seongnam KS009, Korea; kimdokyoung@lignex1.com (D.K.); seungho.baek@lignex1.com (S.B.)

- \* Correspondence: jhjung@unist.ac.kr; Tel.: +82-052-217-2140

Received: 18 January 2019; Accepted: 27 February 2019; Published: 1 March 2019

**Abstract:** TheCLLC resonant converter has been widely used to obtain high power conversion efficiency with sinusoidal current waveforms and a soft switching capability. However, it has a limited voltage gain range according to the input voltage variation. The current-fed structure canbe one solution to extend the voltage gain range for the wide input voltage variation, butit has a limited zero voltage switching (ZVS) range. In this paper, the current-fed CLLC resonant converter with additional inductance is proposed to extend the ZVS range. The operational principle is analyzed to design the additional inductance for obtaining the extended ZVS range. The design methodology of the additional inductance is proposed to maximize the ZVS capability for the entire load range. The performance of the proposed method is verified with a 20 W prototype converter.

**Keywords:** resonant converter; bidirectional power conversion; zero voltage switching; asymmetric pulse width modulation

#### 1. Introduction

Recently, the small sized power converterhas become significant in various industries, such as lightings, TVs, computers, and other home appliances [1,2]. A power converter operating at a high switching frequency is one effective method to improve power density [3–7]. However, the high switching frequency operation induces a large switching loss for the turn-on and turn-off states. Therefore, a soft switching capability is important to obtain a high power conversion efficiency in a high switching frequency operation [8–10]. Resonant power converters, such as LC resonance, LLC resonance, CLLC resonance, and CLL resonance, can implement the soft switching capability by the resonance, which can be a good candidate to implement the high switching frequency operation [11–15]. In addition, the wide band-gap device (WBD), such as gallium nitride (GaN) and silicon carbide (SiC), can increase the switching frequency up to several MHz compared with conventional silicon (Si)-based switching devices [16–19].

The CLLC resonant converter operating at the inductive region can obtain zero voltage switching (ZVS) capability [20–23]. However, the large input voltage variation by the batteryinduces large switching frequency variation. In addition, the voltage gain fluctuation makes a non-ZVS operation with the capacitive operation of the converter [24]. Therefore, the CLLC resonant converter has poor voltage gain characteristics according to the wide input voltage variation. The current-fed CLLC resonant converter can overcome the input voltage variation by the battery, since the current-fed structure compensates the input voltage variation [25,26]. However, the current-fed structure makes a limited ZVS capability of the low side switch, since the low side switch operates as the boost converter and resonant converter simultaneously. Therefore, the increase of the ZVS capability is significant to obtain a high power conversion efficiency for the entire load condition.

In this paper, the current-fed CLLC resonant converter employing the additional inductance is proposed to improve the ZVS capability. The operational principle of the proposed additional inductance is analyzed with the theoretical waveforms. From the operational principle, the design methodology of the additional inductance is analyzed to obtain the ZVS capability for the entire input voltage range and load conditions. The experimental results with a 20 W prototype converter verify the validity of the proposed additional inductance.

#### 2. Operational Principle

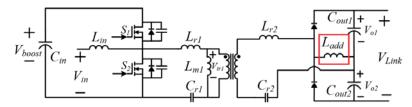

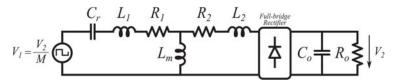

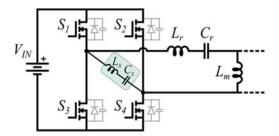

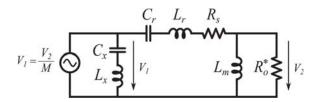

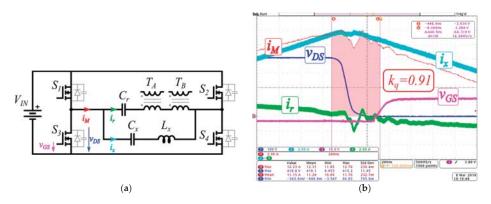

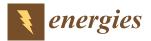

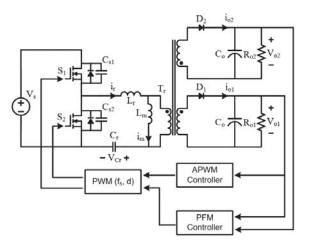

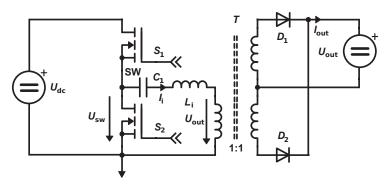

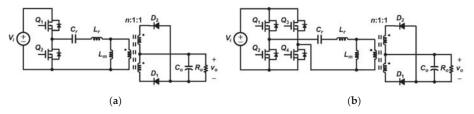

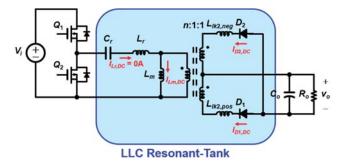

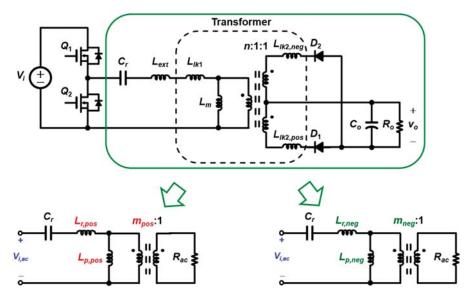

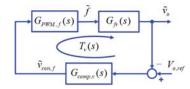

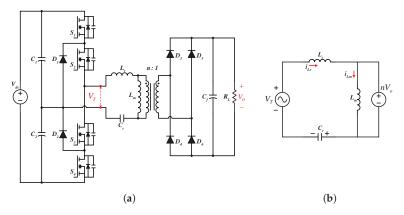

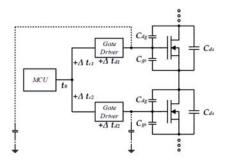

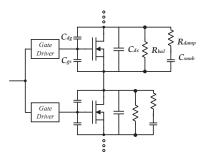

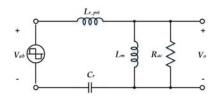

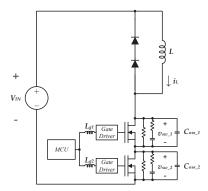

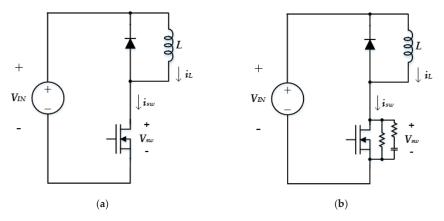

Figure 1 shows the scheme of the proposed current-fed CLLC resonant converter. The current-fed structure regulates the wide input voltage variation with the asymmetric pulse width modulation (APWM), because it operates as the synchronous boost converter. The CLLC resonant tank provides the galvanic isolation using the transformer and resonance. The voltage doubler structure of the secondary side can reduce the turn ratio of the transformer.

Figure 1. Schematic of the proposed CLLC resonant converter employing additional inductance.

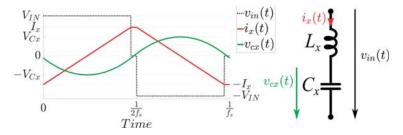

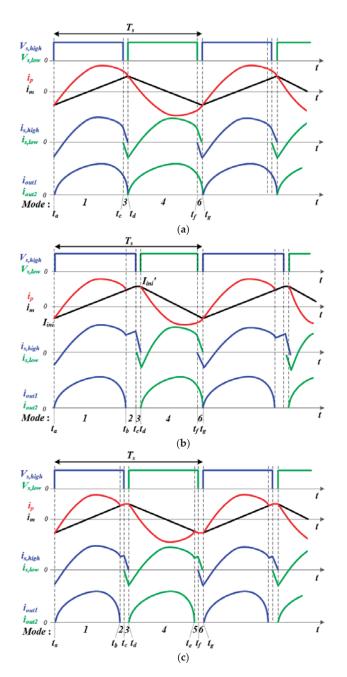

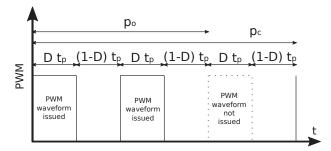

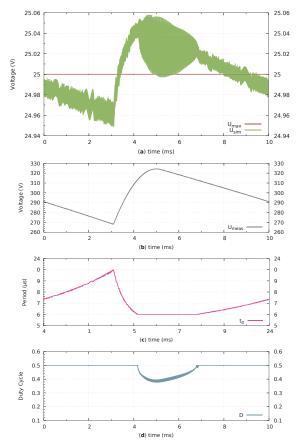

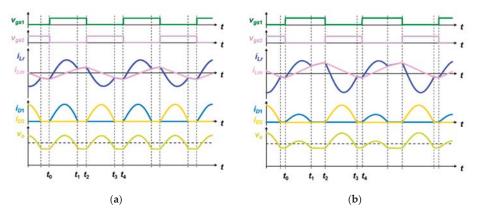

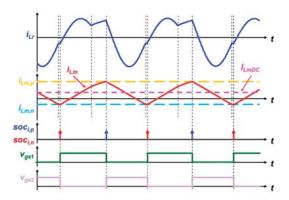

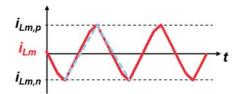

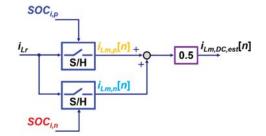

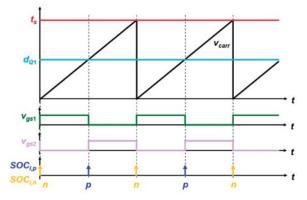

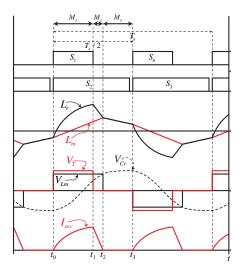

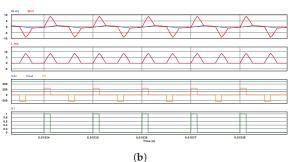

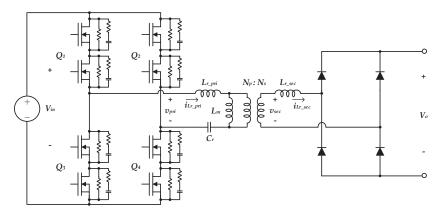

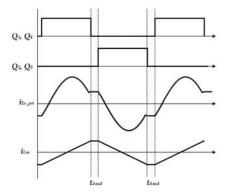

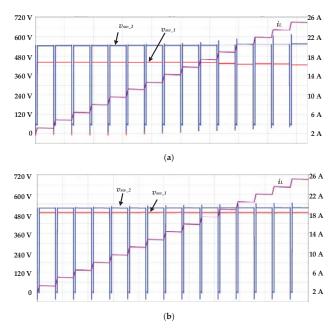

Figure 2 shows the operational waveform of the conventional and the proposed current-fed CLLC resonant converter where  $S_1$  and  $S_2$  are the primary switches,  $V_{ds,S1}$  and  $V_{ds,S2}$  is the drain-source voltage of  $S_1$  and  $S_2$ , respectively,  $I_{Lin}$  is the current passing through the input inductor,  $I_{r,p}$  is the resonant current in the primary side,  $I_{Lm}$  is the magnetizing current,  $I_{S1}$  and  $I_{S2}$  are the currents passing through  $S_1$  and  $S_2$ , respectively, and  $I_{Ladd}$  is the current in the additional inductance. The current-fed structure operates as the conventional boost converter by the switching operation of  $S_1$  and  $S_2$ . The CLLC resonant tank employing the APWM has zero offset current on the magnetizing inductance which reduces the core and conduction losses of the transformer.

The current-fed structure is proper to compensate the wide input voltage variation. However, it limits the ZVS range according to the increase of the output load. The switch current of conventional voltage-fed CLLC resonant converter for the ZVS capability can be derived as follows:

$$ZVS_{S1} = I_r \Big( t_{S2,off} \Big) \tag{1}$$

$$ZVS_{S2} = -I_r \left( t_{S1,off} \right) \tag{2}$$

where  $I_r(t_{s2,off})$  and  $I_r(t_{s1,off})$  are the resonant current at the turn off state of power switches, respectively. The negative current of each switch is required to obtain the ZVS condition. In the voltage-fed CLLC resonant converter, the resonant current onlydetermines the ZVS condition of each switch. In the case of the current-fed CLLC resonant converter, the input inductor and resonant currents determine the ZVS current. The switch current of the current-fed CLLC resonant converter for the ZVS capability can be derived as follows:

$$ZVS_{S1,c} = I_r \left( t_{S2,off} \right) - I_{Lin} \left( t_{s2,off} \right)$$

(3)

$$ZVS_{S2,c} = -I_r \left( t_{S1,off} \right) + I_{Lin} \left( t_{s1,off} \right)$$

(4)

where  $I_{Lin}(t_{s2,off})$  and  $I_{Lin}(t_{s2,off})$  are the input inductor current at the turn off state of power switches, respectively. The high side switch ( $S_1$ ) has a larger ZVS condition compared with Equation (1). However, the low side switch ( $S_2$ ) has a poor ZVS condition compared with Equation (2). Figure 2a shows the theoretical waveforms of the conventional current-fed CLLC resonant converter, whichhas a

Energies 2019, 12, 818

hard switching operation on the  $S_2$ . The ZVS capability of the proposed CLLC resonant converter can be derived as follows:

$$ZVS_{S1,p} = I_r \left( t_{S2,off} \right) - I_{Lin} \left( t_{s2,off} \right) - nI_{Ladd} \left( t_{s2,off} \right)$$

(5)

$$ZVS_{S2,p} = -I_r \left( t_{S1,off} \right) + I_{Lin} \left( t_{s1,off} \right) - nI_{Ladd} \left( t_{s1,off} \right)$$

(6)

where  $I_{Ladd}(t_{s2,off})$  and  $I_{Ladd}(t_{s2,off})$  are the additional inductor currents at the turn off state of power switches, respectively, and *n* is the transformer turn ratio. Figure 2b shows the theoretical waveforms of the proposed CLLC resonant converter. The additional inductance extends the ZVS range compared with the conventional current-fed CLLC resonant converter.

**Figure 2.** Theoretical operating waveforms: (a) Conventional current-fed CLLC resonant converter, (b) Proposed current-fed CLLC resonant converter employing additional inductance.

Energies 2019, 12, 818

The turnon current for the ZVS condition of the current-fed CLLC resonant converter can be calculated with the input inductor current and resonant current. The ZVS condition on the low side switch can be derived as follows:

$$I_{zvs,s2} = \frac{1}{1 - D_{s2}} \frac{V_{boost}}{R} + \frac{(V_{in} - V_{boost})}{2L} (1 - D_{s2}) T_s - \frac{V_{tr1}}{L_m} \frac{1 - D_{s2}}{2} T_s$$

(7)

where  $D_{s_2}$  is the duty ratio of  $S_2$ ,  $V_{boost}$  is the voltage of the current-fed structure,  $V_{in}$  is the input voltage of the battery, R is the load resistance, L is the input inductance,  $T_s$  is the switching time,  $L_m$  is the magnetizing inductance, and  $V_{tr1}$  is the transformer voltage. The negative value of  $I_{zvs,S2}$  guarantees the ZVS capability of  $S_2$ . The decrease of the load resistance makes no ZVS condition of  $S_2$ . In addition, the large duty ratio of  $S_2$  makes the worst ZVS condition, which means that the low input voltage condition is the worst ZVS condition.

The turn on current for ZVS condition of the low side switch with the proposed converter can be derived as follows:

$$I_{zvs,s2,p} = \frac{1}{1 - D_{s2}} \frac{V_{boost}}{R} + \frac{(V_{in} - V_{boost})}{2L} (1 - D_{s2}) T_s - \frac{V_{tr1}}{L_m} \frac{1 - D_{s2}}{2} T_s - \frac{V_{o1}}{nL_{add}} \frac{1 - D_{s2}}{2} T_s$$

(8)

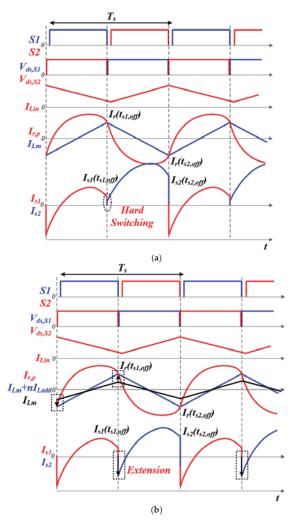

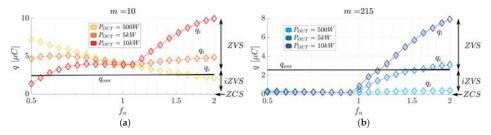

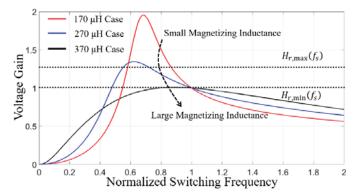

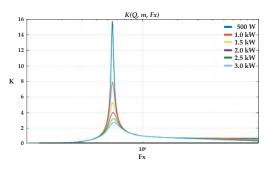

where  $V_{o_1}$  is the voltage on the output capacitor as shown in Figure 1. The proposed converter extends the ZVS condition with the additional inductor on the secondary side as shown in Figure 2b. Figure 3 shows the ZVS capability according to the additional inductance. The ZVS current is the turn on current of  $S_2$ , which is required to have a negative value in order to obtain the ZVS capability. The small additional inductance is proper to extend the ZVS range. However, the small additional inductance increases the conduction loss on the primary side.Therefore, the design methodology of the additional inductance is required to obtain the ZVS capability for the entire load range.

Figure 3. ZVS capability comparison between the conventional current-fed CLLC resonant converter and the proposed current-fed CLLC resonant converter.

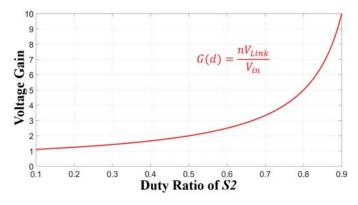

The voltage gain according to the duty ratio can be described in Figure 4. The proposed converter has similar voltage gain to that of the conventional boost converter, which shows wide duty ratio variations to regulate the output voltage. The additional inductance can be designed at the worst duty ratio case, which is the maximum duty ratio of  $S_2$ .

Figure 4. Gain according to duty ratio.

#### 3. Design Methodology of Additional Inductance

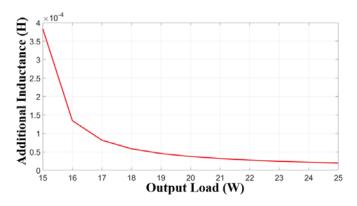

The small additional inductance induces the conduction loss with large circulating current. The large additional inductance cannot obtain the ZVS capability of primary switches. Therefore, the maximum additional inductance is required to obtain the ZVS capability and the minimum conduction loss on the additional inductance, which can be derived with Equation (8) as follows:

$$L_{add} = \frac{V_{o1}}{nA} \frac{1 - D_{s2}}{2} T_s$$

$$A = \frac{1}{1 - D_{s2}} \frac{V_{boost}}{R} + \frac{(V_{in} - V_{boost})}{2L} (1 - D_{s2}) T_s - \frac{V_{tr1}}{L_m} \frac{1 - D_{s2}}{2} T_s$$

(9)

The proper additional inductance can be designed from Equation (9). Figure 5 shows the additional inductance according to the output load condition. The increment of output load requires smaller additional inductance. The design specification is shown in Table 1. The input voltage has a large variation by the state of charge (SOC) of the battery. The load voltage is fixed, and rated load is 20 W. The resonant frequency( $f_r$ ) is 200 kHz. The APWM requires the small resonant inductance to obtain the linear voltage gain according to the duty variation. The turn ratio is determined with the input voltage and output voltage ratio. The additional inductance is determined by (9).

Figure 5. Desired additional inductance to obtain ZVS capability and minimum conduction loss according to output load condition.

| Parameter  | Value      |

|------------|------------|

| Vin        | 12 V–17 V  |

| Load       | 32 V, 20 W |

| fr         | 200 kHz    |

| $L_r$      | 1 µH       |

| $L_m$      | 30 µH      |

| $C_r$      | 633 nF     |

| Turn ratio | 1:1        |

| Ladd       | 25 µH      |

Table 1. Design specification.

#### 4. Simulation and Experimental Results

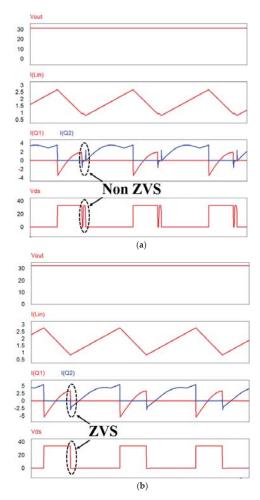

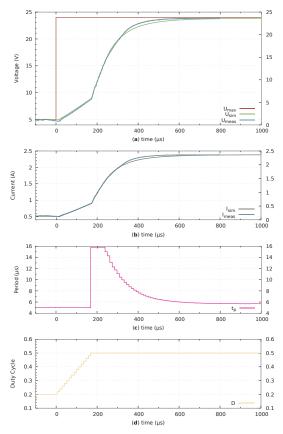

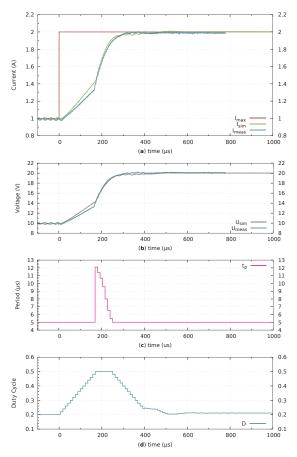

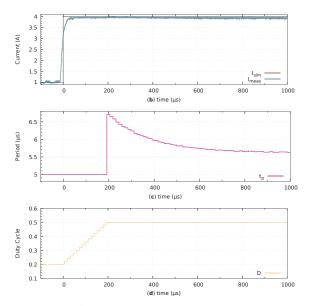

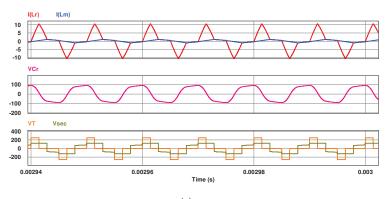

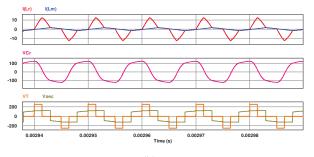

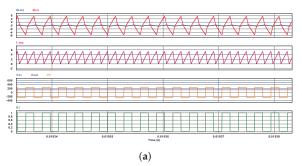

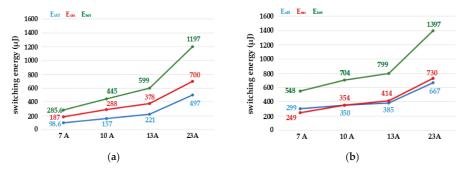

The simulation results show the ZVS capability according to the additional inductance, as shown in Figure 6. The conventional current-fed CLLC resonant converter has no ZVS capability on the bottom side switch. However, the proposed CLLC resonant converter employing the additional inductance can achieve the ZVS condition for both the power switches.

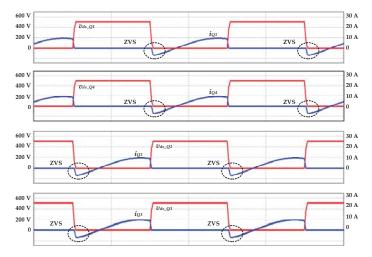

Figure 6. Simulation waveforms to verify ZVS capability: (a) Conventional current-fed CLLC resonant converter; (b) proposed current-fed CLLC resonant converter.

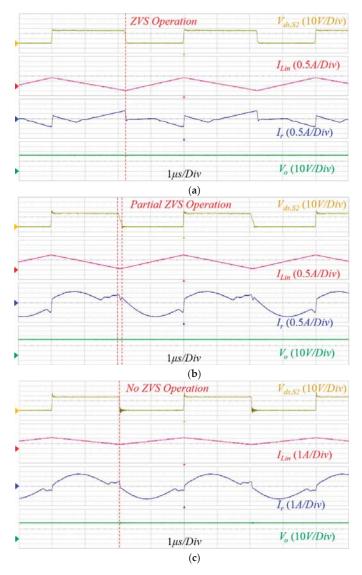

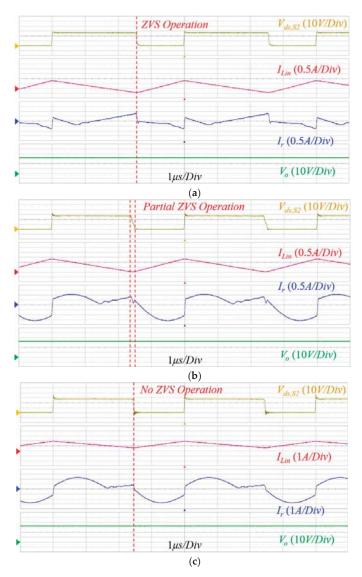

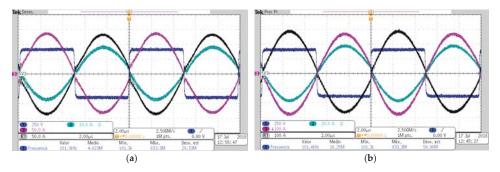

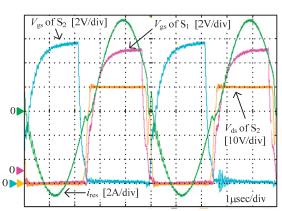

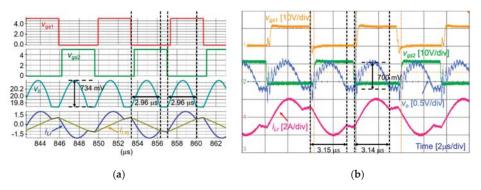

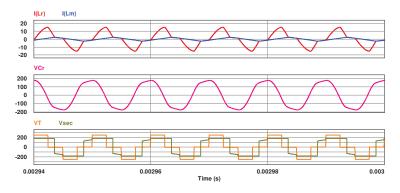

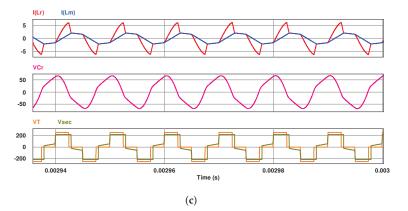

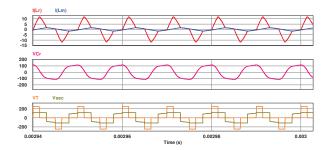

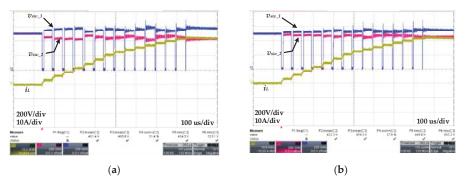

Figures 7–9 show the steady state waveforms of the conventional CLLC resonant converter according to the input voltage variation and load condition. The duty ratio regulates the output voltage according to the load conditions and input voltages. At the light load condition, it shows the ZVS operation. However, the CLLC resonant converter has a partial and no ZVS operation for the middle load and full load conditions, respectively. For allthe input voltage range, the ZVS can be achieved at only the light load condition.

**Figure 7.** Experimental waveforms of the conventional CLLC resonant converter at 12 V condition: (a) 2 W light load condition; (b) 10 W middle load condition; (c) 20 W full load condition.

**Figure 8.** Experimental waveforms of the conventional CLLC resonant converter at 14 V condition: (a) 2 W light load condition; (b) 10 W middle load condition; (c) 20 W full load condition.

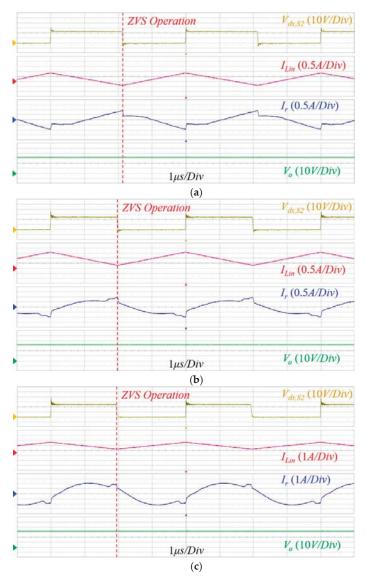

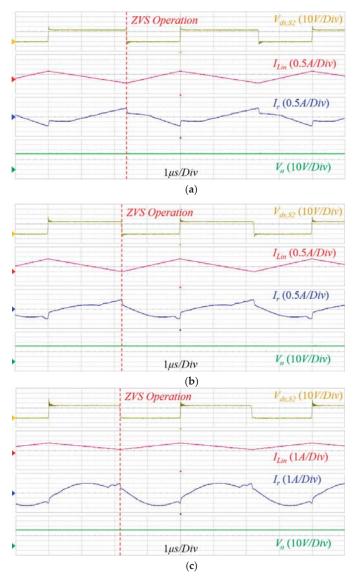

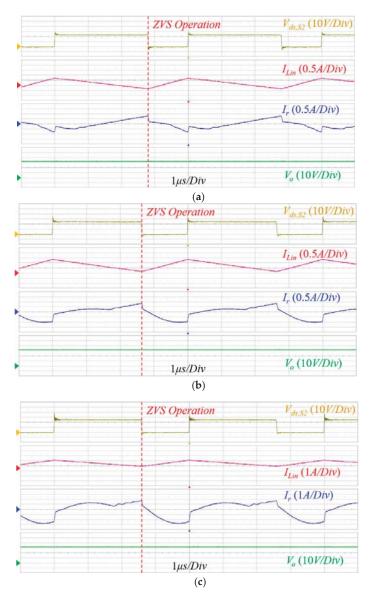

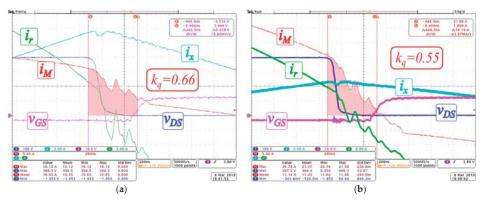

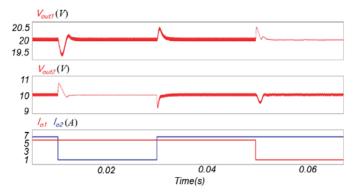

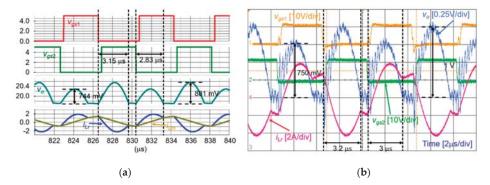

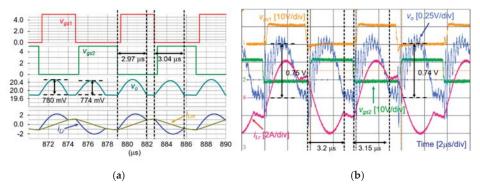

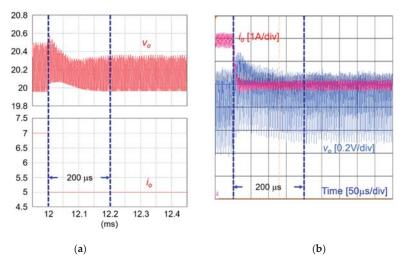

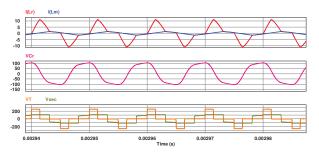

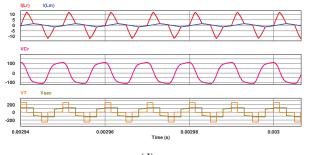

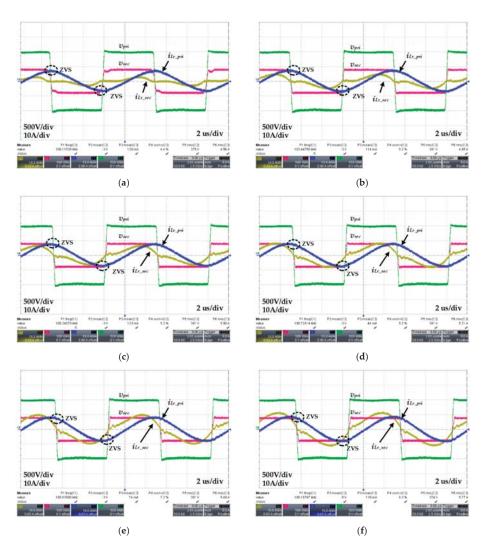

Figures 10–12 show the steady state waveforms of the proposed CLLC resonant converter according to the input voltages and load conditions. The proposed converter shows the ZVS operation for the entire load and input voltage conditions. The extended soft switching capability improves the power conversion efficiency compared with the partial or no ZVS cases. The power loss of the partial and no ZVS cases can be calculated as follows:

$$P_{noZVS} \cong \frac{1}{2} V_{ds,c} I_{on} t_{on} f_{sw} \tag{10}$$

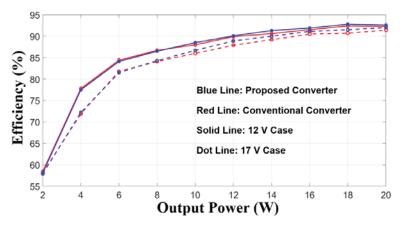

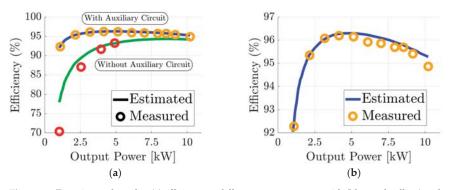

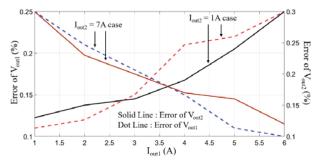

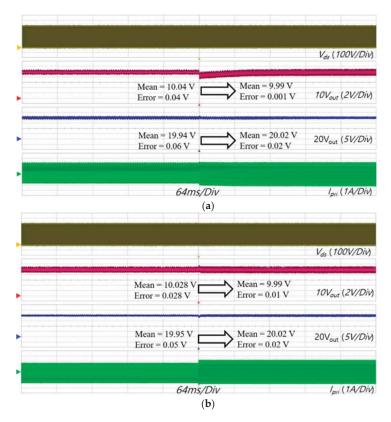

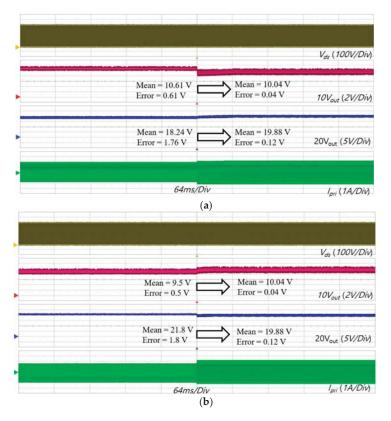

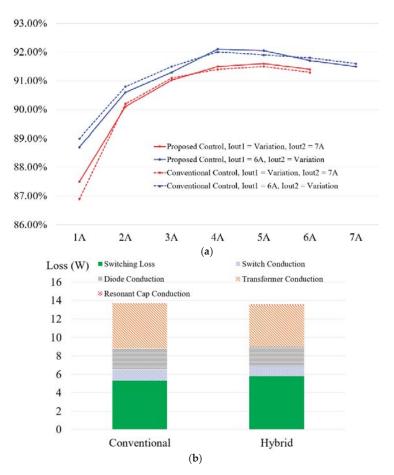

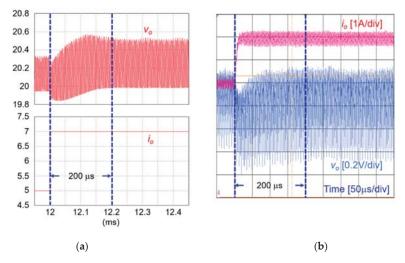

where  $P_{noZVS}$  is the power loss according to the partial or no ZVS conditions,  $V_{ds,c}$  is the drain-source voltage at the turn on state,  $I_{on}$  is the switch current at the turn on state,  $t_{on}$  is the turn on time duration, and  $f_{sw}$  is the switching frequency. Figure 13 shows the comparison of the power conversion efficiency between the conventional current-fed CLLC resonant converter and the proposed converter. For the light load condition, the proposed and conventional methods can obtain ZVS capability at the light load condition, which makes no difference in terms of the efficiency. However, the proposed converter has a higher power conversion efficiency for the middle to full load conditions. The maximum improvement of power conversion efficiency is 1% at the middle load condition.

**Figure 9.** Experimental waveforms of the conventional CLLC resonant converter at 17 V condition: (a) 2 W light load condition; (b) 10 W middle load condition; (c) 20 W full load condition.

**Figure 10.** Experimental waveforms of the proposed CLLC resonant converter at 12 V condition: (a) 2 W light load condition; (b) 10 W middle load condition; (c) 20 W full load condition.

**Figure 11.** Experimental waveforms of the proposed CLLC resonant converter at 14 V condition: (a) 2 W light load condition; (b) 10 W middle load condition; (c) 20 W full load condition.

**Figure 12.** Experimental waveforms of the proposed CLLC resonant converter at 17 V condition: (a) 2 W light load condition; (b) 10 W middle load condition; (c) 20 W full load condition.

Figure 13. Power conversion efficiency curves.

#### 5. Conclusions

A soft switching capability can improve the power conversion efficiency of the power converter. In this paper, the current-fed CLLC resonant converter employing the additional inductance is proposed to extend the ZVS capability. The operational principle and the design methodology of the additional inductance are analyzed to obtain the soft switching capability for the entire load and input voltage conditions. The simulation and experimental results verify the soft switching performance of the proposed CLLC resonant converter compared with the conventional converter. The maximum efficiency improvement using the proposed converter is 1% at the middle load condition.

Author Contributions: Conceptualization, H.P., J.J.; Methodology, H.P.; Software, H.P.; Validation, H.P.; Resources, D.K., S.B., J.J.; Writing-Original Draft Preparation, H.P.; Writing-Review & Editing, J.J.; Supervision, D.K., J.J.; Project Administration, D.K., S.B.; Funding Acquisition, J.J.

Funding: This research is performed based on the cooperation with UNIST-LIG Nex1 Cooperation.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. De Doncker, R.W.; Divan, D.M.; Kheraluwala, M.H. A three-phase soft-switched high-power-density DC/DC converter for high-power applications. *IEEE Trans. Ind. Appl.* **1991**, *27*, 63–73. [CrossRef]

- Liu, Y.-C.; Chen, M.-C.; Yang, C.-Y.; Kim, K.A.; Chiu, H.-J. High-Efficiency Isolated Photovoltaic Microinverter Using Wide-Band Gap Switches for Standalone and Grid-Tied Applications. *Energies* 2018, 11, 569. [CrossRef]

- Zaman, H.; Wu, X.; Zheng, X.; Khan, S.; Ali, H. Suppression of Switching Crosstalk and Voltage Oscillations in a SiC MOSFET Based Half-Bridge Converter. *Energies* 2018, 11, 3111. [CrossRef]

- Pilawa-Podgurski, R.C.N.; Sagneri, A.D.; Rivas, J.M.; Anderson, D.I.; Perreault, D.J. Very-High-Frequency Resonant Boost Converters. *IEEE Trans. Power Electron.* 2009, 24, 1654–1665. [CrossRef]

- Reusch, D.; Strydom, J. Understanding the Effect of PCB Layout on Circuit Performance in a High-Frequency Gallium-Nitride-Based Point of Load Converter. *IEEE Trans. Power Electron.* 2014, 29, 2008–2015. [CrossRef]

- Kaiwei, Y.; Yang, Q.; Ming, X.; Lee, F.C. A novel winding-coupled buck converter for high-frequency, high-step-down DC-DC conversion. *IEEE Trans. Power Electron.* 2005, 20, 1017–1024.

- Meng, Z.; Wang, Y.-F.; Yang, L.; Li, W. High Frequency Dual-Buck Full-Bridge Inverter Utilizing a Dual-Core MCU and Parallel Algorithm for Renewable Energy Applications. *Energies* 2017, 10, 402. [CrossRef]

- Huang, R.; Mazumder, S.K. A Soft-Switching Scheme for an Isolated DC/DC Converter With Pulsating DC Output for a Three-Phase High-Frequency-Link PWM Converter. *IEEE Trans. Power Electron.* 2009, 24, 2276–2288. [CrossRef]

- Liu, X.; Liu, J.; Wang, J.; Wang, C.; Yuan, X. Design Method for the Coil-System and the Soft Switching Technology for High-Frequency and High-Efficiency Wireless Power Transfer Systems. *Energies* 2018, 11, 7. [CrossRef]

- Liu, K.H.; Lee, F.C. Zero-voltage switching technique in DC/DC converters. *IEEE Trans. Power Electron.* 1990, 5, 293–304. [CrossRef]

- Lin, B.-R.; Wu, G.-Y. Bidirectional Resonant Converter with Half-Bridge Circuits: Analysis, Design, and Implementation. *Energies* 2018, 11, 1259. [CrossRef]

- 12. Lin, B.-R. Investigation of a Resonant dc–dc Converter for Light Rail Transportation Applications. *Energies* **2018**, *11*, 1078. [CrossRef]

- Zhang, S.-H.; Luo, F.-Z.; Wang, Y.-F.; Liu, J.-H.; He, Y.-P.; Dong, Y. Control Method Based on Demand Response Needs of Isolated Bus Regulation with Series-Resonant Converters for Residential Photovoltaic Systems. *Energies* 2017, 10, 752. [CrossRef]

- 14. Lin, R.; Huang, L. Efficiency Improvement on LLC Resonant Converter Using Integrated LCLC Resonant Transformer. *IEEE Trans. Ind. Appl.* 2018, *54*, 1756–1764. [CrossRef]

- Tan, X.; Ruan, X. Equivalence Relations of Resonant Tanks: A New Perspective for Selection and Design of Resonant Converters. *IEEE Trans. Ind. Electron.* 2016, 63, 2111–2123. [CrossRef]

- Fayyaz, A.; Romano, G.; Urresti, J.; Riccio, M.; Castellazzi, A.; Irace, A.; Wright, N. A Comprehensive Study on the Avalanche Breakdown Robustness of Silicon Carbide Power MOSFETs. *Energies* 2017, 10, 452. [CrossRef]

- Efthymiou, L.; Camuso, G.; Longobardi, G.; Chien, T.; Chen, M.; Udrea, F. On the Source of Oscillatory Behaviour during Switching of Power Enhancement Mode GaN HEMTs. *Energies* 2017, 10, 407. [CrossRef]

- Seeman, M.D. GaN Devices in Resonant LLC Converters: System-level considerations. *IEEE Power Electron*. Mag. 2015, 2, 36–41. [CrossRef]

- Zhang, W.; Wang, F.; Costinett, D.J.; Tolbert, L.M.; Blalock, B.J. Investigation of Gallium Nitride Devices in High-Frequency LLC Resonant Converters. *IEEE Trans. Power Electron.* 2017, 32, 571–583. [CrossRef]

- Chen, W.; Rong, P.; Lu, Z. Snubberless Bidirectional DC–DC Converter with New CLLC Resonant Tank Featuring Minimized Switching Loss. *IEEE Trans. Ind. Electron.* 2010, 57, 3075–3086. [CrossRef]

- Ryu, M.; Kim, H.; Baek, J.; Kim, H.; Jung, J. Effective Test Bed of 380-V DC Distribution System Using Isolated Power Converters. *IEEE Trans. Ind. Electron.* 2015, *62*, 4525–4536. [CrossRef]

- He, P.; Khaligh, A. Comprehensive Analyses and Comparison of 1 kW Isolated DC–DC Converters for Bidirectional EV Charging Systems. *IEEE Trans. Transp. Electrif.* 2017, 3, 147–156. [CrossRef]

- Zou, S.; Lu, J.; Mallik, A.; Khaligh, A. Bi-Directional CLLC Converter With Synchronous Rectification for Plug-In Electric Vehicles. *IEEE Trans. Ind. Appl.* 2018, 54, 998–1005. [CrossRef]

- Jung, J.; Kim, H.; Ryu, M.; Baek, J. Design Methodology of Bidirectional CLLC Resonant Converter for High-Frequency Isolation of DC Distribution Systems. *IEEE Trans. Power Electron.* 2013, 28, 1741–1755. [CrossRef]

- Zhang, C.; Li, P.; Kan, Z.; Chai, X.; Guo, X. Integrated Half-Bridge CLLC Bidirectional Converter for Energy Storage Systems. *IEEE Trans. Ind. Electron.* 2018, 65, 3879–3889. [CrossRef]

- Sun, X.; Shen, Y.; Zhu, Y.; Guo, X. Interleaved Boost-Integrated LLC Resonant Converter with Fixed-Frequency PWM Control for Renewable Energy Generation Applications. *IEEE Trans. Power Electron.* 2015, 30, 4312–4326. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

## High-Frequency LLC Resonant Converter with GaN Devices and Integrated Magnetics

#### Yu-Chen Liu<sup>1,\*</sup>, Chen Chen <sup>2</sup>, Kai-De Chen <sup>2</sup>, Yong-Long Syu<sup>2</sup> and Meng-Chi Tsai<sup>1</sup>

- <sup>1</sup> Department of Electrical Engineering, National Ilan University, No. 1 Section 1 Shennong Road, Yilan 260, Taiwan; kid3181910@gmail.com

- <sup>2</sup> Department of Electronic Engineering, National Taiwan University of Science, and Technology, No. 43 Section 4 Keelung Rd Da'an District, Taipei 10607, Taiwan; D10502204@mail.ntust.edu.tw (C.C.); d10502203@mail.ntust.edu.tw (K.-D.C.); x452800@gmail.com (Y.-L.S.)

- \* Correspondence: ycliu@niu.edu.tw

Received: 15 April 2019; Accepted: 5 May 2019; Published: 10 May 2019

Abstract: In this study, a light emitting diode (LED) driver containing an integrated transformer with adjustable leakage inductance in a high-frequency isolated LLC resonant converter was proposed as an LED lighting power converter. The primary- and secondary-side topological structures were analyzed from the perspectives of component loss and component stress, and a full-bridge structure was selected for both the primary- and secondary-side circuit architecture of the LLC resonant converter. Additionally, to achieve high power density and high efficiency, adjustable leakage inductance was achieved through an additional reluctance length, and the added resonant inductor was replaced with the transformer leakage inductance without increasing the amount of loss caused by the proximity effect. To optimize the transformer, the number of primary- and secondary-side windings that resulted in the lowest core loss and copper loss was selected, and the feasibility of the new core design was verified using ANSYS Maxwell software. Finally, this paper proposes an integrated transformer without any additional resonant inductor in the LLC resonant converter. Transformer loss is optimized by adjusting parameters of the core structure and the winding arrangement. An LLC resonant converter with a 400 V input voltage, 300 V output voltage, 1 kW output power, and 500 kHz switching frequency was created, and a maximum efficiency of 97.03% was achieved. The component with the highest temperature was the transformer winding, which reached 78.6 °C at full load.

**Keywords:** LLC resonant converter; integrated transformer; adjustable leakage inductance; LED driver

#### 1. Introduction

Light emitting diode (LED) lighting has become more popular in recent years, particularly as product energy efficiency has become more important to consumers [1–3]. Compared with conventional lighting equipment, LEDs are brighter and have a longer service life. LEDs have thus been used in various lighting scenarios, such as street lighting, indoor lighting, and backlighting. They have also been used for lighting equipment with high power requirements, like baseball field or basketball court lights. Most of these LED driver circuits have a two-stage architecture consisting of a power factor correction converter in the first stage and an isolated buck converter in the second stage, with an LLC resonant converter usually employed as the second-stage circuit [4,5].

Unlike other common isolated buck converters, an LLC resonant converter is characterized by power components with zero voltage switching (ZVS) and zero current switching at the high—and low—voltage ends, respectively, in a full load range. Additionally, unlike phase-shifted full-bridge converters, an LLC converter has no output inductance at the low-voltage end and thus has higher conversion efficiency [6]. Moreover, to achieve high power density, increasing the switching frequency

of the power switch reduces the volume of the magnetic component; however, this is accompanied by a considerable increase in switching loss. Therefore, in addition to the ZVS feature of the LLC resonant converter, wide-band-gap switch components should also be employed to reduce the switching loss under high-frequency operation [7,8]. Additionally, selecting an appropriate LLC resonant converter architecture can further optimize the efficiency and reduce component stress [9–11]. The topologies commonly used in the high-voltage end of the LLC resonant converter are the half bridge and full bridge, whereas those used in the low-voltage end are the full bridge or center tap.

To achieve high power density, the leakage inductance of the transformer in this study was used as the resonant inductor of the circuit [12–14], which reduces the number of magnetic components required. Previous research replaced the resonant inductor with the leakage inductance of the transformers, mostly through winding the transformer using litz wire and setting the operating frequency between 50 and 200 kHz. However, when the operating frequency is between 500 kHz and 1 MHz, the litz wire is usually replaced by printed circuit board (PCB) windings to reduce the alternating-current (AC) resistance of the copper traces under high-frequency operation. Additionally, the primary- and secondary-side windings are interleaved to weaken the proximity effect. This approach reduces proximity-effect-induced loss and minimizes the leakage inductance of the transformer [15–17], which is a disadvantage in LLC resonant converters that require leakage inductance to design resonant tanks. A conventional method for increasing the leakage inductance is to increase the spacing between the primary and secondary sides [18–20], which is mostly achieved using a non-interleaved winding that leads to a sharp rise in the proximity-effect-induced AC loss. Therefore, the concept of adjustable leakage inductance [21,22] was adopted in this study, with an additional reluctance length added between the primary-side and secondary-side windings of the transformer. This enabled the magnetic flux generated by the primary-side winding to flow into the added reluctance length, thereby increasing the primary-side leakage inductance. The proposed approach weakens the proximity effect in the interleaved winding and attains the objective of increasing the leakage inductance. Compared to existing LED power converter designs [23–25], this work reduces the switching loss via wide bandgap devices and soft switching techniques under 500 kHz switching frequency conditions and utilizes an integrated transformer without an additional resonant inductor to achieve high power density. Ultimately, an LLC resonant converter with an output power of 1 kW, switching frequency of 500 kHz, input voltage of 400 V, and output voltage of 300 V was achieved in this study.

In this study, a second-stage LLC resonant converter was proposed for the LED driver circuit, and the LLC resonant circuit was used as a direct-current transformer (DCX) to operate the driver circuit at high efficiency. In addition, this study also designed and optimized the primary- and secondary-side topologies and magnetic components in the LLC resonant converter. In Section 2, under the conditions of 1 kW output power, 400 V input voltage, and 300 V output voltage, the loss and component stress at the primary—and secondary—side structures of the converter are analyzed and a topology suitable for the specification in this study is selected. Section 3 details the mathematical induction of adjustable leakage inductance and the appropriate number of primary- and secondary-side windings for the new core based on the optimal point of core loss and copper loss. The feasibility of the designed core structure was verified using ANSYS Maxwell software (ANSYS, Canonsburg, PA, USA). Section 4 presents the experimental results, including temperature distribution maps.

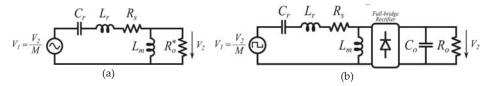

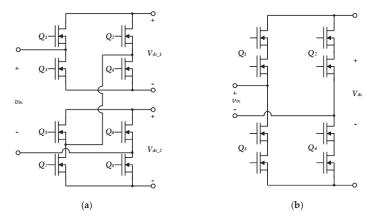

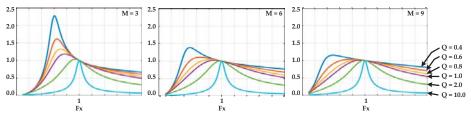

#### 2. LLC Topology Comparison

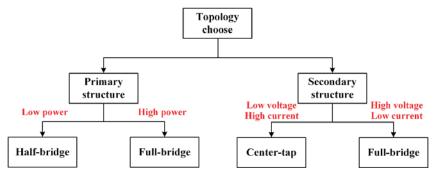

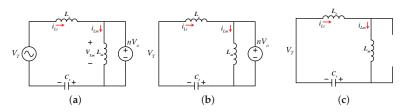

The primary and secondary sides of different architectures are discussed in this section. Because different circuit specifications have their appropriate architecture, the architecture is chosen based on power level and component stress, as shown in Figure 1. The primary side may consist of a half bridge or full bridge, whereas the secondary side comprises a center-tap and full-bridge rectification. The choice of different architectures for the primary side results in different transformer designs; hence, the primary side is mainly selected based on the corresponding architecture for the appropriate power level. As for the different architectures on the secondary side, there are different

component stresses and numbers of switches. Therefore, the appropriate architecture for the secondary side is mainly selected according to the level of the output voltage and current.

Figure 1. Architecture selection diagram.

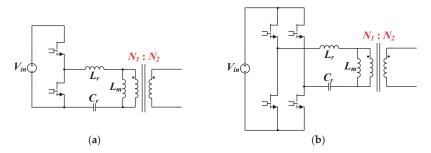

The common structures for the primary side are the half bridge and full bridge (Figure 2). For the half bridge, the voltage across the resonant tank is  $+V_{in}$  to 0 V; however, the actual voltage across the transformer is  $\pm V_{in}/2$ . Therefore, the turns ratio between the primary and secondary sides must be accounted for when designing the transformer. The energy transfer formula in Equation (1) can be rewritten as a general formula that establishes ZVS under a half-bridge structure, as shown in Equation (2).

$$\frac{1}{2}LI^2 \ge \frac{1}{2}CV^2\tag{1}$$

in which the unit of *L* is Henry (H), *I* is Ampere (A), *C* is Farad (F), and *V* is Volt (V).

$$L_m \le \frac{t_{dead}}{16C_{oss}f_{sw}} \tag{2}$$

in which the unit of  $L_m$  is Henry (H),  $t_{dead}$  is seconds (s),  $C_{oss}$  is Farad (F), and  $f_{sw}$  is Hertz (Hz).

Figure 2. Primary structure (a) half bridge and (b) Full bridge topology.

For a full-bridge structure, the voltage across the transformer is approximately  $\pm V_{in}$ , and the input voltage can be directly divided by the output voltage to obtain the turns ratio when designing the transformer. For primary-side switching to achieve ZVS in a full-bridge structure, the energy transfer formula Equation (1) can be rewritten as the following general formula:

$$L_m \le \frac{t_{dead}}{8C_{oss}f_{stv}} \tag{3}$$

Under the conditions of 400 V input voltage, 300 V output voltage, and a half-bridge structure of the primary side, the equivalent turns ratio of the primary and secondary sides is indicated by Equation (4), whereas Equation (5) obtains the equivalent turns ratio of the two sides when a full-bridge structure is adopted on the primary side. In choosing the primary-side architecture, the conditions of primary-side ZVS are influenced by the stray capacitance [26]. In particular, the stray capacitance of the secondary side mapped back to the primary side is affected by the turns ratio. Thus, if a half-bridge structure was adopted under this specification, the stray capacitance mapped from the secondary to the primary side would be magnified. Therefore, a full-bridge structure was employed in this study to reduce the effect on ZVS condition. Table 1 [27] shows a comparison of the various ratings of the two primary-side architectures.

$$\frac{N_1}{N_2} = \frac{V_{in}/2}{V_o} = \frac{2}{3}$$

(4)

$$\frac{N_1}{N_2} = \frac{V_{in}}{V_o} = \frac{4}{3}$$

(5)

| Primary Structure             | Half-Bridge                                                                                                                                                             | Full-Bridge                                                                                                                             |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Primary device voltage stress | V <sub>in</sub><br>(400 V)                                                                                                                                              | V <sub>in</sub><br>(400 V)                                                                                                              |

| Primary device current stress | $\frac{\frac{V_{o}\sqrt{4\pi^{2} + \left(\frac{N_{1}}{N_{2}}\right)^{4}R_{L}^{2}\left(\frac{T}{L_{m}}\right)^{2}}}{4\frac{N_{1}}{N_{2}}\cdot R_{L}}}{(8.25 \text{ A})}$ | $\frac{V_o \sqrt{4\pi^2 + \binom{N_1}{N_2}}^4 R_L^2 (\frac{T}{L_m})^2}{4 \cdot \frac{N_1}{N_2} \cdot R_L}}{(4.81 \text{ A})}$           |

| Primary device rms current    | $\frac{\frac{V_{o}\sqrt{4\pi^{2} + \left(\frac{N_{1}}{N_{2}}\right)^{4}R_{L}^{2}\left(\frac{T}{L_{m}}\right)^{2}}}{8\frac{N_{1}}{N_{2}}\cdot R_{L}}}{(4.08 \text{ A})}$ | $\frac{\frac{V_o \sqrt{4\pi^2 + \binom{N_1}{N_2}}^4 R_L^2 (\frac{T}{L_m})^2}{8 \cdot \frac{N_1}{N_2} \cdot R_L}}{(2.36 \text{ A})}$     |

| Resonant inductor rms current | $\frac{V_o \sqrt{4\pi^2 + \left(\frac{N_1}{N_2}\right)^4 R_L^2 \left(\frac{T}{L_m}\right)^2}}{4 \sqrt{2} \frac{N_1}{N_2} \cdot R_L}}{(5.8 \text{ A})}$                  | $\frac{V_o \sqrt{4\pi^2 + {\binom{N_1}{N_2}}^4 R_L^2 (\frac{T}{Lm})^2}}{4 \sqrt{2} \cdot \frac{N_1}{N_2} \cdot R_L}}{(3.38 \text{ A})}$ |

| ZVS condition                 | $L_m \leq \frac{t_{dead}}{16C_{oss}f_{sw}}$                                                                                                                             | $L_m \leq \frac{t_{dead}}{8C_{oss}f_{sw}}$                                                                                              |

| Turns ratio                   | N <sub>1</sub> :N <sub>2</sub><br>(12:18)                                                                                                                               | N <sub>1</sub> :N <sub>2</sub><br>(24:18)                                                                                               |

| Primary device                | GS66508B, 650 V                                                                                                                                                         | GS66508B, 650 V                                                                                                                         |

| Number of primary device      | 2                                                                                                                                                                       | 4                                                                                                                                       |

| Total SR conduction loss      | $I_{rms}^2 \cdot R_{ds(on)} \cdot 2$ (1.665 W)                                                                                                                          | $I_{rms}^2 \cdot R_{ds(on)} \cdot 4$ (1.114 W)                                                                                          |

| Winding loss of primary side  | 7.24 W                                                                                                                                                                  | 5.51 W                                                                                                                                  |

| Proper specification          | Low power                                                                                                                                                               | High power                                                                                                                              |

Table 1. Comparison of primary-side architectures.

In Table 1, *T* is the switching period, and its unit is seconds (s), and  $\overline{RL}$  is the output load. Its unit is Ohm ( $\Omega$ ). ZVS, zero voltage switching. SR, synchronous rectifier.

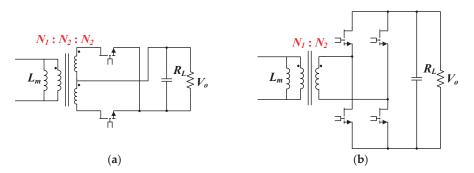

Common structures for the secondary side are center-tap and full-bridge rectification (Figure 3). For center-tap rectification, the voltage over the secondary side of the transformer was  $1 \times V_o$ ; however, the voltage over the synchronous rectifiers (SRs) was  $2 \times V_o$ , and overall, the conduction loss amounted to that of two SRs. Based on this analysis, the center-tap structure was more suitable for low-output-voltage and high-current specifications.

Compared with those in the center-tap structure, the voltage over the secondary side and the SRs of the transformer in the full-bridge rectification structure were  $1 \times V_o$ ; however, the conduction loss amounted to that of four SRs. Based on this analysis, full-bridge rectification was suitable for

high-output-voltage and low-current specifications. For the high-output-voltage specification and considering the tradeoff between the SR voltage rating, SR conduction loss, and secondary-side copper loss, full wave rectification was selected for the secondary-side structure, and the switch employed was the GS66508B. Table 2 shows a comparison of the SR rated voltage, transformer turns ratio, and SR number of the two secondary-side architectures.

Figure 3. Secondary-side architecture: (a) center tap and (b) full bridge.

| Secondary Structure            | Center-Tap                                                                                                                                            | Full-Bridge                                                                                                                                        |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| SR voltage stress              | 2 V <sub>0</sub><br>(600 V)                                                                                                                           | V <sub>0</sub><br>(300 V)                                                                                                                          |

| SR current stress              | $\sqrt{12} \frac{V_o \sqrt{12 \pi^4 + \frac{5 \pi^2 - 48}{L_m^2} \left(\frac{N_1}{N_2}\right)^4 R_L^2 T^2}}{(5.5 \text{ A})}$                         | $\sqrt{12} \frac{V_o \sqrt{12 \pi^4 + \frac{5 \pi^2 - 48}{L_m^2} \left(\frac{N_1}{N_2}\right)^4 R_L^2 T^2}}{(5.5 \text{ A})}$                      |

| SR rms current                 | $\sqrt{3} \frac{\frac{V_o \sqrt{12 \pi^4 + \frac{5 \pi^2 - 48}{Lm^2} \left(\frac{N_1}{N_2}\right)^4 R_L^2 T^2}}{\frac{24 \pi R_L}{(2.67 \text{ A})}}$ | $\sqrt{3} \frac{\frac{V_o \sqrt{12\pi^4 + \frac{5\pi^2 - 48}{Lm^2} \left(\frac{N_1}{N_2}\right)^4 R_L^2 T^2}}{\frac{24\pi R_L}{(2.67 \text{ A})}}$ |

| Turns ratio                    | N1:N2:N2<br>(24:18:18)                                                                                                                                | N1:N2<br>(24:18)                                                                                                                                   |

| SR device                      | GS66508B, 650 V                                                                                                                                       | GS66508B, 650 V                                                                                                                                    |

| Number of SR device            | 2                                                                                                                                                     | 4                                                                                                                                                  |

| Total SR conduction loss       | $I_{rms}^2 \cdot R_{ds(on)} \cdot 2$ (0.713 W)                                                                                                        | $\frac{I_{rms}^2 \cdot R_{ds(on)} \cdot 4}{(1.426 \text{ W})}$                                                                                     |

| Winding loss of secondary side | 2.41 W                                                                                                                                                | 2.41 W                                                                                                                                             |

| Proper specification           | Low output voltage<br>High output current                                                                                                             | High output voltage<br>Low output current                                                                                                          |

Table 2. Comparison of secondary-side architectures.

Next, the differences between the four architectures (primary and secondary side) are compared. In terms of the primary-side switch voltage stress, both the half bridge and full bridge result in a voltage stress of  $1 \times V_{in}$ , whereas the secondary-side switch voltage stress is  $2 V_o$  and  $V_o$  for center-tap and full-bridge rectification, respectively. The voltage over the transformer was  $\pm 0.5 V_{in}$  when a half-bridge structure was employed for the primary side, whereas using a full-bridge structure yielded a voltage of  $\pm V_{in}$ . Therefore, when transmitting the same power, the transformer current was  $I_r$  when a full-bridge structure was used on the primary side but had to be  $2 I_r$  if a half-bridge structure was used. Because the voltage over the transformer was half the input voltage, the current on the primary side was greater when a half-bridge structure was employed than when the primary side comprised a full-bridge structure. Therefore, the primary-side half-bridge architecture is suitable for circuits

with low power applications to prevent excessive current flow through the transformer, which would result in saturation. Regarding the secondary side, the component voltage stress when the center-tap structure was used was twice that when full-bridge rectification was employed, whereas the number of components was half; the center-tap structure is thus appropriate for low-voltage-output and high-current applications. Table 3 shows a comparison of the characteristics for the four architectures.

| Component                                       | Primary Side:<br>Half-Bridge<br>Secondary Side:<br>Center-Tap | Primary Side:<br>Half-Bridge<br>Secondary Side:<br>Full-Bridge | Primary Side:<br>Full-bridge<br>Secondary side:<br>Center-Tap | Primary side:<br>Full-Bridge<br>Secondary side:<br>Full-Bridge |

|-------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|

| Primary device<br>voltage stress                | $V_{in}$                                                      | V <sub>in</sub>                                                | $V_{in}$                                                      | $V_{in}$                                                       |

| SR voltage stress                               | 2 V <sub>0</sub>                                              | $V_0$                                                          | $2V_0$                                                        | $V_0$                                                          |

| Primary-side<br>transformer<br>voltage stress   | ±0.5 V <sub>in</sub>                                          | ±0.5 V <sub>in</sub>                                           | $\pm V_{in}$                                                  | $\pm V_{in}$                                                   |

| Secondary-side<br>transformer<br>voltage stress | $\pm V_0$                                                     | $\pm V_0$                                                      | $\pm V_0$                                                     | $\pm V_0$                                                      |

| Primary-side<br>transformer<br>current          | 2 <i>I</i> <sub>r</sub>                                       | 2 <i>I</i> <sub>r</sub>                                        | I <sub>r</sub>                                                | Ir                                                             |

| Proper<br>specification                         | Low power<br>Low output voltage<br>High output<br>current     | Low power<br>High output<br>voltage<br>Low output current      | High power<br>Low output voltage<br>High output<br>current    | High power<br>High output<br>voltage<br>Low output curren      |

Table 3. Comparison of the four architectures.

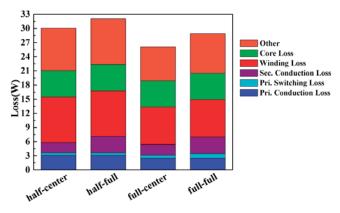

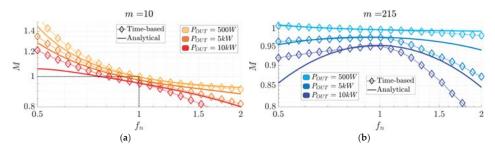

The loss distribution of the four architectures was calculated on the basis of the specifications in this study (Figure 4). According to the loss distribution illustrated in Figure 4, the loss of each architecture type was mostly copper loss of the transformers and other loss types, including the equivalent series resistance of the capacitor and via loss. The overall efficiency of the architecture comprising a primary-side full-bridge structure and secondary-side center-tap structure was the highest of all architectures. However, because the specification of this study was high output voltage, the SR voltage rating of the secondary-side center-tap structure had to be 2  $V_o$ ; additionally, the actual test circuit was not ideal. Therefore, the architecture with primary-side full-bridge and secondary-side full bridge structures, which had the second highest efficiency, was selected to prevent the SR from being damaged by the high voltage.

Figure 4. Comparison of loss types in different architectures.

#### 3. Design Concept and Loss Optimization of Adjustable Leakage Inductance

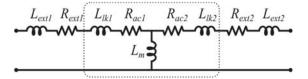

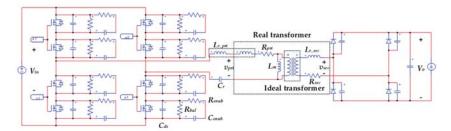

The conventional integrated leakage inductance is formed by leakage flux that is lost to the air and does not pass through the secondary side. Accurate control of the amount of leakage inductance is practically difficult. The concept of adjustable leakage inductance that was adopted in this study was to add an additional reluctance length that prevents some flux generated on the primary side from flowing into the secondary-side winding, in turn generating leakage inductance. The leakage inductance used in this study was designed using the concept of split flow of the transformer reluctance.

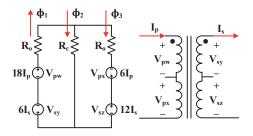

Figure 5 presents the concept of adjustable leakage inductance, where the voltage of the primary side and secondary side are denoted by Vp and Vs, respectively. The winding in the primary side was divided into two parts, of which one part wound counterclockwise with 18 turns around the left outer leg, and the other wound clockwise with 6 turns around the right outer leg. Similarly, the winding on the secondary side was also divided into two parts, in which one part wound clockwise with 6 turns around the left outer leg, and the other wound counterclockwise with 12 turns around the right outer leg. Moreover, according to Equation (6), the magnetomotive force (MMF) of these windings could be represented as 18  $I_p$ , 6 Is, 6 Ip, and 12  $I_s$ , and their voltage as  $V_{pw}$ ,  $V_{px}$ ,  $V_{sy}$ , and  $V_{sz}$ , respectively.  $R_o$  represents the reluctance of the outer leg, and  $R_c$  represents the reluctance of the center leg.

Figure 5. Reluctance model for adjustable leakage inductance.

$$\phi = \frac{mmf}{R} = NI \tag{6}$$

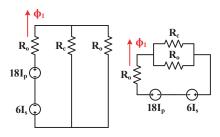

Figure 6 displays the equivalence of the reluctance generated by the passing flux produced in the left leg that was achieved by using the superposition theorem. Regarding the core structure, because the reluctances of both outer legs are the same, the equivalent reluctance passing through  $\phi_1$  and  $\phi_3$  are the same, as indicated in Equation (7). After the reluctance passing through the flux has been obtained,

$\phi_1$  could be presented as Equation (8); although the equivalent reluctance of  $\phi_1$  and  $\phi_{3\neg}$  are the same,  $\phi_3$  could be presented as in Equation (9) because the MMF is different for each leg. Because the center leg had no windings, only the values of flux on the left and right outer legs are listed.

Figure 6. Equivalent reluctance model for flux split flow.

$$R_{\phi 1} = R_{\phi 3} = \frac{R_o(R_o + 2R_c)}{R_o + R_c}$$

(7)

$$\phi_1 = \left(18I_p - 6I_s\right) \cdot \frac{R_o + R_c}{R_o(R_o + 2R_c)}$$

(8)

$$\phi_3 = \left(6I_p - 12I_s\right) \cdot \frac{R_o + R_c}{R_o(R_o + 2R_c)} \tag{9}$$

As mentioned, the MMF generated from the windings on each leg was determined using the superposition theorem. Subsequently, Equations (10)–(12) represent the total flux of each leg in consideration of flux split flow.

$$\phi_{1\_total} = \frac{18R_o + 24R_c}{R_o(R_o + 2R_c)} \cdot I_p - \frac{6R_o + 18R_c}{R_o(R_o + 2R_c)} \cdot I_s \tag{10}$$

$$\phi_{2\_total} = \frac{12}{R_o(R_o + 2R_c)} \cdot I_p - \frac{6}{R_o(R_o + 2R_c)} \cdot I_s$$

(11)

$$\phi_{3\_total} = \frac{6R_o + 24R_c}{R_o(R_o + 2R_c)} \cdot I_p - \frac{12R_o + 18R_c}{R_o(R_o + 2R_c)} \cdot I_s$$

(12)

According to Figure 7, the primary-side voltage of the transformer  $V_p$  is the sum of  $V_{pw}$  and  $V_{px}$ ; the secondary-side voltage of the transformer  $V_s$  is the sum of  $V_{sy}$  and  $V_{sz}$ . As demonstrated by Equation (13), Faraday's law of induction was employed to ascertain the relationship between the voltage, number of turns, and variation in flux over time. Moreover, the primary-side voltage  $V_p$  and secondary-side voltage  $V_s$  of the transformer are represented using Equations (14) and (15).

$$V = n \frac{d\phi}{dt} \tag{13}$$

$$V_p = \frac{360R_o + 576R_c}{R_o(R_o + 2R_c)} \cdot \frac{dI_p}{dt} - \frac{180R_o + 432R_c}{R_o(R_o + 2R_c)} \cdot \frac{dI_s}{dt}$$

(14)

$$V_{s} = \frac{180R_{o} + 432R_{c}}{R_{o}(R_{o} + 2R_{c})} \cdot \frac{dI_{p}}{dt} - \frac{180R_{o} + 324R_{c}}{R_{o}(R_{o} + 2R_{c})} \cdot \frac{dI_{s}}{dt}$$

(15)

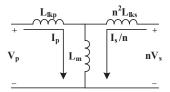

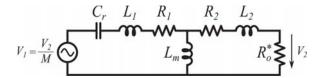

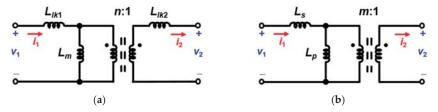

Figure 7. T model of the transformer.

By using Faraday's law of induction to assess the relationship between the voltage, reluctance, and number of turns of the transformer, the T model of the transformer (Figure 7) could be applied. In Figure 7,  $V_p$  refers to the primary-side voltage of the transformer, and  $V_s$  refers to the secondary-side voltage of the transformer; furthermore,  $L_{lkp}$  represents the primary-side leakage inductance,  $L_{lks}$  represents the secondary-side leakage inductance of the transformer. The T model enabled the equivalence of the voltage, current, and leakage inductance of the secondary side with that of the primary side. Equations (16) and (17) present the results.

$$V_p = \left(L_m + L_{lkp}\right) \frac{dI_p}{dt} - \left(\frac{L_m}{n}\right) \frac{dI_s}{dt}$$

(16)

$$V_s = -\left(\frac{L_m}{n}\right)\frac{dI_p}{dt} + \left(\frac{L_m}{n^2} + L_{lks}\right)\frac{dI_s}{dt}$$

(17)

Subsequently, Equations (14) and (16) could be compared with Equations (15) and (17). Equations (18)–(20) represent the relationship among the leakage inductance and excitation inductance of the primary and secondary sides of the transformer and the number of turns of the windings.

$$L_m + L_{lkp} = \frac{360R_o + 576R_c}{R_o(R_o + 2R_c)}$$

(18)

$$\frac{L_m}{n} = \frac{180R_o + 432R_c}{R_o(R_o + 2R_c)}$$

(19)

$$\frac{L_m}{n^2} + L_{lks} = \frac{180R_o + 324R_c}{R_o(R_o + 2R_c)}$$

(20)

The comparison could be used to establish models of equivalent leakage inductance of the primary and secondary sides of the transformer and the excitation inductance. Such models could be presented using Equations (21)–(23).

$$L_m = \frac{240R_o + 576R_c}{R_o(R_o + 2R_c)}$$

(21)

$$L_{lkp} = \frac{120R_o}{R_o(R_o + 2R_c)}$$

(22)

$$L_{lks} = \frac{45R_o}{R_o(R_o + 2R_c)}$$

(23)

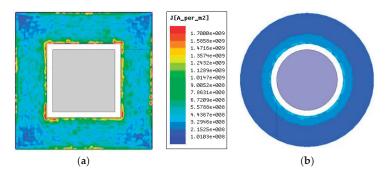

According to the obtained results, a three-legged core could achieve adjustable leakage inductance if the shape of the outer legs easily enables winding. Applying the winding coil is difficult when the commonly used PQ and RM cores are employed because of their outer leg shape; thus, EI or EE cores were used for adjustable leakage inductance [21]. The simulation results of the current distribution of the PCB trace windings based on the shapes of the PQ and EI cores were obtained with Maxwell magnetic simulation software. The simulation results presented in Figure 8 yielded the winding for the square core, and the current distribution obtained using the square core was considerably more uneven than that obtained using the round core, leading to excessively dense current at the corner of the

winding, hot spots, and higher losses. Therefore, the cylindrical core was selected as the transformer core in this study.

Figure 8. Relationship between the winding shapes of effective core cross sections and current distribution: (a) square-shaped cross section; (b) round cross section.

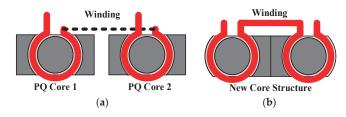

The design presented in Figure 9 was proposed to achieve adjustable inductance through winding on the two outer legs of the three-legged core and the obtainment of even current distributions on PCB windings. Producing adjustable leakage inductance required that windings be set only on the outer legs and not on the center leg. This method enabled the cross-sectional area of the center leg to be altered to a shape suitable for PCB winding, increasing the effectiveness of the winding space of the transformer. Therefore, this study proposed aligning two PQ cores (Figure 9a), where the connected part serves as the center leg of the core, and removal of one outer leg of the original core forms a new three-legged structure for the core. The design is as presented in Figure 9b.

Figure 9. Diagram of the innovative core structure: (a) PQ core structure; (b) the innovative core structure.

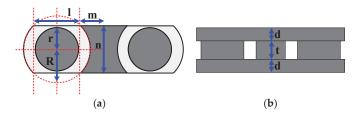

Figure 10 shows a diagram of the core size design in this study. Figure 10a is the top view, and r represents the radius of the effective cross-sectional area, R denotes the radius of the core that can be wound, l is twice the horizontal distance from the core cylinder to the highest point of the center leg, m is the maximum width of the center leg, n is the length of the core, d is the thickness of the top and bottom pieces, and t represents the leg height of the core.

Figure 10. Diagram of the core size marking: (a) top and (b) side view.

Energies 2019, 12, 1781

The overall loss of the transformer can be divided into core loss and copper loss. Core loss is the product of core loss per unit volume and core volume, as shown in Equation (24). In Equation (25), Pv denotes the unit volume loss, and Cm, x, and y can be acquired from the core manufacturer's manual. Combining Equations (24) and (25) reveals that the core loss and volume Vel are related to the switching frequency fs and peak flux density  $B_{max}$ , with core loss being linearly proportional to Vel and exponentially proportional to fs and  $B_{max}$ . Next,  $B_{max}$  was expressed as Equation (26), where  $V_{in}$  denotes the input voltage, Ae represents the effective cross-sectional area of the core, and Np is the number of turns of the primary winding. In this study, the input voltage  $V_{in}$ , switching frequency fs, and effective cross-sectional area of the core are 400 V, 500 kHz, and 194 mm<sup>2</sup>, respectively. The relationship between core loss and the number of primary-side turns is revealed through Equation (26), with a higher number of turns leading to a drop in peak flux density, reducing the core loss. However, from the perspective of copper loss, more turns resulted in greater loss. Thus, the optimal number of turns in this study was acquired by quantifying the core loss and copper loss.

$$Coreloss = Pcv \cdot Vel \tag{24}$$

$$Pv = Cm \cdot fs^x \cdot B^y_{\max} \tag{25}$$

$$B_{\max} = \frac{Vin}{4 \cdot Ae \cdot Np \cdot fs}$$

(26)

In this study, a full-bridge LLC resonant conversion topology was employed for the primary-side circuit architecture, whereas the secondary-side rectification architecture consisted of a full-bridge topology. The turns ratio of the transformer was calculated using Equation (27), and substituting the circuit specifications of this study (400 V input voltage and 300 V output voltage) yielded a transformer turns ratio of 4:3. However, the minimal number of turns on the primary side cannot be 1 because of the winding method of the adjustable leakage inductance, because the primary-side should be wound to the two outer legs, and because the primary side on both legs cannot be the same. Additionally, the winding ratio of the primary and secondary sides has to be an integer to prevent the need for a non-integer number of turns on the secondary side. Table 4 shows that the winding width of the core could be obtained by subtracting *r* from *R*, and the actual winding width was 5.5 mm.

$$n = \frac{Vin}{Vo} \tag{27}$$

| Core Size | Value               |

|-----------|---------------------|

| Ae        | 194 mm <sup>2</sup> |

| R         | 13.3 mm             |

| r         | 7.8 mm              |

| 1         | 18.8 mm             |

| m         | 7.29 mm             |

| п         | 18.8 mm             |

| d         | 6 mm                |

| t         | 10.3 mm             |

|           |                     |

Table 4. Parameter design of the asymmetric resonant tank.

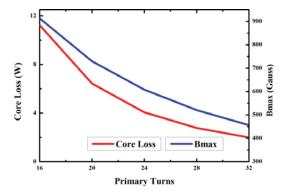

The transformer turns ratio in this study was 4:3; thus, the number of turns at the primary and secondary sides could be 4:3, 8:6, 12:9, and so on. The core loss per unit volume (Pv) increased substantially when the peak flux density of the transformer exceeded 1000 G. Therefore, the peak flux density was designed to be less than 1000 G in the core turns design. Next, Equation (26) was rewritten as Equation (28), and  $B_{max}$  was set to 1000 G. According to Equation (28), the minimum number of winds on the primary side was 14.6. Practically, more windings mean more layers and greater costs.

Therefore, only the following five windings on the primary and secondary sides were considered: 16:12, 20:15, 24:18, 28:21, and 32:24.

$$Np > \frac{Vin}{4 \cdot Ae \cdot B_{\max} \cdot fs} = 14.6$$

<sup>(28)</sup>

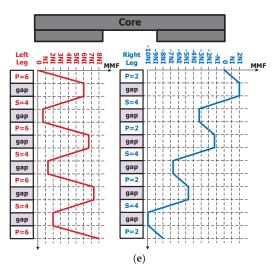

The peak flux density and core loss for different numbers of turns were obtained using Equations (24) and (26), and the results are plotted in Figure 11. The relationship between core loss and number of turns was nonlinear. The difference in core loss between 16 and 20 turns on the primary-side winding was 4.8 W, whereas 28 and 32 turns on the primary-side winding yielded a core loss of approximately 0.8 W. This was the main reason for designing  $B_{\text{max}}$  to be less than 1000 G.

Figure 11. Peak flux density and core loss.

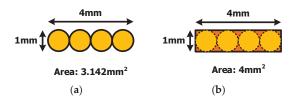

The high-frequency copper loss was analyzed next. Conventional transformers are mostly wound with litz wire; however, planar routing is more advantageous to utilize the window area of a transformer. Figure 12 compares the use of planar routing and four litz wires. Under the same condition of an occupied area of 4 mm<sup>2</sup>, the cross-sectional area of the litz wires was 3.142 mm<sup>2</sup>, whereas that of the planar routing was 4 mm<sup>2</sup> (Figure 12a,b, respectively); both yielded a 27% difference in DC resistance under the same length. Therefore, PCB routing was used as the transformer winding in this study to achieve high power density.

Figure 12. Winding usage in different transformers: (a) litz wire and (b) planar trace.

PCB routing was selected over litz wire under the same transformer window area because it resulted in lower DC resistance of the winding. However, a sharp rise in AC resistance loss was observed when the switching frequency was increased from the conventional 50 kHz–200 kHz to 500 kHz–1 MHz. Therefore, the AC resistance loss of the transformer winding was analyzed.

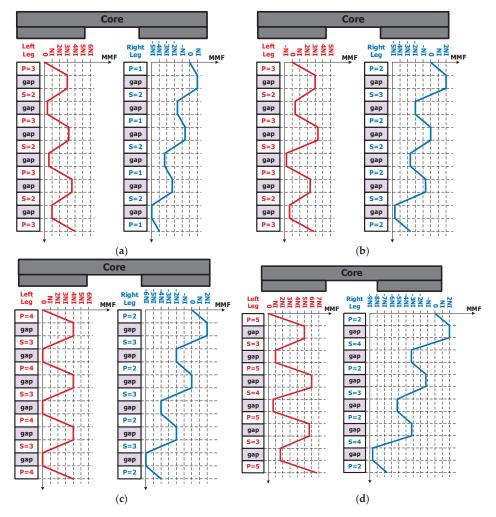

According to Dowell's equation, the skin effect and proximity effect can be expressed by Equations (29) and (30), respectively, where  $\xi = h/\delta$ , with *h* denoting the thickness of the copper wire in the transformer winding and  $\delta$  representing the skin depth of the transformer winding. Additionally, *m* can be expressed using Equation (31), where *e* represents the number of winding layers. The five numbers of windings that were employed and the corresponding distributions of MMF are displayed in Figure 13.

Because the circuit architecture in this study was an LLC rather than bidirectional CLLC, only the leakage inductance on the primary side was adjusted. Therefore, the secondary side was wound around the two outer legs with the same or almost the same number of turns, and the primary and secondary sides were wound on an eight-layer PCB in an interleaved manner. A total of seven layers of PCB winding were used, and one layer was reserved as the routing that connected the two leg windings.

$$R_{ac\_skin} = \frac{\xi}{2} \cdot \frac{\sinh(\xi) + \sin(\xi)}{\cosh(\xi) - \cos(\xi)} \cdot R_{dc}$$

<sup>(29)</sup>

$$R_{ac\_proximity} = \frac{\xi}{2} \cdot (2m-1)^2 \cdot \frac{\sinh(\xi) - \sin(\xi)}{\cosh(\xi) + \cos(\xi)} \cdot R_{dc}$$

(30)

$$m = \left| \frac{MMF(e)}{MMF(e) - MMF(e-1)} \right|$$

(31)

Figure 13. Cont.

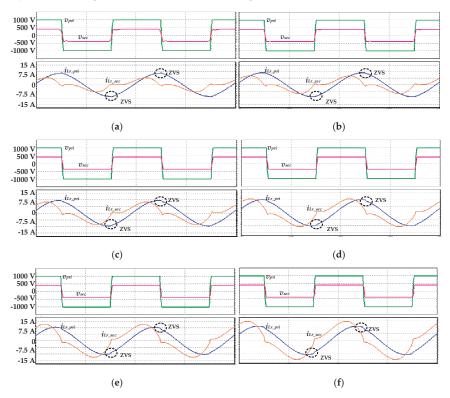

**Figure 13.** MMF distribution map of different numbers of windings: (a) Np = 16, Ns = 12; (b) Np = 20, Ns = 15; (c) Np = 24, Ns = 18; (d) Np = 28, Ns = 21; and (e) Np = 32, Ns = 24.

Figure 14 illustrates the copper loss and total loss of the transformer for different numbers of turns. The core loss could be obtained from Figure 11. More turns resulted in lower peak flux density of the core and thus lower core loss. However, more windings also led to greater copper loss, which could be divided into that associated with DC resistance and AC resistance. DC resistance was greater for more windings; however, the resistance that actually affects the high-frequency copper loss is AC resistance loss. Because an eight-layer board was used for transformer routing, more turns meant that each layer of the PCB board had to accommodate more windings, which narrowed the width of each winding. Moreover, according to Figure 13, more windings in each layer resulted in a higher MMF, causing substantially greater AC resistance under high frequency, which in turn resulted in greater copper loss. The various amounts of core loss and copper loss are presented in Table 5, and the results are plotted in Figure 14. Ultimately, the number of turns with the lowest total loss (24:18) was selected as the suitable number of turns of the transformer in this study. Figure 15 shows the peak flux density of the core, as simulated by ANSYS Maxwell software, to verify that the core operated normally.

Figure 14. Copper loss and total loss.

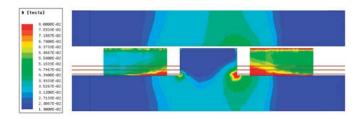

Figure 15. Flux density distribution by FEA 3D simulation.

| $Condition \backslash Np:Ns$ | 16:12 | 20:15 | 24:18 | 28:21 | 32:24 |

|------------------------------|-------|-------|-------|-------|-------|

| B <sub>max</sub> (Gauss)     | 913   | 730   | 608   | 521   | 456   |

| Core Loss (W)                | 11.23 | 6.43  | 4.07  | 2.77  | 1.99  |

| Rdc (mΩ)                     | 157   | 223   | 260   | 479   | 689   |

| Rac (m $\Omega$ )            | 167   | 232   | 270   | 530   | 796   |

| Copper Loss (W)              | 3.33  | 4.50  | 5.74  | 10.50 | 15.57 |

| Total Loss (W)               | 14.56 | 10.93 | 9.81  | 13.27 | 17.55 |

Table 5. Parameter design of the asymmetric resonant tank.

# 4. Results

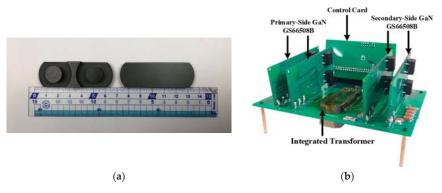

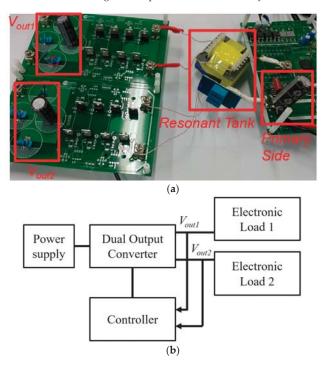

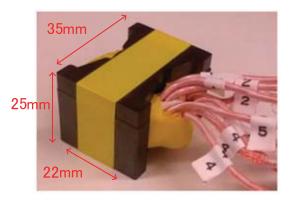

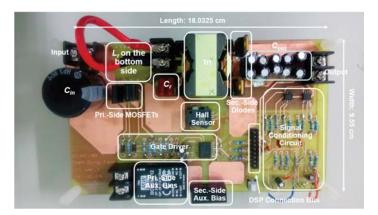

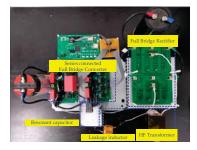

An LLC resonant converter with 1 kW output power and 500 kHz switching frequency was proposed in this study. Figure 16a,b shows the actual core size and circuit diagram, respectively. Table 6 details the components and design parameters used in this study.

Figure 16. Experimental prototype of the (a) core structure and (b) circuit.

| Table 6. Parameter design of the asymmetric resonant tank. |

|------------------------------------------------------------|

|------------------------------------------------------------|

\_

| Component                        | Value    |

|----------------------------------|----------|

| Resonant and Operating Frequency | 500 kHz  |

| Transformer Turns Ratio          | 24:18    |

| Transformer Material             | 3F36     |

| Primary-Side Switch Device       | GS66508B |

| Secondary-Side Switch Device     | GS66508B |

| Primary-Side Driver              | Si8271GB |

| Secondary-Side Driver            | Si8271GB |

| Resonant Capacitor               | 22.4 nF  |

| Leakage Inductance               | 4.7 μΗ   |

| Magnetizing Inductance           | 80.5 μH  |

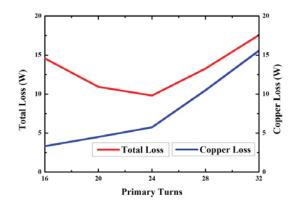

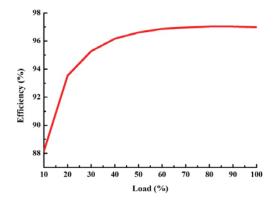

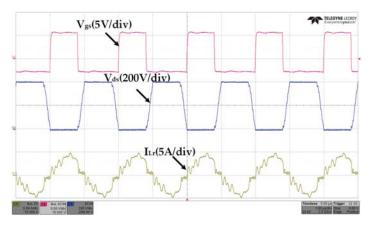

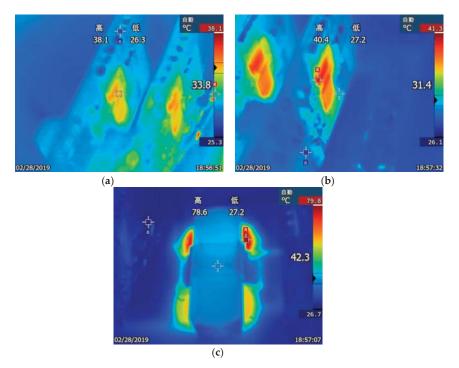

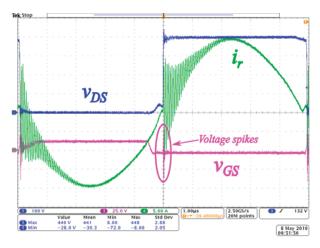

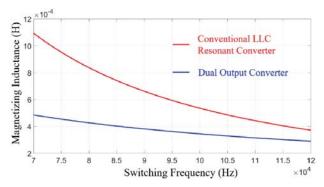

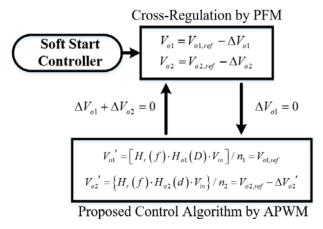

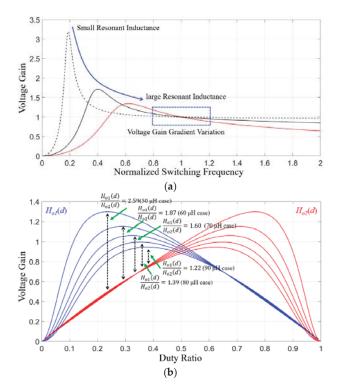

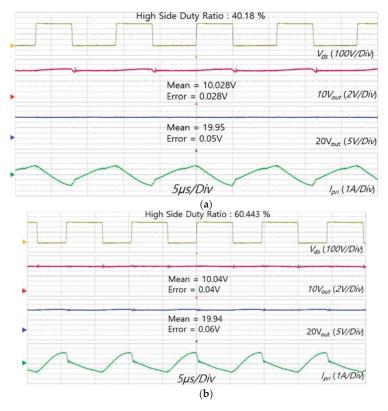

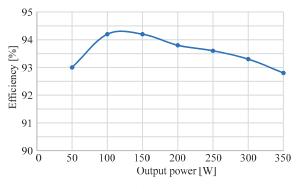

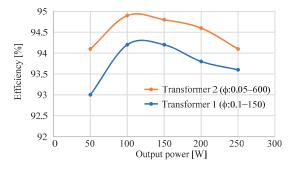

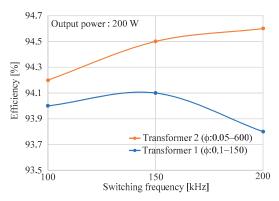

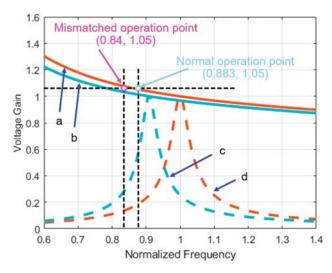

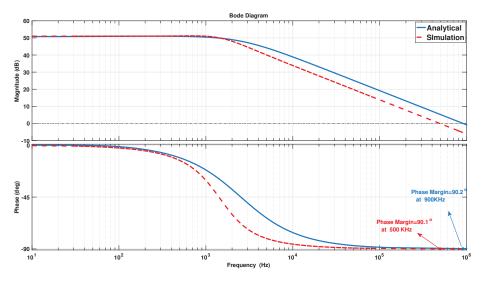

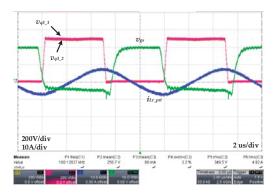

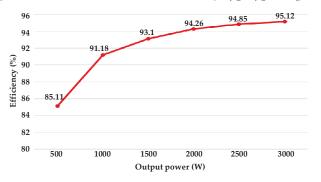

Figure 17 plots the measured conversion efficiency of the converter. The highest efficiency of 97.03% was achieved at 80% load. Figure 18 displays the circuit test waveform at full load, which includes the waveforms of *Vds*, *Vgs*, and the resonant current  $I_{Lr}$  of the primary-side power switch operating properly. Figure 19a–c shows temperature distribution of the primary-side power components at full load, with maximum temperatures of 38.1 °C, 40.4 °C, and 78.6 °C, respectively. Because the specifications of this paper are high-voltage to high-voltage, according to the loss analysis in Figure 4, the loss can be mainly attributed to the transformer, especially, on the transformer windings. Because the primary or secondary switching elements have zero-voltage-switch turn-on, the temperature distribution of the overall converter will be concentrated on the windings of the transformer.

Figure 17. Measured power efficiency.

Figure 18. Experimental waveforms for the converter at full load.

**Figure 19.** Temperature of the LLC converter at full load; (**a**) primary-side GaN devices, (**b**) secondary-side GaN devices, and (**c**) core and winding of transformer.

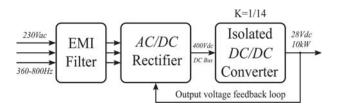

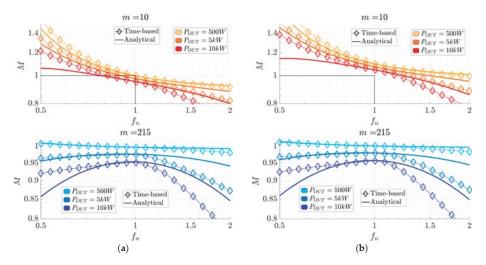

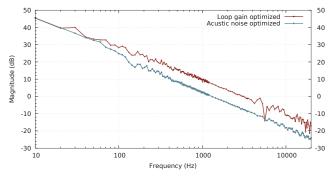

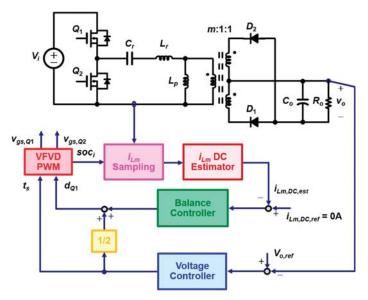

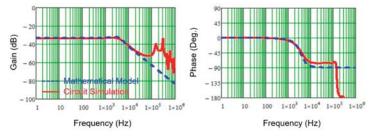

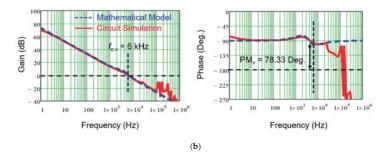

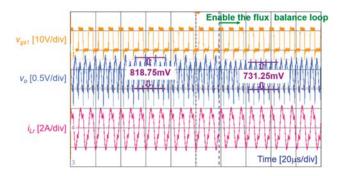

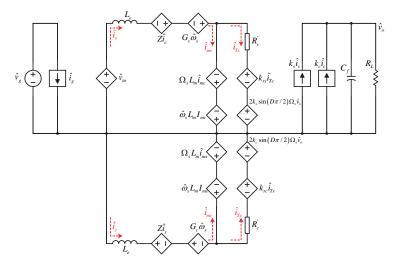

#### 5. Conclusions