# Industrial Applications of Power Electronics

Edited by

Eduardo M. G. Rodrigues, Edris Pouresmaeil and Radu Godina

Printed Edition of the Special Issue Published in *Electronics*

# **Industrial Applications of Power Electronics**

## **Industrial Applications of Power Electronics**

Editors

Eduardo M. G. Rodrigues Edris Pouresmaeil Radu Godina

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

Editors

Eduardo M. G. Rodrigues Management and Production Technologies of Northern Aveiro—ESAN Portugal

Edris Pouresmaeil Aalto University Finland Radu Godina Universidade NOVA de Lisboa Portugal

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Electronics* (ISSN 2079-9292) (available at: https://www.mdpi.com/journal/electronics/special\_issues/IndustrialApplications\_PE).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Article Number*, Page Range.

ISBN 978-3-03943-483-1 (Hbk) ISBN 978-3-03943-484-8 (PDF)

© 2020 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## **Contents**

| About the Editors                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "Industrial Applications of Power Electronics" is                                                                                                         |

| Eduardo M. G. Rodrigues, Radu Godina and Edris Pouresmaeil                                                                                                           |

| Industrial Applications of Power Electronics                                                                                                                         |

| Reprinted from: Electronics 2020, 9, 1534, doi:10.3390/electronics9091534                                                                                            |

| Oleksandr Husev, Tatiana Shults, Dmitri Vinnikov, Carlos Roncero-Clemente,<br>Enrique Romero-Cadaval and Andrii Chub                                                 |

| Comprehensive Comparative Analysis of Impedance-Source Networks for DC and AC Application                                                                            |

| Reprinted from: Electronics 2019, 8, 405, doi:10.3390/electronics8040405                                                                                             |

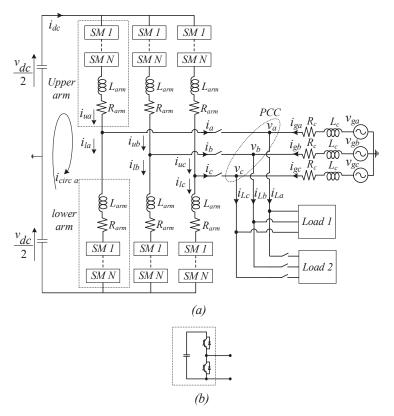

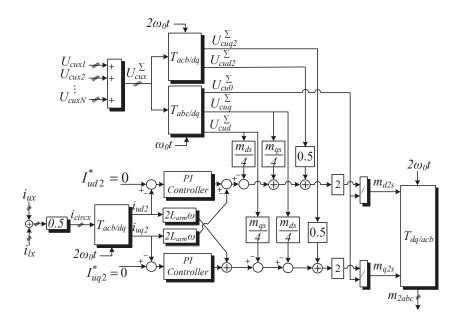

| Fatemeh Shahnazian, Ebrahim Adabi, Jafar Adabi, Edris Pouresmaeil, Kumars Rouzbehi,<br>Eduardo M. G. Rodrigues and João P. S. Catalão                                |

| Control of MMC-Based STATCOM as an Effective Interface between Energy Sources and the Power Grid                                                                     |

| Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 1264, doi:10.3390/electronics8111264                                                                     |

| Mehrdad Mahmoudian, Eduardo M. G. Rodrigues and Edris Pouresmaeil                                                                                                    |

| An Efficient H7 Single-Phase Photovoltaic Grid Connected Inverter for CMC Conceptualization and Mitigation Method                                                    |

| Reprinted from: <i>Electronics</i> <b>2020</b> , <i>9</i> , 1440, doi:10.3390/electronics9091440                                                                     |

| Kumars Rouzbehi, Arash Miranian, Juan Manuel Escaño, Elyas Rakhshani, Negin Shariati<br>and Edris Pouresmaeil                                                        |

| A Data-Driven Based Voltage Control Strategy for DC-DC Converters: Application to DC Microgrid                                                                       |

| Reprinted from: Electronics 2019, 8, 493, doi:10.3390/electronics8050493                                                                                             |

| Filippo Pellitteri, Rosario Miceli, Giuseppe Schettino, Fabio Viola and Luigi Schirone Design and Realization of a Bidirectional Full Bridge Converter with Improved |

| Modulation Strategies Reprinted from: <i>Electronics</i> <b>2020</b> , <i>9</i> , 724, doi:10.3390/electronics9050724                                                |

| Emad Samadaei, Aidin Salehi, Mina Iranian and Edris Pouresmaeil                                                                                                      |

| Single DC Source Multilevel Inverter with Changeable Gains and Levels for Low-Power Loads                                                                            |

| Reprinted from: <i>Electronics</i> <b>2020</b> , <i>9</i> , 937, doi:10.3390/electronics9060937                                                                      |

| Emad Samadaei, Mohammad Kaviani, Mina Iranian and Edris Pouresmaeil                                                                                                  |

| The P-Type Module with Virtual DC Links to Increase Levels in Multilevel Inverters                                                                                   |

| Reprinted from: Electronics 2019, 8, 1460, doi:10.3390/electronics8121460                                                                                            |

| Amir Heidary, Hamid Radmanesh, Ali Moghim, Kamran Ghorbanyan, Kumars Rouzbehi,                                                                                       |

| Eduardo M. G. Rodrigues and Edris Pouresmaeil                                                                                                                        |

| A Multi-Inductor H Bridge Fault Current Limiter  Reprinted from: Electronics 2019, 8, 795, doi:10.3390/electronics8070795                                            |

|                                                                                                                                                                      |

| Janina Rzasa         An Alternative Carrier-Based Implementation of Space Vector Modulation to Eliminate         Common Mode Voltage in a Multilevel Matrix Converter         Reprinted from: Electronics 2019, 8, 190, doi:10.3390/electronics8020190                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amir Heidary, Hamid Radmanesh, Ali Bakhshi, Kumars Rouzbehi and Edris Pouresmaeil  A Compound Current Limiter and Circuit Breaker Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 551, doi:10.3390/electronics8050551                                                                         |

| Peifei Li, Lei Zhang, Bin Ouyang and Yong Liu Nonlinear Effects of Three-Level Neutral-Point Clamped Inverter on Speed Sensorless Control of Induction Motor Reprinted from: Electronics 2019, 8, 402, doi:10.3390/electronics8040402                                                                     |

| Guozheng Zhang, Chen Chen, Xin Gu, Zhiqiang Wang and Xinmin Li  An Improved Model Predictive Torque Control for a Two-Level Inverter Fed Interior Permanent Magnet Synchronous Motor  Reprinted from: Electronics 2019, 8, 769, doi:10.3390/electronics8070769                                            |

| Young-Bae Ji and Jung-Hyo Lee Feedforward Interpolation Error Compensation Method for Field Weakening Operation Region of PMSM Drive Reprinted from: Electronics 2019, 8, 1052, doi:10.3390/electronics8091052 205                                                                                        |

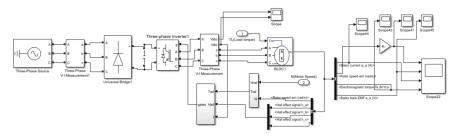

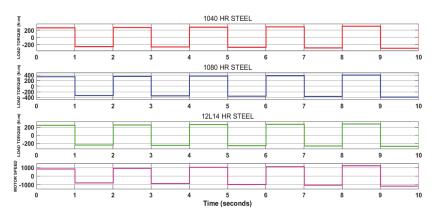

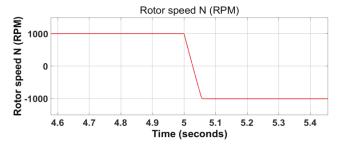

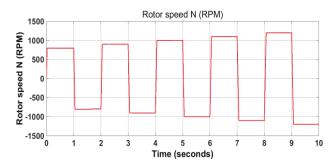

| Mohanraj N., Sankaran R., Subashini N. and Shriram S. Rangarajan  Novel Efficacious Utilization of Fuzzy-Logic Controller-Based Two-Quadrant Operation of PMBLDC Motor Drive Systems for Multipass Hot-Steel Rolling Processes  Reprinted from: Electronics 2020, 9, 1008, doi:10.3390/electronics9061008 |

| Xiujuan Wang, Zhihong Fu, Yao Wang, Wendong Wang, Wei Liu and Junli Zhao  A Wide-Frequency Constant-Amplitude Transmitting Circuit for Frequency Domain Electromagnetic Detection Transmitter  Reprinted from: Electronics 2019, 8, 640, doi:10.3390/electronics8060640                                   |

| Cunxue Wu, Feng Gao, Hanzhe Dai and Zilong Wang A Topology-Based Approach to Improve Vehicle-Level Electromagnetic Radiation Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 364, doi:10.3390/electronics8030364                                                                              |

| Shen-Li Chen, Pei-Lin Wu and Yu-Jen Chen Robust ESD-Reliability Design of 300-V Power N-Channel LDMOSs with the Elliptical Cylinder Super-Junctions in the Drain Side Reprinted from: Electronics 2020, 9, 730, doi:10.3390/electronics9050730                                                            |

| Chunlong Zhang, Hongyan Xing, Pengfei Li, Chunying Li, Dongbo Lv and Shaojie Yang<br>An Experimental Study of the Failure Mode of ZnO Varistors Under Multiple Lightning Strokes<br>Reprinted from: <i>Electronics</i> <b>2019</b> , <i>8</i> , 172, doi:10.3390/electronics8020172                       |

| Chunlong Zhang, Chunying Li, Dongbo Lv, Hao Zhu and Hongyan Xing An Experimental Study on the Effect of Multiple Lightning Waveform Parameters on the Aging Characteristics of ZnO Varistors Reprinted from: Electronics 2020, 9, 930, doi:10.3390/electronics9060930 293                                 |

|                                                                                                                                                                                                                                                                                                           |

### **About the Editors**

Eduardo M. G. Rodrigues received his degree in Electromechanical Engineering from the University of Beira Interior (UBI), Portugal. Before becoming a PhD Researcher with UBI under the EU FP7 funded Project "Smart and Sustainable Insular Electricity Grids Under Large-Scale Renewable Integration", he gained significant industrial experience in different industrial sectors, namely in control valve manufacturing, the automotive industry, and in steel casting foundries, covering different technical areas such as quality management systems, product development, electrical and mechanical assistance in the heavy mechanical sector, automation development, and technical support in MW-size resonant inverter-controlled induction furnaces. As part of the researching consortium and during the first stage of his PhD studies, he collaborated onsite with the team responsible for energy storage technology at Department of Future Technology Execution, Alstom Power (Switzerland). He collaborated as Postdoctoral Researcher in the Compete 2020 -Portugal funded project "Enhancing Smart GRIDs for Sustainability" and as task leader at University of Beira Interior. Currently, he is invited Assistant Professor at University of Aveiro - School of Design, Management and Production Technologies, Aveiro North. In addition, he has a managing role in an engineering firm, being one its founders, where he has acquired the function of hardware and firmware engineer, providing industrial machine retrofitting services, automation-based control solutions, and industrial electronics products designed in-house. He has authored or co-authored more than 70 indexed international journals, book chapters and conference proceedings papers. He is Editor for journals Electronics, Automation, and Ad Hoc & Sensor Wireless Networks and has also served as a member of more than 40 international conference committees. His research interests are in industrial electronics, advanced industrial power electronics applications, instrumentation and signal acquisition, digital signal processing, and the implementation of advanced control techniques.

Edris Pouresmaeil received his PhD degree in Electrical Engineering (with honors) from the Technical University of Catalonia BarcelonaTech (CITCEA-UPC), Barcelona, Spain, in 2012. After completing his PhD, he joined the Department of Electrical and Computer Engineering, at the University of Waterloo, ON, Canada, as a Postdoctoral Research Fellow. Following his postdoctoral appointment, he was appointed Associate Professor at the Centre for Energy Informatics, University of Southern Denmark (SDU), Odense, Denmark. He is currently Associate Professor with the Department of Electrical Engineering and Automation (EEA) at Aalto University, Espoo, Finland. His main research fields are operation and control of power electronics in power systems, integration of large-scale renewable energy sources into the low-inertia power grid, ICT-based power networks, smart grids, microgrid operation and control, and simulator design and software development for smart grid applications. Dr. Pouresmaeil is Senior Member of the IEEE.

Radu Godina received his PhD degree from University of Beira Interior (UBI), Covilha, Portugal, and since 2019, has served at the Department of Mechanical and Industrial Engineering as invited Assistant Professor at NOVA School of Science and Technology (FCT), Universidade NOVA de Lisboa (NOVA University Lisbon), Portugal. He has authored or co-authored more than 110 indexed international journals, book chapters, and conference proceedings papers. He served as a member of 50 international scientific conferences related to such topics as energy, sustainability, and industrial engineering. Radu Godina is Editor of the Swiss journal *Applied Sciences* and of the *European Journal*

of Sustainable Development Research. His main research fields are industrial symbiosis, sustainability, lean manufacturing, electric vehicles, circular economy, model predictive control, and quality control.

Editoria

## **Industrial Applications of Power Electronics**

Eduardo M. G. Rodrigues 1,\*, Radu Godina 2,\* and Edris Pouresmaeil 3,\*

- Management and Production Technologies of Northern Aveiro—ESAN, Estrada do Cercal 449, Santiago de Riba-Ul, 3720-509 Oliveira de Azeméis, Portugal

- UNIDEMI, Department of Mechanical and Industrial Engineering, Faculty of Science and Technology (FCT), Universidade NOVA de Lisboa, 2829-516 Caparica, Portugal

- Department of Electrical Engineering and Automation, Aalto University, Office 3563, Maarintie 8, 02150 Espoo, Finland

- Correspondence: emgrodrigues@ua.pt (E.M.G.R.); r.godina@fct.unl.pt (R.G.); edris.pouresmaeil@aalto.fi (E.P.)

Received: 16 September 2020; Accepted: 18 September 2020; Published: 19 September 2020

Abstract: Electronic applications use a wide variety of materials, knowledge, and devices, which pave the road to creative design, development, and the creation of countless electronic circuits with the purpose of incorporating them in electronic products. Therefore, power electronics have been fully introduced in industry, in applications such as power supplies, converters, inverters, battery chargers, temperature control, variable speed motors, by studying the effects and the adaptation of electronic power systems to industrial processes. Recently, the role of power electronics has been gaining special significance regarding energy conservation and environmental control. The reality is that the demand for electrical energy grows in a directly proportional manner with the improvement in quality of life. Consequently, the design, development, and optimization of power electronics and controller devices are essential to face forthcoming challenges. In this Special Issue, 19 selected and peer-reviewed papers discussing a wide range of topics contribute to addressing a wide variety of themes, such as motor drives, AC-DC and DC-DC converters, electromagnetic compatibility and multilevel converters.

**Keywords:** power converters; electrical machines; power grid stability analysis; inverters; power supplies; power quality; multilevel converters; motor drives; power semiconductor devices; electromagnetic compatibility

#### 1. Introduction

In recent years, power electronics have been intensely contributing to the development and evolution of new structures for the processing of energy. It is becoming very common to generate electrical energy in different ways and convert it into another form in order to be able to use it—for instance, renewable sources, battery banks, and the transmission of electric power in direct current (DC), which makes the voltage of the network available in different levels, in detriment to the supplied voltage from the grid [1]. The main users of these signals are pieces of electronic equipment that use voltages at levels different from that which is available from the grid; the drives of electrical machines, which modify the voltage of the electrical network (amplitude and frequency) to control the machines and finally, in electrical systems, DC power transmission and frequency conversion [2].

Two leading trends are currently noticeable in the power systems field of study. The first trend is the increasingly and prevalent employment of renewable energy resources. The second trend is decentralized energy generation. This scenario raises many challenges. Therefore, the design, development, and optimization of power electronics and controller devices are required in order to face such challenges. New microprocessor control units (MCUs) could be utilized for power production

control and for remote control operation, while power electronic converters are and could be utilized to control the power flow [3].

Nevertheless, power electronics can be used for a wide range of applications, from power systems and electrical machines to electric vehicles and robot arm drives [4]. In conjunction with the evolution of microprocessors and advanced control theories, power electronics are playing an increasingly essential role in our society [5].

Thus, in order cope with the obstacles lying ahead, original studies and modelling methods can be developed and proposed that could overcome the physical and technical boundary conditions and at the same time, consider technical, economic, and environmental aspects. The objective of this Special Issue was to present studies in the field of electrical energy conditioning and control using circuits and electronic devices, with an emphasis on power applications and industrial control. Therefore, researchers contributed their manuscripts to this Special Issue, and contribute models, proposals, reviews, and studies. In this Special Issue, 19 selected and peer-reviewed papers contribute to a wide range of topics, by addressing a wide variety of themes, such as motor drives, AC-DC and DC-DC Converters, multilevel converters and electromagnetic compatibility, among others.

A significant portion of the currently produced electricity worldwide is mostly generated by centralized systems, based on conventional fossil fuel plants or nuclear power [6,7]. The barriers that policy makers, researchers, and engineers have to overcome when it comes to the operation and control of conventional power plants, and the development of low voltage power generation systems, have paved the way for diverse opportunities of energy generation, closer to the load, by the customers themselves, also known as distributed generation (DG) [8]. Thus, concerning this topic, several papers are published in this Issue.

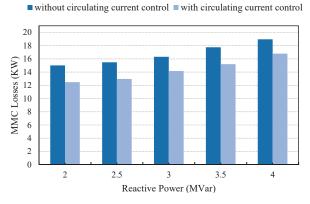

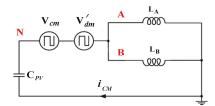

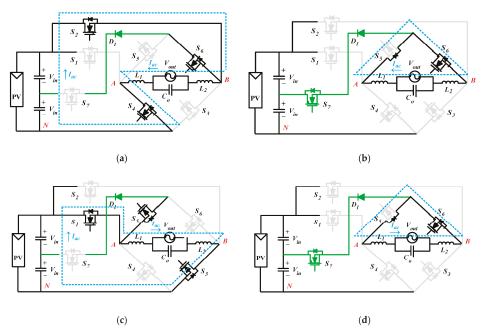

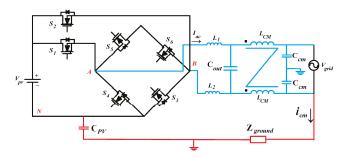

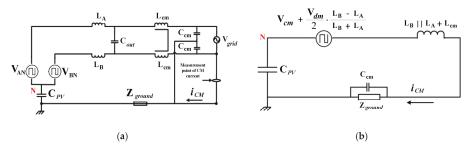

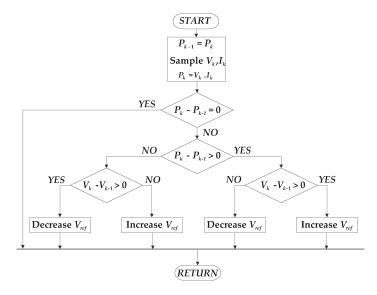

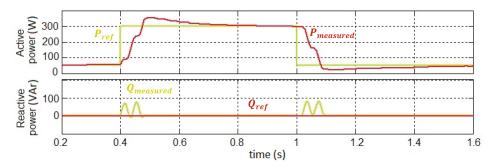

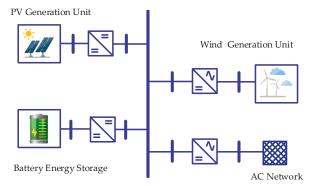

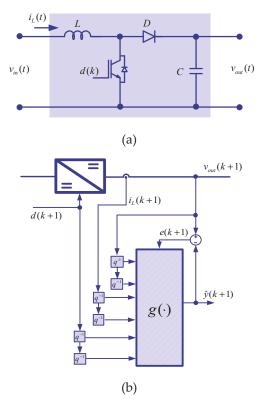

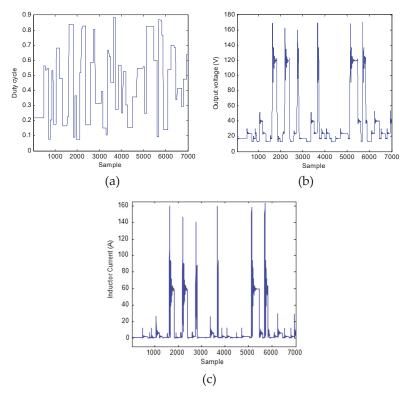

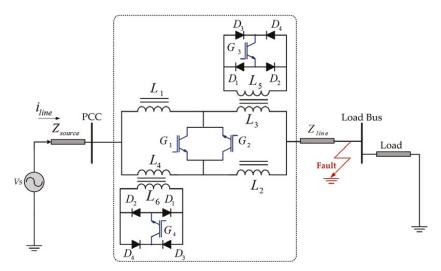

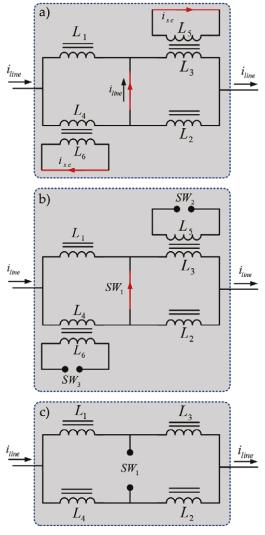

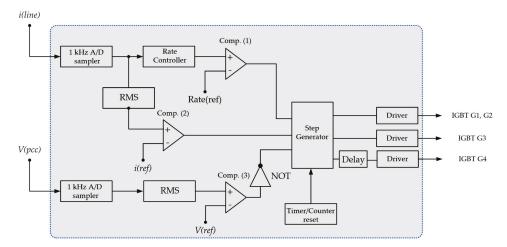

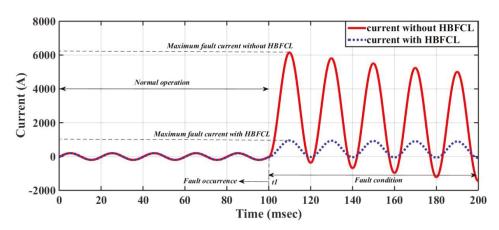

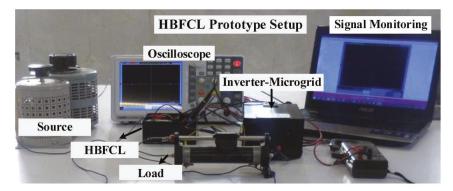

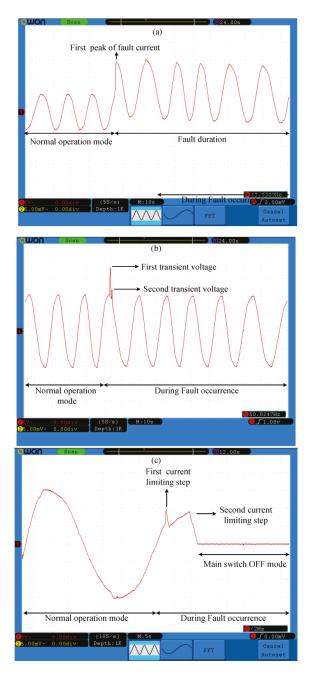

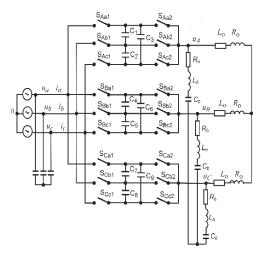

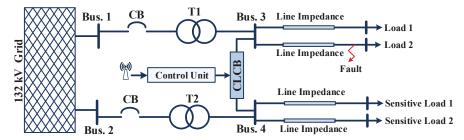

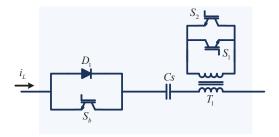

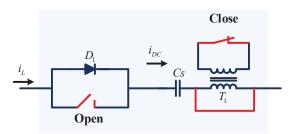

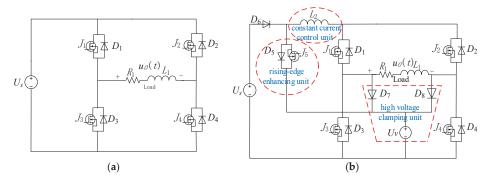

In [9], an efficient H7 single-phase photovoltaic grid-connected inverter for common mode current conceptualization and mitigation is proposed. Specifically, an extended H6 transformerless inverter that operates with an additional power switch (H7) is utilised for improving the common mode leakage current mitigation in a single-phase utility grid. A new control for a modular multilevel converter (MMC) based static synchronous compensator (STATCOM) is proposed in [10] as an effective interface between energy sources and the power grid. This study showed that the proposed control method led to an effective reduction in capacitor voltage fluctuation and losses. The protection of sensitive loads against voltage drop is a challenge for the power system, especially in face of the rising use of DG. Thus, in order to address this obstacle, a compound current limiter and circuit breaker is proposed in [11] and validated through experimental and simulation results. The authors argue that in this study that the proposed compound current limiter is able to limit the fault current and fast break in order to adjust voltage sags at the protected buses. A data-driven based voltage control strategy for DC-DC converters, which are increasingly used to integrate renewable energy resources, with the aim of applying them to DC microgrids is given in [12]. Because these converters can be used for so many applications, suitable modelling and control methods are necessary for their voltage regulation. Simulations performed in this study show a satisfying performance of the data-driven control strategy. Since DG will most likely cause a higher occurrence of fault current levels, in [13], a multi-inductor H bridge fault current limiter is proposed in order to reduce the frequency of occurrence of such types of problems. Positive results are obtained through experimental and simulated tests.

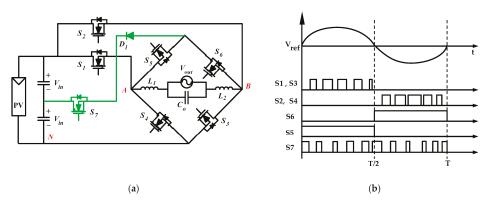

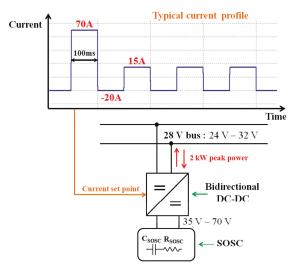

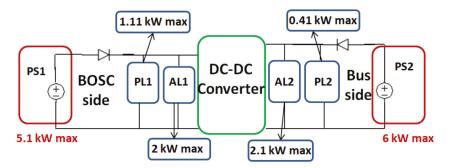

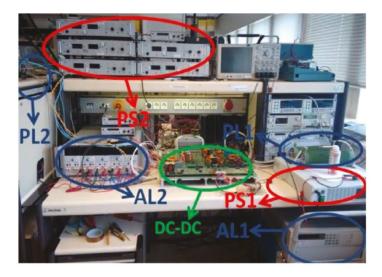

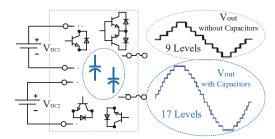

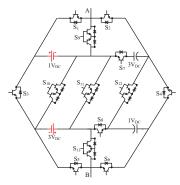

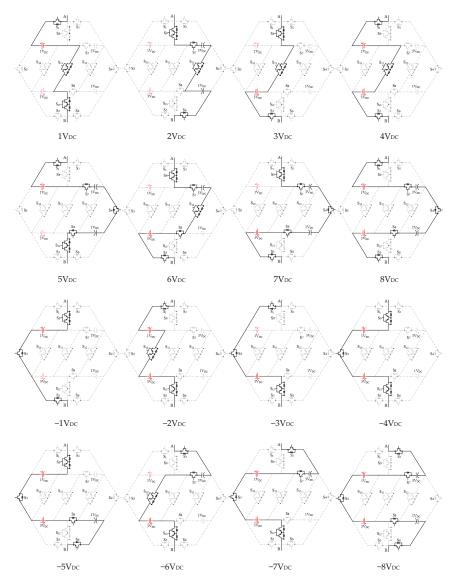

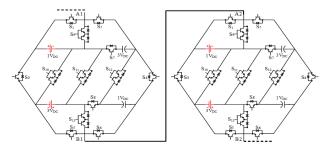

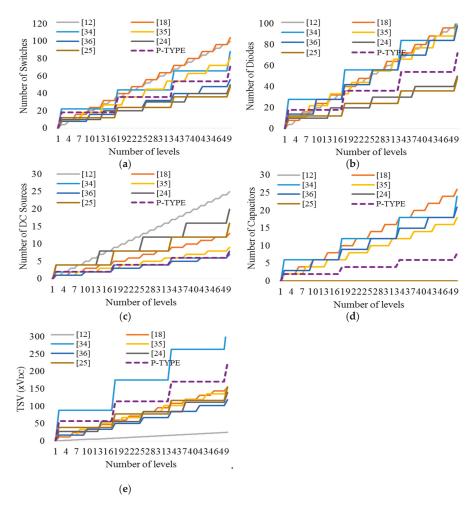

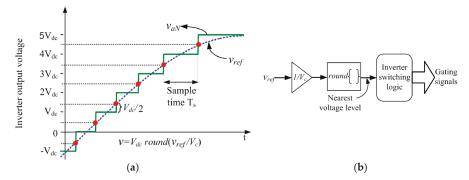

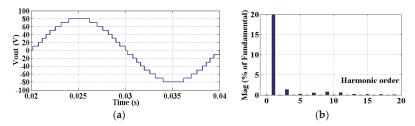

As for research studies revolving around converters, a full-bridge converter (FBC) for bidirectional power transfer is presented in [14]. The proposed FBC is an isolated DC-DC bidirectional converter, linked to a double voltage source—a voltage bus on one side, and a stack of super-capacitors (SOSC) on the other side and real prototype, compliant with automotive applications. In [15], a single DC source multilevel inverter with changeable gains and levels for low-power loads is proposed. The validation of this inverter was conducted through simulation and experimental tests using nine different modulations. A p-type module with virtual DC links to increase levels in multilevel inverters is proposed in [16], which are able to produce higher voltage levels with a lower number of components, making them appropriate for a wide range of applications. In another study [17], Janina Rząsa proposes

an alternative carrier-based implementation of space vector modulation to eliminate common mode voltage in a multilevel matrix converter and evidences that part of the high-frequency output voltage distortion component is eliminated. The proposed modulation method is validated though simulation and experimental results. A comprehensive comparative analysis of impedance-source based DC-DC and DC-AC converters regarding passive component count and size, range of input voltage variation, and semiconductor stress is proposed in [18]. The authors analyzed the main impedance-source converters with or without inductor coupling and with or without a transformer; useing simulations and experiments to validate this.

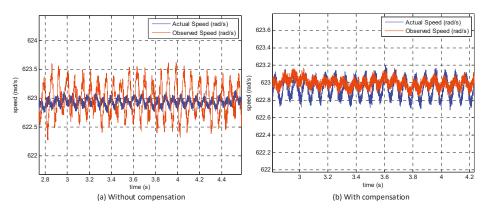

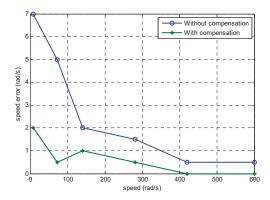

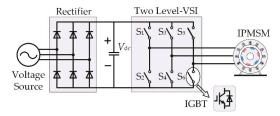

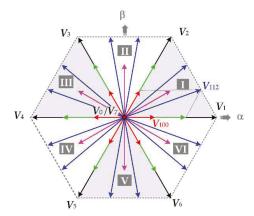

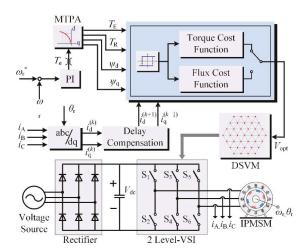

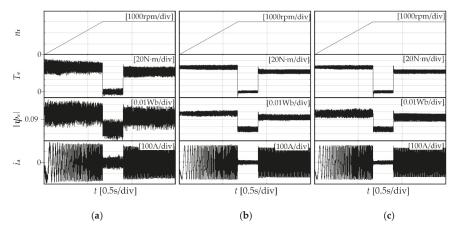

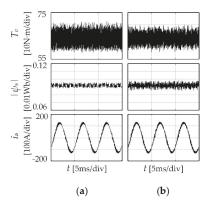

Converters and inverters are used for several applications, as gathered from the above-mentioned studies, and as so, they are also used for permanent-magnet synchronous machines (PMSM). An improved model predictive torque control combined with discrete space vector modulation for a two-level inverter fed interior PMSM is proposed in [19] and the authors establish a cost function involving the excitation torque and reluctance torque. Simulation and experimental results are used to validate this study, in which the torque ripple and current ripple is reduced. The nonlinear effects, such as voltage and command voltage deviation, of a three-level neutral-point clamped inverter on speed sensorless control of an induction motor are studied in [20]. In this study a new voltage deviation compensation measure based on the volt-second balance principle is proposed and validated through experimental results.

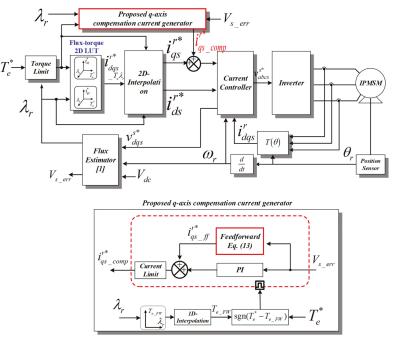

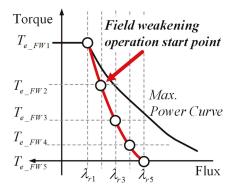

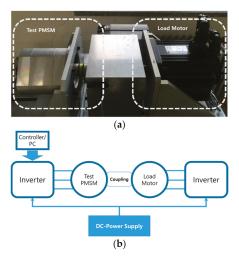

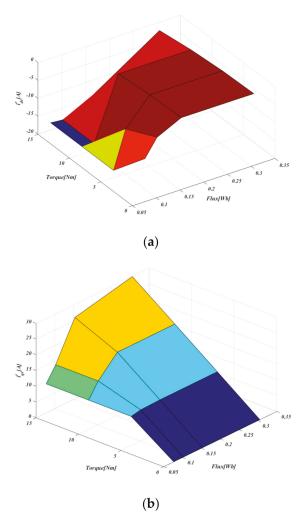

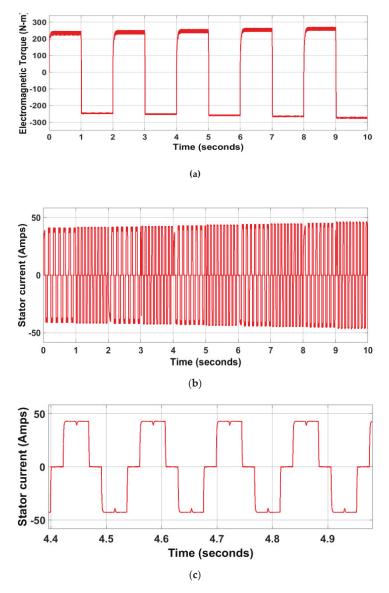

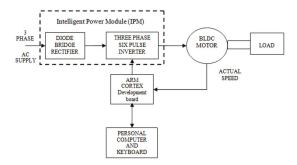

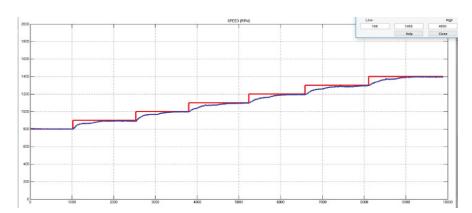

Extensive research is also made in the area of motor drives. A new effective use and operation of fuzzy-logic controller-based two-quadrant operation of a permanent magnet brushless DC motor drive system for multipass hot-steel rolling processes is proposed in [21], with validation through simulation and experimental tests provided. Another study [22], proposed a field weakening control method that employs interpolation error compensation of the look-up table based PMSM method. As in the majority of these studies, the improvement reached by using the proposed method is validated through experimental and simulation tests.

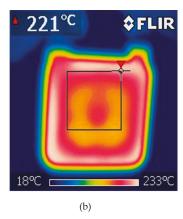

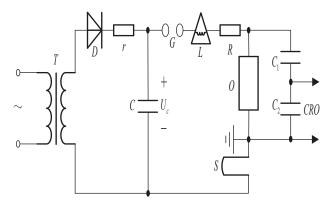

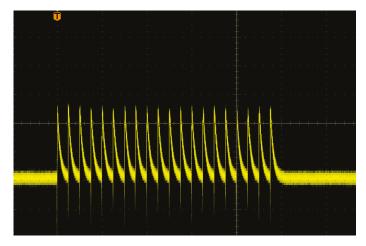

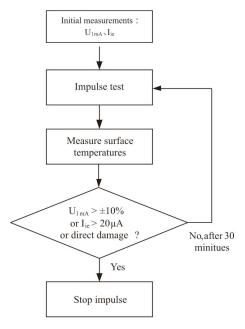

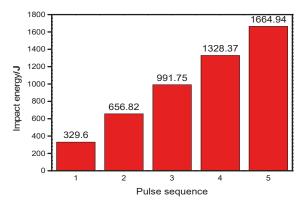

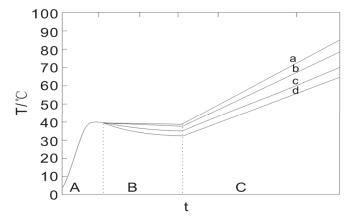

Non-linear ceramic resistors such as metal oxide ZnO-based varistors are mainly utilised to protect electronic and electric circuits from overvoltage. The ZnO varistor, also known as metal oxide varistor, is the most well-known type of varistor, and, as such, it is a topic that attracts attention from the research community. This Special Issue is no exception. An experimental study on the effect of multiple lightning waveform parameters on the aging characteristics of ZnO varistors is proposed in [23], in which the aging rate and surface temperature rise of ZnO varistor under the impact of multi-pulse current was examined. Another experimental study was made in [24] by focusing on the failure mode of ZnO varistors under multiple lightning strokes, in which alterations were observed in the performance of these ZnO varistors after multiple lightning impulses. These changes were analyzed from micro and macro perspectives.

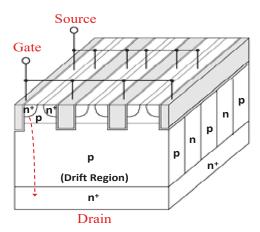

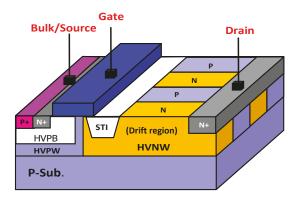

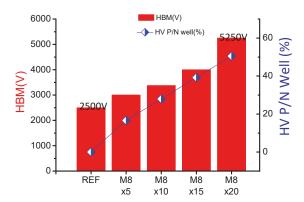

In the semiconductor area of research, a robust electrostatic discharge reliability design of an ultra-high voltage 300-V power n-channel lateral diffused MOSFETs, with elliptical cylinder super-junctions in the drain side, is given in [25]. The authors have concluded that this is a decent strategy and the human-body model capability of these ultra-high voltage n-channel lateral diffused MOSFETs could be successfully improved without altering the basic electrical properties or adding any extra cell area.

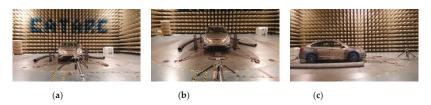

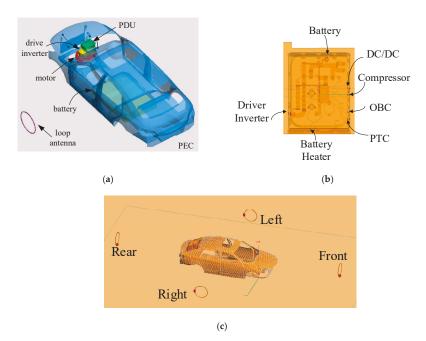

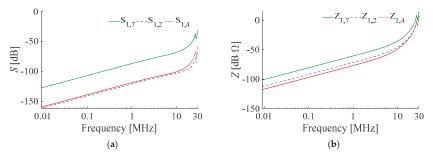

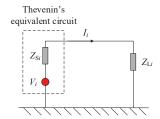

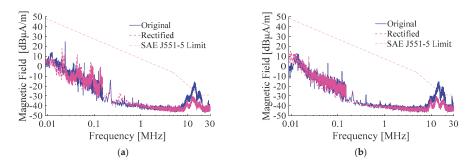

In this area of electromagnetism, a novel AC magnetic transmitter current source circuit is proposed in [26] for the application of frequency domain electromagnetic method prospecting. The proposed current source circuit is able to generate high frequency and high constant amplitude currents, which are the main technical problems for the frequency domain electromagnetic method. The results obtained through simulation and experimental tests show that the proposed circuit achieves the linearity of the rising/falling edge, a short reversal time, a low power loss, and a constant amplitude. Since the penetration of electric vehicles is constantly growing in the market, in another study [27], a new topology-based approach to improve vehicle-level electromagnetic radiation is proposed due to the fact that electric vehicles suffer from various electromagnetic interferences. The efficacy of this

method was demonstrated through experimental tests that compared the predicted vehicle-radiated emissions at low frequency with the obtained experimental results.

Improved control methods, better energy efficiency and problem mitigation can be achieved at any level and in almost any system, as can be seen in the contributions to this Special Issue. Even though numerous challenges still remain, research and technology are vital tools for overcoming the challenges that arise in power electronics, specially by heading towards responsible and careful use of the environment. Power electronics plays a key role in the development of renewable energy systems and, therefore, in reducing greenhouse gases. Therefore, through small incremental steps, the objective is to strengthen the role of innovation, with the aim of facing the challenges that lay ahead [28] with efficient responses that, additionally, can ensure an economical, reliable and sustainable electrical supply, on which we have grown to become so dependent.

**Author Contributions:** E.M.G.R., R.G. and E.P.; writing—original draft, E.M.G.R., R.G. and E.P.; writing—Review and editing, E.M.G.R., R.G. and E.P. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Acknowledgments: This Special Issue is the result of the contributions of various talented authors, experienced reviewers, and the devoted editorial team of *Electronics*. Thanks are due to all authors and peer reviewers. Finally, the editorial team of *Electronics* "Power Electronics" Section are to be congratulated for the success of this project, and in particular, thanks are due to Judy Jia, Eric Lin, Xenia Xie and Josephine Yang, and especially to Michelle Zhou, Assistant Editor from MDPI Branch Office, Beijing.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Rehg, J.A.; Sartori, G.J. Industrial Electronics, 1st ed.; Pearson Prentice Hall: Upper Saddle River, NJ, USA, 2006; ISBN 978-0-13-206418-7.

- 2. Rashid, M.H. (Ed.) Power Electronics Handbook, 3rd ed.; Butterworth-Heinemann: Oxford, UK, 2011.

- Perreault, D.J.; Afridi, K.K.; Khan, I.A. 32-Automotive Applications of Power Electronics. In *Power Electronics Handbook*, 4th ed.; Rashid, M.H., Ed.; Butterworth-Heinemann: Oxford, UK, 2018; pp. 1067–1090. ISBN 978-0-12-811407-0.

- 4. Pollefliet, J. 15-Applications of Power Electronics. In *Power Electronics*; Pollefliet, J., Ed.; Academic Press: Cambridge, MA, USA, 2018; pp. 15.1–15.44. ISBN 978-0-12-814643-9.

- Siwakoti, Y.P.; Forouzesh, M.; Ha Pham, N. Chapter 1-Power Electronics Converters—An Overview. In Control of Power Electronic Converters and Systems; Blaabjerg, F., Ed.; Academic Press: Cambridge, MA, USA, 2018; pp. 3–29. ISBN 978-0-12-805245-7.

- Funcke, S.; Ruppert-Winkel, C. Storylines of (de)centralisation: Exploring infrastructure dimensions in the German electricity system. *Renew. Sustain. Energy Rev.* 2020, 121, 109652. [CrossRef]

- Agnew, S.; Smith, C.; Dargusch, P. Understanding transformational complexity in centralized electricity supply systems: Modelling residential solar and battery adoption dynamics. *Renew. Sustain. Energy Rev.* 2019, 116, 109437. [CrossRef]

- 8. Blaabjerg, F.; Chen, Z.; Kjaer, S.B. Power electronics as efficient interface in dispersed power generation systems. *IEEE Trans. Power Electron.* **2004**, *19*, 1184–1194. [CrossRef]

- Mahmoudian, M.; Rodrigues, E.M.G.; Pouresmaeil, E. An Efficient H7 Single-Phase Photovoltaic Grid Connected Inverter for CMC Conceptualization and Mitigation Method. *Electronics* 2020, 9, 1440. [CrossRef]

- Shahnazian, F.; Adabi, E.; Adabi, J.; Pouresmaeil, E.; Rouzbehi, K.; Rodrigues, E.M.G.; Catalão, J.P.S. Control

of MMC-Based STATCOM as an Effective Interface between Energy Sources and the Power Grid. *Electronics*2019, 8, 1264. [CrossRef]

- 11. Heidary, A.; Radmanesh, H.; Bakhshi, A.; Rouzbehi, K.; Pouresmaeil, E. A Compound Current Limiter and Circuit Breaker. *Electronics* **2019**, *8*, 551. [CrossRef]

- Rouzbehi, K.; Miranian, A.; Escaño, J.M.; Rakhshani, E.; Shariati, N.; Pouresmaeil, E. A Data-Driven Based Voltage Control Strategy for DC-DC Converters: Application to DC Microgrid. *Electronics* 2019, 8, 493. [CrossRef]

- Heidary, A.; Radmanesh, H.; Moghim, A.; Ghorbanyan, K.; Rouzbehi, K.; Rodrigues, E.M.G.; Pouresmaeil, E. A Multi-Inductor H Bridge Fault Current Limiter. *Electronics* 2019, 8, 795. [CrossRef]

- 14. Pellitteri, F.; Miceli, R.; Schettino, G.; Viola, F.; Schirone, L. Design and Realization of a Bidirectional Full Bridge Converter with Improved Modulation Strategies. *Electronics* **2020**, *9*, 724. [CrossRef]

- Samadaei, E.; Salehi, A.; Iranian, M.; Pouresmaeil, E. Single DC Source Multilevel Inverter with Changeable Gains and Levels for Low-Power Loads. *Electronics* 2020, 9, 937. [CrossRef]

- Samadaei, E.; Kaviani, M.; Iranian, M.; Pouresmaeil, E. The P-Type Module with Virtual DC Links to Increase Levels in Multilevel Inverters. *Electronics* 2019, 8, 1460. [CrossRef]

- Rząsa, J. An Alternative Carrier-Based Implementation of Space Vector Modulation to Eliminate Common Mode Voltage in a Multilevel Matrix Converter. *Electronics* 2019, 8, 190. [CrossRef]

- Husev, O.; Shults, T.; Vinnikov, D.; Roncero-Clemente, C.; Romero-Cadaval, E.; Chub, A. Comprehensive Comparative Analysis of Impedance-Source Networks for DC and AC Application. *Electronics* 2019, 8, 405. [CrossRef]

- 19. Zhang, G.; Chen, C.; Gu, X.; Wang, Z.; Li, X. An Improved Model Predictive Torque Control for a Two-Level Inverter Fed Interior Permanent Magnet Synchronous Motor. *Electronics* **2019**, *8*, 769. [CrossRef]

- 20. Li, P.; Zhang, L.; Ouyang, B.; Liu, Y. Nonlinear Effects of Three-Level Neutral-Point Clamped Inverter on Speed Sensorless Control of Induction Motor. *Electronics* **2019**, *8*, 402. [CrossRef]

- Nandakumar, M.; Ramalingam, S.; Nallusamy, S.; Rangarajan, S.S. Novel Efficacious Utilization of Fuzzy-Logic Controller-Based Two-Quadrant Operation of PMBLDC Motor Drive Systems for Multipass Hot-Steel Rolling Processes. *Electronics* 2020, 9, 1008. [CrossRef]

- Ji, Y.-B.; Lee, J.-H. Feedforward Interpolation Error Compensation Method for Field Weakening Operation Region of PMSM Drive. Electronics 2019, 8, 1052. [CrossRef]

- Zhang, C.; Li, C.; Lv, D.; Zhu, H.; Xing, H. An Experimental Study on the Effect of Multiple Lightning Waveform Parameters on the Aging Characteristics of ZnO Varistors. Electronics 2020, 9, 930. [CrossRef]

- 24. Zhang, C.; Xing, H.; Li, P.; Li, C.; Lv, D.; Yang, S. An Experimental Study of the Failure Mode of ZnO Varistors Under Multiple Lightning Strokes. *Electronics* **2019**, *8*, 172. [CrossRef]

- 25. Chen, S.-L.; Wu, P.-L.; Chen, Y.-J. Robust ESD-Reliability Design of 300-V Power N-Channel LDMOSs with the Elliptical Cylinder Super-Junctions in the Drain Side. *Electronics* **2020**, *9*, 730. [CrossRef]

- Wang, X.; Fu, Z.; Wang, Y.; Wang, W.; Liu, W.; Zhao, J. A Wide-Frequency Constant-Amplitude Transmitting Circuit for Frequency Domain Electromagnetic Detection Transmitter. *Electronics* 2019, 8, 640. [CrossRef]

- 27. Wu, C.; Gao, F.; Dai, H.; Wang, Z. A Topology-Based Approach to Improve Vehicle-Level Electromagnetic Radiation. *Electronics* **2019**, *8*, 364. [CrossRef]

- Mendes, T.D.P.; Godina, R.; Rodrigues, E.M.G.; Matias, J.C.O.; Catalão, J.P.S. Smart and energy-efficient home implementation: Wireless communication technologies role. In Proceedings of the 2015 IEEE 5th International Conference on Power Engineering, Energy and Electrical Drives (POWERENG), Riga, Latvia, 11–13 May 2015; pp. 377–382.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

# Comprehensive Comparative Analysis of Impedance-Source Networks for DC and AC Application

Oleksandr Husev $^1$ , Tatiana Shults $^2$ , Dmitri Vinnikov $^1$ , Carlos Roncero-Clemente $^3$ , Enrique Romero-Cadaval $^{3,*}$  and Andrii Chub $^1$

- Department of Electrical Power Engineering and Mechatronics, School of Engineering, Tallinn University of Technology, Ehitajate tee 5, 19086 Tallinn, Estonia; oleksandr.husev@ieee.org (O.H.); dmitri.vinnikov@ttu.ee (D.V.); andrusha.chub@gmail.com (A.C.)

- Power Electronics Institute, Novosibirsk State Technical University, 630073 Novosibirsk, Russia; tanuta91@mail.ru

- <sup>3</sup> Power Electrical and Electronics System Research Group, University of Extremadura, 06006 Badajoz, Spain; croncero@peandes.net

- \* Correspondence: eromero@unex.es; Tel.: +34-924-289-300 (ext. 86787)

Received: 19 March 2019; Accepted: 2 April 2019; Published: 5 April 2019

Abstract: This paper presents a comprehensive analytical comparison of the impedance-source-based dc-dc and dc-ac converters in terms of the passive component count and size, semiconductor stress, and range of input voltage variation. The conventional solution with a boost converter was considered as a reference value. The main criterion of the comprehensive comparison was the energy stored in the passive elements, which was considered both under a constant and predefined high frequency current ripple in the inductors and the voltage ripple across the capacitors. Main impedance-source converters with or without a transformer and with or without inductor coupling were analyzed. Dc-dc and dc-ac applications were considered. Selective simulation results along with experimental verification are shown. The conclusions provide a selection guide of impedance-source networks for different applications taking into account its advantages and disadvantages.

Keywords: impedance-source inverter; shoot-through; dc-dc converter; dc-ac converter

#### 1. Introduction

The Z-source inverter (ZSI) was introduced in 2003 [1]. It was claimed that the converter overcomes the conceptual and theoretical barriers and limitations of the traditional voltage-source inverter (VSI) and current-source (CS) inverter and provides a novel power conversion concept. ZSI utilizes the shoot-through (ST) cross-conduction states to boost the input dc-voltage by switching on both the top and bottom switches of at least one inverter leg. ZSI can buck-boost voltage, minimize component count, increase efficiency, and reduce the cost. This topology also has no forbidden switching states, which improves converter reliability significantly.

This solution is intended for various fields of application: dc-dc, ac-ac, ac-ac, and dc-ac. In particular, it is suitable for grid integration or electric drive control [1–4]. Further, the quasi-Z-source (qZS) network was proposed in [2]. As compared to the Z-source (ZS) network, it has a continuous conduction mode (CCM) of the input current. Also, the volume of the capacitors may be lower in the qZS network. Due to these features, ZS and qZS networks have been named as the most suitable solution for renewable energy applications. Many papers have studied in detail possibilities for such applications [5–7]. Steady-state analysis and dynamic analysis along with different control strategies have been described in detail [8–25].

Since then, many derivative topologies of impedance source (IS) networks have been presented. The main justification of the presented solutions is that they overcome drawbacks of the ZS and qZS networks. Mostly, the benefit is in the low dc-link utilization under constant boost control [15–25].

References [26–32] present a good overview of existing solutions. Almost all the presented novel solutions are based on the magnetically coupled inductors. The main hypothesis in those papers addresses possible reductions of size and volumes of passive components due to the increase in the turns ratio in magnetically coupled elements. At the same time, the overall conclusions and predictions seem to be incomplete. These papers are devoted to very general issues related to the gain factor, and the number of active and passive components.

After an in-depth overview of the comparative papers, some contradictory results can be underlined. As a result of a direct comparison between novel and conventional solutions, the conclusions reached contain high uncertainty [33–39]. Several papers reveal only superior performance of the IS-based converters over conventional solutions [33–35]. At the same time, other papers reveal opposite results. In conclusion, despite many studies devoted to the IS derived converters, there are still many open questions.

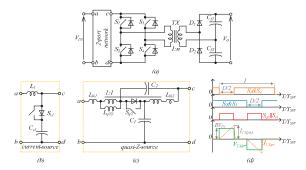

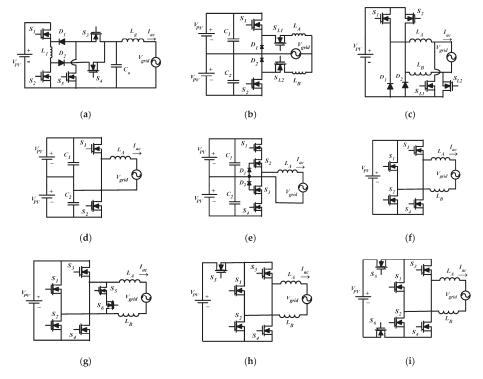

This research work focuses on the comparison between each other by overall dimensions and voltage stress on semiconductors. A comprehensive comparative analysis is provided for all key types of IS networks with conventional solutions for the dc-dc and the dc-ac application. Conventional solutions based on the boost dc-dc converter will be considered as well (Figure 1a).

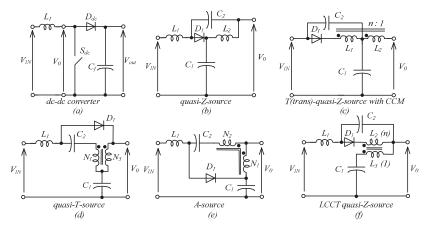

**Figure 1.** Basic impedance source (IS) networks along with the boost dc-dc converter: (a) Boost dc-dc converter, (b) quasi-Z-source, (c) trans (T)-quasi-Z-source, (d) quasi-T-source, (e) A-source, and (f) LCCT quasi-Z-source.

The paper is organized as follows. Section 2 presents a brief overview of IS derived converters. Section 3 describes a comparative analysis approach while Section 4 represents results of comparison. Section 5 is devoted to the pros and cons discussions of IS networks application in galvanically isolated converters. Simulation and experimental study is summarized in Section 6. Finally, conclusions are presented and discussed in Section 7.

#### 2. Brief Overview of IS Derived Converters

Over 20 different types of IS networks subdivided into subgroups have been presented. They may have separated inductors, magnetically coupled inductors, or transformers. Implementation of magnetically coupled inductors or transformers in the IS network can result in a higher voltage boost factor due to the turns ratio. All IS networks can also be divided into those with discontinuous input

current and continuous input current (CIC). At the same time, it has been shown that networks with discontinuous input current have no advantage over topologies that have CIC [30].

Figure 1 shows basic IS networks. The conventional boost converter is presented in Figure 1a as a reference solution that provides the same functionality. Another reason of including the conventional solution here is that some research results claim that novel IS networks have unconditional advantages over the boost converter [33–35].

The first IS network under consideration was the qZS network (Figure 1b). As mentioned above, it has a CIC and the same size and volume of passive components as for ZSI. The other four selected topologies belonged to the magnetically coupled IS networks [29–31]. Since any magnetically coupled inductor can be represented as a combination of leakage inductance, magnetizing inductance, and ideal transformer, any other IS network with a magnetically coupled inductor can be considered a derivation of the above solutions. This was very well demonstrated in [38].

The trans (T)-quasi-Z-source network (Figure 1c) with a CIC was the first network with coupled inductors under consideration [40-47]. As it was shown in [47], despite an additional capacitor, the overall size of capacitors is lower. The quasi-T-source network (Figure 1d) has a CIC and a slightly different configuration.

LCCT networks (Figure 1f) have quite similar features [48]. At the same time, many derivative circuits and types of converters are proposed in [49–53]. Finally, the A-source network (Figure 1e) was one of the latest solutions proposed and will be compared as well [54,55].

The main advantage of all magnetically coupled derived IS networks is the high boost due to the high turns ratio of the transformer. As a result, the ST duty cycle is shorter. At the same time, no studies have demonstrated the impact of the shorter ST duty cycle on the size, volume, and probable cost of the converter.

#### 3. Comparative Analysis Approach

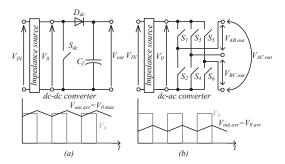

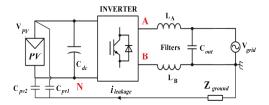

The two possible applications of any IS network are shown in Figure 2. In the dc-dc application, the dc-link voltage is close to the peak voltage across the IS network (Figure 2a). At the same time, the dc-ac converter based on the IS network has no direct dc-link. When the load terminals are shorted through both the upper and lower semiconductor devices of any one phase leg, the energy is accumulating in the inductors of the IS network.

Figure 2. Difference between the output voltage of (a) the impedance source dc-dc converter and (b) the dc-ac converter.

This ST zero state provides the unique buck-boost feature to the inverter. At the same time, average voltage applied to the acload is lower than the peak voltage across the IS network. The ST duty cycle inserted in the switching states reduces the effective dc-link voltage. In other words, the peak voltage generated from the IS network across an inverter should be higher than in the conventional VSI to compensate the zero ST states (Figure 2b). It has to be taken into account in the design of the converter. In particular, voltage stress across semiconductors is increasing.

Maximum boost control (MBC) is a well-known approach in the implementation of the ST states without degradation of dc-link voltage utilization, but this approach cannot be considered as an equivalent alternative because of low frequency input current generation. Such a ripple can be mitigated by increasing the size and cost of passive components, which is not a competitive solution. The modulation techniques with equal ST states distribution are considered for a comparative analysis in this work [22].

Usually, parameters such as the amount of semiconductors, size, and volume of the passive components along with overall power losses define the feasibility of a power electronics converter. In order to include such criteria in the comparative analysis, several assumptions were considered.

The first assumption is that the volume of the magnetic components is proportional to the maximum stored energy  $E_L$ :

$$E_L = \frac{L \cdot I_{MAX}^2}{2},\tag{1}$$

which is estimated by means of the inductance L and the maximum inductor current  $I_{MAX}$ . For convenience and generalization of the analysis, the total magnetics energy in relative units is introduced as:

$$E_{LW} = \sum_{i=1}^{N_L} \frac{L_i \cdot I_{MAXi}^2}{2},$$

(2)

where  $N_L$  is the number of inductances.

A similar parameter can be introduced for the capacitors:

$$E_{CW} = \sum_{i=1}^{N_C} \frac{C_i \cdot V_{MAXi}^2}{2},$$

(3)

where  $E_{CW}$  is the total maximum energy stored in the capacitors and  $N_C$  is the number of capacitors.

It is well known that size, volume, and cost of the capacitors depend on the maximum voltage and capacitance. It should be mentioned that volume and cost also depend on the technology of manufacturing of the magnetic components and capacitors and some corrective coefficients can be introduced [23].

In order to estimate the contribution of the semiconductors to the discussed topologies, their number and blocking voltage are also taken into account.

$$D_{W} = \sum_{i=1}^{N_D} V_{BDi}, \tag{4}$$

$$T_{W} = \sum_{i=1}^{N_{T}} V_{BTi}, \tag{5}$$

The blocking voltage of semiconductors is one of the objective parameters that depends on the topology and can be clearly estimated. The current stress could be taken into account, but it is more difficult to estimate it; moreover, it depends on the passive components.

The size of the passive elements depends on the material and switching frequency as well, but these parameters are assumed to be the same for all topologies. Thereby, the above presented approach will provide results that depend only on the topology itself. The power level, input current ripple, as well as the dc-link voltage ripple are considered equal for all cases under comparison.

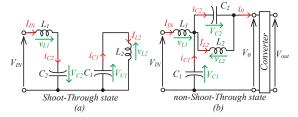

Figure 3 shows equivalent circuits of the qZS network. It shows two main states of the dc-dc or dc-ac converter that are based on the qZS network. ST state (Figure 3a) corresponds to the accumulating energy time period in which the duty cycle is usually denoted as  $D_S$ .

**Figure 3.** Equivalent circuits of the quasi-Z-source network: (a) The shoot-through (ST) state and (b) the non-ST state.

During the ST time interval, the current in the inductor is increasing and energy is accumulating in the inductors. An non-ST equivalent circuit state is depicted in Figure 3b. It corresponds to the time interval when energy is provided to the load and charges the capacitors while the current is decreasing. The average current value remains the same in the steady state condition. The inductance value is usually selected to limit this current ripple. This value of inductance along with the peak current value defines the size, volume, and finally the cost of the inductors.

The calculation of the inductance value is exemplified in many papers [1,8,14,26,33]. The input power level, input voltage range, and the predefined input current ripple are completely sufficient to define the parameters of the magnetic components.

Similar processes are happening in the capacitors. The value of capacitance is selected in order to limit the voltage ripple that is proportional to the power level.

After the steady state analysis presented in the above papers, the summarized equations for selected topologies were derived and are shown in Table 1.

**Table 1.** Summarized equations for selected topologies <sup>1</sup>.

|   | $V_C$                                                                                                                        | $I_L$                                | С                                                                                                                                         | L                                                                                                                                                                  | V <sub>0</sub> dc-dc        | V <sub>0</sub> dc-ac                           |

|---|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------|

| a | $V_{C1} = V_0 = \frac{V_{in}}{1 - D_S}$                                                                                      | $I_{L1} = I_{in}$                    | $C_1 = \frac{D_S (1 - D_S)^2 I_{in}}{V_{in} k_{C1} f_S}$                                                                                  | $L_1 = \frac{V_{in}D_S}{I_{in}k_{L1}f_S}$                                                                                                                          | $\frac{V_{in}}{1-D_S}$      | $\frac{V_{in}}{1-D_S}$                         |

| b | $V_{C1} = \frac{(1-D_S)V_{in}}{1-2D_S}$ $V_{C2} = \frac{D_SV_{in}}{1-2D_S}$                                                  |                                      | $C_1 = \frac{D_S(1-2D_S)I_{in}}{V_{in}(1-D_S)k_{C1}f_S}$ $C_2 = \frac{(1-2D_S)I_{in}}{V_{in}k_{C2}f_S}$                                   | $L_1 = \frac{V_{in}D_S(1-D_S)}{I_{in}(1-2D_S)k_{L1}f_S}$ $L_2 = \frac{V_{in}D_S(1-D_S)}{I_{in}(1-2D_S)k_{L2}f_S}$                                                  | $\frac{V_{in}}{1-2D_S}$     | $\frac{V_{in}(1-D_S)}{1-2D_S}$                 |

| c | $\begin{array}{c} V_{C1} = \\ \frac{(1-D_S)V_{in}}{1-(n+1)D_S} \\ V_{C2} = \\ \frac{nD_SV_{in}}{1-(n+1)D_S} \end{array}$     | $I_{Lm} = \frac{(n+1)I_{in}}{n}$     | $C_{1} = \frac{nD_{S}(1-(n+1)D_{S})I_{in}}{V_{in}(1-D_{S})k_{C1}f_{S}}$ $C_{2} = \frac{(1-D_{S}(n+1))I_{in}}{V_{in}nk_{C1}f_{S}}$         | $L_{m} = \frac{V_{in}D_{S}(1-D_{S})(n)^{2}}{I_{in}(1-(n+1)D_{S})(n+1)k_{m}f_{S}}$                                                                                  | $\frac{V_{in}}{1-(n+1)D_S}$ | $\frac{V_{in}(1-D_S)}{1-(1+n)D_S}$             |

| d | $V_{C1} = \frac{(1-D_S)V_{in}}{1-nD_S}$ $V_{C2} = \frac{(n-1)D_SV_{in}}{1-nD_S}$                                             | $I_{L1} = I_{in}$                    | $C_{1} = \frac{D_{S}(n-1)(1-nD_{S})I_{in}}{V_{in}(1-D_{S})k_{C1}f_{S}}$ $C_{2} = \frac{(1-D_{S}n)I_{in}}{V_{in}(n-1)k_{C2}f_{S}}$         | $L_{1} = \frac{V_{in}D_{S}(1-D_{S})n}{I_{in}(1-nD_{S})k_{L1}f_{S}}$                                                                                                | $\frac{V_{in}}{1-nD_S}$     | $\frac{V_{in}(1-D_{\rm S})}{1-nD_{\rm S}}$     |

| e | $\begin{array}{c} V_{C1} = \\ \frac{(1-D_S)V_{in}}{1-(n+2)D_S} \\ V_{C2} = \\ \frac{(n+1)D_SV_{in}}{1-(n+2)D_S} \end{array}$ | $I_{L1} = I_{in}$ $I_{Lm} = I_{in}$  | $C_{1} = \frac{D_{S}(n+1)(1-(n+2)D_{S})I_{in}}{V_{in}(1-D_{S})k_{C1}f_{S}}$ $C_{2} = \frac{(1-(n+2)D_{S})I_{in}}{V_{in}(n+1)k_{C2}f_{S}}$ | $\begin{array}{c} L_1 = \\ \frac{V_m(n+1)D_S(1-D_S)}{I_m(1-(n+2)D_S)k_{L1}f_S} \\ L_m = \\ V_{im}D_S(1-D_S) \\ \overline{I_{in}(1-(n+2)D_S)k_{Lm}f_S} \end{array}$ | $\frac{V_{in}}{1-(n+2)D_S}$ | $\frac{V_{in}(1-D_{\rm S})}{1-(n+2)D_{\rm S}}$ |

| f | $V_{C1} = \frac{(1-D_S)V_{in}}{1-(n+1)D_S}$ $V_{C2} = \frac{D_S n V_{in}}{1-(n+1)D_S}$                                       | $I_{L1} = I_{in}$ $I_{Lm} = -I_{in}$ | $C_{1} = \frac{D_{S}n(1-(n+1)D_{S})I_{in}}{V_{in}(1-D_{S})k_{C1}f_{S}}$ $C_{2} = \frac{(1-(n+1)D_{S})I_{im}}{V_{in}nk_{C2}f_{S}}$         | $\begin{array}{c} L_1 = \\ \frac{V_{in}D_S(1-D_S)}{I_{in}(1-(n+1)D_S)k_{L1}f_S} \\ L_m = \\ \frac{V_{in}D_Sn(1-D_S)}{I_{in}(1-(n+1)D_S)k_{L2}f_S} \end{array}$     | $\frac{V_m}{1-(n+1)D_S}$    | $\frac{V_{in}(1-D_S)}{1-(n+1)D_S}$             |

<sup>&</sup>lt;sup>1</sup> for Figure 1d,  $n = N_1/N_3$ ; for Figure 1e,  $n = N_2/N_1$ .

The table shows the voltage across the capacitors, average current across inductors, nominal values of capacitances and inductances that depend on the voltage high frequency ripple factor  $k_C$  and the current high frequency ripple factor  $k_L$ , the boost factor in dc-dc application, and the gain factor in the dc-ac application. Based on the derived equations, the main parameters, such as the inductance and maximum current for inductors and capacitance and peak voltage for capacitors presented in Equations (1)–(5), can be obtained.

#### 4. Results of Comparison

In a very general case, any boost converter can provide a very wide range of the boost factor and the input voltage regulation, respectively. The main limitations usually consist in the size of passive elements and losses in semiconductors.

The main outcome of the proposed comparative approach is in the possibility to define the maximum stored energy in the passive components as a function of the input voltage taking into account the constant ripples in the voltage across capacitors and current across inductors. For normal operation of the converter, the output RMS voltage level has to be constant despite the input voltage variation. As it was mentioned before, in the dc-dc application, the dc-link voltage is equal to the peak voltage across the IS network, while in the dc-ac application, the effective dc-link voltage is less than the peak voltage across the IS network.

As a result, at the constant dc-link voltage or constant effective (average) dc-link voltage across the IS networks, the ST duty cycle strictly depends on the input voltage. The closed loop control system sets up the ST duty cycle to maintain the necessary dc-link voltage. In other words, the ST duty cycle can be replaced in expressions presented above by the input voltage.

For example, in the case of qZSI, the ST duty cycle can be expressed as

$$D_{qZS} = \frac{V_0 - V_{in}}{2V_0 - V_{in}},\tag{6}$$

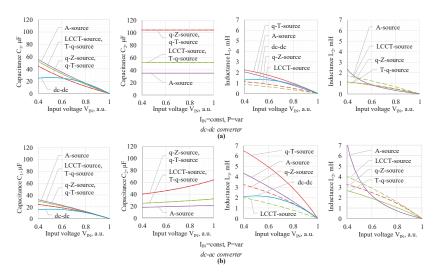

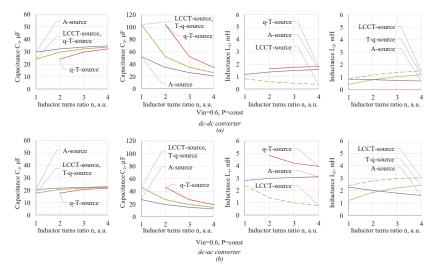

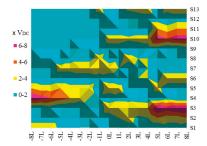

Taking into account Equation (6) and equations shown in Table 1, Figures 4 and 5 show the dependences of the passive elements values as a function of the input voltage and inductor turns ratio (n), respectively.

**Figure 4.** Value of the passive components as a function of the input voltage for (a) the dc-dc converter and (b) the dc-ac application.

**Figure 5.** Value of the passive components as a function of the different value of turns ratio (n) for (a) the dc-dc converter and (b) the inverter, with  $V_{in} = 0.6$ .

Figure 4 shows the required values of the passive components to provide a constant current ripple in magnetic components ( $L_1$  and  $L_2$ ) and voltage ripple across the capacitors ( $C_1$  and  $C_2$ ) as a function of the input voltage. Figure 4a illustrates the dc-dc application while Figure 4b corresponds to the dc-ac application. It can be seen that in all cases, the increasing input voltage leads to the capacitance  $C_1$  and inductances  $L_1$ ,  $L_2$  decreasing. This result is expected because of no need for the boosting voltage. If the input voltage corresponds to the nominal dc-link voltage, only simple VSI is enough to provide energy injection to the grid or ac load.

The most interesting conclusion is that the classical solution in the worst case ( $V_{in}$  = 0.4 a.u.) requires lower capacitance and inductance than all other IS solutions.

A separate study was conducted in order to verify the hypothesis that an increase in the turns ratio may improve the characteristics of the IS based converter. Figure 5 shows that certain improvements in the value of capacitance and inductance are not evident. In particular, it can be seen that the behavior of the topologies is different, but a common conclusion is that an increase in the turns ratio leads to an opportunity to decrease one capacitor and inductance but at the same time, increasing inductance and capacitance of another one is required.

The only evident advantages of increasing the turns ratio lie in lower peak dc-link voltage for the dc-ac application.

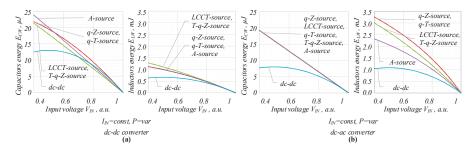

At the same time, the value of inductance or capacitance is not an objective criterion. The value of stored energy should be analyzed. It is assumed to be proportional to the size and cost. Figure 6 shows the maximum energy stored in the passive components during the switching period. It can be seen that in all cases, this energy is decreasing with the input voltage decreasing. If the input voltage equals the nominal dc-link voltage, the energy stored in the IS network is equal to zero. It means that no boost is required and the IS network is not required at all. A direct conclusion from this graph is that in order to provide a higher boost, the size and the volume of the passive components must be increased.

**Figure 6.** Energy stored in the passive components in (a) the dc-dc converter and (b) the inverter.

It can also be seen that the conventional solution based on the conventional boost circuit is better almost in all points. This conclusion is even more evident in the dc-ac application.

Another interesting conclusion is that high-gain IS based solutions such as the A-source network have a slightly smaller size of inductances but still higher than in the conventional solution. There is also an interesting feature of the total energy stored in capacitors in the dc-ac application: All IS based solutions have the same capacitance energy and they are independent of the turns ratio of coupled inductors. It means that different IS circuits have the same nature.

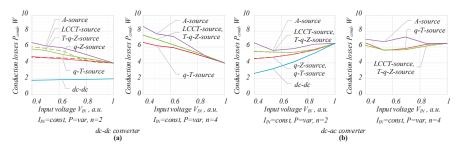

Figure 7 shows the dependence of conduction losses versus the input voltage. It is based on the assumption that conduction losses are proportional to the RMS current value in transistors and the average current in diodes. The same type of transistors and diodes were selected for all topologies  $(V_F = 0.8, R_{DS} = 0.27)$ . It can be seen that despite a constant value of the input current, the high power losses correspond to the high boost. It means that the ST current is increasing and leads to the conduction losses increasing in semiconductors. It can also be seen that the value of the turns ratio leads to the conduction losses increasing as well. It is explained by the current ripple increasing in the semiconductors.

**Figure 7.** Conduction losses by different (*n*) in (**a**) the dc-dc converter and (**b**) the inverter.

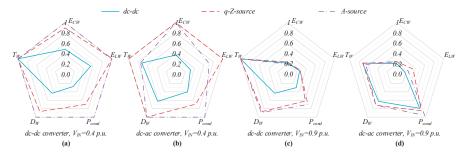

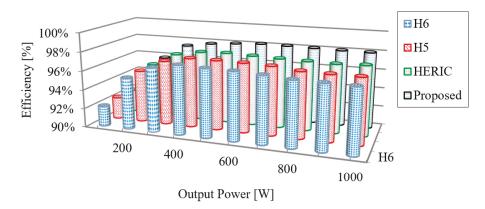

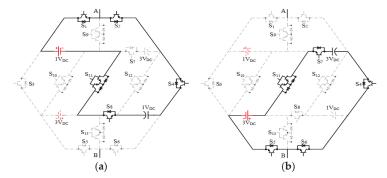

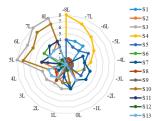

Finally, in order to summarize the results of the comparison, Figure 8 shows several spider diagrams. These diagrams include the capacitors energy, inductors energy, voltage stress across semiconductors (diodes and transistors), and conduction losses in relative units. Among all the discussed topologies, the conventional solution with the boost circuit, the qZS network, and the A-source network were selected for the comparison. Similar to the previous figures, both dc-dc and dc-ac applications were considered.

**Figure 8.** Comparative diagrams of the boost circuit, quasi-Z-source (qZS) networks, and A-source network: (a) dc-dc application with  $V_{in} = 0.4$  p.u., (b) dc-ac application with  $V_{in} = 0.4$  p.u., (c) dc-dc application with  $V_{in} = 0.9$  p.u., and (d) dc-ac application with  $V_{in} = 0.9$  p.u.

Figure 8a shows a diagram for the dc-ac application when the input voltage is relatively low (0.4 p.u.). In this case, the size of the passive components in all IS solutions was significantly larger.

Figure 8b shows a diagram for the same input voltage but for the dc-dc application. In this case, the size of the passive components was larger as well, but the difference was not so evident.

1 p.u. of the input voltage corresponds to the boundary input voltage between the buck and the boost mode. In the case of the dc-dc converter, 1 p.u. of the input voltage is equal to the reference output voltage. All the other parameters that are shown in Figure 8 were normalized to the maximum value.

Similar results are demonstrated in Figure 8c,d. In this case, only a minor boost is required and the difference in the capacitors and inductors energy is not significant.

As an intermediate conclusion, it can be claimed that IS networks require larger sizes of the passive components with the same current and voltage ripples. It also means that in the case of the equal components, the ripple will be higher. Among IS network topologies, the simple qZS topology can be recommended for the dc-dc and dc-ac application. The A-source has lower inductors energy where the inductance  $L_1$  and the magnetizing inductance  $L_M$  of the coupled inductor are taken into account, but also the ideal transformer should be considered. It does not contribute in terms of accumulated energy, but it contributes in terms of size and costs.

At the same time, it should be mentioned that the IS network is a more complex solution with a larger number of passive components. It gives some freedom for size components optimization. For example, the second inductor of the qZS network can be smaller at higher ripples, which does not define the input current ripple. There is also many techniques for efficiency optimization.

#### 5. Pros and Cons for Application in Galvanically Isolated Converters

The IS technology was applied to the galvanically isolated dc-dc converter right after the introduction of the qZS network in 2009 [2], which was the first network with a continuous input current [6]. Later on, this research area mostly focused on high step-up dc-dc converters due to the requirements of the wide input voltage range needed in emerging applications [30]. The basic competitor for these IS converters was CS counterparts, in particular, those with active clamping utilized, as shown in Figure 9.

Figure 9. Generalized topology of high step-up galvanically isolated dc-dc converters (a) that can be implemented as either (b) active-clamped current-source (CS) or (c) qZS and feature (d) a triangular transformer current.

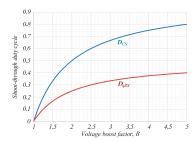

This section compares galvanically isolated qZS and CS full-bridge converters from Figure 9. Both converters feature a capacitive filter and triangular transformer current resulting from the presence of a transformer leakage inductance in real conditions. Both of them could be controlled by means of ST generation through the overlap of active states with the cumulative ST duty cycle of *D*. The qZS converter contains a higher number of passive components than that in the CS counterpart and a similar number of the semiconductor components. In such implementation, both converters will suffer from the same voltage stress of switches, but require a different ST duty cycle to achieve the required input voltage boost factor *B* that defines the transformer voltage amplitude. Obviously, the qZS converter requires lower duty cycle to step up the input voltage:

$$D_{qZS} = \frac{B-1}{2B} \tag{7}$$

At the same time, the CS counterpart requires twice higher duty cycle:

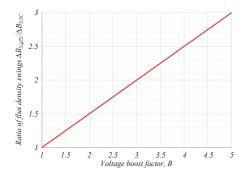

$$D_{CS} = \frac{B-1}{B} \tag{8}$$

Dependences (7) and (8) are visualized in Figure 10. The curve described by Equation (7) is asymptotic to the maximum value of  $D_{CS} = 0.5$ , while the one of Equation (8) is asymptotic to  $D_{CS} = 1$ . Hence, the qZS converter provides better transformer utilization, since the active state is never less than half of the switching period:  $(1 - D_{qZS}) \ge 0.5$ . Evidently, the CS converter should transfer energy through isolation within very narrow pulses at a high boost factor. As a result, the CS counterpart can suffer from a higher RMS current in the transformer as well as from a wider spectrum harmonic content of this current, resulting in higher skin and proximity losses.

Figure 10. Dependences of the ST duty cycles on the input voltage boost factor.

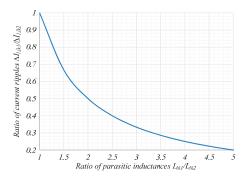

Applications where the given converters compete are usually of low power at the sub-kW level. This enables implementation of the qZS network with a coupled inductor instead of the two discrete inductors. Usually, the leakage inductances  $L_{lk1}$  and  $L_{lk2}$  are considered to be equal. This assumption results in an ideal case, when the magnetizing current ripple is equally shared by the windings:  $\Delta I_{LqZS}/2 = \Delta I_{Llk1} = \Delta I_{Llk2}$ . However, in practice, the current ripples could be calculated as follows [56]:

$$\Delta I_{Llk1} = \frac{V_{in} \cdot L_{lk2} \cdot D_{qZS} \cdot (1 - D_{qZS})}{f_{SW} \cdot (L_{lk1} \cdot L_{lk2} + L_{aZS} \cdot (L_{lk1} + L_{lk2})) \cdot (1 - 2 \cdot D_{aZS})},$$

(9)

$$\Delta I_{Llk2} = \frac{V_{in} \cdot L_{lk1} \cdot D_{qZS} \cdot (1 - D_{qZS})}{f_{SW} \cdot (L_{lk1} \cdot L_{lk2} + L_{qZS} \cdot (L_{lk1} + L_{lk2})) \cdot (1 - 2 \cdot D_{qZS})}.$$

(10)

From Equations (9) and (10), it follows that the input current ripple of the qZS converter can be reduced greatly when  $L_{lk1} \gg L_{lk2}$ . In this case, the magnetizing current ripple is distributed among the windings asymmetrically. The asymmetry is inversely proportional to the ratio of the leakage inductances, as shown in Figure 11. In practice, the tight coupling with very low leakage inductance is relatively easy to achieve in the coupled inductor. Therefore, a small wiring inductance at the input can result in a tremendous reduction of the input current ripple. Therefore, in low power galvanically isolated applications, the coupled inductor in the qZS network could be designed to be comparable in size than the inductor of the competing CS converter. This possibility to divert the current ripple from the input source is not available in the CS converter and, hence, it gives additional flexibility over the CS counterpart.

Figure 11. Dependence of the asymmetry of the current ripples in the qZS network coupled inductor.

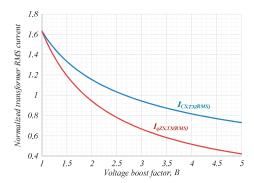

One of the main advantages of the qZS converter is a lower RMS current of the transformer winding. The normalized value of the transformer RMS current in the qZS converter can be calculated as follows:

$$I_{qZS,TX(RMS)} = \frac{I_{TX(RMS)}}{I_{in}} \Big|_{D=D_{qZS}} = \frac{2 \cdot \sqrt{2 \cdot (1 - D_{qZS})}}{\sqrt{3} \cdot B \cdot (1 - D_{qZS})} = \frac{4}{\sqrt{3 \cdot B \cdot (B+1)}}$$

(11)

A similar equation could be derived for the corresponding CS converter:

$$I_{CS,TX(RMS)} = \frac{I_{TX(RMS)}}{I_{in}} \Big|_{D=D_{CS}} = \frac{2 \cdot \sqrt{2 \cdot (1 - D_{CS})}}{\sqrt{3} \cdot B \cdot (1 - D_{CS})} = \frac{2 \cdot \sqrt{6}}{3 \cdot \sqrt{B}}$$

(12)

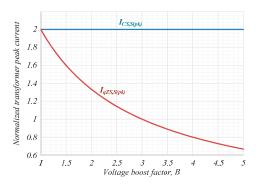

Dependences (11) and (12) are compared in Figure 12. Evidently, the RMS current stress of the transformer is up to 45% lower in the qZS converter than that in the CS converter at high boost factors.

**Figure 12.** Normalized RMS current of the transformer input winding as a function of the input voltage boost factor *B*.

Another advantage of the qZS converter is the lower peak current of the transformer. The normalized value of the transformer peak current in the qZS converter can be calculated as follows:

$$I_{qZS,TX(pk)} = \frac{I_{TX(pk)}}{I_{in}} \Big|_{D=D_{qZS}} = \frac{2}{B \cdot (1 - D_{qZS})} = \frac{4}{(B+1)}.$$

(13)

Similar to that, it can be shown that the peak transformer current of the CS converter is double of the average input current:

$$I_{CS,TX(pk)} = \frac{I_{TX(pk)}}{I_{in}} \Big|_{D=D_{CS}} = \frac{2}{B \cdot (1 - D_{CS})} = 2.$$

(14)

Dependences (13) and (14) are compared in Figure 13. It can be appreciated from the figure that the qZS converter features up to a 70% lower transformer peak current, while the normalized transformer peak current of the CS converter is constant. It should be mentioned that these results derived under the assumption of the same current ripple in the input stage inductors.

**Figure 13.** Normalized peak current of the transformer input winding as a function of the input voltage boost factor *B*.

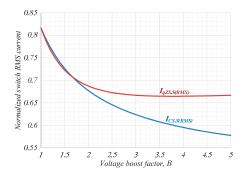

Operation of the qZS converter with lower ST duty cycles is associated with twice higher current stress during the ST states in the inverter bridge. As a result, the normalized RMS switch current of the qZS converter is calculated as:

$$I_{qZS,S(RMS)} = \frac{I_{S(RMS)}}{I_{in}} \Big|_{D=D_{qZS}} = \sqrt{D_{qZS} + \frac{2}{3 \cdot B^2 \cdot (1 - D_{qZS})}} = \sqrt{\frac{3 \cdot B^2 + 5}{6 \cdot B \cdot (B + 1)}},$$

(15)

is higher than that of the CS converter calculated as:

$$I_{CS,S(RMS)} = \frac{I_{S(RMS)}}{I_{in}} \Big|_{D=D_{CS}} = \sqrt{\frac{D_{CS}}{4} + \frac{2}{3 \cdot B^2 \cdot (1 - D_{CS})}} = \sqrt{\frac{3 \cdot B + 5}{12 \cdot B}},$$

(16)

which results in increased RMS losses in the qZS converter, as shown in Figure 14. Moreover, this stress is the same for both topologies at the low boost factors up to 1.7, while the gap increases to up to only 15% at very high boost factors. Hence, this small increase in the current stress of the switches is not a challenge in low power high step-up systems, where low voltage Si MOSFETs with very low on-state resistance are commonly utilized.

**Figure 14.** Normalized RMS current of the input side switches as a function of the input voltage boost factor *B*.

Another disadvantage of the qZS converters that becomes apparent as compared to the CS counterparts is the higher flux density swing in the transformer resulting from a longer active state of the qZS converter. The core flux swing  $\Delta B_S$  is proportional to the transformer voltage and the duty cycle:  $\Delta B_S \propto B \cdot V_{in} \cdot (1-D)$ . This results in up to a three times higher core flux density swing, as shown in Figure 15. This implies that the transformer should be designed differently for the qZS and CS converters.

From the considerations described above it follows that IS converters optimize the operation of the magnetic components, take advantage of wiring inductance to achieve ripple-free input current, and provide buck regulation mode, considerably enhancing the input voltage regulation range—all of these features are unavailable in the CS converters. However, design of the IS converters is more complicated due to the design constraints described above.

Figure 15. Ratio of the flux density swings at different input voltage boost factors.

#### 6. Simulation and Experimental Study

In order to verify the theoretical conclusions, a simulation and an experimental study were performed. The qZS and A-source networks were selected for practical realization as the most evident representatives of the discussed network topologies. The parameters of the selected topologies are presented in Table 2. A three-phase dc-ac system was selected for simulation and experimental verification.

**Table 2.** Parameters of the Network Used for Simulation and Experimental Verification.

| Parameters =                                  |        | qZS        |            | A-Source |            |            |  |

|-----------------------------------------------|--------|------------|------------|----------|------------|------------|--|

| Parameters -                                  | Theory | Simulation | Experiment | Theory   | Simulation | Experiment |  |

| Input voltage $V_{\it in}$                    | 183 V  | 183 V      | 183 V      | 183 V    | 183 V      | 183 V      |  |

| Input average current $I_{in}$                | 3.14 A | 3.4 A      | 3.14 A     | 2.64 A   | 2.6 A      | 2.6 A      |  |

| Input current ripple $\Delta I_{in}$          | 1.83 A | 1.87 A     | 1.5 A      | 1.08 A   | 1.07 A     | 1.1 A      |  |

| Transformer current ripple $\Delta I_{trans}$ | -      | -          | -          | -        | 6.66 A     | 6.5 A      |  |

| Output ac RMS voltage $V_{OUT}$               | 110 V  | 117.7 V    | 116.6 V    | 110 V    | 116 V      | 110.5 V    |  |

| dc-link peak voltage $V_0$                    | 467 V  | 479.3 V    | 480 V      | 396 V    | 395 V      | 396 V      |  |

| Voltage across capacitor $C_1$                | 325 V  | 330 V      | 341.6 V    | 325 V    | 323.8 V    | 306.8 V    |  |

| Voltage across capacitor $C_2$                | 142 V  | 147 V      | 155.8 V    | 142 V    | 140.8 V    | 127.7 V    |  |

| ST duty cycle $D_S$                           | 0.3    | 0.3        | 0.3        | 0.18     | 0.18       | 0.2        |  |

| Switching frequency f                         |        |            | 60 kl      | Hz       |            |            |  |

Table 2. Cont.

| Parameters                               |                    | qZS                         |                       | A-Source           |                             |                     |

|------------------------------------------|--------------------|-----------------------------|-----------------------|--------------------|-----------------------------|---------------------|

| Parameters                               | Theory             | Simulation                  | Experiment            | Theory             | Simulation                  | Experiment          |

| Passive components                       | Value              | Energy<br>(Rated<br>energy) | Size                  | Value              | Energy<br>(Rated<br>energy) | Size                |

| Capacitance value of the capacitor $C_1$ | 0.47 mF (400<br>V) | 25 J (37.6 J)               | $38.5  \mathrm{sm}^3$ | 0.47 mF<br>(400 V) | 24 J (37.6 J)               | $38.5 \text{ sm}^3$ |

| Capacitance value of the capacitor $C_2$ | 1.5 mF (200<br>V)  | 16.2 J (30 J)               | $43.3 \text{ sm}^3$   | 1.5 mF<br>(200 V)  | 14.7 J (30 J)               | $43.3 \text{ sm}^3$ |

| Inductance value of the inductor $L_1$   | 900 μH (9 A)       | 4.4 mJ<br>(36.5 mJ)         | $110 \text{ sm}^3$    | 1.8 mH (9 A)       | 6 mJ (73 mJ)                | $220 \text{ sm}^3$  |

| Inductance value of the inductors $L_2$  | 900 μH (9 A)       | 4.4 mJ<br>(36.5 mJ)         | $110 \text{ sm}^3$    | -                  | -                           |                     |

| Output side inductor filter $L_g$        | 0.2 mH             |                             |                       | 0.2 mH             | -                           |                     |

| Capacitor filter $C_f$                   | 0.47 μF            |                             |                       | 0.47 μF            | -                           |                     |

| Transformer $T_r$                        |                    |                             |                       |                    |                             | $230 \text{ sm}^3$  |

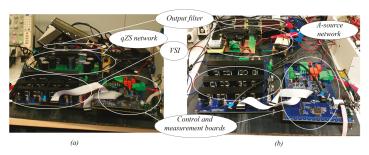

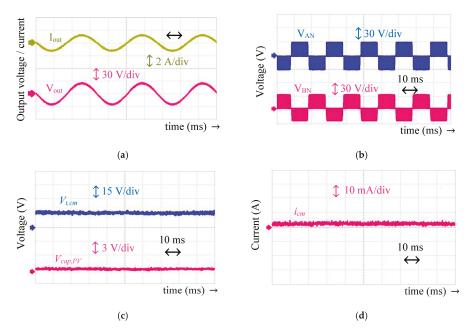

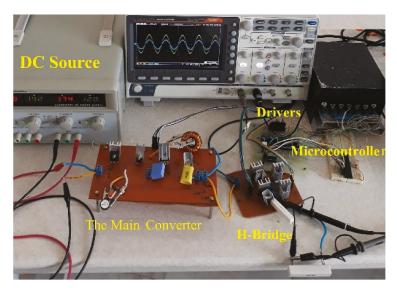

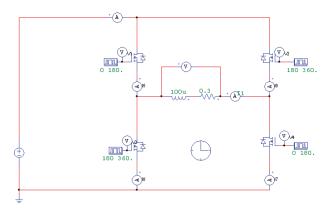

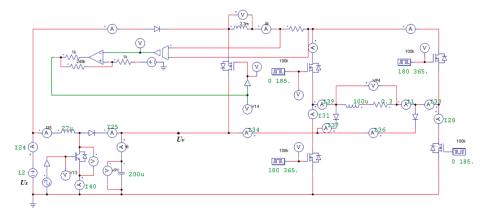

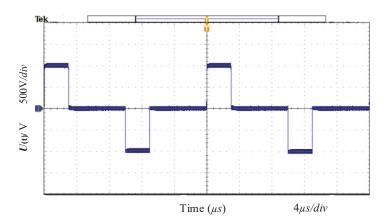

Figure 16 shows the experimental setup. It consisted of the three-phase VSI, qZS or A-source network, and inductive output filter. The control board was based on a field-programmable gate array (FPGA) which is able to provide any modulation technique. The measurement system was also involved for general monitoring. The experimental setup depicted in Figure 16a belonged to a qZS inverter, while the setup depicted in Figure 16b belonged to an A-source inverter. It can be seen, that it is the same setup and only IS networks were replaced.

**Figure 16.** Experimental setup: **(a)** The qZS three-phase inverter and **(b)** the A-source three-phase inverter.

Selected topologies were compared by the same parameters of the input voltage, load, capacitors, and input inductor value. The input voltage was equal to 183~V with a RMS ac output voltage of about 110~V.

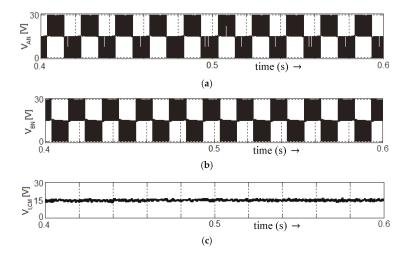

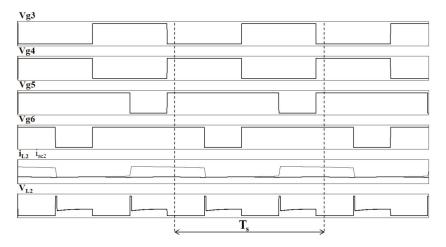

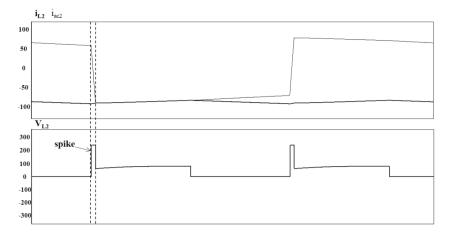

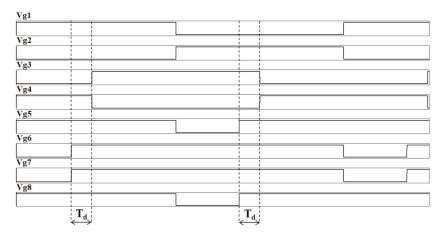

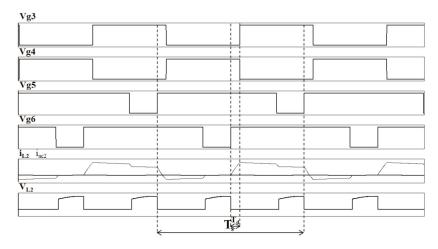

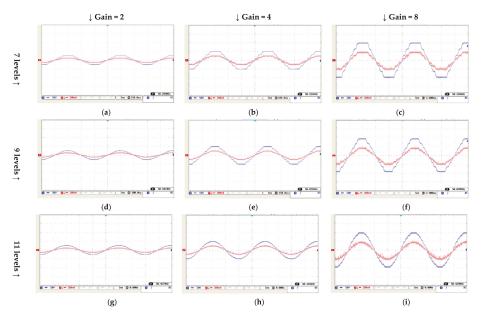

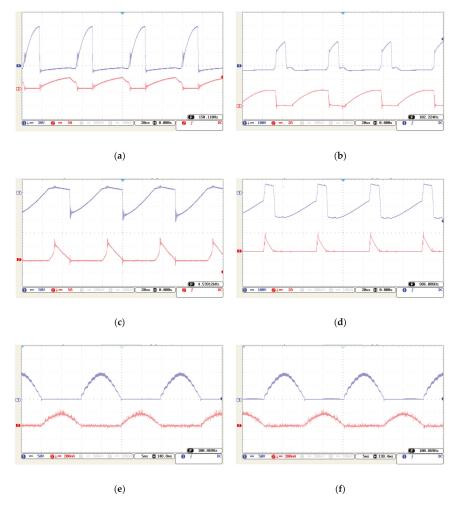

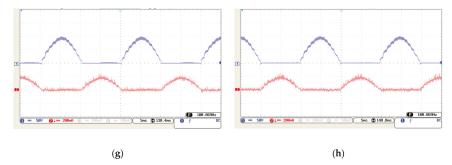

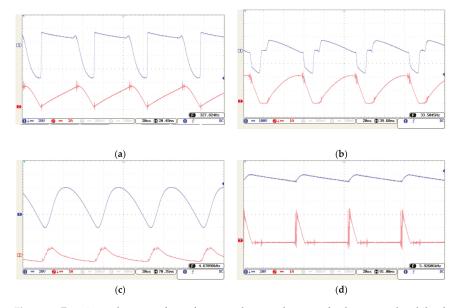

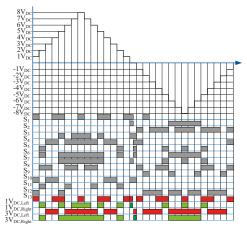

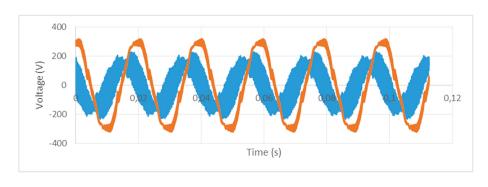

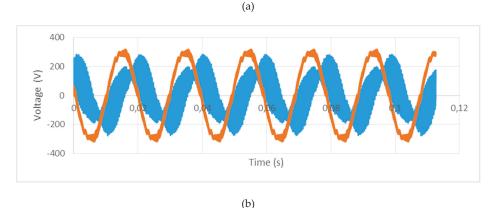

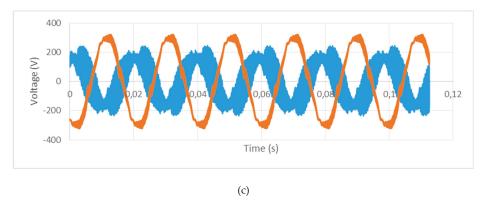

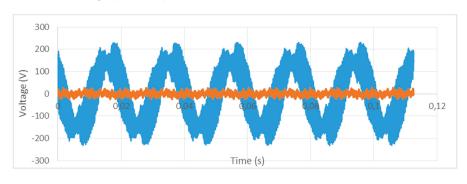

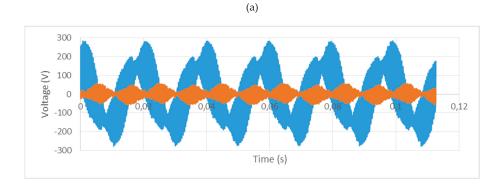

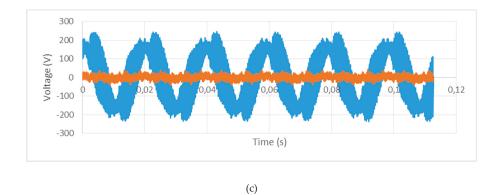

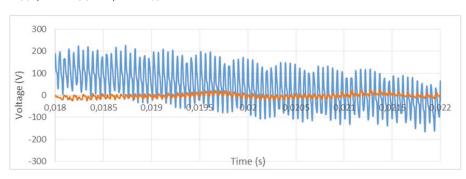

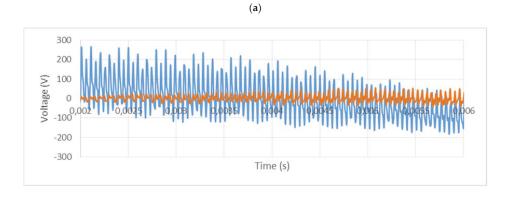

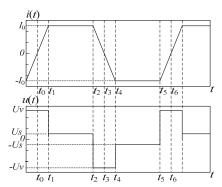

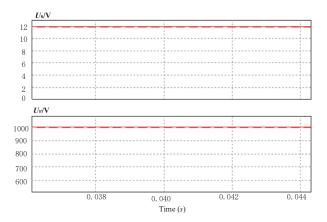

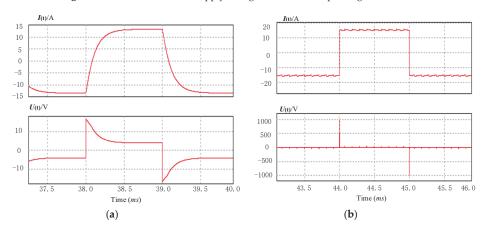

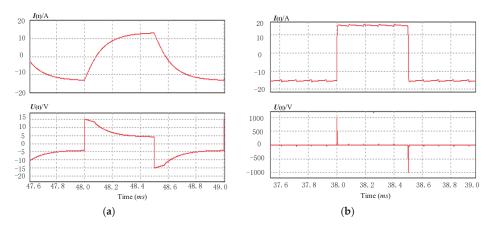

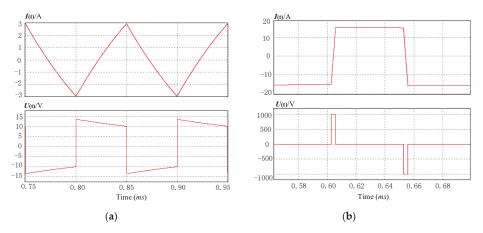

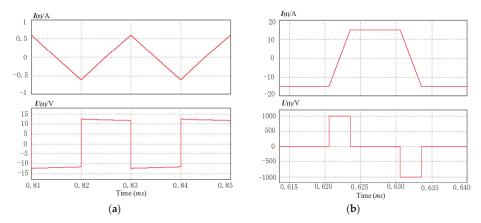

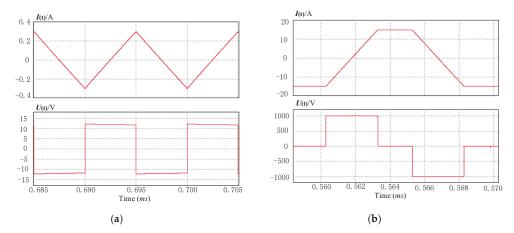

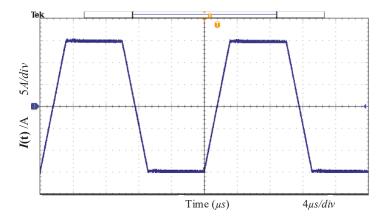

Figure 17 shows the simulation results for the qZS network, while Figure 18 shows similar results for the A-source network. It can be seen that approximately the same output voltage was achieved for different circuits. The ST duty cycle  $D_{qZS} = 0.2$  of the A-source was smaller than  $D_{qZS} = 0.27$  of the qZS.

**Figure 17.** Simulation results of the qZS inverter: (a) Input voltage  $(V_{in})$  along with the dc-link voltage  $(V_o)$ , (b) input current  $(I_{in})$  along with the inductor current  $(I_{L2})$ , and (c) voltage across capacitors  $V_{C1}$  and  $V_{C2}$ .

**Figure 18.** Simulation results of the A-source inverter: (a) Input voltage  $(V_{in})$  along with the dc-link voltage  $(V_0)$ , (b) input current  $(I_{in})$  along with the inductor current  $(I_{L2})$ , and (c) voltage across capacitors  $V_{C1}$  and  $V_{C2}$ .

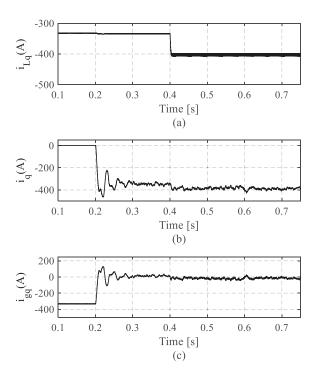

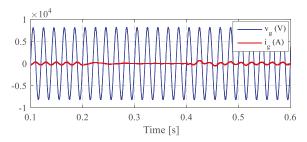

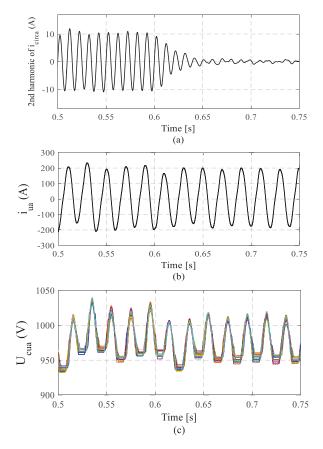

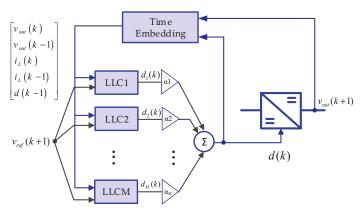

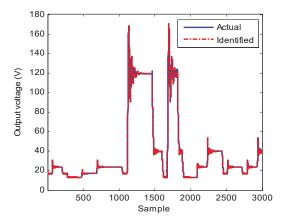

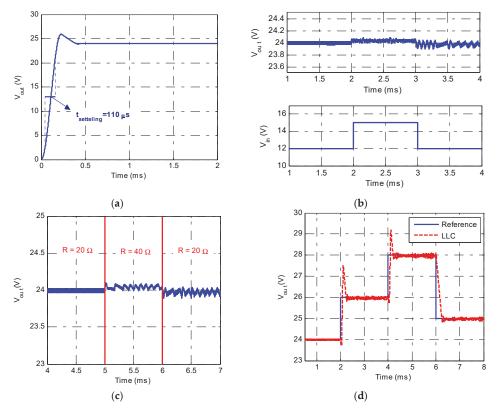

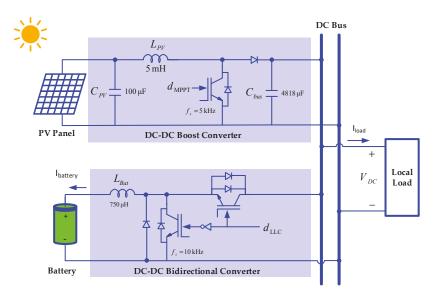

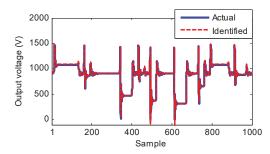

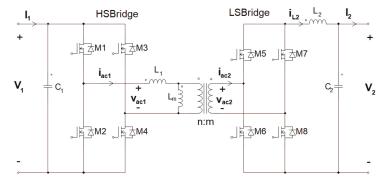

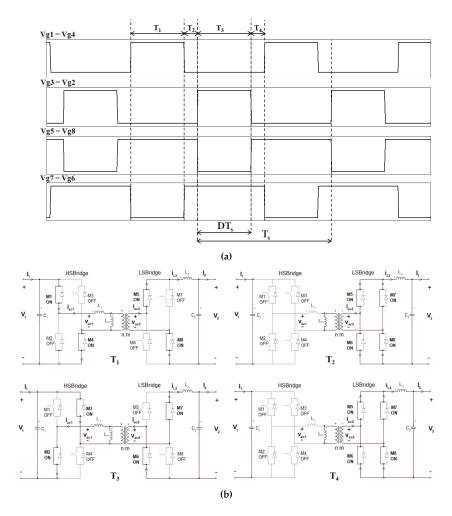

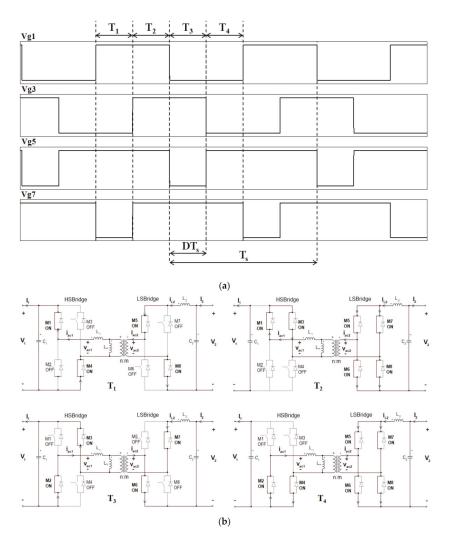

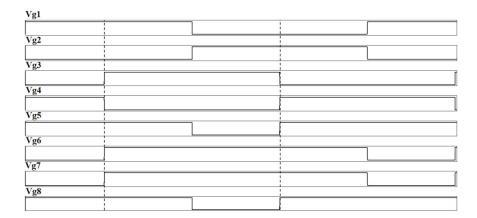

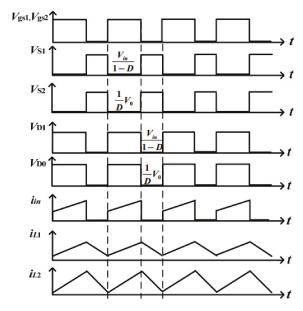

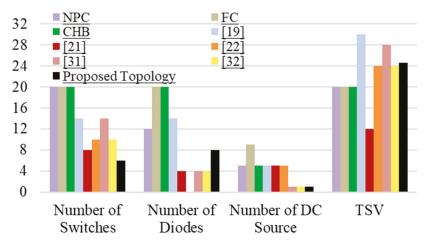

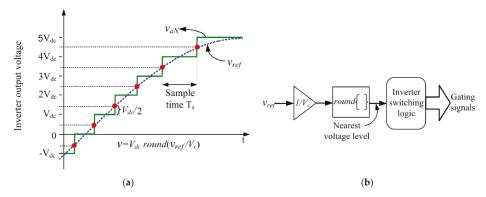

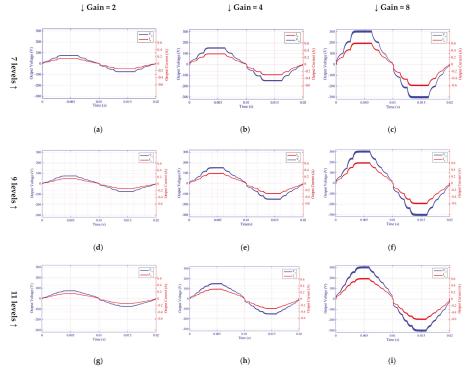

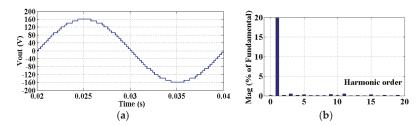

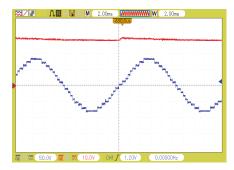

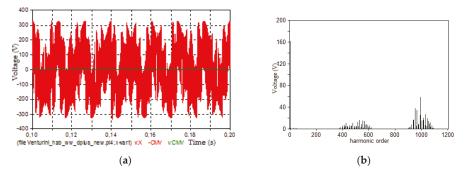

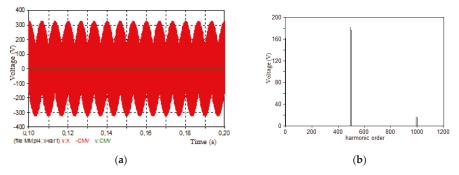

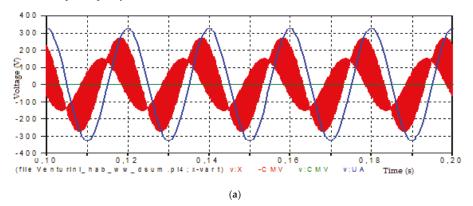

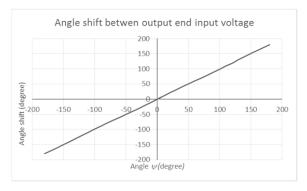

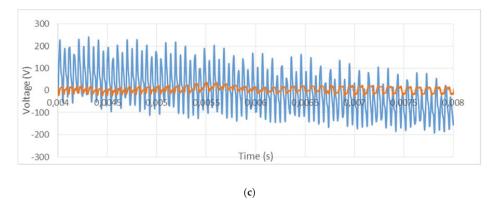

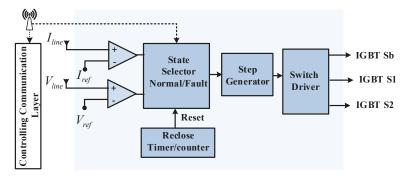

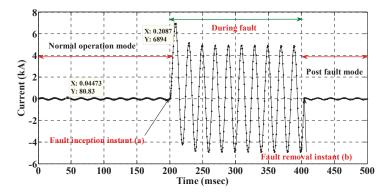

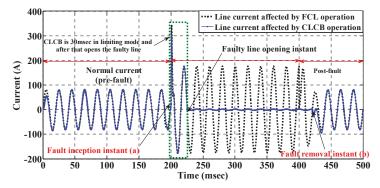

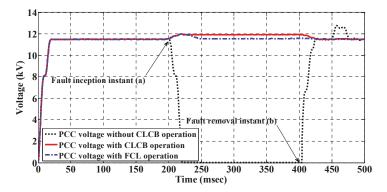

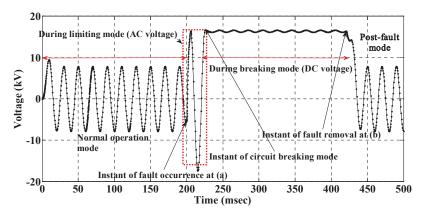

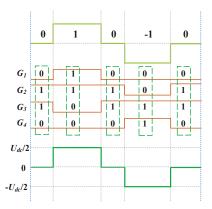

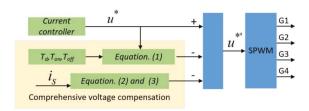

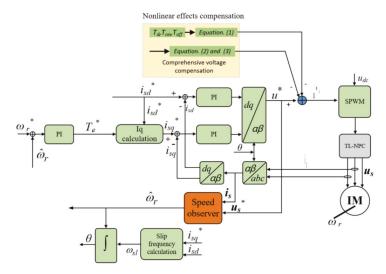

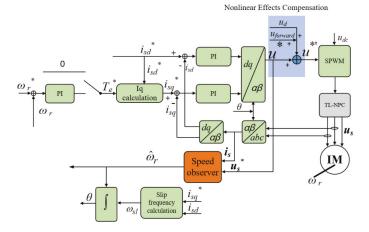

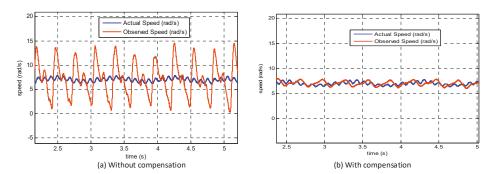

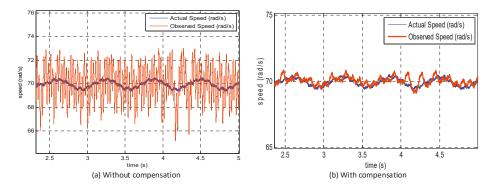

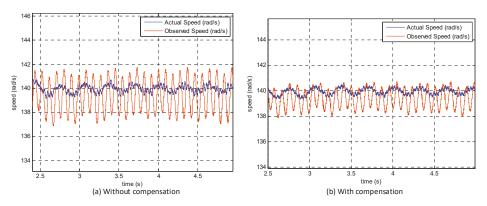

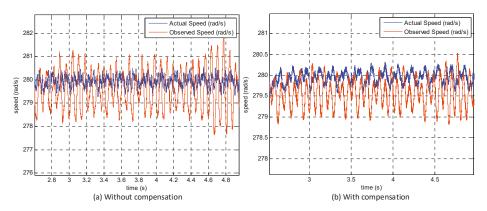

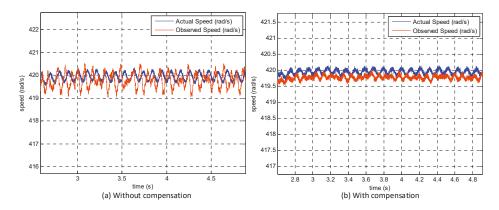

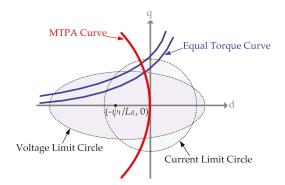

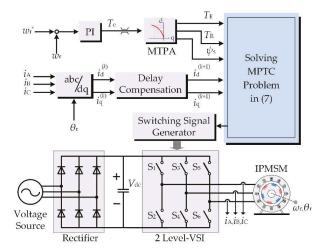

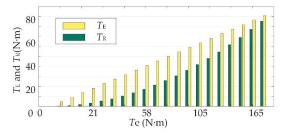

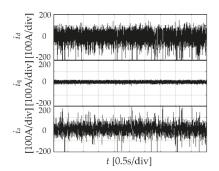

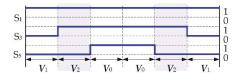

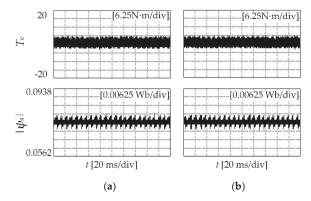

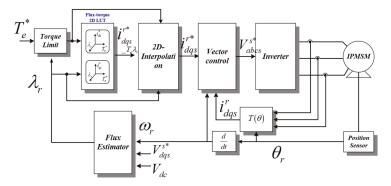

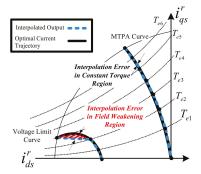

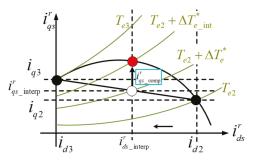

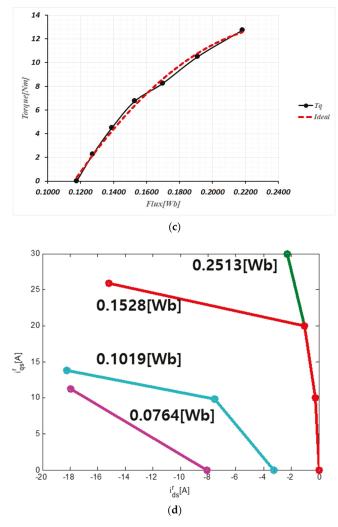

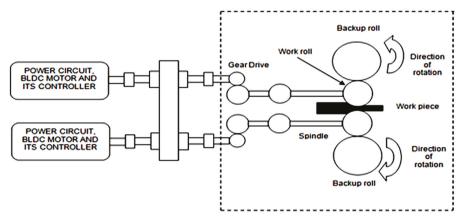

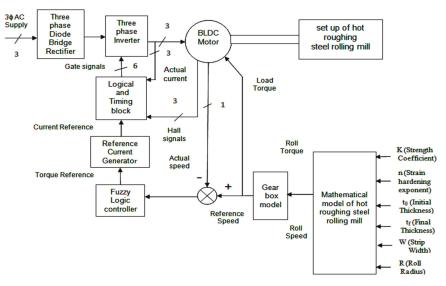

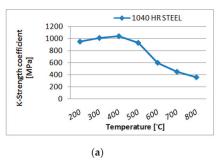

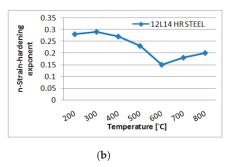

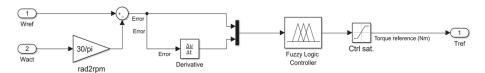

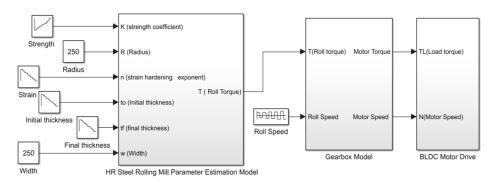

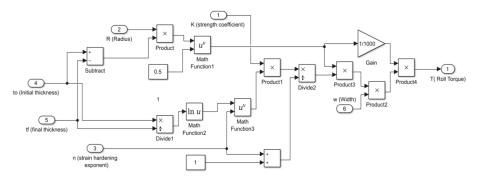

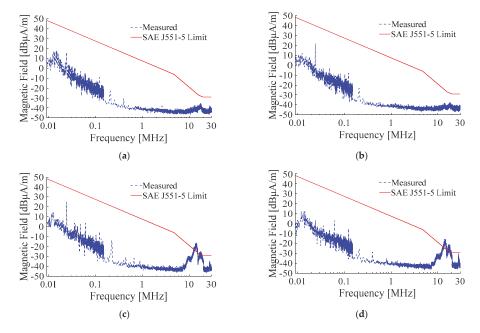

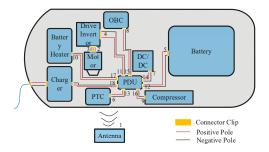

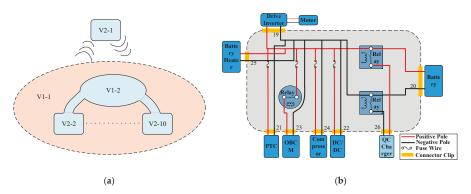

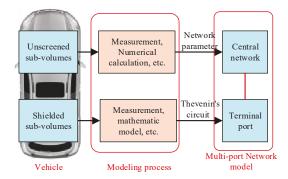

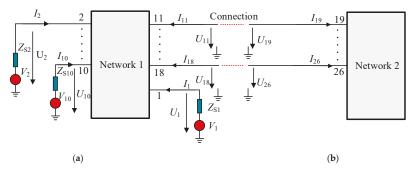

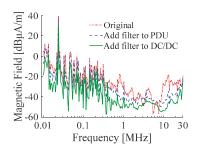

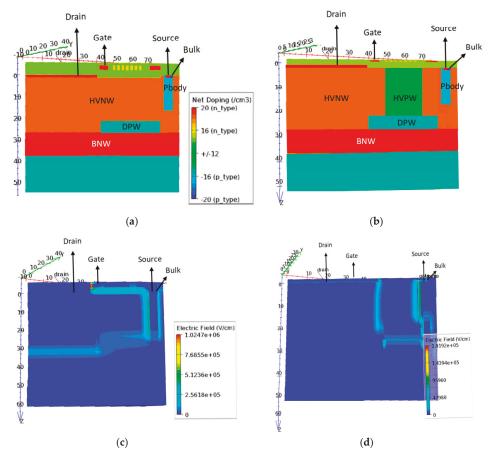

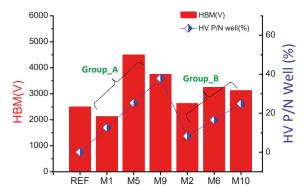

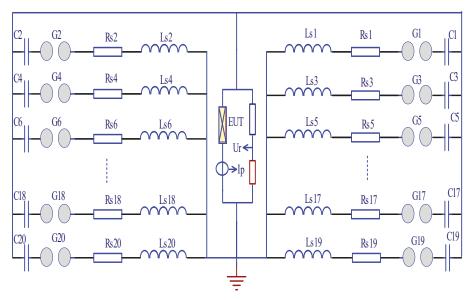

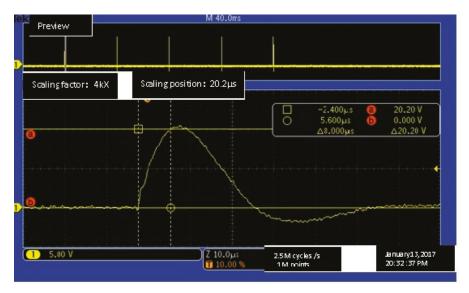

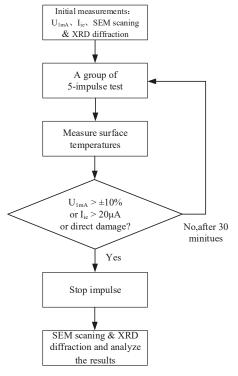

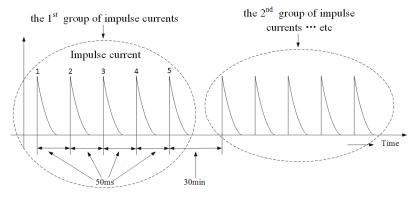

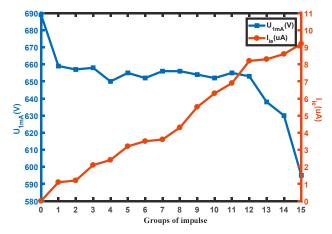

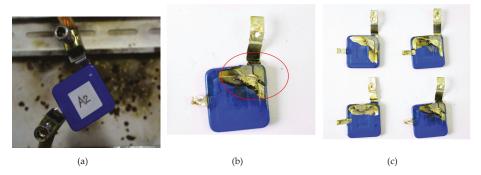

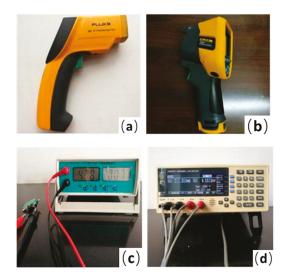

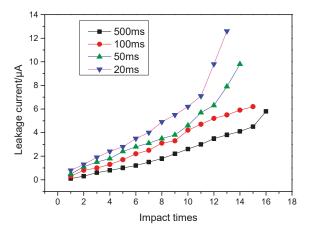

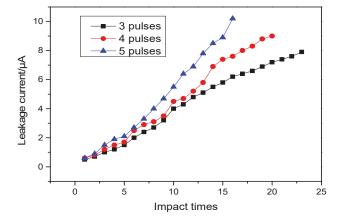

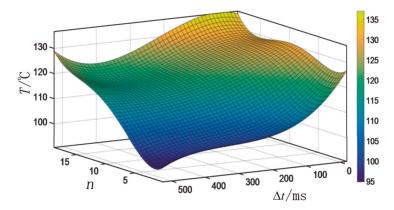

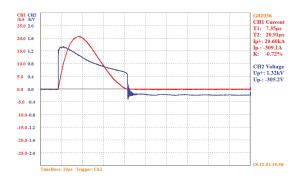

The input current quality of the A-source was slightly better. The input average current value of the A-source was lower than qZS: The average value of the input current was  $I_{in} = 2.6$  A and  $I_{in} = 3.14$  A, respectively.