# Emerging Converter Topologies and Control for Grid Connected Photovoltaic Systems

Edited by

Dmitri Vinnikov, Samir Kouro and Yongheng Yang

Printed Edition of the Special Issue Published in *Energies*

## **Emerging Converter Topologies and Control for Grid Connected Photovoltaic Systems**

## **Emerging Converter Topologies and Control for Grid Connected Photovoltaic Systems**

**Editors**

Dmitri Vinnikov Samir Kouro Yongheng Yang

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

**Editors**

Dmitri Vinnikov

antii viitiikov

Department of Electrical Power Engineering and Mechatronics,

Estonia

Samir Kouro

**Electronics Engineering**

Department, Universidad

Tallinn University of Technology Técnica Federico Santa María

Chile

Yongheng Yang

Department of Energy

Technology, Aalborg University

Denmark

Editorial Office MDPI

MDII

St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Energies* (ISSN 1996-1073) (available at: https://www.mdpi.com/journal/energies/special\_issues/Emerging\_Converter\_Photovoltaic\_Systems).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-03943-909-6 (Hbk) ISBN 978-3-03943-910-2 (PDF)

© 2020 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

#### Contents

| About the Editors                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "Emerging Converter Topologies and Control for Grid Connected Photovoltaic Systems"                                                                                                           |

| Yoon-Geol Choi, Hyeon-Seok Lee, Bongkoo Kang, Su-Chang Lee and Sang-Jin Yoon Compact Single-Stage Micro-Inverter with Advanced Control Schemes for                                                       |

| Photovoltaic Systems                                                                                                                                                                                     |

| Reprinted from: Energies 2019, 12, 1234, doi:10.3390/en12071234                                                                                                                                          |

| Cristian Verdugo, Samir Kouro, Christian A. Rojas, Marcelo A. Perez, Thierry Meynard and<br>Mariusz Malinowski                                                                                           |

| Five-Level T-type Cascade Converter for Rooftop Grid-Connected Photovoltaic Systems Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 1743, doi:10.3390/en12091743                               |

| Chun-Wei Lin, Chang-Yi Peng and Huang-Jen Chiu                                                                                                                                                           |

| A Novel Three-Phase Six-Switch PFC Rectifier with Zero-Voltage-Switching and Zero-Current-Switching Features  Reprinted from: Energies 2019, 12, 1119, doi:10.3390/en12061119                            |

|                                                                                                                                                                                                          |

| Nicolás Müller, Samir Kouro, Pericle Zanchetta, Patrick Wheeler, Gustavo Bittner and Francesco Girardi                                                                                                   |

| Energy Storage Sizing Strategy for Grid-Tied PV Plants under Power Clipping Limitations Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 1812, doi:10.3390/en12091812                           |

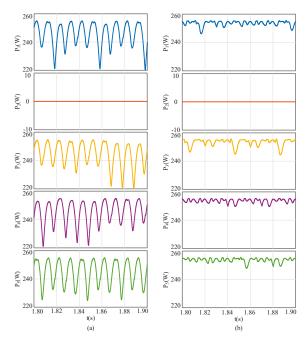

| Wang Mao, Xing Zhang, Yuhua Hu, Tao Zhao, Fusheng Wang, Fei Li and Renxian Cao  A Research on Cascaded H-Bridge Module Level Photovoltaic Inverter Based on a Switching  Modulation Strategy             |

| Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 1851, doi:10.3390/en12101851                                                                                                                   |

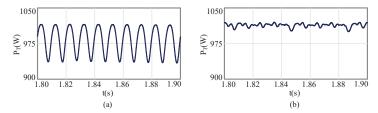

| Guangqing Bao, Hongtao Tan, Kun Ding, Ming Ma and Ningbo Wang  A Novel Photovoltaic Virtual Synchronous Generator Control Technology Without Energy                                                      |

| Storage Systems Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 2240, doi:10.3390/en12122240                                                                                                   |

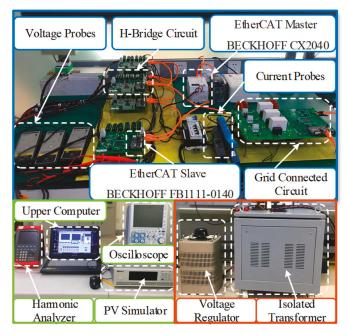

| Baoji Wang, Xing Zhang, Chao Song and Renxian Cao<br>Research on the Filters for Dual-Inverter Fed Open-End Winding Transformer Topology in<br>Photovoltaic Grid-Tied Applications                       |

| Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 2338, doi:10.3390/en12122338                                                                                                                   |

| Serhii Stepenko, Oleksandr Husev, Dmitri Vinnikov, Carlos Roncero-Clemente, Sergio Pires<br>Pimentel and Elena Santasheva                                                                                |

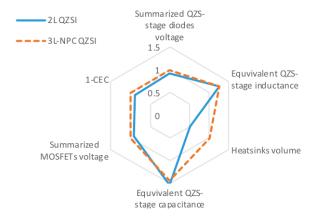

| Experimental Comparison of Two-Level Full-SiC and Three-Level Si–SiC Quasi-Z-Source                                                                                                                      |

| Inverters for PV Applications Reprinted from: Energies 2019, 12, 2509, doi:10.3390/en12132509                                                                                                            |

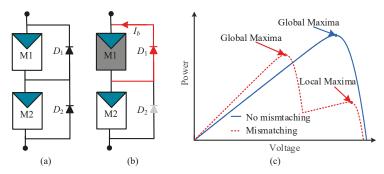

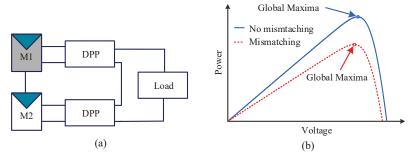

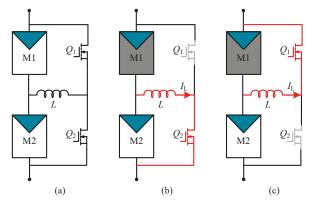

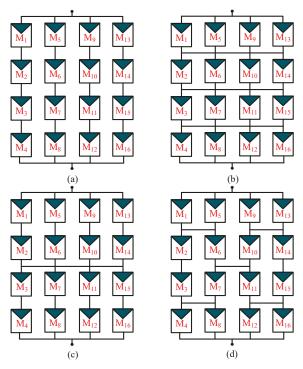

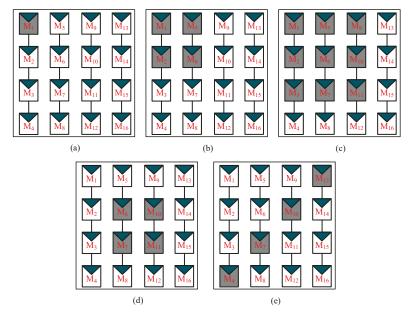

| Kamran Ali Khan Niazi, Yongheng Yang, Mashood Nasir and Dezso Sera Evaluation of Interconnection Configuration Schemes for PV Modules with Switched-Inductor Converters under Partial Shading Conditions |

| Reprinted from: <i>Energies</i> <b>2019</b> , 12, 2802, doi:10.3390/en12142802                                                                                                                           |

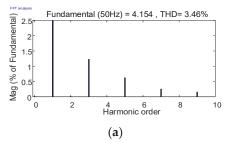

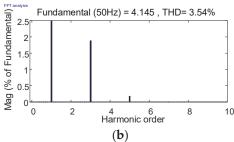

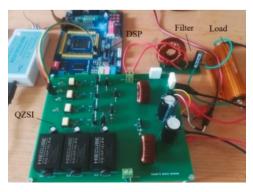

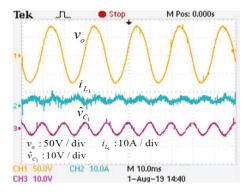

| Ripple Vector Cancellation Modulation Strategy for Single-Phase Quasi-Z-Source Inverter Reprinted from: <i>Energies</i> <b>2019</b> , <i>12</i> , 3344, doi:10.3390/en12173344                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

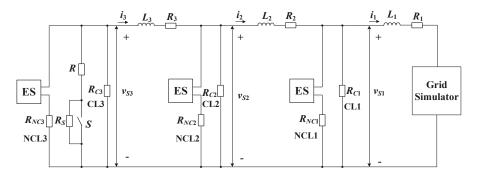

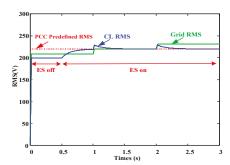

| Daojun Zha, Qingsong Wang, Ming Cheng, Fujin Deng and Giuseppe Buja Regulation Performance of Multiple DC Electric Springs Controlled by Distributed Cooperative System                                                                                               |

| Reprinted from: Energies 2019, 12, 3422, doi:10.3390/en12183422                                                                                                                                                                                                       |

| Qingsong Wang, Wujian Zuo, Ming Cheng, Fujin Deng and Giuseppe Buja Hierarchical Control with Fast Primary Control for Multiple Single-Phase Electric Springs Reprinted from: Energies 2019, 12, 3511, doi:10.3390/en12183511                                         |

| Andrii Chub, Dmitri Vinnikov, Serhii Stepenko, Elizaveta Liivik and Frede Blaabjerg Photovoltaic Energy Yield Improvement in Two-Stage Solar Microinverters Reprinted from: Energies 2019, 12, 3774, doi:10.3390/en12193774                                           |

| Ana Cabrera-Tobar, Eduard Bullich-Massagué, Mònica Aragüés-Peñalba and Oriol Gomis-Bellmunt  Active and Reactive Power Control of a PV Generator for Grid Code Compliance  Reprinted from: Energies 2019, 12, 3872, doi:10.3390/en12203872                            |

| Xiumei Yue, Hongliang Wang, Xiaonan Zhu, Xinwei Wei and Yan-Fei Liu  A Topology Synthetization Method for Single-Phase, Full-Bridge, Transformerless Inverter with Leakage Current Suppression Part I Reprinted from: Energies 2020, 13, 434, doi:10.3390/en13020434  |

| Xiumei Yue, Hongliang Wang, Xiaonan Zhu, Xinwei Wei and Yan-Fei Liu  A Topology Synthetization Method for Single-Phase, Full-Bridge, Transformerless Inverter with Leakage Current Suppression—Part II Reprinted from: Energies 2020, 13, 446, doi:10.3390/en13020446 |

| Ben Zhao, Alexander Abramovitz, Chang Liu, Yongheng Yang and Yigeng Huangfu  A Family of Single-Stage, Buck-Boost Inverters for Photovoltaic Applications  Reprinted from: Energies 2020, 13, 1675, doi:10.3390/en13071675                                            |

| Anirudh Budnar Acharya, Dezso Sera, Remus Teodorescu and Lars Einar Norum  Modular Multilevel Converter for Photovoltaic Application with High Energy Yield under Uneven Irradiance Reprinted from: Energies 2020, 13, 2619, doi:10.3390/en13102619                   |

| Jinkui He, Yongheng Yang and Dmitri Vinnikov  Energy Storage for 1500 V Photovoltaic Systems: A Comparative Reliability Analysis of DC- and AC-Coupling  Reprinted from: Energies 2020, 13, 3355, doi:10.3390/en13133355                                              |

| Abualkasim Bakeer, Andrii Chub and Dmitri Vinnikov Step-Up Series Resonant DC–DC Converter with Bidirectional-Switch-Based Boost Rectifier for Wide Input Voltage Range Photovoltaic Applications Reprinted from: Energies 2020, 13, 3747, doi:10.3390/en13143747     |

|                                                                                                                                                                                                                                                                       |

#### **About the Editors**

Dmitri Vinnikov received his Dipl.Eng., M.Sc., and Dr.Sc.techn. degrees in electrical engineering from Tallinn University of Technology, Tallinn, Estonia, in 1999, 2001, and 2005, respectively. He is currently the Head of the Power Electronics Group, Department of Electrical Power Engineering and Mechatronics, Tallinn University of Technology (Estonia) and a Visiting Professor at the Institute of Industrial Electronics and Electrical Engineering, Riga Technical University (Latvia). He is the CTO and co-founder of Ubik Solutions LLC - an Estonian start-up company dedicated to innovative and smart power electronics for renewable energy systems. He has authored more than 200 published papers on power converter design and development and is the holder of numerous patents and utility models in this field. His research interests include the applied design of power electronic converters and control systems, renewable energy conversion systems, impedance-source power converters, and implementation of wide bandgap power semiconductors. Dr. Vinnikov has directed over 25 National and International R&D projects, he is one of the founders and leading researchers of ZEBE - Estonian Centre of Excellence for zero energy and resource-efficient smart buildings and districts. He has authored or co-authored two books, five monographs, and one book chapter. D. Vinnikov is a Chair of the IES/PELS Joint Societies Chapter of the IEEE Estonia Section. He leads the Inverters/Rectifiers subcommittee of the Power Electronics Technical Committee (PETC) of the IEEE-IES and is a member of the Student and Young Professionals Activity Committee of the IEEE-IES. Dr. Vinnikov received the Best Young Scientist and Scientist of the Year awards of Tallinn University of Technology in 2010 and 2017, correspondingly. In 2014, he received the Estonian National Research Award in Technical Sciences for his contribution to innovative power electronic systems for renewable energy applications. In 2016, he was awarded a Doctor Honoris Causa from Chernihiv National University of Technology (Ukraine).

Samir Kouro received the M.Sc. and Ph.D. degrees in electronics engineering from the Universidad Tecnica Federico Santa Maria (UTFSM), Valparaíso, Chile, in 2004 and 2008, respectively. He currently is an academic at the Department of Electronic Engineering and serves as Director of Innovation and Technology Transfer of UTFSM. From 2009 to 2011, he was a Postdoctoral Fellow at the Department of Electrical and Computer Engineering, Ryerson University, Toronto, Canada. interests include power electronics, renewable energy conversion systems (photovoltaic and wind), and automotive applications. Dr. Kouro is a Principal Investigator of the Solar Energy Research Center (SERC-Chile), and Deputy Director of the Advanced Center of Electrical and Electronics Engineering (AC3E), both of which are R&D centers of excellence in Chile. He has directed 39 R&D projects, co-authored one book, 10 book chapters, 4 patents, and over 200 refereed journal and conference papers. He currently serves as the President of the IEEE PELS Chapter Chile and is a Board Member of the Solar Energy and Energy Innovation Committee of the Chilean Government. Dr. Kouro was included in the Clarivate Analytics 2018 Highly Cited Researcher List, and received the 2018 IEEE-AIE Outstanding Engineer Award, the 2016 IEEE Industrial Electronics Bimal K. Bose Award for Industrial Electronics Applications in Energy Systems, the 2015 IEEE Industrial Electronics Society J. David Irwin Early Career Award, and the 2012 IEEE Power Electronics Society Richard M. Bass Outstanding Young Power Electronics Engineer Award. He has also received 4 best paper awards in IEEE journals in the years 2019, 2016, 2012, and 2008.

Yongheng Yang received his B.Eng. degree from Northwestern Polytechnical University, China, in 2009, and his Ph.D. degree from Aalborg University, Denmark, in 2014. He was a postgraduate student at Southeast University, China, from 2009 to 2011. In 2013, he spent three months as a Visiting Scholar at Texas A&M University, USA. Currently, he is an Associate Professor with the Department of Energy Technology, Aalborg University, where he is also the Vice Program Leader for the research program on photovoltaic systems. Dr. Yang is the Chair of the IEEE Denmark Section. He is now an Associate Editor for several prestigious IEEE Transactions/Journals. He is a Deputy Editor of the IET Renewable Power Generation for Solar Photovoltaic Systems. He was the recipient of the 2018 IET Renewable Power Generation Premium Award and was an Outstanding Reviewer for the IEEE TRANSACTIONS ON POWER ELECTRONICS in 2018. His current research includes grid-integration of photovoltaic systems and multi-energy vectors with an emphasis on the power converter design, control, and reliability.

# Preface to "Emerging Converter Topologies and Control for Grid Connected Photovoltaic Systems"

Continuous cost reduction of photovoltaic (PV) systems and the rise of power auctions resulted in the establishment of PV power not only as a green energy source but also as a cost-effective solution to the electricity generation market. Various commercial solutions for grid-connected PV systems are available at any power level, ranging from multi-megawatt utility-scale solar farms to sub-kilowatt residential PV installations. Compared to utility-scale systems, the feasibility of small-scale residential PV installations is still limited by the existing technologies that have not yet properly addressed issues like operation in weak grids, opaque and partial shading, etc. New market drivers such as warranty improvement to match the PV module lifespan, operation voltage range extension for application flexibility, and embedded energy storage for load shifting have again put small-scale PV systems in the spotlight. This Special Issue collects the latest developments in the field of power electronic converter topologies, control, design, and optimization for better energy yield, power conversion efficiency, reliability, and longer lifetime of the small-scale PV systems. This Special Issue will serve as a reference and update for academics, researchers, and practicing engineers to inspire new research and developments that pave the way for next-generation PV systems for residential and small commercial applications. Enjoy reading.

Dmitri Vinnikov, Samir Kouro, Yongheng Yang

Editors

Article

# Compact Single-Stage Micro-Inverter with Advanced Control Schemes for Photovoltaic Systems

Yoon-Geol Choi 1, Hyeon-Seok Lee 1, Bongkoo Kang 1, Su-Chang Lee 2 and Sang-Jin Yoon 3,\*

- Department of Electrical Engineering, Pohang University of Science and Technology, Pohang 37673, Korea; ygchoi@postech.ac.kr (Y.-G.C.); hsasdf@postech.ac.kr (H.-S.L.); bkkang@postech.ac.kr (B.K.)

- <sup>2</sup> LG Electronics Co., Ltd., Energy Business Center, Gumi 39368, Korea; suchang.lee@lge.com

- Department of Electrical Engineering, Korea Polytechnics, Gumi 39257, Korea

- \* Correspondence: sjyoon@kopo.ac.kr; Tel.: +82-54-468-5248

Received: 18 March 2019; Accepted: 27 March 2019; Published: 31 March 2019

**Abstract:** This paper proposes a grid-connected single-stage micro-inverter with low cost, small size, and high efficiency to drive a 320 W class photovoltaic panel. This micro-inverter has a new and advanced topology that consists of an interleaved boost converter, a full-bridge converter, and a voltage doubler. Variable switching frequency and advanced burst control schemes were devised and implemented. A 320 W prototype micro-inverter was very compact and slim with 60-mm width, 310-mm length, and 30-mm height. In evaluations, the proposed micro-inverter achieved CEC weighted efficiency of 95.55%, MPPT efficiency >95% over the entire load range, and THD 2.65% at the rated power. The proposed micro-inverter is well suited for photovoltaic micro-inverter applications that require low cost, small size, high efficiency, and low noise.

**Keywords:** single stage micro-inverter; burst control; variable frequency control; maximum power-point tracking

#### 1. Introduction

The photovoltaic (PV) generation is emerging as a future energy system because of its installation convenience, no-noise, infinite, and eco-friendly characteristics [1–4]. It is classified into the centralized power system and the distributed power system depending on the scale of solar power generation [5]. The centralized power system has a simple circuit structure with PV strings as the input energy source, but it has a disadvantage that the power generation is considerably lowered when some panels of the PV string are shaded. On the other hand, in the distributed power system, the optimal power extraction is possible because the maximum power point tracking (MPPT) control can be applied to each PV panel with a micro-inverter connected. So, it can minimize the loss of power generation caused by the shading effect. However, one micro-inverter is required for each PV panel, so implementation of this strategy is expensive. Therefore, many attempts have recently been made to lower the cost of micro-inverters.

In general, considering the cost, micro-inverters have been designed to use circuit architectures with a flyback converter [6-10], which provides galvanic isolation with fewer switches than other designs. Although the flyback converter has the advantage of circuit simplicity and low cost, the design must use a transformer with a high turns ratio to achieve a high voltage-conversion ratio from low dc voltage on a single PV panel. In the transformer, the high turns ratio causes a large leakage inductance which increases the stress on semiconductor switches. Moreover, due to low utilization of the transformer, this topology is most suitable for low-power applications <200 W. Recently, multi-phase interleaved technology has been applied to solar power generation from PV panels that output  $\geq$ 320 W, but this technology requires large and expensive components.

This paper proposes a low-cost, slim, single-stage micro-inverter to drive a 320-W-class PV panel. The proposed micro-inverter has an interleaved structure based on the boost half-bridge (BHB) converter [11] with a cascaded voltage doubler. The interleaved BHB has an inversely-coupled inductor for the voltage step-up operation. The coupled inductor can reduce input ripple current and can be reduced in size. The voltage doubler increases the ac output voltage from the interleaved converter. Therefore, the transformer can have a lower turns ratio in the interleaved BHB than in a flyback converter and can be reduced in size. In the proposed micro-inverter, semiconductor switches achieve turn-on zero-voltage-switching (ZVS) and turn-off zero-current-switching (ZCS) by exploiting the resonance between the leakage inductance of the transformer and output capacitors of the voltage doubler, without additional components.

This paper also presents two advanced control algorithms. First, a variable switching frequency control scheme was implemented to reduce total harmonic distortion (THD) by reducing output ripple current. Then an advanced burst control scheme was implemented to improve power-conversion efficiency at light loads. By distributing output current temporally at light loads, input ripple voltage can be reduced. Therefore, the size of decoupling capacitors is reduced and MPPT efficiency is improved compared with the conventional burst control [12,13]. Section 2 describes the circuit structure and operating principles of the proposed micro-inverter, Section 3 gives the proposed control schemes, Section 4 shows experimental results using a 320-W prototype micro-inverter, and Section 5 concludes the paper.

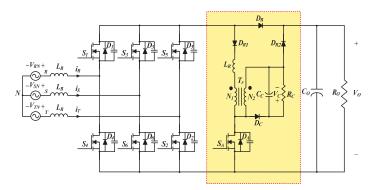

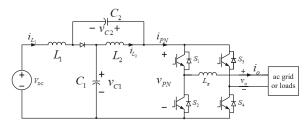

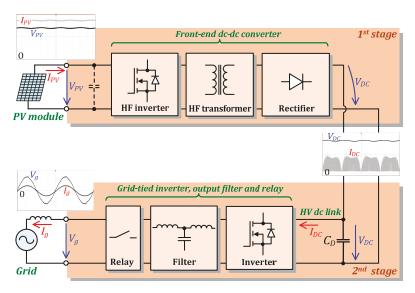

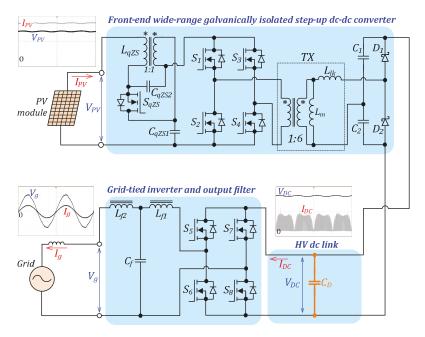

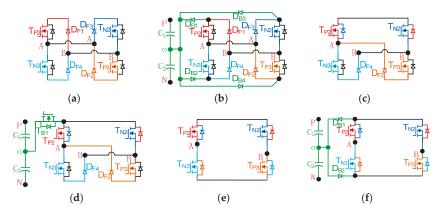

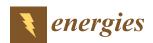

#### 2. Circuit Structure and Operating Principles of the Proposed Micro-inverter

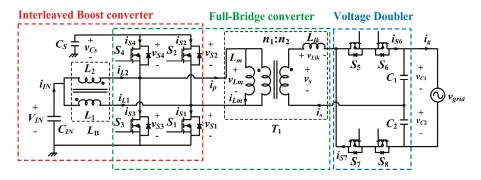

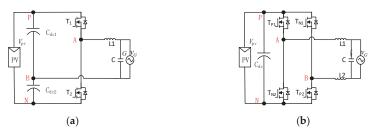

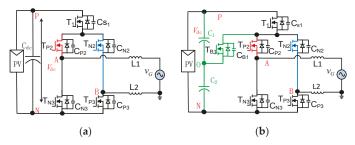

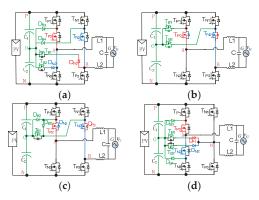

The proposed micro-inverter (Figure 1) consists of an interleaved boost converter, a full-bridge converter, and a voltage doubler. The portion that is composed of the interleaved boost and full-bridge converters is based on a boost half-bridge topology. The interleaved boost converter consists of an inversely-coupled inductor  $L_B$ , four switches  $S_1$ – $S_4$ , and a storage capacitor  $C_5$ . The full-bridge converter consists of a transformer  $T_1$  and the same four switches  $S_1$ – $S_4$  as the interleaved boost converter. The voltage doubler has four switches  $S_5$ – $S_8$  and two capacitors  $C_1$  and  $C_2$ .

Figure 1. The circuit structure of the proposed micro-inverter.

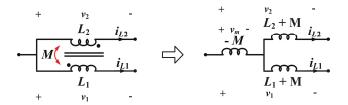

In the proposed interleaved boost converter, two inductors  $L_1$  and  $L_2$  form  $L_B$  (Figure 2) by using a single magnetic core instead of two separate magnetic cores used in the conventional interleaved boost converter [14].  $L_B$  has a turns ratio of 1:1;  $L_1$  and  $L_2$  each have self-inductance L. The mutual inductance M between  $L_1$  and  $L_2$  is represented as:

$$M = kL, (k < 0), \tag{1}$$

where k is the coupling coefficient. The voltage drops of  $L_1$  and  $L_2$  are given, respectively, by

$$v_1 = L\frac{di_1}{dt} - M\frac{di_2}{dt},\tag{2}$$

and

$$v_2 = L\frac{di_2}{dt} - M\frac{di_1}{dt}. (3)$$

Using Equations (2) and (3) and  $v_m = -Md(i_1 + i_2)/dt$  yields

$$v_1 - v_m = (L+M)\frac{di_1}{dt} \tag{4}$$

and

$$v_2 - v_m = (L+M)\frac{di_2}{dt}. (5)$$

$S_1$ , the body diode of  $S_2$ , and  $L_1$  form one boost power stage.  $S_3$ , the body diode of  $S_4$  and  $L_2$  form the other boost power stage. The two boost power stages form an interleaved boost converter and two outputs operate out of phase. When  $S_1$  or  $S_3$  is turned on, voltage  $v_{IN}$  is applied to  $L_1$  or  $L_2$ , respectively. When  $S_1$  or  $S_3$  is turned off, voltage  $v_{IN} - v_{Cs}$  is applied to  $L_1$  or  $L_2$ , respectively. The energy accumulated during the on-state for each boost power stage is transferred into  $C_S$ . There are four cases of the voltage  $v_1$  of  $L_1$  and the voltage  $v_2$  of  $L_2$  depending on the states of  $S_1$  and  $S_3$ . Using Equations (4) and (5), the equivalent inductance for each case is obtained (Table 1). M < 0 in Equation (1), so Table 1 demonstrates that appropriate design of the inversely coupled inductor can reduce the input ripple current of the micro-inverter [15].

**Figure 2.** The equivalent circuit of the inversely coupled inductor  $L_B$ .

Table 1. Equivalent inductances in the interleaved boost converter.

| Symbol    | Value                              | Condition                              |

|-----------|------------------------------------|----------------------------------------|

| $L_{eq1}$ | $\frac{L^2 - M^2}{L + DM/1 - D}$   | $v_1 = v_{IN}, v_2 = v_{IN} - v_{Cs}$  |

| $L_{eq2}$ | L+M                                | $v_1 = v_2 = v_{IN}$                   |

| $L_{eq3}$ | L + M                              | $v_1 = v_2 = v_{IN} - v_{Cs}$          |

| $L_{eq4}$ | $\frac{L^2 - M^2}{L + (1 - D)M/D}$ | $v_1 = v_{IN} - v_{Cs},  v_2 = v_{IN}$ |

The full-bridge converter shares four switches  $S_1$ – $S_4$  with the interleaved boost converter, and its input power comes from  $C_S$ . The leakage inductance  $L_{lk}$  of  $T_1$  and capacitors  $C_1$  and  $C_2$  in the voltage doubler form an LC resonant circuit. The LC resonant current flows through the primary and secondary sides of  $T_1$  with turns ratio  $n_1$ : $n_2$ . This current causes the body diode of each switch to conduct before the turn-on gate signal is applied, thus achieving zero-voltage-switching (ZVS) for  $S_1$ – $S_4$ .

In the voltage doubler,  $S_5$ – $S_8$  rectify current on the secondary side of  $T_1$ . When grid voltage is positive, both  $S_5$  and  $S_8$  are turned on, and both  $S_6$  and  $S_7$  act as diodes. When grid voltage is negative, both  $S_6$  and  $S_7$  are turned on, and both  $S_5$  and  $S_8$  act as diodes. The energy transferred to the voltage

doubler through  $T_1$  is stored in  $C_1$  and  $C_2$ .  $C_1$  and  $C_2$  are connected in series, and the output voltage of the micro-inverter is the sum of the voltage  $v_{C1}$  of  $C_1$  and the voltage  $v_{C2}$  of  $C_2$ .

In the proposed micro-inverter, variable-switching-frequency control is used, and the output voltage is a sinusoidal grid voltage. However, for simplicity, the analysis is based on the assumption that the micro-inverter generates a constant output voltage with a fixed switching frequency at a certain point in the analysis. In addition, the electrical losses of all components are ignored, and the following conditions are assumed:  $2\pi\sqrt{L_{lk}(C_1+C_2)}>DT_s$  and  $n^2L_m>>L_{lk}$ , where  $L_m$  is the magnetizing inductance and  $T_s$  is the switching period. The operation cycle  $S_1$ – $S_4$  is the same regardless of the polarity of the grid voltage, so the analysis considers only positive grid voltage.

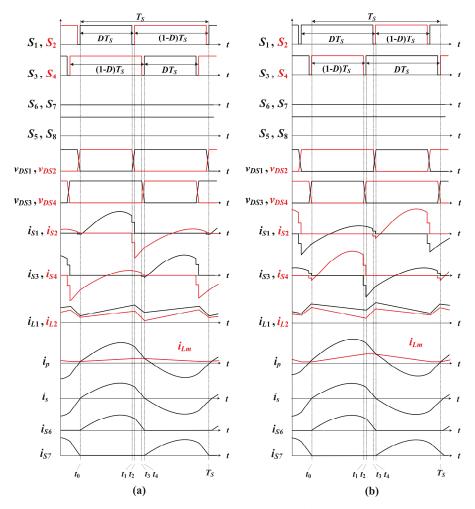

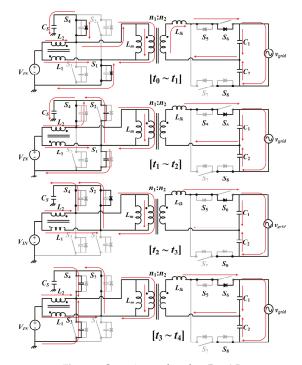

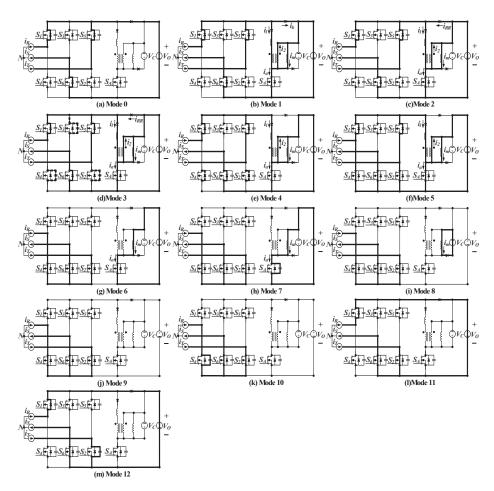

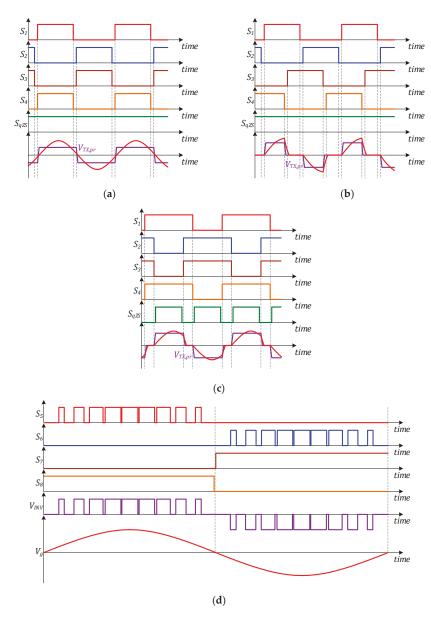

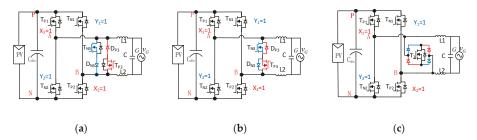

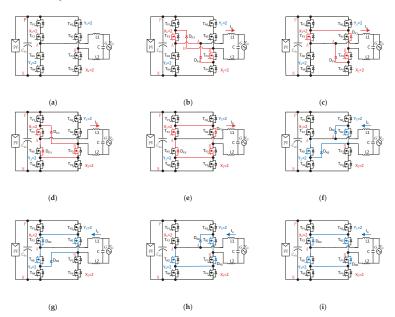

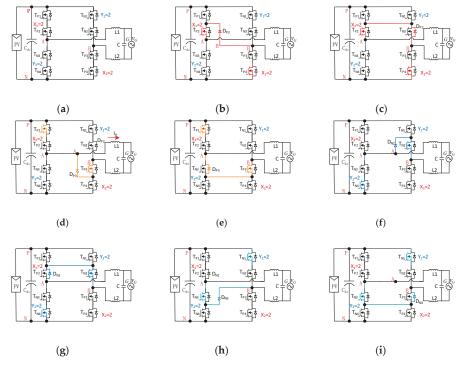

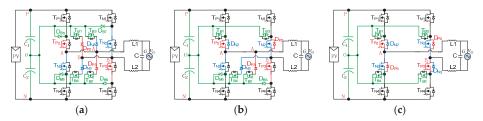

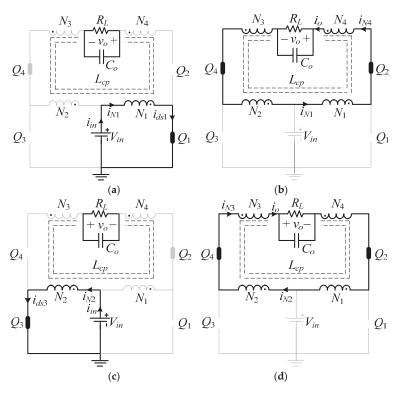

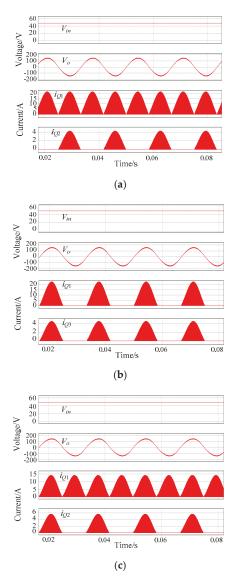

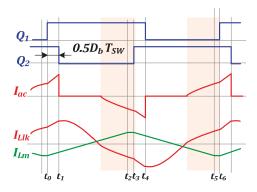

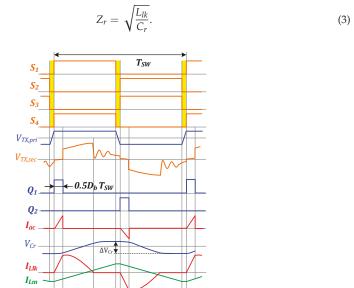

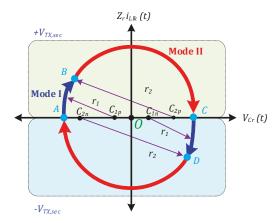

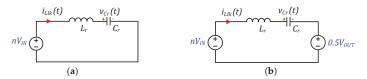

The operating waveforms (Figure 3) of the proposed micro-inverter depend on the duty ratio D. First, operational states are analyzed for  $D \le 0.5$  (Figures 3a and 4).

**Figure 3.** Operating waveforms of the proposed micro-inverter for (a)  $D \le 0.5$  and (b) D > 0.5.

**Figure 4.** Operating modes when  $D \le 0.5$ .

State 1 ( $t_0$ – $t_1$ ): At  $t = t_0$ ,  $S_1$  is turned on,  $v_{DS1} = 0$ , and  $i_{SW1} < 0$ .  $S_4$  remains in the turn-on state, and both  $S_2$  and  $S_3$  remain in the turn-off state. For  $T_1$ , the voltage  $v_{Lm}$  across  $L_m$  is equal to  $v_{Cs}$ , and the secondary voltage  $v_s$  proportional to the turns ratio  $n_1$ : $n_2$  is generated on the secondary side of  $T_1$ . The magnetizing current  $i_{Lm}$  is increased and is given by:

$$i_{Lm}(t) = i_{Lm}(t_0) + \frac{v_{Cs}}{L_m}(t - t_0).$$

(6)

Resonance is generated by  $L_{lk}$  on the secondary side of  $T_1$  and capacitors  $C_1$  and  $C_2$ , and the state equation is given by

$$L_{lk}\frac{di_s}{dt} = nv_{Lm} - v_{C1},\tag{7}$$

$$i_s = C_1 \frac{dv_{C1}}{dt} - C_2 \frac{dv_{C2}}{dt} = (C_1 + C_2) \frac{dv_{C1}}{dt}.$$

(8)

Using Equations (7) and (8), the secondary current  $i_s$  of  $T_1$  is obtained as

$$i_{s}(t) = \frac{nv_{Lm} - v_{C1}}{Z_{r}} \sin[\omega_{r}(t - t_{0})],$$

(9)

where

$$Z_r = \sqrt{\frac{L_{lk}}{C_1 + C_2}} {(10)}$$

is the resonant impedance and

$$\omega_r = \frac{1}{\sqrt{L_{lk}(C_1 + C_2)}} \tag{11}$$

is the resonant angular frequency.

From Equations (6) and (9), the primary current  $i_p$  of  $T_1$  is obtained as

$$i_p(t) = i_{Lm}(t_0) + \frac{v_{Cs}}{L_m}(t - t_0) + \frac{n^2 v_{Lm} - n v_{C1}}{Z_r} \sin[\omega_r(t - t_0)].$$

(12)

From Table 1, the currents  $i_{L1}$  and  $i_{L2}$  of the coupled inductor are obtained as

$$i_{L1}(t) = i_{L1}(t_0) + \frac{v_{IN}}{L_{eq1}}(t - t_0), \quad i_{L2}(t) = i_{L2}(t_0) + \frac{v_{IN} - v_{Cs}}{L_{eq1}}(t - t_0).$$

(13)

State 2  $(t_1-t_2)$ : At  $t = t_1$ ,  $S_1$  is turned off and  $S_4$  remains in the turn-on state. Both  $S_2$  and  $S_3$  remain in the turn-off state. This interval is a dead time to prevent shoot-through before  $S_2$  is turned on. During this state, the drain-source voltage of  $S_1$  increases from 0 V to  $v_{Cs}$  and that of  $S_2$  decreases from  $v_{Cs}$  to 0 V by charging and discharging parallel capacitance across each switch, respectively.

State 3 ( $t_2$ – $t_3$ ): At  $t = t_2$ ,  $S_2$  is turned on,  $v_{DS2} = 0$ , and  $i_{SW2} < 0$ .  $S_4$  remains in the turn-on state, and both  $S_1$  and  $S_3$  remain in the turn-off state. For  $T_1$ , the voltage  $v_{Lm}$  across  $L_m$  is 0 V and the voltage  $v_{lk}$  across  $L_{lk}$  is  $-v_{C1}$ . The amplitude of  $i_{Lm}$  remains unchanged during state 3 as:

$$i_{Lm}(t) = i_{Lm}(t_2) = i_{Lm}(t_0) + \frac{v_{Cs}}{L_m}(t_2 - t_0).$$

(14)

$i_s$  begins to decrease because the energy stored in  $L_{lk}$  is transferred to  $C_1$ , and is given by

$$i_s(t) \cong i_s(t_2) - \frac{v_{C1}}{L_{lk}}(t - t_2) = \frac{nv_{Lm} - v_{C1}}{Z_r} \sin[\omega_r(t_2 - t_0)] - \frac{v_{C1}}{L_{lk}}(t - t_2).$$

(15)

From Equations (14) and (15),  $i_p$  is obtained as

$$i_p(t) = i_{Lm}(t_0) + \frac{v_{Cs}}{L_m}(t_2 - t_0) + \frac{n^2 v_{Lm} - n v_{C1}}{Z_r} \sin[\omega_r(t_2 - t_0)] - \frac{n v_{C1}}{L_{lk}}(t - t_2).$$

(16)

From Table 1,  $i_{L1}$  and  $i_{L2}$  are obtained as

$$i_{L1}(t) = i_{L1}(t_2) + \frac{v_{IN}}{L_{\rho\rho\beta}}(t - t_2), \quad i_{L2}(t) = i_{L2}(t_2) + \frac{v_{IN} - v_{Cs}}{L_{\rho\rho\beta}}(t - t_2).$$

(17)

State 4  $(t_3-t_4)$ : At  $t=t_3$ ,  $S_4$  is turned off and  $S_2$  remains in the turn-on state. Both  $S_1$  and  $S_3$  remain in the turn-off state. This time interval is a dead time to prevent shoot-through before  $S_3$  is turned on. During this state, the drain-source voltage of  $S_4$  increases from 0 V to  $v_{Cs}$  and that of  $S_3$  decreases from  $v_{Cs}$  to 0 V.

The proposed micro-inverter has an interleaved structure, so both the operating principle of the next half cycle for  $D \le 0.5$  and the operating principle for D > 0.5 are the same as the above analysis except for the switches used. Thus, further analysis for the others is not given.

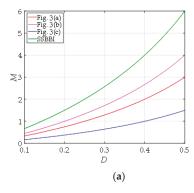

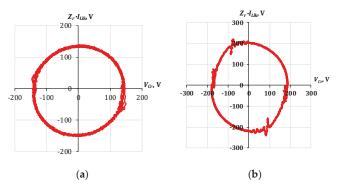

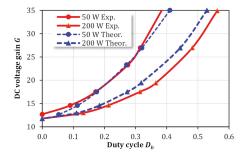

The voltage gain  $G_v$  of the proposed micro-inverter is twice the product of the boost converter voltage gain and the full bridge converter voltage gain:

$$G_v = \frac{V_{grid}}{V_{IN}} = 2 \cdot \frac{1}{1 - D} \cdot 2nD = \frac{4nD}{1 - D}.$$

(18)

#### 3. The Proposed Control Schemes

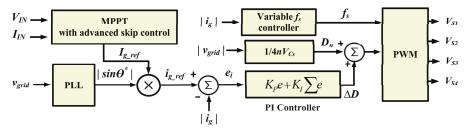

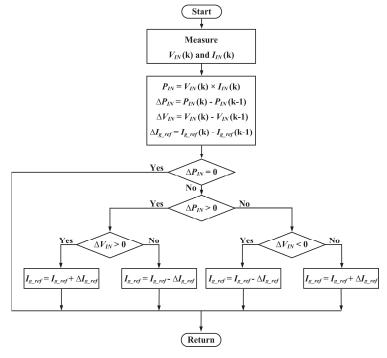

The main controller (Figure 5) for the proposed micro-inverter takes as analog-to-digital inputs the grid voltage  $v_{grid}$ , the grid current  $i_g$ , the input voltage  $V_{IN}$  and the input current  $I_{IN}$ . The MPPT controller is based on the perturb and observe (P&O) MPPT algorithm [16]. This controller determines the amplitude of the reference grid current  $I_{g\_ref}$  by using  $I_{IN}$  and  $V_{IN}$  to maximize solar power

generation. In the P&O MPPT algorithm used (Figure 6),  $I_{g\_ref}$  is increased if  $\Delta P_{IN} > 0$  and  $\Delta V_{IN} > 0$  or if  $\Delta P_{IN} < 0$  and  $\Delta V_{IN} < 0$ . If  $\Delta P_{IN} < 0$  and  $\Delta V_{IN} < 0$  or if  $\Delta P_{IN} < 0$  and  $\Delta V_{IN} < 0$ . This process is repeated until the maximum power point (MPP) is reached, i.e.,  $\Delta P_{IN} = 0$ .

Figure 5. Block diagram of the main controller for the proposed micro-inverter.

Figure 6. The perturb and observe MPPT algorithm.

The phase-locked loop (PLL) generates the phase information  $|\sin \theta^*|$  by using  $v_{grid}$ . In the PLL, virtual voltage  $v_{q1}$  is derived from  $v_{grid}$  for phase detection.

$$v_{q1}(s) = G_{PLL}(s)v_{grid}(s) = V_{grid}(-\frac{1}{s+\omega} + \frac{s}{s^2+\omega^2} + \frac{\omega}{s^2+\omega^2}), \tag{19} \label{eq:pll}$$

where  $G_{PLL}(s)$  is PLL gain and  $V_{grid}$  is the amplitude of  $v_{grid}$ .

From the inverse Laplace transform of  $v_{q1}(s)$ ,

$$v_{q1}(t) = V_{grid}(-e^{\omega t} + \cos \omega t + \sin \omega t) \approx V_{grid}(\cos \omega t + \sin \omega t), \tag{20}$$

where  $\omega t$  is the actual phase of the grid.

Using equation (20), the other virtual voltage  $v_{q2}$  is obtained as

$$v_{a2}(t) = v_{a1}(t) - v_{orid}(t) = V_{orid} \sin \omega t. \tag{21}$$

$v_{grid}$  and  $v_{q2}$  are transformed into the synchronous reference frame as follows:

$$\begin{bmatrix} v^e_{grid} \\ v^e_{q2} \end{bmatrix} = \begin{bmatrix} \cos \theta^* \sin \theta^* \\ -\sin \theta^* \cos \theta^* \end{bmatrix} \begin{bmatrix} v_{grid} \\ v_{q2} \end{bmatrix}, \tag{22}$$

where  $\theta^*$  is a phase output from the PLL. From Equation (22),

$$v^e_{grid} = V_{grid}\cos(\omega t - \theta^*) \approx V_{grid},$$

(23)

$$v^e_{q2} = V_{grid} \sin(\omega t - \theta^*) \approx V_{grid}(\omega t - \theta^*).$$

(24)

The PLL generates  $\theta^*$  to follow  $\omega$ t through PI control inside the PLL. The reference current signal  $i_{g\_ref}$  is the product of  $I_{g\_ref}$  and  $|\sin\theta^*|$ :

$$i_{g\_ref} = I_{g\_ref} \Big| \sin \theta^* \Big|. \tag{25}$$

The proportional-integral (PI) controller determines the duty ratio variation  $\Delta D$  by using the difference between  $i_{g\_ref}$  and  $|i_g|$  as follows:

$$\Delta D = K_P(i_{g\_ref} - \left| i_g \right|) + K_I \sum (i_{g\_ref} - \left| i_g \right|)$$

(26)

$\Delta D$  compensates for the voltage drop of  $L_{lk}$ , so that  $i_g$  follows  $i_{g\_ref}$ . The nominal duty ratio

$$D_n = \frac{\left| v_{grid} \right|}{G_v} = \frac{\left| v_{grid} \right|}{4nV_{Cs}} \tag{27}$$

provides stable system dynamics for nonlinear sinusoidal waves which are difficult to control using only  $\Delta D$ . The total duty ratio

$$D = D_n + \Delta D = \frac{|v_{grid}|}{4nV_{Cs}} + K_P(i_{g\_ref} - |i_g|) + K_I \sum_{g\_ref} (i_{g\_ref} - |i_g|)$$

(28)

where  $D_n$  is duty ratio generated by the grid voltage and  $\Delta D$  is a duty ratio variation generated by the grid current. D is given to the pulse-width-modulation (PWM) controller. The PWM controller generates gate signals for switches to track the reference power.

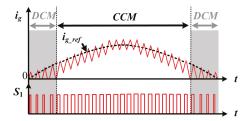

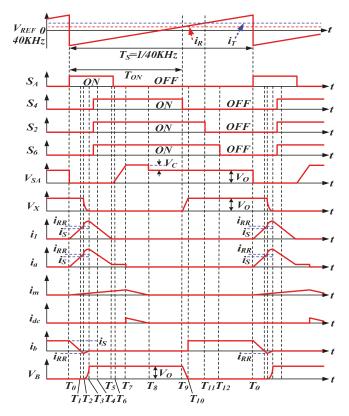

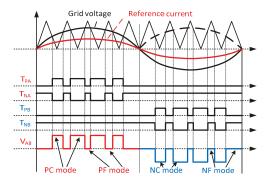

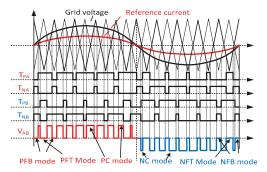

Operating modes (Figure 7) depend on the grid current level when grid voltage is positive. When  $i_g$  is low, the proposed micro-inverter operates in discontinuous conduction mode (DCM) because  $i_g$  becomes zero before the end of the switching cycle with the period  $T_s$ . When  $i_g$  is high, continuous conduction mode (CCM) is applied.

If a fixed switching frequency is used for the operating modes, especially the DCM mode, two problems occur: (1) High grid current ripples at low grid currents increase total harmonic distortion (THD); (2) as the output power decreases, the total DCM operating time can increase over the total CCM operating time, and the power conversion efficiency of the micro-inverter can be reduced by high current stress. To solve these problems, this paper proposes two advanced control schemes: Variable-switching-frequency (VSF) control and the advanced burst (AB) control.

Figure 7. Operating modes depending on the grid current level during the positive grid voltage.

#### 3.1. Variable Switching Frequency Control

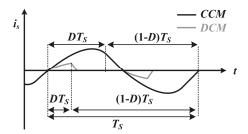

During  $T_s$ ,  $i_s$  of  $T_1$  in DCM and CCM modes vary with D (Figure 8). As D decreases, the energy stored in  $L_{lk}$  decreases, so time required to demagnetize  $L_{lk}$  decreases. Therefore, the micro-inverter is operated in DCM mode. From Equations (9) and (15), the operating condition for DCM is given by

$$0 > \frac{nv_{Lm} - v_{C1}}{Z_r} \sin \omega_r DT_s - \frac{v_{C1}T_s}{2L_{lk}} (1 - 2D)$$

(29)

**Figure 8.** Secondary current  $i_s$  of the transformer  $T_1$  depending on the operating mode.

Existing methods to optimize the DCM mode duration have drawbacks. One method is to increase the value of  $L_{lk}$ ; a large  $L_{lk}$  increases the inductive energy and increases the demagnetizing time, but this solution requires a large transformer with a large number of windings. Another solution is to increase the switching frequency  $f_s$ ; this approach can also increase the power density, but high  $f_s$  causes high switching loss. Thus, this paper presents VSF control, which minimizes switching loss without increasing the transformer size. VSF control varies  $f_s$  depending on the magnitude  $|i_g|$  of the grid current.

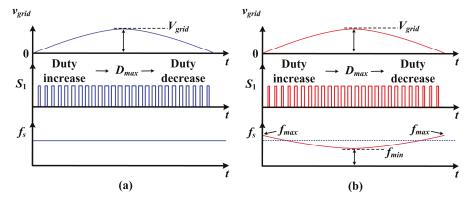

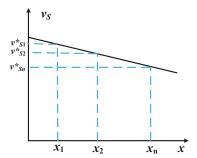

Fixed-switching-frequency (FSF) control and VSF controls have distinct attributes (Figure 9). FSF control changes only D depending on  $v_{grid}$  (Figure 9a). In contrast, VSF control changes both D and  $f_s$  depending on  $v_{grid}$  (Figure 9b). When  $v_{grid}$  is near zero, the switching loss is very small because  $i_g$  is close to zero. Therefore, when VSF control is used,  $f_s$  is increased to the maximum switching frequency  $f_{max}$  and the time interval between demagnetizings of  $L_{lk}$  is reduced (Figure 9b). As  $v_{grid}$  increases,  $f_s$  is decreased to the minimum switching frequency  $f_{min}$  to reduce switching losses.  $f_s$  is given by

$$f_s = f_{\text{max}} - (f_{\text{max}} - f_{\text{max}}) \frac{v_{grid}}{V_{grid}}$$

(30)

where  $V_{grid}$  is the peak value of  $v_{grid}$ .

Figure 9. (a) Fixed and (b) variable switching frequency controls.

#### 3.2. Advanced Burst Control

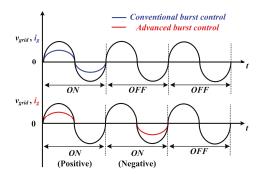

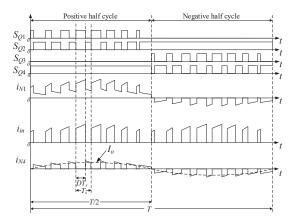

When solar power generation and load are very small, micro-inverters operate only intermittently to supply the desired power to the grid on an average power basis. This intermittent operation is called "burst control". For the burst control, the micro-inverter supplies  $i_g$  to the grid only during the ON state, and stops running during the OFF state. The burst control improves power-conversion efficiency by reducing the ripple of  $i_g$  and switching loss when the load is small.

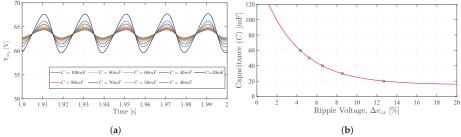

In the conventional burst control scheme, positive and negative grid currents are consecutively supplied to the grid during one ON-state period (Figure 10). Then OFF-state periods follow the ON-state period. During the OFF state, no power is output, so output occurs only during the ON state, and the energy flowing out of  $C_{IN}$  is also concentrated. Therefore, the input ripple voltage  $\Delta V_{IN}$  is increased, the MPPT efficiency is reduced, and additional time is required to charge the input capacitor  $C_{IN}$  for the next operation.

Figure 10. Conventional and advanced burst control schemes.

To further improve the performance of burst control, this paper proposes AB control, which supplies positive grid current during the first ON-state (Figure 10). The negative grid current is supplied during the ON-state that immediately follows the first ON-state period. Then, OFF-state periods follow the ON-state periods. This scheme has the effect of distributing the output current temporally compared with the conventional burst control scheme. Therefore, in the proposed micro-inverter with the advanced burst control scheme, the MPPT efficiency can be improved, and the input capacitance  $C_{IN}$  can be reduced due to the reduced  $\Delta V_{IN}$ .

#### 4. Experimental Results

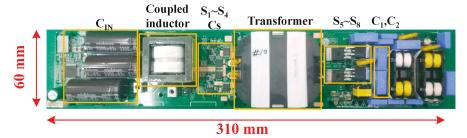

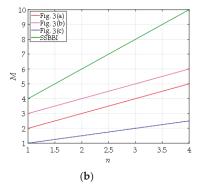

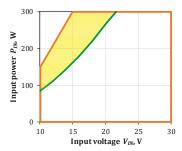

The proposed grid-connected micro-inverter (Figure 11) was designed to operate at the rated power 320 W,  $V_{IN} = 25 \sim 52$  V<sub>DC</sub>,  $I_{IN.max} = 12$  A<sub>DC</sub>, and  $f_s = 60 \sim 90$  kHz. The grid voltage was 220 V<sub>rms</sub>, the grid frequency was 60 Hz, and grid current supplied by the proposed micro-inverter is  $0 \sim 1.45$  A<sub>rms</sub>. The proposed micro-inverter was implemented using the circuit parameters given in Table 2. The microcontroller used was a MN103DF35 (PANASONIC). For the PI controller in the main controller,  $K_P$  and  $K_I$  were experimentally optimized and set to 9.5 and 200, respectively. The sampling frequency for analog signals is 20 kHz, and the resolution of the analog-to-digital converter is 12 bits. The turns ratio of  $L_B$  is 10:10 and that of  $T_1$  is 6:19. The resonant frequency  $f_r = 35.5$  kHz from  $L_{Ik} = 100$   $\mu$ H and  $C_1 = C_2 = 100$  nF. The MOSFET package of  $S_1 - S_4$  is PG-TDSON-8 and that of  $S_5 - S_8$  is D<sup>2</sup>PAK. Capacitors  $C_s$ ,  $C_1$  and  $C_2$  are MPP-film type. The fabricated micro-inverter was compact and slim with 60-mm width, 310-mm length, and 30-mm height.

Figure 11. Photograph of the proposed micro-inverter.

Table 2. Hardware specifications and circuit parameters.

| Unit Type | Symbol           | Value                                   | Note                                                      |

|-----------|------------------|-----------------------------------------|-----------------------------------------------------------|

|           | $P_o$            | 320 W                                   | Output power                                              |

|           | $C_{IN}$         | 9900 μF                                 | Input capacitor                                           |

|           | $L_1, L_2$       | 190 μΗ                                  | Self inductance ( $k = -0.947$ )                          |

|           | $S_1$ – $S_4$    | BCS035N10NS5                            | MOSFET ( $V_{DS} = 100 \text{ V}, I_D = 100 \text{ A}$ )  |

|           | $C_s$            | 60 μF                                   | Storage capacitor                                         |

|           | $L_m$            | 600 μΗ                                  | Magnetizing inductance                                    |

| Micro     | $L_{lk}$         | 100 μΗ                                  | Leakage inductance                                        |

| Inverter  | $S_5 - S_8$      | IPB65R150                               | MOSFET ( $V_{DS} = 650 \text{ V}, I_D = 22.4 \text{ A}$ ) |

|           | $C_1, C_2$       | 100 nF                                  | Doubler capacitors                                        |

|           | $f_s$            | 60~90 kHz                               | Switching frequency                                       |

|           | $v_{grid}$       | $220  \mathrm{V_{rms}}/60  \mathrm{Hz}$ | Grid voltage                                              |

|           | $i_g$            | $\sim 1.45 \; A_{rms}/60 \; Hz$         | Grid current                                              |

|           | $V_{IN}^{\circ}$ | 25~52 V <sub>DC</sub>                   | Operating voltage range                                   |

|           | $I_{IN.max}$     | $12 A_{DC}$                             | Max input current                                         |

|           | $V_{PV}$         | 40.9 V                                  | Open circuit voltage                                      |

| PV        | $V_{MP}$         | 34 V                                    | MPP voltage                                               |

| module    | $I_{PV}$         | 10.05 A                                 | Short circuit current                                     |

|           | $I_{MP}$         | 9.38 A                                  | MPP current                                               |

Instead of an actual PV module, the photovoltaic simulator ETS600X14CPVF TerraSAS from AMETEK was used as an input source. The solar cell I-V characteristic curve for the experiment was based on that of the NeON\$2 PV module from LG electronics.

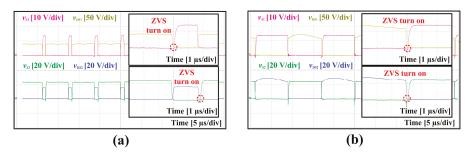

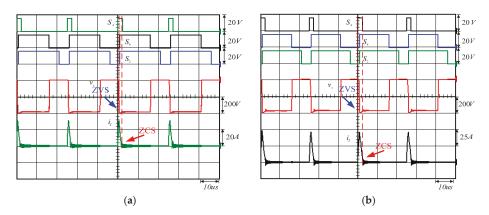

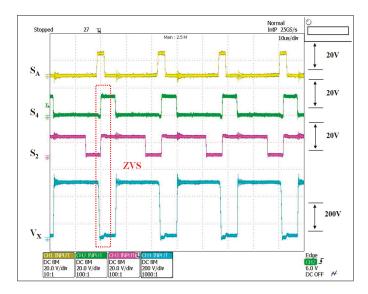

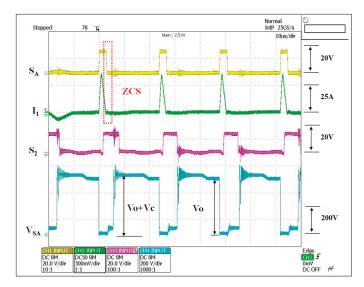

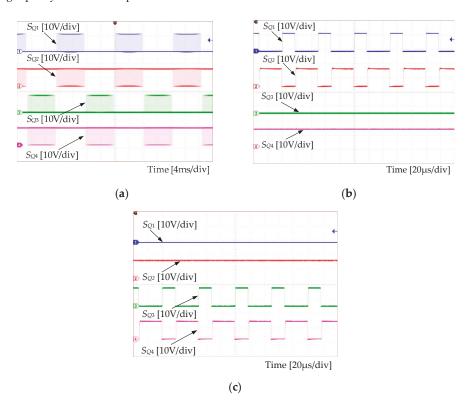

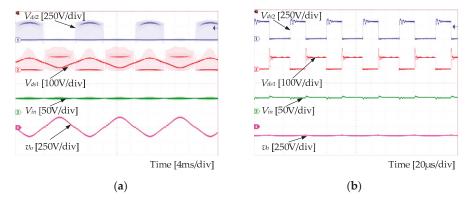

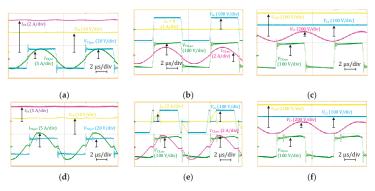

Gate-source and drain-source voltages were obtained for  $S_1$  and  $S_2$  at  $D \le 0.5$  (Figure 12a) and at D > 0.5 (Figure 12b) at  $V_{IN} = 34$  V and  $v_{grid} = 220$  V<sub>rms</sub> /60 Hz. The drain-source voltage v<sub>DS1</sub> of  $S_1$  drops to 0 V before the gate signal  $v_{S1}$  is applied, so  $S_1$  turns on with ZVS.  $S_2$  is complementary to  $S_1$

and achieves a ZVS turn-on. The operation of  $S_3$  and  $S_4$  is out of phase with that of  $S_1$  and  $S_2$ , so  $S_3$  and  $S_4$  can also achieve the ZVS turn-on.

**Figure 12.** Gate-source and drain-source voltages of  $S_1$  and  $S_3$  for (a)  $D \le 0.5$  and (b) D > 0.5.

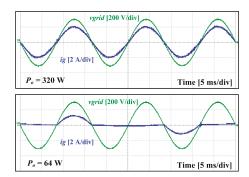

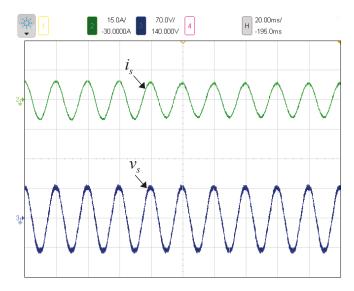

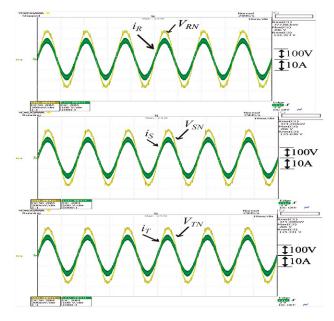

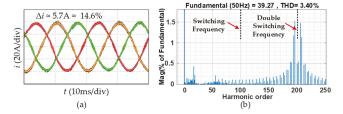

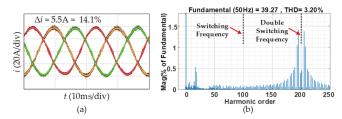

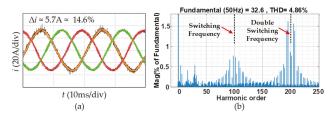

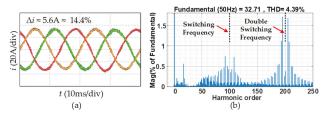

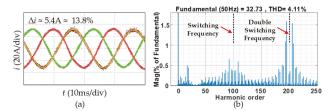

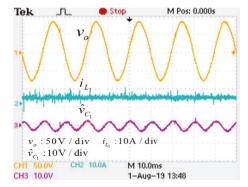

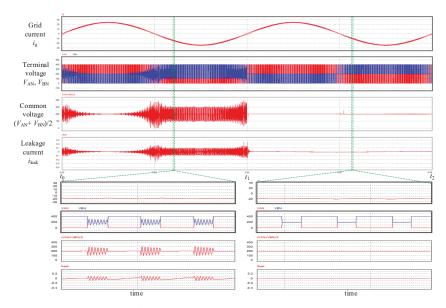

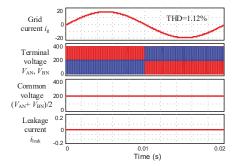

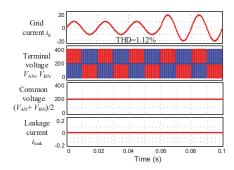

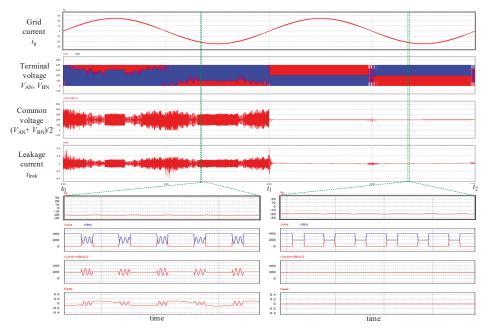

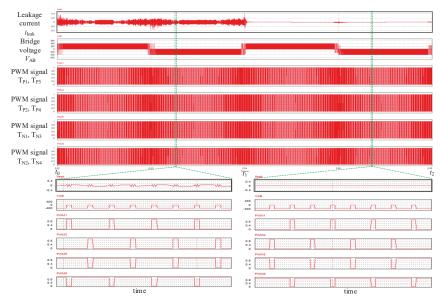

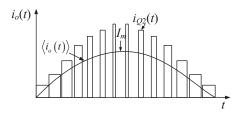

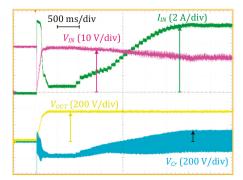

Waveforms (Figure 13) were obtained for  $v_{grid}$  and  $i_g$  at  $V_{IN}$  = 34 V and  $v_{grid}$  = 220V<sub>rms</sub> / 60 Hz for output power  $P_o$  = 320 W and 64 W. To maximize efficiency, the proposed micro-inverter operates in normal mode at  $P_o$   $\geq$  110 W and in AB control mode at  $P_o$  < 110 W. The boundary of the output power at which the proposed micro-inverter switches from the normal mode to AB control mode and vice versa is selected to be in a range where the peak value of  $i_g$  does not exceed the rated grid current.

Figure 13. Grid voltage and current waveforms.

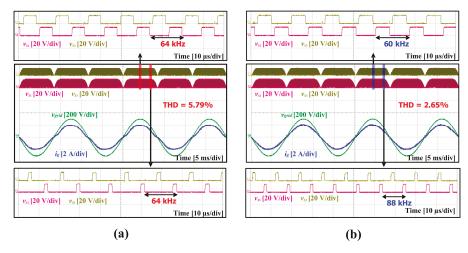

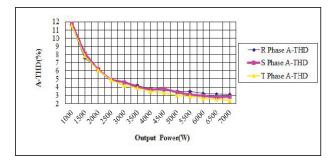

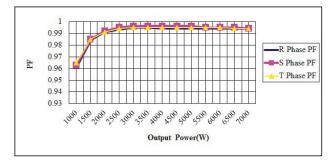

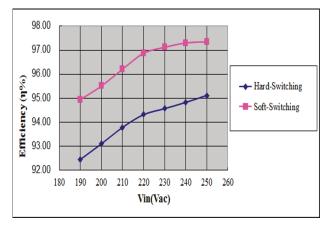

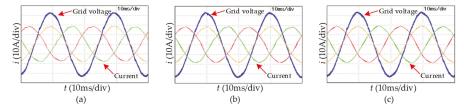

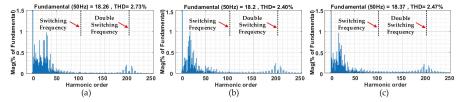

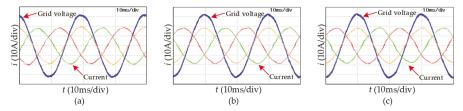

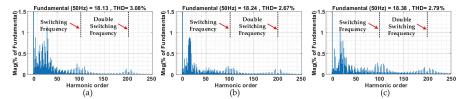

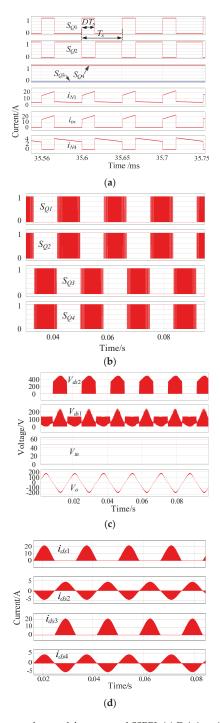

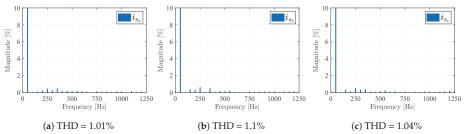

Waveforms were obtained for the fixed-frequency (Figure 14a) and the variable-switching-frequency (Figure 14b) controls. Gate signals of  $S_1$  and  $S_3$ ,  $i_g$  and  $v_{grid}$  were measured at  $V_{IN} = 34$  V,  $v_{grid} = 220$  V<sub>rms</sub> / 60 Hz, and output power  $P_o = 320$  W. When fixed-switching frequency control was used,  $i_g$  was distorted near zero-crossing, and THD was increased to 5.79%. In contrast, when variable switching frequency control was used, the distortion of  $i_g$  was improved near zero-crossing, and THD was reduced to 2.65%, which is below the requirement for distributed power. The switching frequency  $f_s$  decreased as  $i_g$  increased, so switching loss was also reduced.

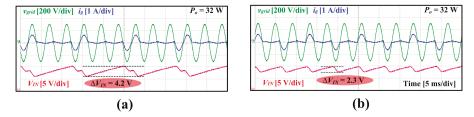

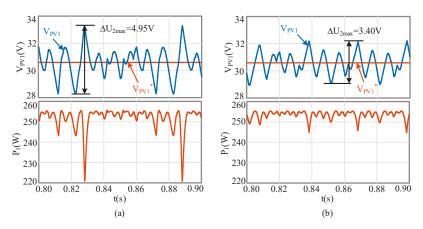

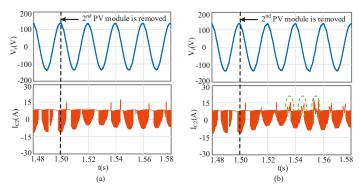

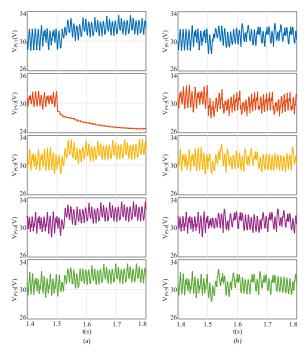

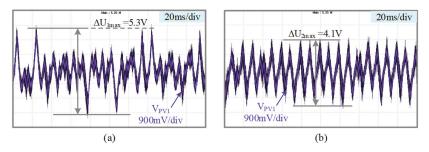

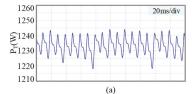

$\Delta V_{IN}$  is higher when conventional burst control is used (Figure 15a) than when AB control is used (Figure 15b), because AB control reduces the energy supplied by  $C_{IN}$  during one ON-state period. At  $V_{IN}$  = 34 V,  $v_{grid}$  = 220 V<sub>rms</sub> / 60 Hz, and  $P_o$  = 32 W,  $\Delta V_{IN}$  was 4.2 V when conventional burst control was used, but 2.4 V when AB control was used.

**Figure 14.** Gate signals of  $S_1$  and  $S_3$ , grid voltage and grid current in (a) the fixed and (b) the variable switching frequency controls.

Figure 15. Input ripple voltage in (a) the conventional and (b) the advanced burst controls.

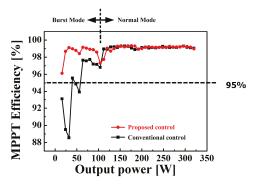

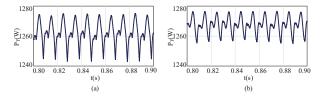

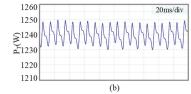

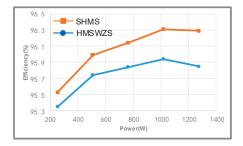

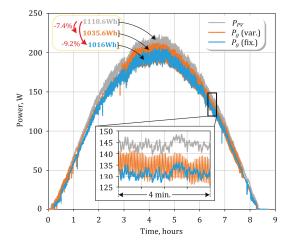

The MPPT efficiency of the proposed micro-inverter was measured (Figure 16) in the range of irradiance from 50 W/m² ( $P_o$  = 16 W)–1000 W/m² ( $P_o$  = 320 W). In the proposed control scheme, for  $P_o$  < 110 W (burst mode), the MPPT efficiency was kept >95% because  $\Delta V_{IN}$  and  $\Delta I_{g\_ref}$  are reduced. However, in the conventional control scheme, the MPPT efficiency was reduced to ~88% because fluctuation of  $I_{g\_ref}$  increased. During burst mode, the maximum MPPT efficiency was >99% for the proposed control scheme but <97.5% for the conventional control scheme.

Figure 16. MPPT efficiency depending on control methods.

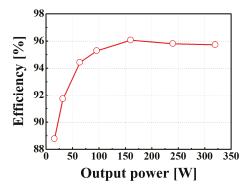

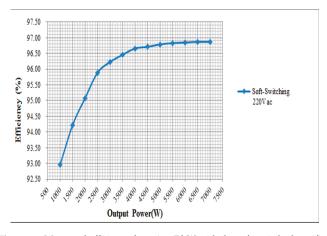

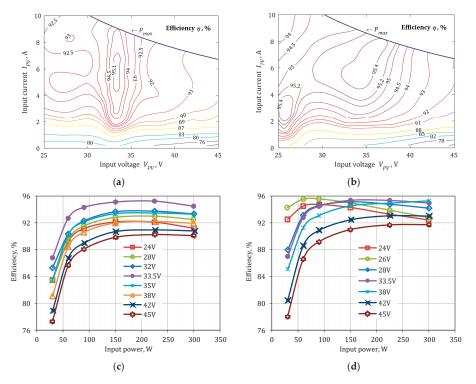

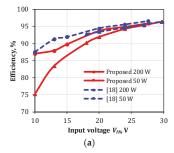

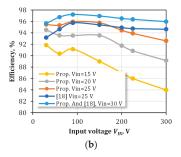

In a micro-inverter, one of the most important factors is the power conversion efficiency  $\eta_\ell$  for 50~75% load under actual solar irradiation. Therefore, the California Energy Commission (CEC) weighted efficiency to represent this fact has been widely used to measure the performance of micro-inverters. The power conversion efficiency  $\eta_\ell$  (Figure 17) was measured for the proposed micro-inverter; the result indicate that the CEC weighted efficiency [17,18] is 95.55%, in which  $\eta_\ell$ (10%) = 91.71%,  $\eta_\ell$ (20%) = 94.42%,  $\eta_\ell$ (30%) = 95.28%,  $\eta_\ell$ (50%) = 96.06%,  $\eta_\ell$ (75%) = 95.8%, and  $\eta_\ell$ (100%) = 95.72%. The maximum  $\eta_\ell$  is 96.06% for  $P_o$  = 160 W.

Figure 17. Power conversion efficiency  $\eta_{\ell}$  measured at  $V_{IN}=34~\mathrm{V}$  and  $v_{grid}=220~\mathrm{V}_{rms}/60~\mathrm{Hz}$ .

#### 5. Conclusions

A compact single-stage micro-inverter with advanced control schemes for PV systems is described. The proposed micro-inverter achieved a high voltage-conversion ratio and high efficiency by using a new topology that consists of an interleaved boost converter, a full-bridge converter, and a voltage doubler. The leakage inductance of the transformer and the capacitors of the voltage doubler ensure ZVS condition without any additional components. A variable-switching-frequency control scheme is applied to the micro-inverter to decrease THD by reducing the grid ripple current. An advanced burst-control scheme increases MPPT efficiency with smaller input ripple voltage than the conventional burst control causes. A fabricated 320-W prototype micro-inverter was very compact and slim with 60-mm width, 310-mm length, and 30-mm height. It achieved CEC weighted efficiency of 95.55%, MPPT efficiency > 95% over the entire load rage, and THD 2.65% at  $V_{IN} = 34$  V,  $v_{grid} = 220$  V  $v_{rms}$  /60 Hz, and  $P_o = 320$  W. These results show that the proposed micro-inverter is well suited for PV micro-inverter applications that require low cost, small and slim size, high efficiency, and low noise.

**Author Contributions:** Y.-G.C. conceived the main idea for the proposed micro-inverter and performed overall analysis and experiment with H.-S.L., B.K. led the project and gave technical advice. S.-C.L. contributed to determining circuit parameters and fabricating a prototype. S.-J.Y. contributed to analyzing the experimental results and writing the manuscript with Y.-G.C.

**Acknowledgments:** This research was supported by the Ministry of Science and ICT (MSIT), Korea, under the "ICT Consilience Creative Program" (IITP-2018-2011-1-00783) supervised by Institute for Information & communications Technology Promotion (IITP).

Conflicts of Interest: The authors have no conflict of interest.

#### References

- Lee, S.-W.; Cho, B.-H. Master–Slave Based Hierarchical Control for a Small Power DC-Distributed Microgrid System with a Storage Device. *Energies* 2016, 9, 880. [CrossRef]

- Han, H.; Luo, C.; Hou, X.; Su, M.; Yuan, W.; Liu, Z.; Guerrero, J.M. A Cost-Effective Decentralized Control for AC-Stacked Photovoltaic Inverters. *Energies* 2018, 11, 2262. [CrossRef]

- Huang, L.; Qiu, D.; Xie, F.; Chen, Y.; Zhang, B. Modeling and Stability Analysis of a Single-Phase Two-Stage Grid-Connected Photovoltaic System. Energies 2017, 10, 2176. [CrossRef]

- Jeong, H.-G.; Kim, G.-S.; Lee, K.-B. Second-Order Harmonic Reduction Technique for Photovoltaic Power Conditioning Systems Using a Proportional-Resonant Controller. *Energies* 2013, 6, 79–96. [CrossRef]

- 5. Blaabjerg, F.; Chen, Z.; Kjaer, S.B. Power electronics as efficient interface in dispersed power generation system. *IEEE Trans. Power Electron.* **2004**, *19*, 1184–1194. [CrossRef]

- Nanakos, A.C.; Christidis, G.C.; Tatakis, E.C. Weighted efficiency optimization of flyback microinverter under improved boundary conduction mode (i-BCM). *IEEE Trans. Power Electron.* 2015, 30, 5548–5564.

[CrossRef]

- Rezaei, M.A.; Lee, K.J.; Huang, A.Q. A high-efficiency flyback micro-inverter with a new adaptive snubber for photovoltaic applications. *IEEE Trans. Power Electron.* 2016, 31, 318–327. [CrossRef]

- Chen, Y.; Liao, C. A PV micro-inverter with PV current decoupling strategy. IEEE Trans. Power Electron. 2017, 32, 6544–6557.

- Voglitsis, D.; Papanikolaou, N.; Kyritsis, A.C. Incorporation of harmonic injection in an interleaved flyback inverter for the implementation of an active anti-islanding technique. *IEEE Trans. Power Electron.* 2017, 32, 8526–8543. [CrossRef]

- Milad, K.; Ehsan, A.; Hosein, F. Micro-inverter based on single-ended primary-inductance converter topology with an active clamp power decoupling. IET Power Electron. 2018, 11, 73–81.

- Jafari, M.; Malekjamshidi, Z.; Li, L.; Zhu, J.G. Performance analysis of full bridge, boost half bridge and half bridge topologies for application in phase shift converters. In Proceedings of the International Conference on Electrical Machines and Systems, Busan, Korea, 26–29 October 2013; pp. 1589–1594.

- 12. Zhao, Z.; Wu, K.-H.; Lai, J.-S.; Yu, W. Utility grid impact with high penetration PV micro-inverters operating under burst mode using simplified simulation model. In Proceedings of the Energy Conversion Congress and Exposition (ECCE), Phoenix, AZ, USA, 17–22 September 2011; pp. 3928–3932.

- Du, Y.; Xiao, W.; Hu, Y.; Lu, D.D.-C. Control approach to achieve burst mode operation with DC-link voltage protection in single-phase two-stage PV inverters. In Proceedings of the Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 47–52.

- Thiyagarajan, A.; Praveen Kumar, S.G.; Nandini, A. Analysis and comparison of conventional and interleaved DC/DC boost converter. In Proceedings of the Second International Conference on Current Trends In Engineering and Technology—ICCTET 2014, Coimbatore, India, 8 July 2014; pp. 198–205.

- Wong, P.; Wu, Q.; Xu, P.; Bo, Y.; Lee, F.C. Investigating coupling inductors in the interleaving QSW VRM. In Proceedings of the APEC 2000, Fifteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.00CH37058), New Orleans, LA, USA, 6–10 February 2000; pp. 973–978.

- Ahmed, A.S.; Abdullah, B.A.; Abdelaal, W.G.A. Mppt algorithms: Performance and evaluation. In Proceedings of the 11th International Conference on Computer Engineering & Systems (ICCES), Cairo, Egypt, 20–21 December 2016; pp. 461–467.

- 17. Building Energy Efficiency Standards; California Energy Commission: Sacramento, CA, USA, 2019.

- Zhang, L.; Sun, K.; Hu, H.; Xing, Y. A system-level control strategy of photovoltaic grid-tied generation systems for European efficiency enhancement. IEEE Trans. Power Electron. 2014, 29, 3445–3453. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

# Five-Level T-type Cascade Converter for Rooftop Grid-Connected Photovoltaic Systems

Cristian Verdugo <sup>1,‡</sup>, Samir Kouro <sup>2,†,‡</sup>, Christian A. Rojas <sup>2,\*,†,‡</sup>, Marcelo A. Perez <sup>2,†,‡</sup>, Thierry Meynard <sup>3,‡</sup> and Mariusz Malinowski <sup>4,‡</sup>

- Electrical Engineering Department, Polytechnic University of Catalonia, 08222 Barcelona, Spain; cristian.andres.verdugo@upc.edu

- <sup>2</sup> Electronics Engineering Department, Universidad Técnica Federico Santa María, Valparaiso 2390123, Chile; samir.kouro@usm.cl (S.K.); marcelo.perez@usm.cl (M.A.P.)

- Institut National Polytechnique de Toulouse, 31071 Toulouse, France; Thierry. Meynard@laplace.univ-tlse.fr

- <sup>4</sup> Institute of Control & Industrial Electronics, Warsaw University of Technology, 00-662 Warsaw, Poland; malin@isep.pw.edu.pl

- Correspondence: christian.rojas@usm.cl

- † Current address: Av. España 1680, Valparaíso 2390123, Chile.

- ‡ These authors contributed equally to this work.

Received: 12 April 2019; Accepted: 30 April 2019; Published: 8 May 2019

Abstract: Multilevel converters are widely considered to be the most suitable configurations for renewable energy sources. Their high-power quality, efficiency and performance make them interesting for PV applications. In low-power applications such as rooftop grid-connected PV systems, power converters with high efficiency and reliability are required. For this reason, multilevel converters based on parallel and cascaded configurations have been proposed and commercialized in the industry. Motivated by the features of multilevel converters based on cascaded configurations, this work presents the modulation and control of a rooftop single-phase grid-connected photovoltaic multilevel system. The configuration has a symmetrical cascade connection of two three-level T-type neutral point clamped power legs, which creates a five-level converter with two independent string connections. The proposed topology merges the benefits of multi-string PV and symmetrical cascade multilevel inverters. The switching operation principle, modulation technique and control scheme under an unbalanced power operation among the cell are addressed. Simulation and experimental validation results in a reduced-scale power single-phase converter prototype under variable conditions at different set points for both PV strings are presented. Finally, a comparative numerical analysis between other T-type configurations to highlight the advantages of the studied configuration is included.

**Keywords:** grid-connected photovoltaic systems; cascade multilevel converters; multistring converters; T-type converters

#### 1. Introduction

Rooftop photovoltaic (PV) energy conversion systems (less than 20 kW), have become a well-established technology in the industry. The most common configurations for single-phase grid-connected PV systems commercially found are the string, multistring and ac-module integrated topologies. Central and string inverters have been widely applied to manage and control PV energy systems [1]. Among the string topologies, the transformerless H5, H6, HERIC, neutral point clamped (NPC) and T-type NPC converters have been successfully commercialized [2]. In fact, multilevel inverters (MLI) are designed to produce a stepped voltage waveform by reducing the Total Harmonic Distortion (THD) and the voltage stress across semiconductor devices. Secondly, reduction of the

output filter size and power footprint also permit an important improvement in terms of costs, weight and efficiency [3]. These technical features have led to the massive adoption of MLI over the last thirty years for high-power medium voltage (MV) motor drive applications. In the last years, three-level neutral point clamped (3L-NPC) converters have been used for interfacing PV systems into the grid, where a higher PV incorporation has brought substantial concerns on power efficiency, power quality and grid code compliance [1] as well as power grid services [4].

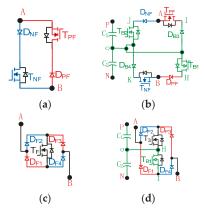

T-type neutral point clamped inverters (3L-TNPC), also known as neutral point piloted converters (3L-NPP), [5] have gained a wide presence in the industry sector due to several advantages as symmetrical loss distribution, higher overall efficiency, small footprints [6] and low harmonic injection in relation to the conventional 3L-NPC [7]. In fact, many manufactures such as Fuji, On Semiconductor, Mitsubishi and Semikron have commercial T-type legs used in central PV inverters and motor drive applications [8–10]. For the three-level inverter, based on the T-type leg, was presented thirty-five years ago for motor drives, with the bidirectional medium switch being realized with thyristors and improved with GTO-thyristors [11]. After some years, many configurations based on the well-known three-level T-type NPC leg can be found in the literature [12]. In [13] a five-level TNPC (5L-TNPC) was introduced, which corresponds to the parallel connection of two 3L-TNPC legs [14,15]. Furthermore, a variation of this configuration with reduced switches, also known as five-level hybrid T-type NPC (5L-HTNPC), was presented in the recent literature [16]. This topological variation is built with a 3L-TNPC leg and a two-level leg inverter, forming a five-stepped voltage waveform in the AC terminals.

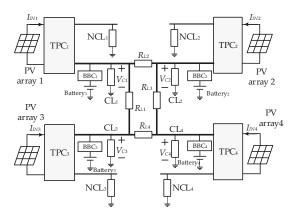

In the literature there are two main possibilities for increasing the number of levels in the power converter field, which is by increasing the internal DC capacitors connected to a single DC source or by connecting several converters in the series at the AC side, in which each converter has an independent DC source. Focusing on the second alternative, cascade MLI can be developed by using symmetrical or asymmetrical voltage levels and by using different type of topologies such as: Full H-Bridge, 3L-TNPC converters or by performing a hybrid configuration [17]. Note that symmetrical cascade configurations have had a more industrial presence as the case of Cascade H-Bridge (CHB) converters [3] due to modulation and control simplicity compared with asymmetrical configurations [18]. In fact, in [19] a symmetrical nine-level T-type converter (9L-TNPC) is presented for motor drive applications, which is based on the cascade connection of two 5L-TNPC converters. The same number of levels can be generated with advanced hybrid topologies as presented in [6,12].

Considering the advantages and features previously presented regarding the 3L-TNPC and symmetrical cascaded configurations, this paper described and validated the 5L-CTNPC topology for rooftop PV applications by using a cascaded connection of two 3L-TNPC legs which was firstly introduced in [20] as a cascade 3L-TNPC converter. Thus, the advantages of symmetrical cascade configurations with multistring inputs are merged. Each 3L-TNPC converter can interface a dedicated DC bus, and consequently two separate maximum power point tracking (MPPT) algorithms are allowed to obtain the maximum power of each PV string. Note that the PV string of each module can be sized to handle half the entire PV string in the conventional 3L-TNPC converter, providing better MPPT efficiency since less modules are combined in a series per string. The main contribution of this paper is the experimental validation of a simplified control scheme to alleviate the power unbalancing mismatch between 3L-TNPC modules and to compensate capacitor voltage variations per each converter, which was presented earlier in [20]. Furthermore, a brief comparison between five-level voltage waveform converters based on the conventional 3L-TNPC is performed as a second contribution in terms of the main electrical features.

The rest of the document is organized as follows. In Section 2, a hardware description of the proposed converter, switching states and implemented modulation is presented. In Section 3, a simple stationary reference-frame voltage-oriented control and a voltage control loop to compensate a possible power unbalance operation are included. Then, in Section 4, simulation results and experimental verification of the proposed multilevel converter and its control system behavior are

added. Furthermore, a brief comparison with the 5L-TNPC and 5L-HTNPC is performed to highlight the main advantages of the proposed configuration. Finally, in Section 5, the conclusions of the paper summarize the work done.

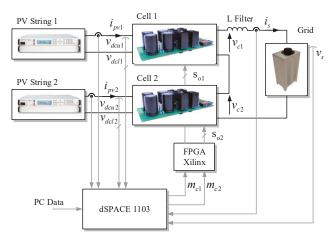

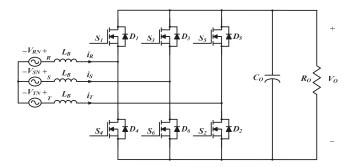

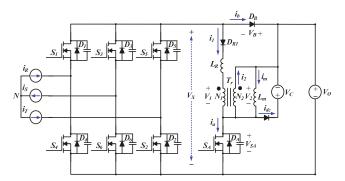

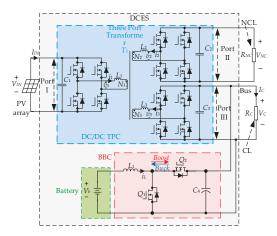

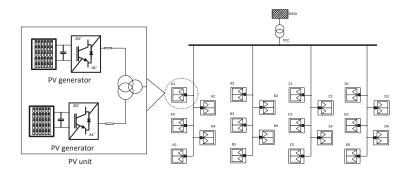

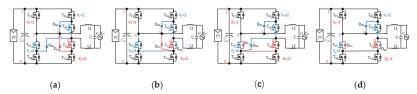

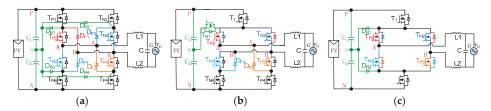

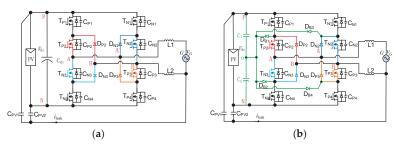

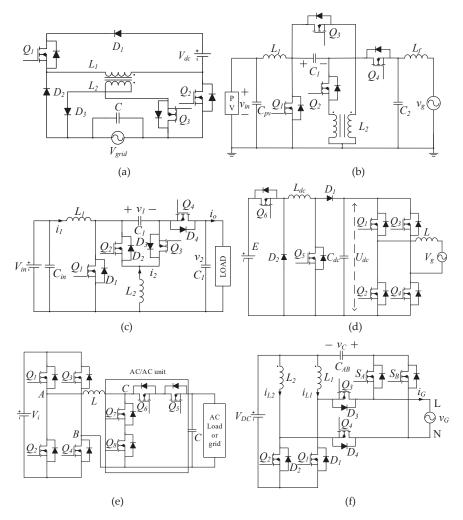

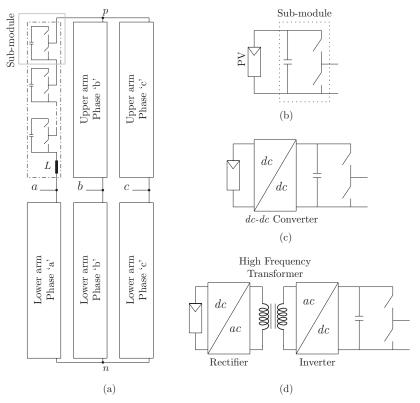

#### 2. The 5L-CTNPC Converter Topology

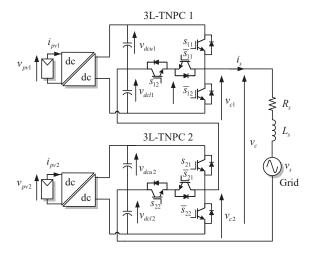

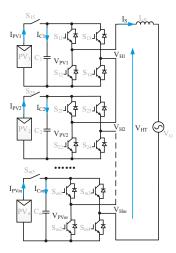

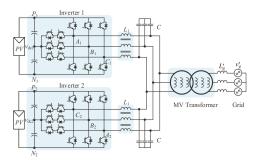

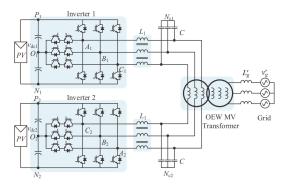

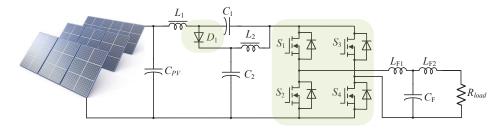

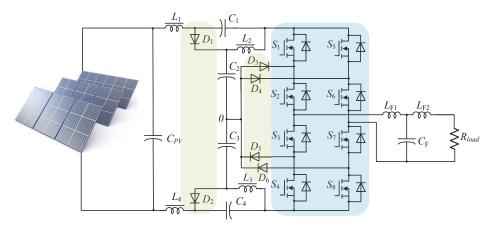

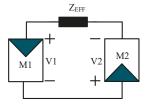

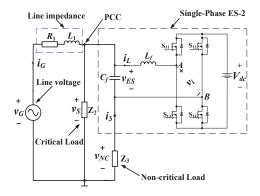

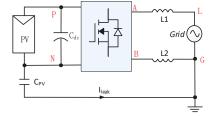

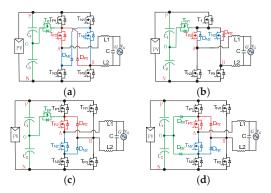

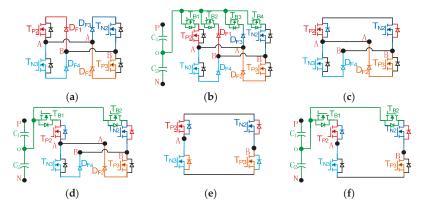

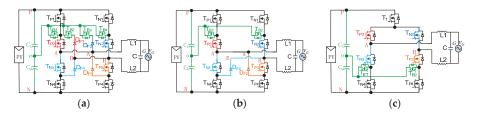

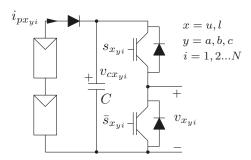

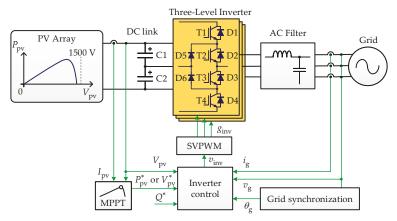

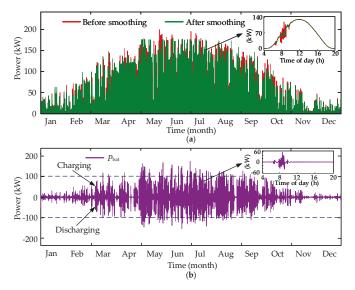

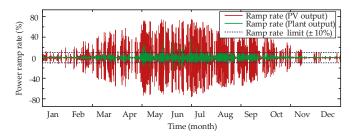

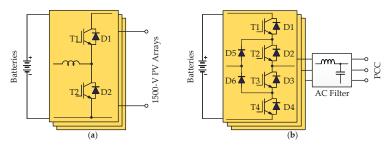

The power topology of the analyzed cascade 5L-CTNPC for a rooftop grid-connected PV system is depicted in Figure 1. The configuration is composed of a series connection of two 3L-TNPC legs, where each of them is built with two conventional IGBTs and one bidirectional switch. This bidirectional switch could be formed either by two conventional IGBTs in common-emitter or by a common-collector and reverse blocking IGBT connection. Actually, a classical IGBT semiconductor structure could be replaced by a reverse blocking MOSFETs for a high-voltage [21] and high-switching frequency operation [22]. Although more than two cells in a series connection are conceptually feasible, for the sake of simplicity, two-cell 3L-TNPC converters have been introduced as a proof-of-concept applied to conventional string rooftop PV applications.

Figure 1. Proposed 5L-CTNPC power topology.

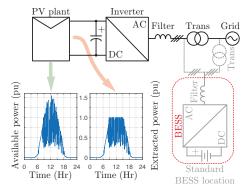

Each 3L-TNPC leg operates as a string inverter connected to a single potential-induced degradation converter which is fed by one PV string. This potential-induced degradation stage can be designed to boost the DC voltage and perform the MPPT. Furthermore, it could be isolated [23] to avoid leakage currents due to the PV aluminium metallic frame grounded [1]. To reduce leakage currents paths and avoid high-frequency transformers there are three successful options well-documented in the literature: Changing the modulation stage to avoid switched common mode [16], by reducing surface conductivity of PV modules to avoid potential-induced degradation (PID) and by including extra switches between the PV array and the inverter, also well-known as transformerless inverters [24]. Although, a potential-induced degradation stage is desired to provide an independent DC voltage control, in this work, the validation of the proposed configuration does not integrate a potential-induced degradation stage, giving place to the worst case scenario under study where the MPPT control is fulfilled directly from each 3L-TNPC power cell, instead of using a high frequency galvanic isolated converter with its appropriate MPPT control. Thus, the overall control loops are more challenging since the voltage fluctuations in the PV panel is directly presented in the DC-side of each 3L-TNPC module, i.e.,  $v_{dck} = v_{pvk}$ , where  $k = \{1,2\}$  is given by the number of cell. Furthermore, in order to extract the maximum power from the PV panels, an integration of an external

MPPT algorithm is required so as to define the appropriate DC voltage reference in each cell. Note that the proposed topology is modeled without affecting the basic control objectives.

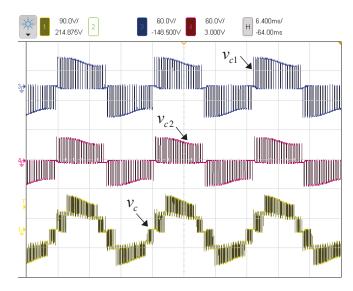

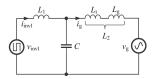

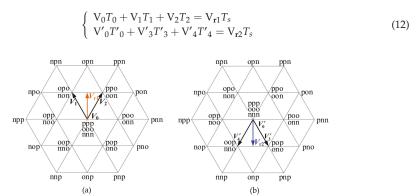

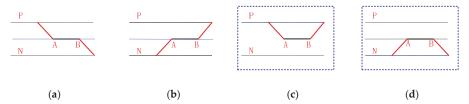

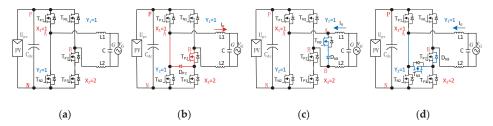

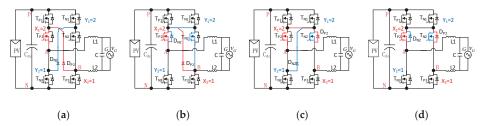

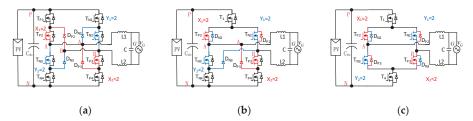

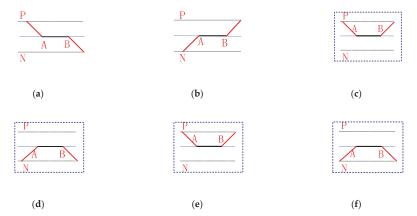

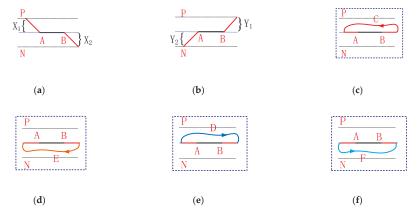

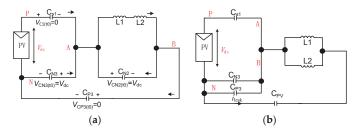

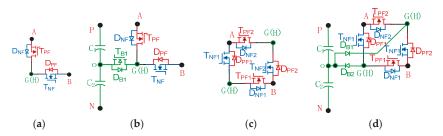

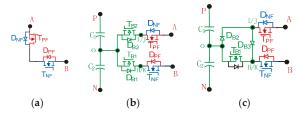

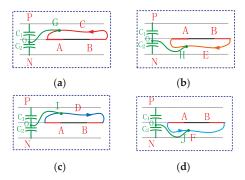

#### 2.1. Fundamental Principle of the 5L-CTNPC

The 3L-TNPC provides three-output voltage levels:  $v_{dck}/2$ , 0 and  $-v_{dck}/2$ , where k is the cell or module number. These voltage steps are generated by connecting the AC terminals to the positive, neutral and negative pole of the DC-link terminals. Although, the 3L-TNPC configuration gives rise to four switching states, in order to avoid a short-circuit to the DC side there are only three of them possible. The cascade connection of two 3L-TNPC cells permits the generation of five voltage steps, where the zero level is combined into just one at the AC converter output voltage  $v_c$ . According to the switching states presented in Table 1, the output voltage in the 5L-CTNPC can be modeled as:

$$v_c = \underbrace{(S_{11} + S_{12} - 1)\frac{v_{dc1}}{2}}_{v_{c1}} + \underbrace{(S_{21} + S_{22} - 1)\frac{v_{dc2}}{2}}_{v_{c2}},\tag{1}$$

where  $v_c$  is the addition of the converter voltages of both modules,  $S_{1k}$  and  $S_{2k}$  are the switching states of the k-th 3L-TNPC unit and  $v_{dck}/2$  is the total DC-link voltage of each cell. Furthermore, the dynamic model of the AC current in terms of the output voltage is governed by the next expression:

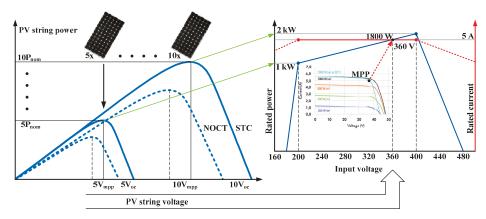

$$v_c = i_s R_s + L_s \frac{di_s}{dt} + v_s, \tag{2}$$

with  $v_s$  as the grid voltage measured at the point of common coupling (PCC),  $i_s$  as the grid current,  $L_s$  the grid filter inductance and  $R_s$  is the filter resistance included for modeling purposes. According to Table 1, the switching states are able to generate nine voltage levels in the output voltage  $v_c$  where each state has an associated voltage level in function to the DC-link  $v_{dc1}$  and  $v_{dc2}$ . Note that in this rooftop PV application both strings will be considered to work with similar DC-link voltages, i.e.,  $v_{dc1} \approx v_{dc2} = v_{dc}$ . By doing this, the output voltage  $v_c$  can be reduced just to  $\pm v_{dc}$ ,  $\pm v_{dc}/2$  and 0. This assumption leads to five switching states with similar output voltage steps between two consecutive levels [20]. The redundant switching states will be used to balance the voltage in the DC-link capacitors by adjusting the power mismatch between the converter cells. The computed peak amplitude of the converter output voltage  $\hat{v}_c$  is equal to  $v_{pv1}/2 + v_{pv2}/2$ , i.e., each power cell has a DC-link equal to the maximum level of the converter voltage. Therefore, for a proper grid current regulation, each PV string must be designed to satisfy  $v_{pv1} \approx v_{pv2} > v_s$ . In fact, this aspect is a practical advantage of cascaded configurations, since the overall DC-link voltage of the central configuration is split among power cells, thus reducing the string size.

| State       | S <sub>11</sub> | S <sub>12</sub> | S <sub>21</sub> | S <sub>22</sub> | $v_c$                     |

|-------------|-----------------|-----------------|-----------------|-----------------|---------------------------|

| 1           | 1               | 1               | 1               | 1               | $v_{dc1}/2 + v_{dc2}/2$   |

| 2 3         | 1<br>0          | 1<br>1          | 0<br>1          | 1<br>1          | $v_{dc1}/2$ $v_{dc2}/2$   |

| 4<br>5<br>6 | 1<br>0<br>0     | 1<br>0<br>1     | 0<br>1<br>0     | 0<br>1<br>1     | 0                         |

| 7<br>8      | 0               | 1<br>0          | 0               | 0<br>1          | $-v_{dc1}/2 \ -v_{dc2}/2$ |

| 9           | 0               | 0               | 0               | 0               | $-v_{dc1}/2 - v_{dc2}/2$  |

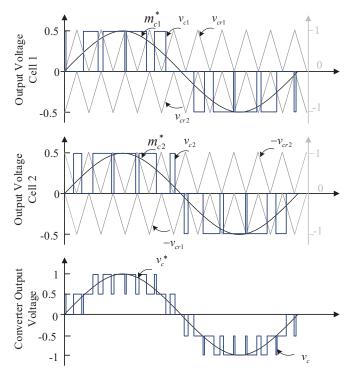

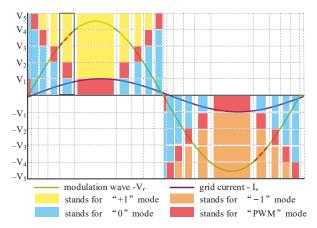

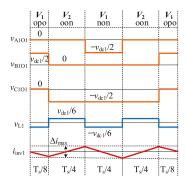

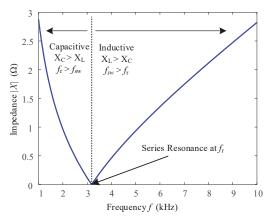

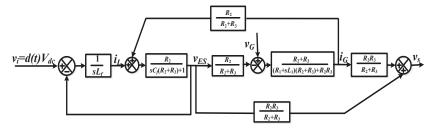

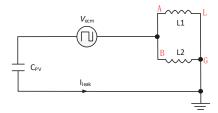

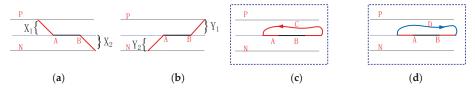

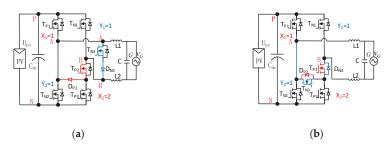

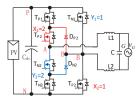

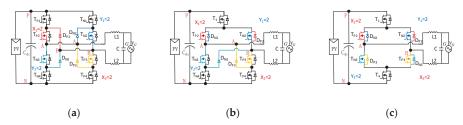

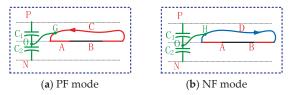

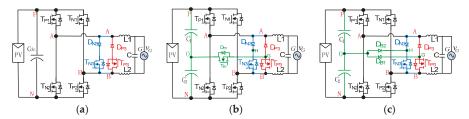

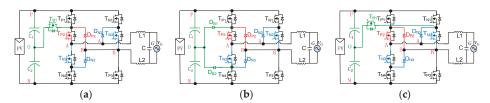

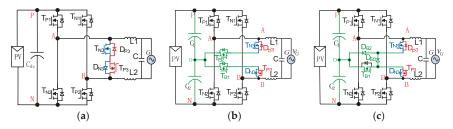

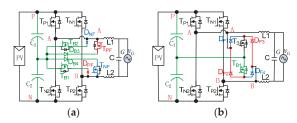

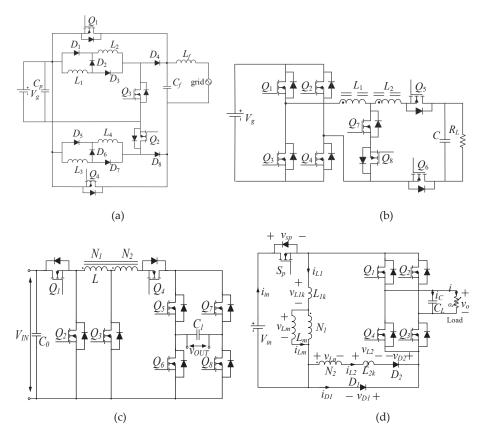

#### 2.2. Proposed Hybrid LS-PWM and PS-PWM Modulation Scheme for 5L-CTNPC Converter

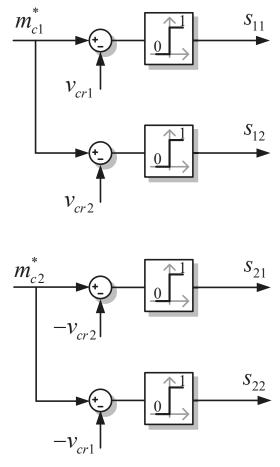

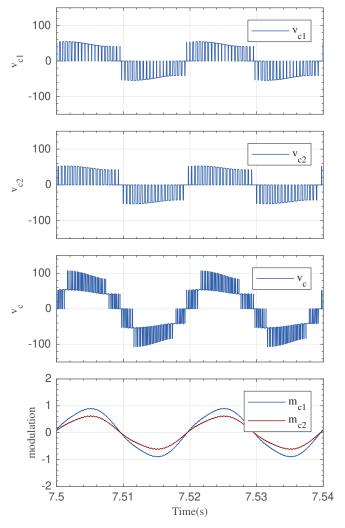

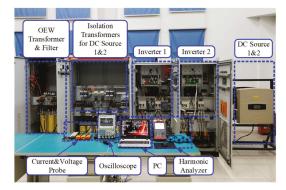

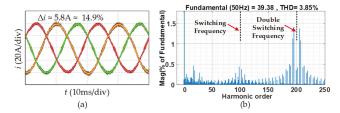

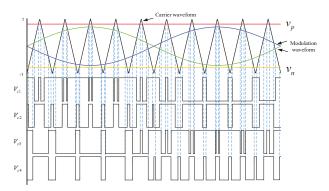

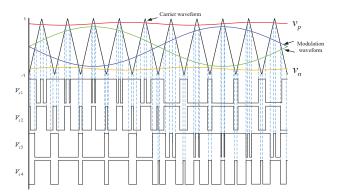

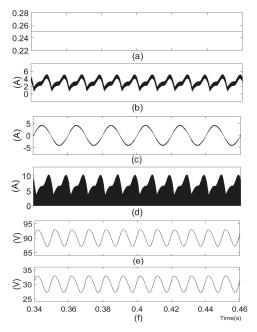

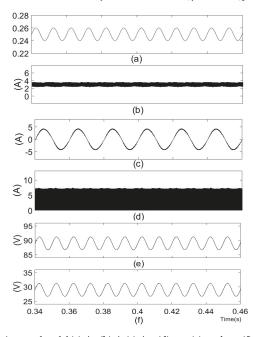

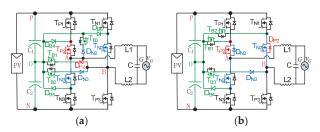

The proposed modulation scheme for the 5L-CTNPC is based on two well-known carriers based on the sinusoidal PWM methods. The first is the Sinusoidal Level-Shifted Pulse Width Modulator (LS-PWM), used in 3L-NPC three-phase converters [25] and the single 3L-TNPC legs [20]. This modulation strategy requires two carrier signals in phase, to generate the three voltage levels in the output terminals of each cell. One carrier signal has a positive polarity (0 to 1) and the other has a negative polarity (-1 to 0). Furthermore, the LS-PWM is merged with the Sinusoidal Phase-Shifted PWM (PS-PWM) conventionally used in cascaded H-bridge power converters [26]. In the PS-PWM modulation, a phase shift between the carrier signals of each series connected to a power cell is introduced to increase the number of voltage levels, giving rise to a five-level stepped voltage waveform. The operation principle of this hybrid modulation technique is illustrated in Figure 2, where  $m_{ck}^*$  and  $v_{ck}$  are the modulation signal and the output voltage in the k-th cell, respectively. Note that each cell uses two carrier signals defined as  $v_{cr1}$  and  $v_{cr2}$ . Thus, the stacked connection of both cells creates the converter voltage  $v_c$ , which is commanded by its reference  $v_c^*$ . The combination of both methods is simpler in respect to the space vector modulation (SVM) [27]. Finally, the implementation of this modulation technique is depicted in the block diagram of Figure 3, where simple comparators and two carrier signals are required to implement the proposed technique.

Figure 2. Proposed modulation scheme for 5L-CTNPC based on the hybrid LS-PWM and PS-PWM.

**Figure 3.** Straightforward implementation of hybrid LS-PWM and PS-PWM modulation for a 5L-CTNPC converter.

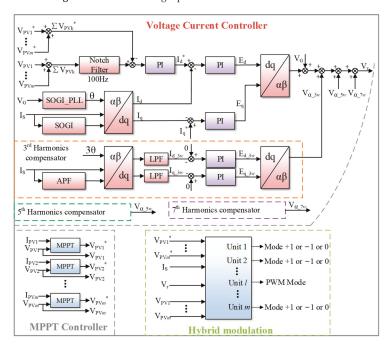

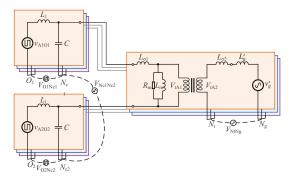

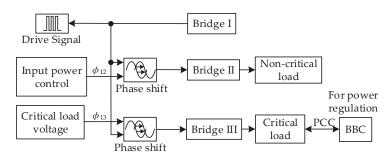

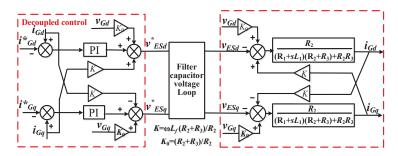

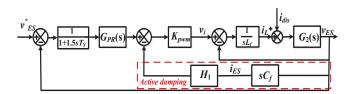

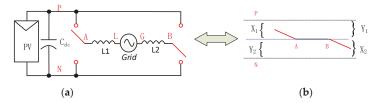

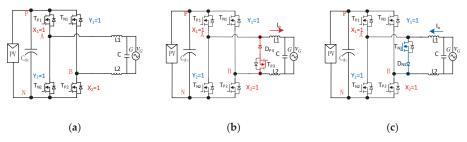

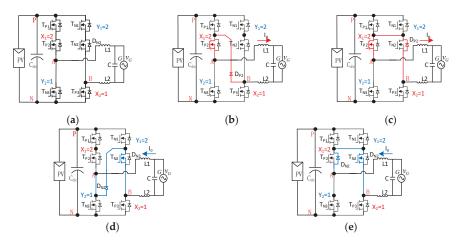

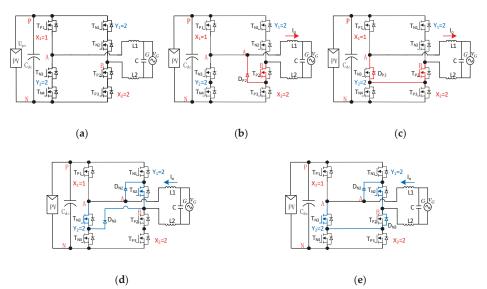

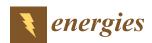

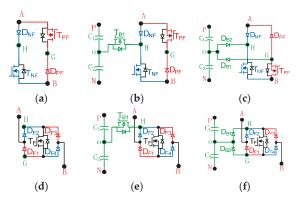

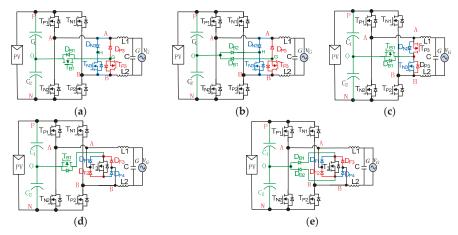

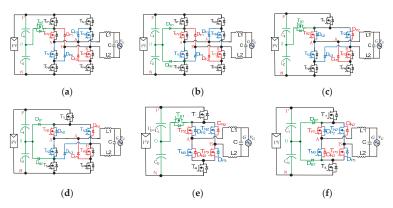

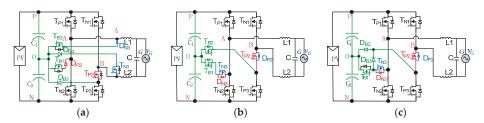

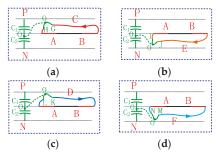

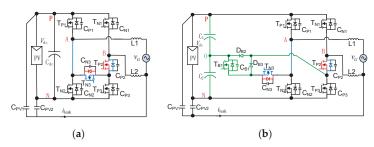

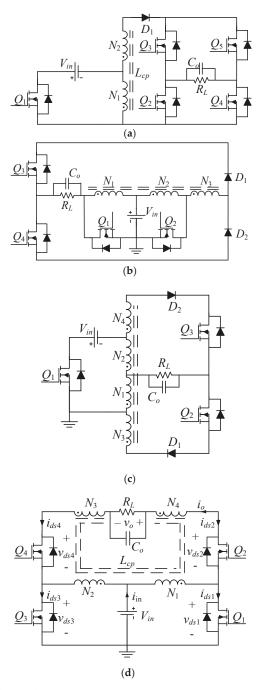

#### 3. Overall Control Strategy

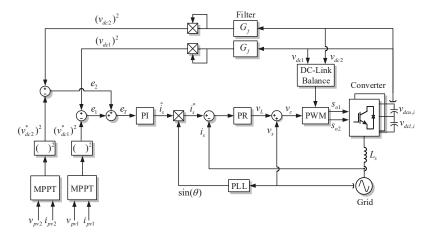

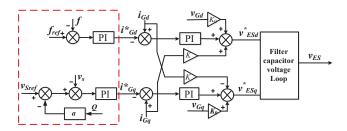

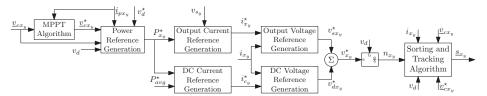

In this work three decoupled control stages are programmed to regulate the current injected into the grid, the power generated by each PV string and the power mismatch between cells. The first one is the MPPT, which set the DC-link voltage reference for both cells and is optionally included to extract the maximum power from the PV panels in case of direct connection to the 3L-TNPC modules. This control stage is complemented with the total DC-link control loop based on the energy interchange between the power cells. The second control stage is the single-phase voltage-oriented control loop, which has an embedded stationary current control loop implemented with Proportional Multi-Resonant (PMR) controllers. The last control loop is in charge of attenuating the DC-link voltage differences to compensate power mismatch issues among each cell of the converter. The overall control scheme is presented in Figure 4, where  $v_{pvk}$ ,  $i_{pvk}$ ,  $v_{dck}$  and  $s_{ok}$  are the PV voltage, PV current, DC-link voltage measurement and gating pulses of each k-th module.

Figure 4. Single-phase voltage-oriented control strategy for the proposed 5L-CTNPC converter.

#### 3.1. MPPT and Outer DC-Link Controller

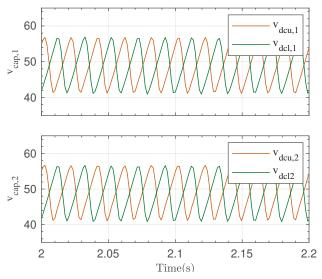

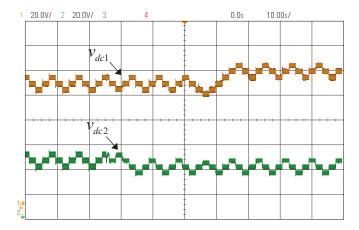

The well-known Perturb and Observe (P&O) MPPT routine has been implemented for simplicity in this application. As the analyzed power configuration features two separate DC-links or PV string connections, two independent MPPT algorithms are required to obtain its full power operation. The MPPT routines compute the voltage reference for each DC-link  $v_{dc1}^*$  and  $v_{dc2}^*$ , as illustrated in Figure 4. Then, the DC-link control loop is designed to manage the total energy of the system through the difference between the voltage reference and the voltage measured, i.e.,  $e_T = e_1 + e_2$ . This total energy is governed by using a proportional-integral (PI) controller, which generates the amplitude of the injected grid current  $\hat{i}_s$ . Note that the DC-link voltage measurements are acquired and processed with a notch filter  $G_f$  to eliminate the second harmonic ripple  $2\omega_s$  presented in the DC-link capacitors by the rectification of a single-phase grid voltage. In fact, not filtering this harmonic voltage component will generate an undesired third harmonic  $3\omega_s$  component in the grid current reference. The MPPT parameters such as voltage step  $\Delta v_{pv}$  and time period  $T_k$  are designed according with conventional commercial values. In experimental results, the voltage step  $\Delta v_{pv} = 6$  V and the time period  $T_k = 2$  s, whereas in simulation results,  $\Delta v_{pv} = 6$  V and the time period is ten times smaller than the experimental results. Furthermore, the DC-link compensator has been designed by using a DC-link control bandwidth of 14Hz. Major details about the outer control design can be found in [20].

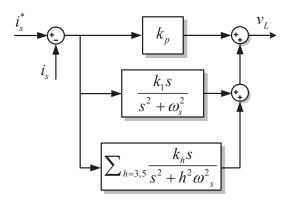

#### 3.2. PMR Current Control Scheme

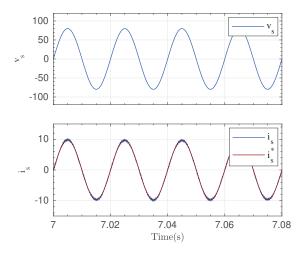

The grid current reference is generated by multiplying the amplitude of the injected grid current  $\hat{i}_s$  with a unitary sinusoidal signal synchronized to the grid voltage. To avoid voltage measurement noise and low frequency harmonic components, a second order generalized integrator (SOGI) with a synchronous reference frame phase lock loop (SRF-PLL) is implemented to set the synchronous angle. Then, the grid current reference  $i_s^*$  is compared with the current measured value  $i_s$ , giving rise to a current error which is regulated by using a PMR control scheme. The structure of the implemented controller is included in Figure 5 and expressed as following:

$$C_i(s) = k_p + \sum_{h=1,3,5} \frac{2k_{ih}s}{s^2 + h^2\omega_s^2}$$

(3)

where  $k_p$  is the proportional gain and  $k_{ih}$  is the resonant gain at each selected h-th harmonic. Note that the above resonant controllers have been considered to achieve selective harmonic impedance enhancement at 3st and 5th components. The resonant frequency at  $\omega_s$  is equal to the grid frequency,

hence the compensator  $C_i(s)$  has infinite gain at  $\omega_s$ , providing perfect sinusoidal tracking with zero steady-state error. The PMR compensator in Figure 5 has been designed by a simple pole placement with a crossover frequency of 270 Hz, which corresponds to a rate twenty times faster than the outer control loop. This control scheme is currently adopted for grid-connected PV systems where the grid voltage has important low-frequency harmonics [28].

Figure 5. Stationary current control loop implemented with PMR controllers.

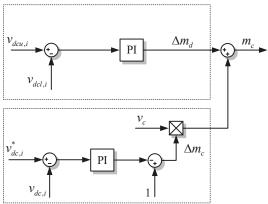

The output of the current control loop set the voltage reference across the grid inductor  $v_L^*$ . Neglecting the voltage drop in the resistance  $R_s$ , the converter voltage is equal to  $v_c = v_L + v_s$ . Commonly, the obtained inverter voltage reference  $v_c$  would be directly connected to the modulation block stage to generate the firing pulses in each semiconductor device. Since the current  $i_s$  is the same for both series connected 3L-TNPC converters, the voltage references for each power unit must be modified in advance to allow different power inputs. This important control requirement is performed by including an internal DC-link voltage balance stage, which enables the voltage balancing between capacitors in the DC-link and the power unbalance operation between both cells. In fact, the voltage balancing operation is performed by the DC-link voltage references  $v_{dc1}^*$  and  $v_{dc2}^*$  naturally delivered by the MPPT algorithm.

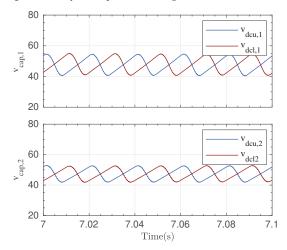

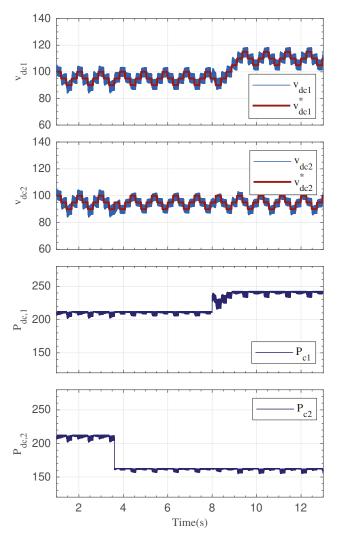

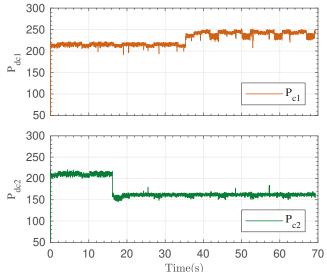

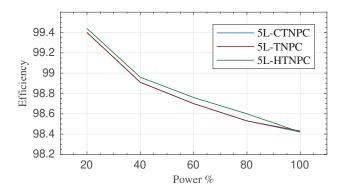

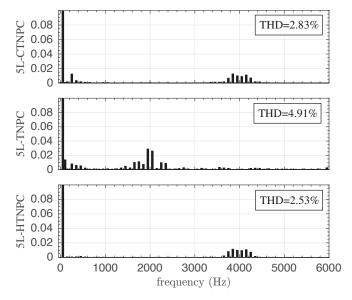

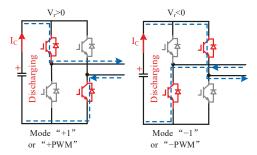

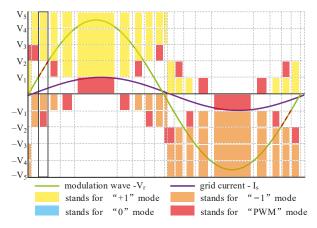

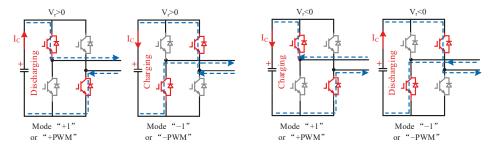

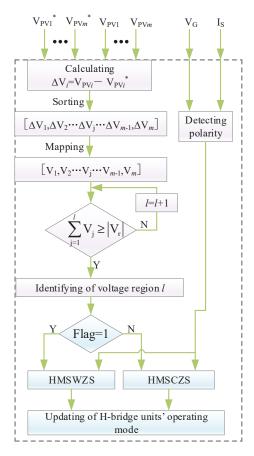

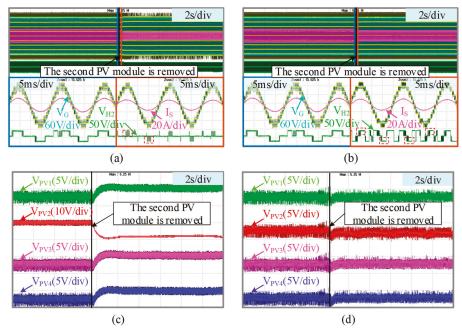

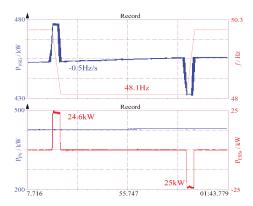

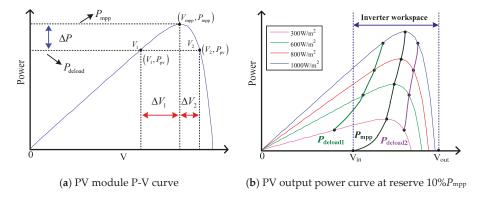

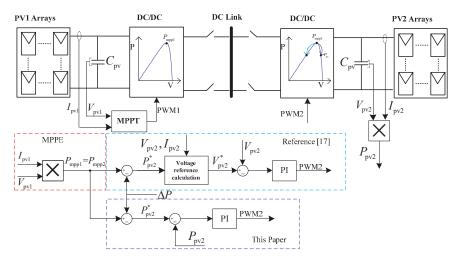

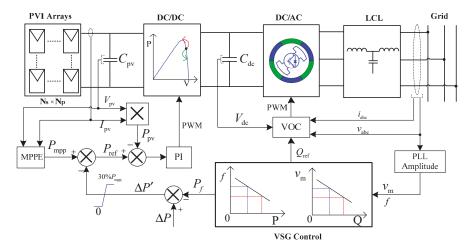

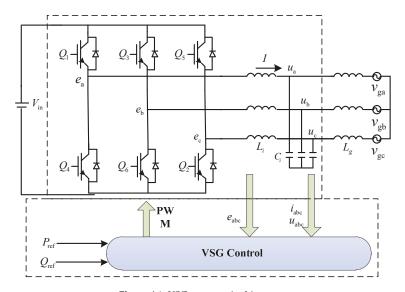

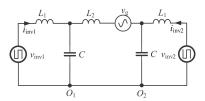

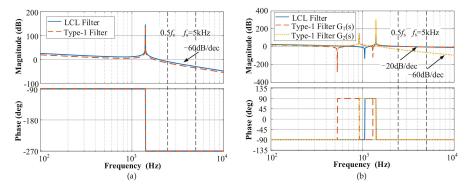

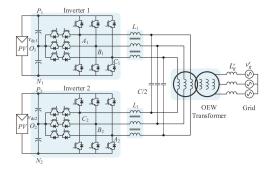

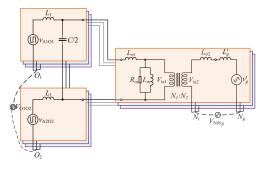

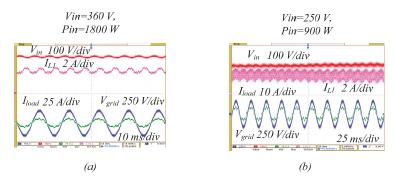

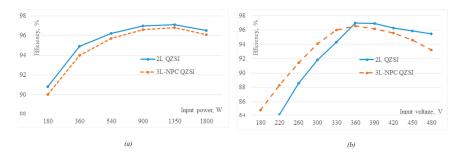

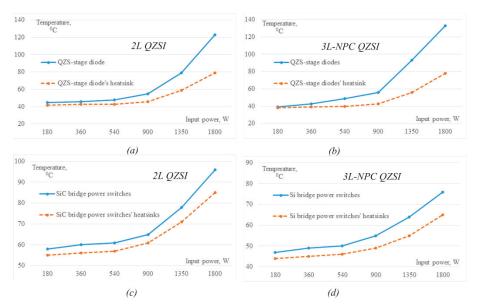

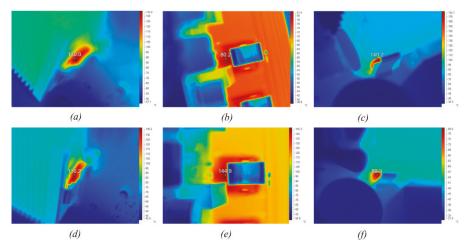

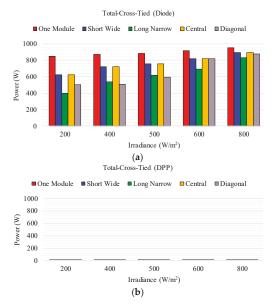

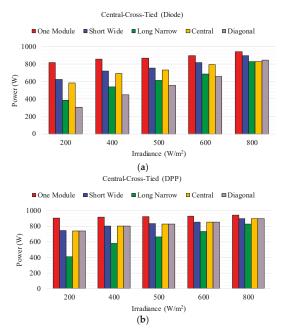

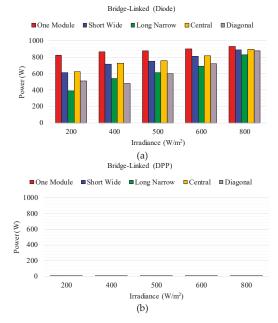

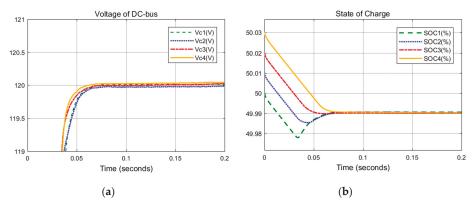

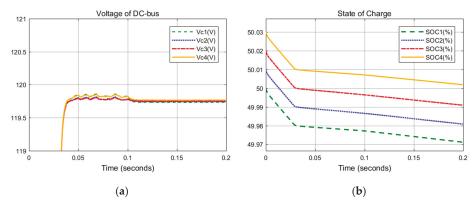

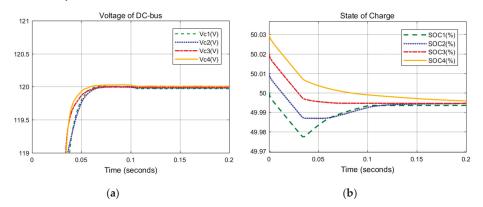

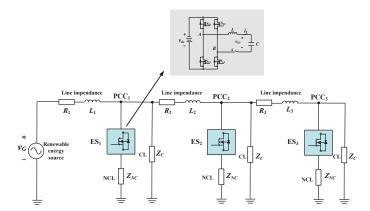

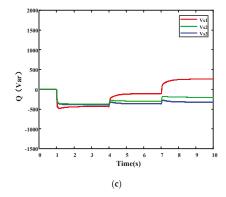

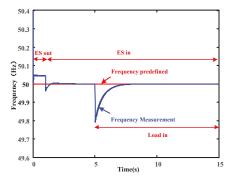

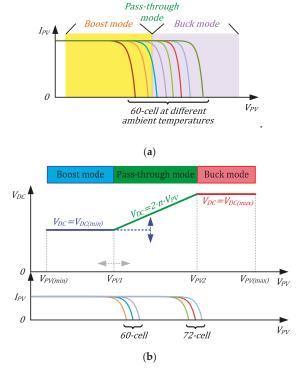

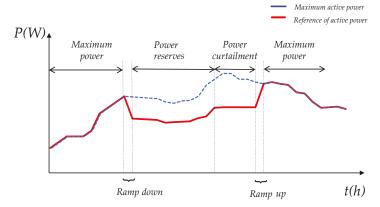

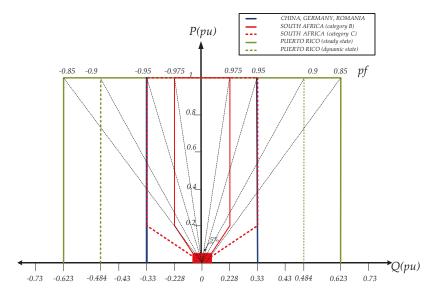

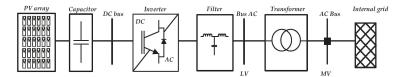

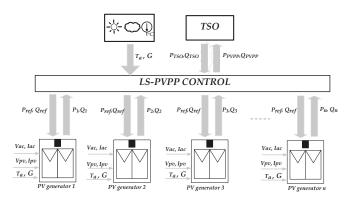

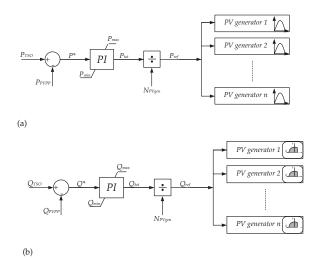

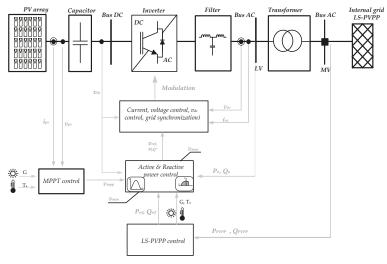

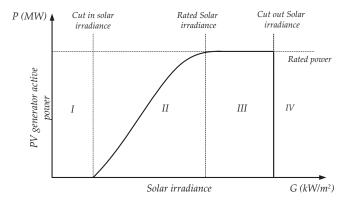

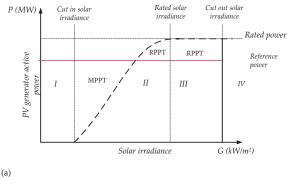

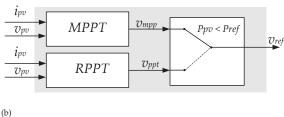

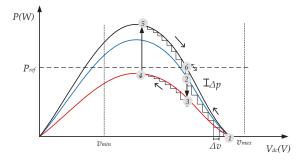

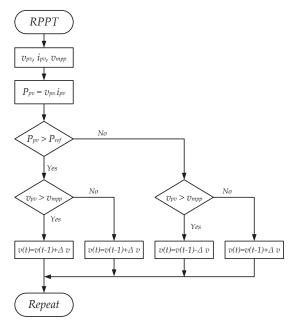

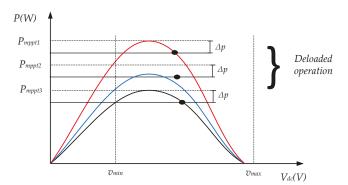

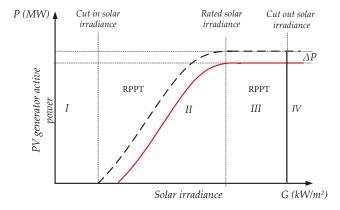

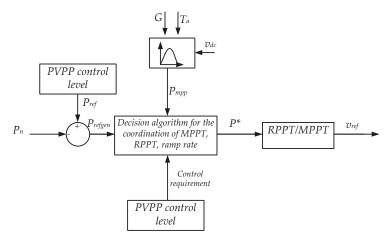

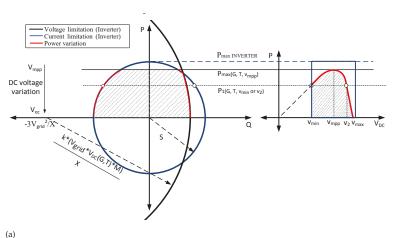

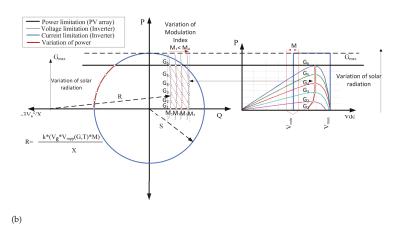

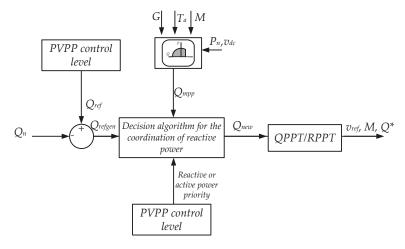

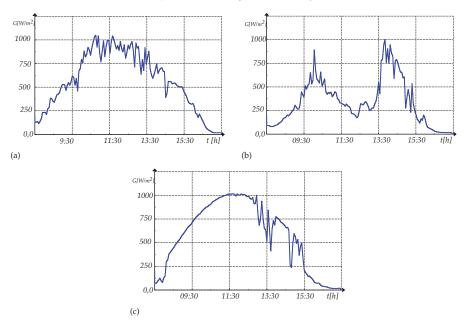

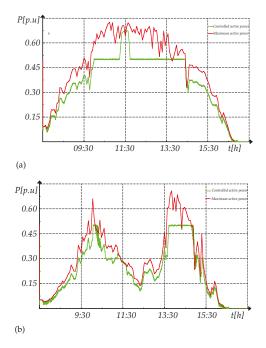

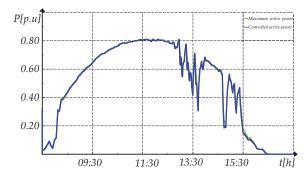

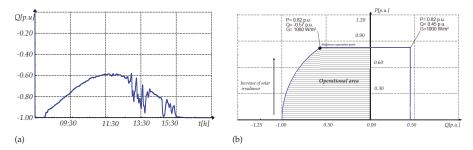

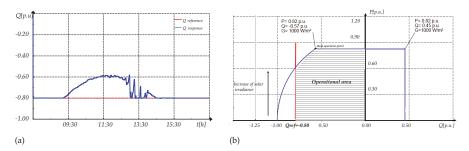

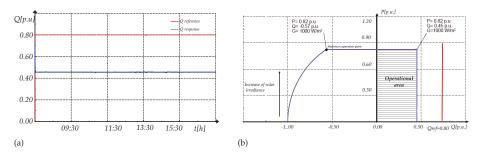

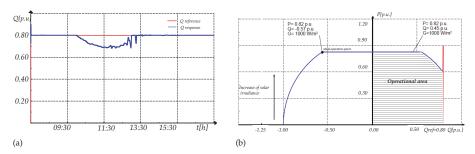

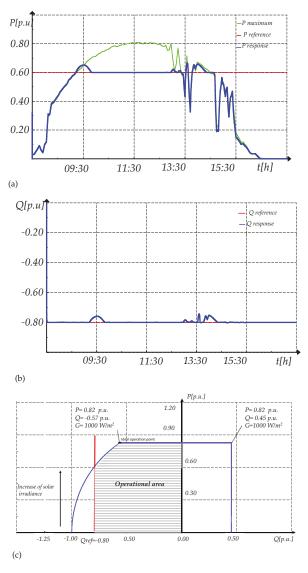

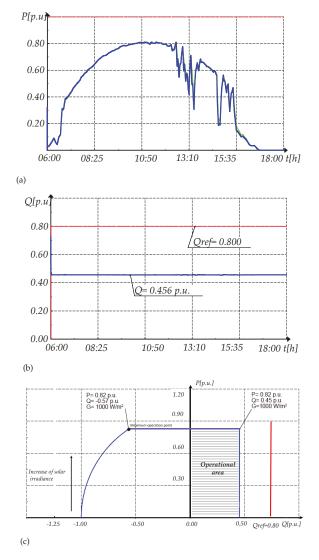

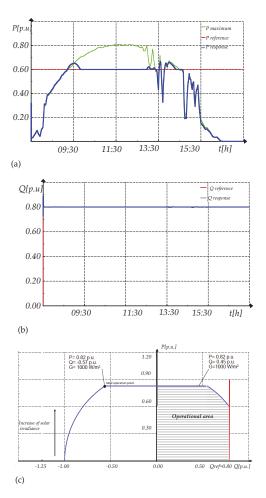

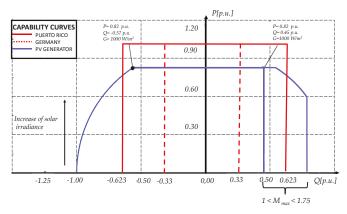

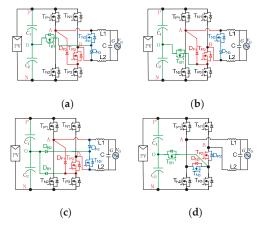

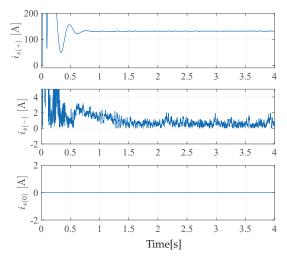

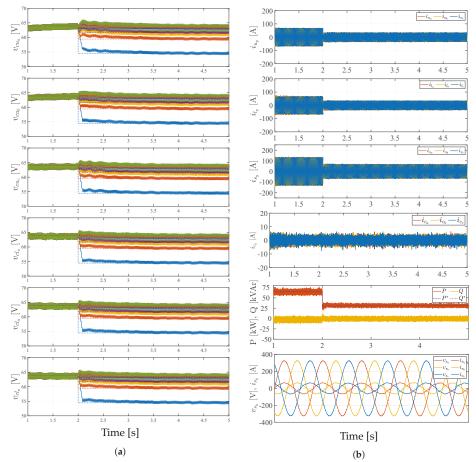

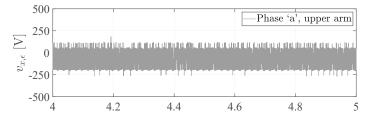

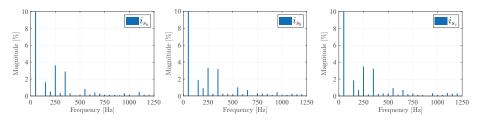

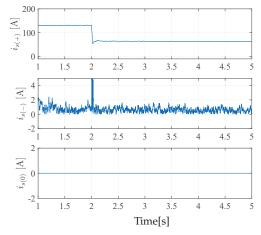

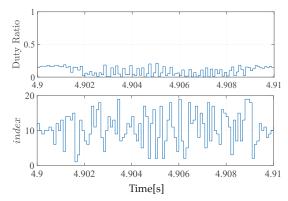

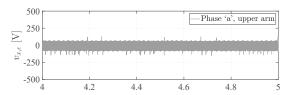

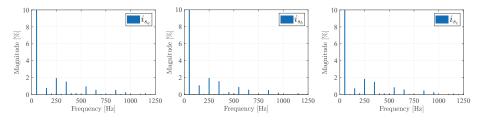

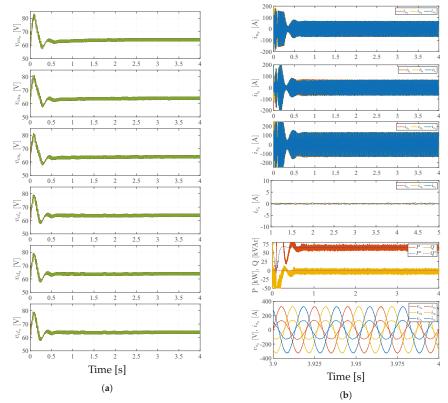

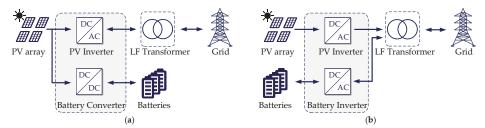

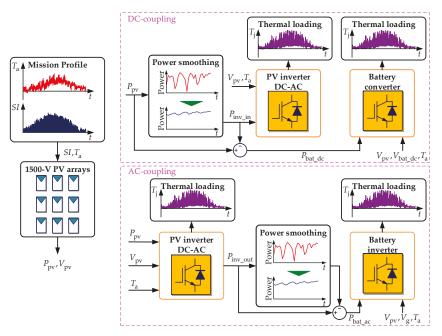

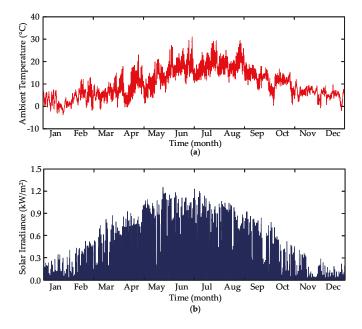

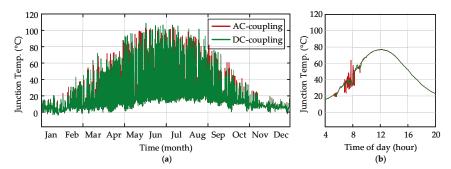

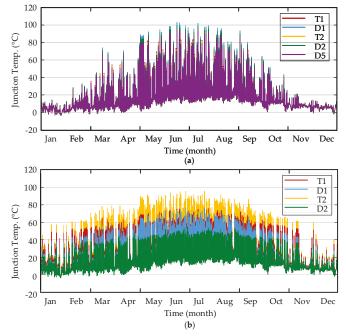

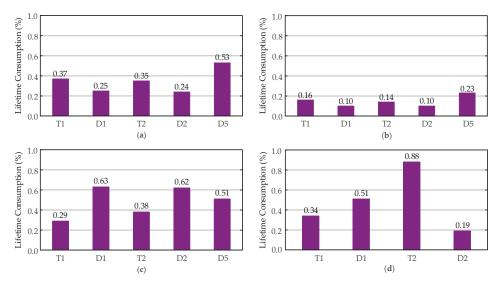

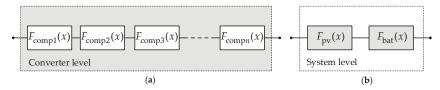

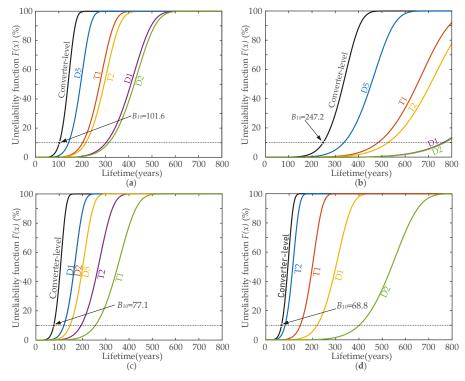

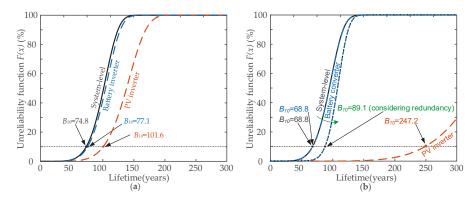

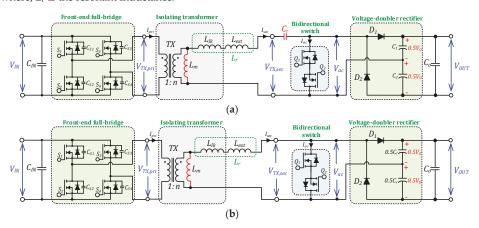

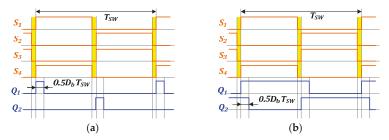

#### 3.3. Voltage Balancing Control and Power Balance Scheme