# Industrial and Technological Applications of Power Electronics Systems

Edited by Ryszard Strzelecki, Galina Demidova and Dmitri Vinnikov Printed Edition of the Special Issue Published in *Energies*

www.mdpi.com/journal/energies

# Industrial and Technological Applications of Power Electronics Systems

# Industrial and Technological Applications of Power Electronics Systems

Editors

Ryszard Strzelecki Galina Demidova Dmitri Vinnikov

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

*Editors* Ryszard Strzelecki Gdansk University of Technology Poland

Galina Demidova ITMO University, Russia Dmitri Vinnikov Tallinn University of Technology Estonia

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Energies* (ISSN 1996-1073) (available at: https://www.mdpi.com/journal/energies/special\_issues/Applications\_of\_Power\_Electronics\_Systems).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-0822-1 (Hbk) ISBN 978-3-0365-0823-8 (PDF)

© 2021 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## Contents

| About the Editors                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "Industrial and Technological Applications of Power Electronics Systems" ix                                                                                                       |

| Hamidreza Heidari, Anton Rassõlkin, Mohammad Hosein Holakooie, Toomas Vaimann,<br>Ants Kallaste, Anouar Belahcen, Dmitry V. Lukichev                                                         |

| A Parallel Estimation System of Stator Resistance and Rotor Speed for Active Disturbance                                                                                                     |

| Rejection Control of Six-Phase Induction MotorReprinted from: Energies 2020, 13, 1121, doi:10.3390/en130511211                                                                               |

| Anton Dianov and Alecksey Anuchin                                                                                                                                                            |

| Adaptive Maximum Torque per Ampere Control of Sensorless Permanent Magnet Motor DrivesReprinted from: Energies 2020, 13, 5071, doi:10.3390/en1319507119                                      |

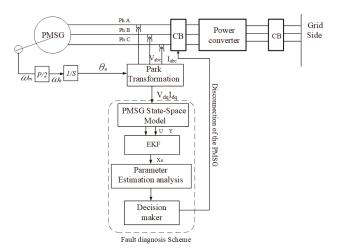

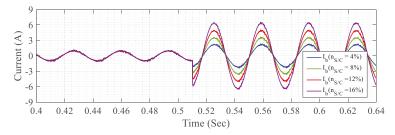

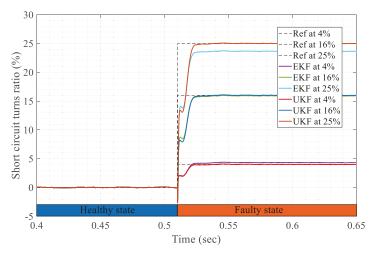

| Waseem El Sayed, Mostafa Abd El Geliel and Ahmed Lotfy                                                                                                                                       |

| Fault Diagnosis of PMSG Stator Inter-Turn Fault Using Extended Kalman Filter and Unscented                                                                                                   |

| Kalman Filter<br>Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 2972, doi:10.3390/en13112972                                                                                      |

| <b>Zbigniew Waradzyn, Robert Stala, Andrzej Mondzik, Aleksander Skała and Adam Penczek</b><br>GaN-Based DC-DC Resonant Boost Converter with Very High Efficiency and Voltage<br>Gain Control |

| Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 6403, doi:10.3390/en13236403                                                                                                       |

| Adam Kawa and Robert Stala<br>SiC-Based Bidirectional Multilevel High-Voltage Gain Switched-Capacitor Resonant Converter                                                                     |

| with Improved Efficiency<br>Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 2445, doi:10.3390/en13102445                                                                           |

| Robert Stala, Zbigniew Waradzyn and Szymon Folmer                                                                                                                                            |

| DC-DC High-Voltage-Gain Converters with Low Count of Switches and Common GroundReprinted from: Energies 2020, 13, 5657, doi:10.3390/en1321565795                                             |

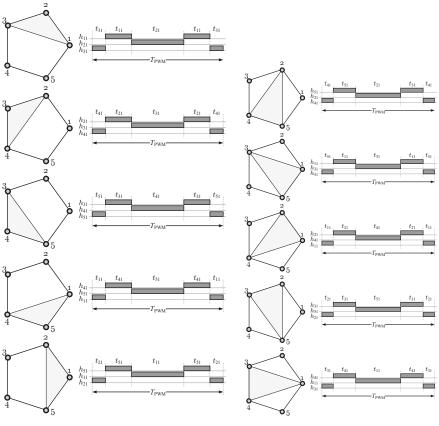

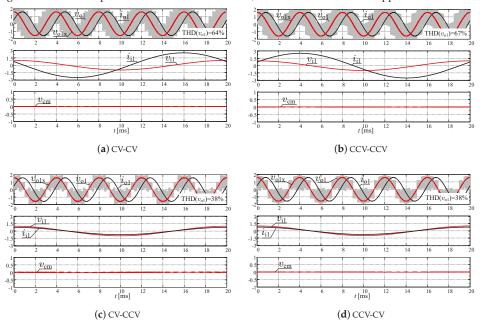

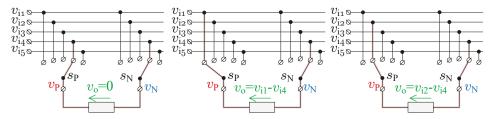

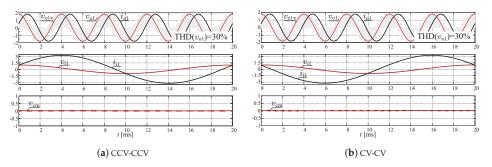

| Pawel Szczepankowski, Natalia Strzelecka and Enrique Romero-Cadaval<br>A New Approach to the PWM Modulation for the Multiphase Matrix Converters Supplying                                   |

| Loads with Open-End Winding                                                                                                                                                                  |

| Reprinted from: <i>Energies</i> <b>2021</b> , <i>14</i> , 466, doi:10.3390/en14020466                                                                                                        |

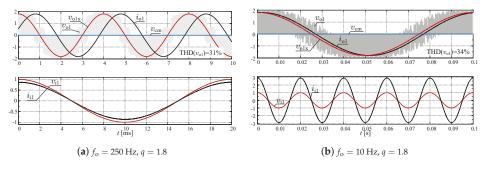

| Marcin Steczek, Włodzimierz Jefimowski and Adam Szelag<br>Application of Grasshopper Optimization Algorithm for Selective Harmonics Elimination in                                           |

| Low-Frequency Voltage Source Inverter                                                                                                                                                        |

| Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 6426, doi:10.3390/en13236426                                                                                                       |

| Krzysztof Jakub Szwarc, Pawel Szczepankowski, Janusz Nieznański, Cezary Swinarski,<br>Alexander Usoltsev and Ryszard Strzelecki                                                              |

| Hybrid Modulation for Modular Voltage Source Inverters with Coupled Reactors                                                                                                                 |

| Reprinted from: <i>Energies</i> , 2020, 4450, doi:10.3390/en13174450                                                                                                                         |

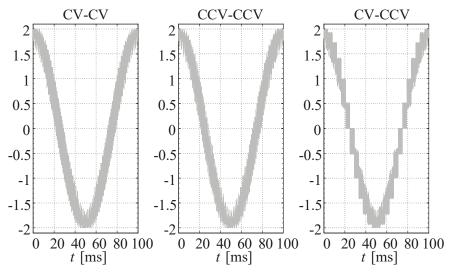

| Pawel Szczepankowski, Jaroslaw Luszcz, Alexander Usoltsev, Natalia Strzelecka and         Enrique Romero-Cadaval         The Conceptual Research over Low-Switching Modulation Strategy for Matrix Converters with         the Coupled Reactors         Reprinted from: Energies 2021, 14, 675, doi:10.3390/en14030675                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jerzy Szymanski, Marta Zurek-Mortka, Daniel Wojciechowski and Nikolai Poliakov<br>Unidirectional DC/DC Converter with Voltage Inverter for Fast Charging of Electric Vehicle<br>Batteries<br>Reprinted from: <i>Energies</i> 2020, 13, 4791, doi:10.3390/en13184791                                                                               |

| Wojciech Sleszynski, Artur Cichowski and Piotr Mysiak         Suppression of Supply Current Harmonics of 18-Pulse Diode Rectifier by Series Active Power         Filter with LC Coupling         Reprinted from: Energies 2020, 13, 6060, doi:10.3390/en13226060                                                                                  |

| <b>Andrzej Szromba</b><br>The Unified Power Quality Conditioner Control Method Based on the Equivalent Conductance<br>Signals of the Compensated Load<br>Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 6298, doi:10.3390/en13236298                                                                                                   |

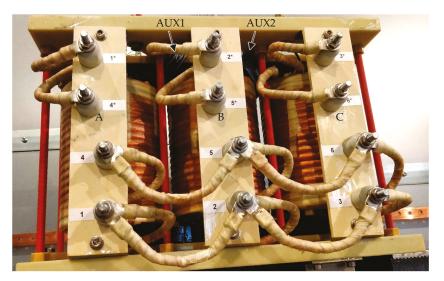

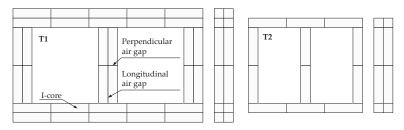

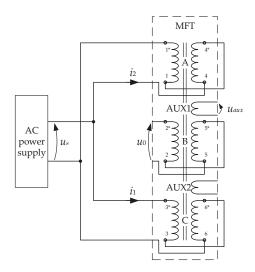

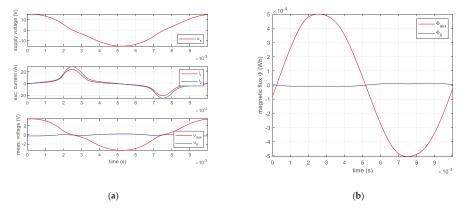

| Piotr Dworakowski, Andrzej Wilk, Michal Michna, Bruno Lefebvre, Fabien Sixdenier andMichel Mermet-GuyennetEffective Permeability of Multi Air Gap Ferrite Core 3-Phase Medium Frequency Transformerin Isolated DC-DC ConvertersReprinted from: Energies 2020, 13, 1352, doi:10.3390/en13061352                                                    |

| Marek Adamowicz and Janusz Szewczyk         SiC-Based Power Electronic Traction Transformer (PETT) for 3 kV DC Rail Traction         Reprinted from: Energies 2020, 13, 5573, doi:10.3390/en13215573                                                                                                                                              |

| Viktor Shevchenko, Bohdan Pakhaliuk, Oleksandr Husev, Oleksandr Veligorskyi,<br>Deniss Stepins and Ryszard Strzelecki<br>Feasibility Study GaN Transistors Application in the Novel Split-Coils Inductive Power Transfer<br>System with T-Type Inverter<br>Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 4535, doi:10.3390/en13174535 |

| Hermes Loschi, Robert Smolenski, Piotr Lezynski and Douglas Nascimento<br>Aggregated Conducted Electromagnetic Interference Generated by DC/DC Converters with<br>Deterministic and Random Modulation<br>Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 3698, doi:10.3390/en13143698                                                   |

| Hermes Loschi, Piotr Lezynski, Robert Smolenski, Douglas Nascimento         and Wojciech Sleszynski         FPGA-Based System for Electromagnetic Interference Evaluation in Random Modulated         DC/DC Converters         Reprinted from: Energies 2020, 13, 2389, doi:10.3390/en13092389                                                    |

| Jan Mucko, Robert Dobosz and Ryszard Strzelecki<br>Dielectric Barrier Discharge Systems with HV Generators and Discharge Chambers for Surface<br>Treatment and Decontamination of Organic Products<br>Reprinted from: <i>Energies</i> <b>2020</b> , <i>13</i> , 5181, doi:10.3390/en13195181                                                      |

### About the Editors

**Ryszard Strzelecki** (M'97-SM'07) was born in Bydgoszcz, Poland. He received the M.Sc. and Ph.D. degrees in Electronic Engineering from the Department of Industrial Electronics, National Technical University of Ukraine "Kyiv Polytechnic Institute", Kyiv, Ukraine, in 1981 and 1984, respectively, and the Dr. Sc. degree in Electrical Engineering from the Institute of Electrodynamics, The National Academy of Sciences of Ukraine, Kyiv, in 1991. He is currently a full professor with the Gdańsk University of Technology (Gdańsk, Poland), co-head of the Laboratory of Power Electronics and Automated Electric Drive, ITMO University (St. Petersburg, Russia), and Scientific Consultant for Power Electronics to the Management Board of AREX Ltd. In 2020, he was elected to the Committee on Electrical Engineering of the Polish Academy of Sciences. His research activity is concentrated on the topology, control, and industry application of power electronic conditioners, particularly for power quality enhancement and power flow control on distributed electrical networks.

Galina Demidova received her B.Sc., engineer, and Ph.D. degrees from ITMO University, Saint Petersburg, Russia. At present she is an Associate Professor at the Faculty of Control Systems and Robotics, Engineer of the Industrial Department of Precision Electromechanical Systems, and researcher of the International Scientific Laboratory "Power electronics and Automated Electric Drive", at ITMO University. She has performed more than 20 R&D projects, dealing with control systems in digital electric power drives for tracking telescopes. She has authored or coauthored more than 50 conference and journal papers. She is co-Guest Editor in several Special Issues, and an organizer of the IEEE Conference. Her current research interests include adaptive control, fuzzy logic control, motion control, automatic control, fuzzy neural networks, hybrid intelligent systems, genetic algorithms, electromechanical systems, wind turbines, and multi-agent control

Dmitri Vinnikov Guest Editor 3: Prof. Dr. Dmitri Vinnikov Dmitri Vinnikov was born in Tallinn, Estonia, in 1976. He received the Dipl.Eng., M.Sc., and Dr.Sc.techn. degrees in Electrical Engineering from Tallinn University of Technology, Tallinn, Estonia, in 1999, 2001, and 2005, respectively. He is currently a Research Professor and the Head of the Power Electronics Group, Department of Electrical Power Engineering and Mechatronics, Tallinn University of Technology (Estonia), and a visiting professor in the Faculty of Control System and Robotics, ITMO University, Saint Petersburg, Russia. He is the Head of R&D and co-founder of Ubik Solutions LLC.— an Estonian start-up company dedicated to innovative & smart power electronics for renewable energy systems. Moreover, he is one of the founders and leading researchers of ZEBE—the Estonian Centre of Excellence, performing research toward the development of zero energy and resource efficient smart buildings and districts. He has authored or co-authored two books, five monographs, and one book chapter, as well as more than 300 published papers on power converter design and development, and is the holder of numerous patents and utility models in this field. His research interests include applied designs of power electronic converters and control systems, renewable energy conversion systems (photovoltaic and wind), impedance-source power converters, and implementation of wide bandgap power semiconductors. D. Vinnikov is a Chair of the IEEE Estonia Section .

## Preface to "Industrial and Technological Applications of Power Electronics Systems"

Since the turn of the century, interest in electrical power systems has been growing steadily, in part due to a tendency to move from directly controlled to intelligent autonomous energy systems. In particular, the increasing presence of renewable energy sources and the development of novel technologies, which demand active and often ultra-precise power supply systems, have generated extensive research in the area of advanced power electronics systems. The importance and scope of the application of regulated power sources in various technological systems are also growing, e.g., using plasma, ultrasounds, and superconductors. Furthermore, researchers pay great attention to loads in these systems, which are mostly represented by various types of electric drives that should be energy efficient. Hence, the main role in many modern technologies and industrial systems is to diversify power electronics converters by applying new topologies, components, and smart controls, where emphasis is placed on such merits as wide input voltage, load regulation range, improved quality of the input and output parameters, high control flexibility, and low cost. To promote research, and accelerate the transfer of knowledge and experience in the above areas, we propose a Special Issue of Energies on industrial and technological applications of power electronics systems. An important premise of this Special Issue would be the synergy effect derived from a combination of views and approaches from various power electronics application areas.

> Ryszard Strzelecki, Galina Demidova , Dmitri Vinnikov Editors

Article

## A Parallel Estimation System of Stator Resistance and Rotor Speed for Active Disturbance Rejection Control of Six-Phase Induction Motor

Hamidreza Heidari <sup>1,\*</sup>, Anton Rassõlkin <sup>1</sup>, Mohammad Hosein Holakooie <sup>2</sup>, Toomas Vaimann <sup>1</sup>, Ants Kallaste <sup>1</sup>, Anouar Belahcen <sup>1,3</sup> and and Dmitry V. Lukichev <sup>4</sup>

- <sup>1</sup> Department of Electrical Power Engineering and Mechatronics, Tallinn University of Technology, 19086 Tallinn, Estonia; anton.rassolkin@taltech.ee (A.R.); toomas.vaimann@taltech.ee (T.V.); ants.kallaste@taltech.ee (A.K.); anouar.belahcen@aalto.fi (A.B.)

- <sup>2</sup> Department of Electrical Engineering, University of Zanjan, Zanjan 45371-38791, Iran; hosein.holakooie@znu.ac.ir

- <sup>3</sup> Department of Electrical Engineering, Aalto University, 11000 Aalto, Finland

- <sup>4</sup> Faculty of Control Systems and Robotics, ITMO University, 197101 St. Petersburg, Russia; lukichev@itmo.ru

- \* Correspondence: haheid@taltech.ee

Received: 3 February 2020; Accepted: 24 February 2020; Published: 2 March 2020

**Abstract:** In this paper, a parallel estimation system of the stator resistance and the rotor speed is proposed in speed sensorless six-phase induction motor (6PIM) drive. First, a full-order observer is presented to provide the stator current and the rotor flux. Then, an adaptive control law is designed using the Lyapunov stability theorem to estimate the rotor speed. In parallel, a stator resistance identification scheme is proposed using more degrees of freedom of the 6PIM, which is also based on the Lyapunov stability theorem. The main advantage of the proposed method is that the stator resistance adaptation is completely decoupled from the rotor speed estimation algorithm. To increase the robustness of the drive system against external disturbances, noises, and parameter uncertainties, an active disturbance rejection controller (ADRC) is introduced in direct torque control (DTC) of the 6PIM. The experimental results clarify the effectiveness of the proposed approaches.

**Keywords:** active disturbance rejection controller (ADRC); direct torque control (DTC); full-order observer; sensorless; six-phase induction motor (6PIM); stator resistance estimator

#### 1. Introduction

Three-phase induction motor drives have become a mature technology in the last years, but investigations into concepts of multiphase induction motor drives are still taking place. Multiphase drive systems have a nearly 40-year history of research and study due to their promising advantages against the conventional three-phase systems. The phase redundancy of the multiphase drives provides extra merits such as fault-tolerant operation, series-connected multimotor drive systems, asymmetry and braking systems. Six-phase induction motors (6PIMs) are known for its fault-tolerant capability, low rate of inverter switches, and low DC-link voltage utilization compared with its three-phase one [1–3]. On the other hand, the modular three-phase structure of the 6PIM allows the use of well-known three-phase technologies. The 6PIM is successfully used in special applications, such as electric ships, electric aircrafts, electric vehicles, and melt pumps, where the high reliability and continuity of the operation are critical factors for the system [4]. The phase redundancy of the 6PIM provides the ability of the open-phase fault-tolerant operation without any extra electronic components [5,6].

Among different structures of the 6PIM [4], the asymmetrical 6PIM with double isolated neutral points, which consists of two sets of three-phase windings spatially shifted by 30 electrical degrees,

MDPI

has attracted the interest of many researchers [7–10]. The traditional three-phase control strategies, including switching table-based direct torque control (ST-DTC) [7], modulation-based DTC [8], the field-oriented control (FOC) [9], and finite control set-model predictive control (FCS-MPC) [10], can be extended to 6PIM (or other multi-phase machines) with some modifications to use more freedom degrees that exist in multi-phase machines. DTC is a well-accepted technique due to its simplicity, quick dynamics, and robustness [11]. The modulation-based DTC strategy offers better phase current, torque, and flux response. On the contrary, this method has more complexity against conventional ST-DTC. The ST-DTC approach has straightforward and simple structure, but it is completely overshadowed by low-order harmonics due to unused voltage vectors in the losses subspaces. To overcome this restriction, the idea of duty cycle control is introduced by several researchers [12,13].

The rapid development of intelligent and high-performance control technologies has also brought about changes in the adjustable speed drive system for different industrial applications [14,15]. To operate safely and reliably under different conditions, there is a lot of debate nowadays about the main control strategy of the system [16,17]. Among different high-performance control strategies of drive systems, the DTC strategy has a straightforward algorithm. The DTC technique is inherently speed sensorless. Nevertheless, if an outer speed loop is added to the DTC, the speed value is also necessary. Sensorless three/multi-phase induction machine drives are widely addressed in the technical literature due to multiple shortcomings of shaft encoders [18–23]. To investigate the instability problem of the traditional rotor flux-based model reference adaptive system (MRAS) speed estimators in the regenerating-mode low-speed operation, a stator current-based and back electromotive force-based MRASs are addressed in [19,20], respectively. In [21], two modified adaptation mechanisms are proposed to replace the classical proportional-integral (PI) regulator. The full-order Luenberger and Kalman filter observers are discussed in [22,23], respectively. Providing a DTC drive system with parallel identification of the rotor speed and the stator resistance is a challenging task because the operation of the DTC scheme is severely dependent on the stator resistance. This problem is sporadically reported for three-phase induction machines (3PIMs) [24,25], where the rotor speed and the stator resistance estimators encounter an overlap due to limited freedom degrees of 3PIM. In this paper, the problem of parallel estimation is investigated using more freedom degrees of 6PIM.

The outer speed control loop of the DTC scheme conventionally contains the PI regulator to obtain torque command from speed error. In general, the control law of a PID regulator is a linear combination of proportional-integral-derivative terms, which is suitable for linear systems. For nonlinear systems, such as the 6PIM drive system, the PI regulator has been given a lot of attention due to its simplicity. However, it suffers from multiple problems including: (1) tuning of its parameters; (2) high sensitivity against noise and external disturbances; and (3) loss of efficiency due to oversimplified control law [26,27]. One promising technique to relatively get rid of the drawbacks of PI regulator is active disturbance rejection controller (ADRC) [26,28]. The ADRC is a nonlinear control scheme, which provides a robust control against noises, external disturbances, and parameter uncertainties. For these reasons, the ADRC technique has recently attracted more attention for electric drive systems. To address this issue, a modified FOC scheme based on first-order ADRCs for current and speed control loops is proposed in [29]. A combined active disturbance rejection and sliding-mode controller for an induction motor is presented to achieve total robustness [30].

The aim of this paper is to present an ADRC-based DTC scheme for sensorless 6PIM drives. The speed estimator is based on adaptive full-order observer, and its control law is designed using Lyapunov stability theorem. Besides the speed estimation system, a stator resistance estimator is proposed using additional degrees of freedom of the 6PIM to enhance the robustness of the sensorless DTC strategy against stator resistance uncertainties. The adaptation law for the stator resistance estimator is derived using the Lyapunov stability theorem to ensure its overall convergence.

The rest of this paper is organized as follows. Section 2 introduces the mathematical model of the 6PIM. Section 3 presents the design procedure of the adaptive full-order observer, the speed estimator,

and the stator resistance estimator. The DTC scheme of the 6PIM is discussed in Section 4, which includes the ST-DTC scheme, and ADRC in DTC. The experimental results are presented in Section 5. Finally, Section 6 summarizes the findings and concludes the paper.

#### 2. Dynamic Model of 6PIM

There are two popular approaches for modeling of the multi-phase machines: (1) multiple d–q approach [9]; (2) vector space decomposition (VSD) approach [31]. The first method is exclusively used for modular three-phase structures-based multi-phase machines such as six-phase and nine-phase machines. However, the second method can be used for all types of multi-phase machines. In this research, the VSD approach is used, where a 6PIM with distributed windings is modeled in the three orthogonal subspaces, i.e., the  $\alpha - \beta$ ,  $z_1 - z_2$  and  $o_1 - o_2$ . Among them, only the  $\alpha - \beta$  variables are in relation with electromechanical energy conversion, while  $z_1 - z_2$  and  $o_1 - o_2$  variables do not actively contribute to the torque production.

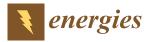

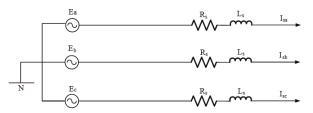

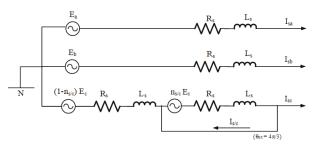

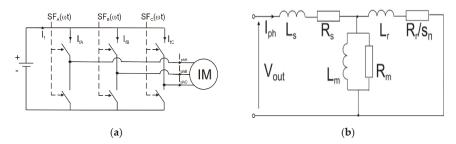

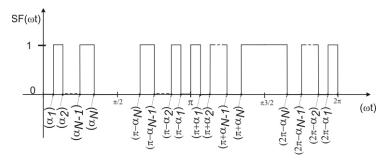

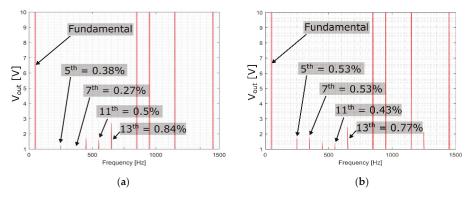

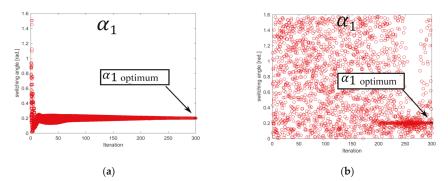

The schematic diagram of a six-phase voltage source inverter (VSI)-fed an 6PIM with two isolated neutral points is shown in Figure 1. The transfer between the normal a - x - b - y - c - z variables and  $\alpha - \beta - z_1 - z_2 - o_1 - o_2$  variables is performed by  $T_6$  transformation matrix as follows [31]:

$$T_{6} = \frac{1}{3} \begin{bmatrix} 1 & \frac{\sqrt{3}}{2} & -\frac{1}{2} & -\frac{\sqrt{3}}{2} & -\frac{1}{2} & 0\\ 0 & \frac{1}{2} & \frac{\sqrt{3}}{2} & \frac{1}{2} & -\frac{\sqrt{3}}{2} & -1\\ 1 & -\frac{\sqrt{3}}{2} & -\frac{1}{2} & \frac{\sqrt{3}}{2} & -\frac{1}{2} & 0\\ 0 & \frac{1}{2} & -\frac{\sqrt{3}}{2} & \frac{1}{2} & \frac{\sqrt{3}}{2} & -1\\ 1 & 0 & 1 & 0 & 1 & 0\\ 0 & 1 & 0 & 1 & 0 & 1 \end{bmatrix}$$

(1)

By applying  $T_6$  matrix to the voltage equations in the original six-dimensional system, the 6PIM model can be represented in the three orthogonal submodels, identified as  $\alpha - \beta$ ,  $z_1 - z_2$ , and  $o_1 - o_2$ . The voltage space vector equations of the 6PIM in the  $\alpha - \beta$  subspace are written as follows:

$$\boldsymbol{v}_s = \boldsymbol{R}_s \boldsymbol{i}_s + \boldsymbol{p} \boldsymbol{\Psi}_s \tag{2}$$

$$0 = R_r i_r + p \Psi_r - j \omega_r \Psi_r \tag{3}$$

The flux linkages are

$$\Psi_s = L_s i_s + L_m i_r \tag{4}$$

$$\Psi_r = L_m i_s + L_r i_r \tag{5}$$

where v, i,  $\Psi$ , R, and L represent voltage, current, flux linkage, resistance, and inductance, respectively, for stator (s subscript) and rotor (r subscript) quantities, and p denotes derivative operator. The electromagnetic torque produced by the 6PIM is expressed as

$$T_e = 3P \Psi_s \otimes i_s \tag{6}$$

where *P* is pole pairs and  $\otimes$  denotes the cross product.

The 6PIM voltage equations in the  $z_1 - z_2$  subspace are the same as a passive R-L circuit as follows:

$$v_{sz1} = R_s i_{sz1} + L_{ls} p i_{sz1} \tag{7}$$

$$v_{s22} = R_s i_{s22} + L_{ls} p i_{s22} \tag{8}$$

where  $L_{ls}$  is stator leakage inductance.

On the presumption that the stator mutual leakage inductances can be neglected, the 6PIM model in the  $o_1 - o_2$  subspace has the same form of the  $z_1 - z_2$  subspace. However, the applied 6PIM with

two isolated neutral points avoids zero-sequence currents because it contains two sets of balanced three-phase windings.

Figure 1. Six-phase two-level VSI-fed 6PIM.

#### 3. Adaptive Full-Order Observer

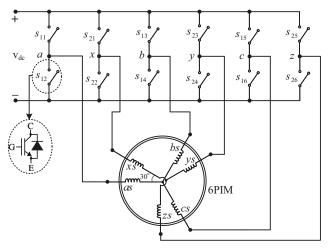

The block diagram of the proposed  $R_s$  and  $\omega_r$  estimators based on the adaptive state observer is shown in Figure 2. It contains the stator current and rotor flux observers, the stator resistance identifier, and the rotor speed estimator, which are discussed below.

**Figure 2.** The block diagram of the proposed parallel estimation system of the stator resistance and the rotor speed based on an adaptive full-order observer.

#### 3.1. Stator Current and Rotor Flux Observers

The general form of state-space model of the 6PIM in the  $\alpha - \beta$  subspace is

$$\begin{cases} \dot{x}_1 = A_1 x_1 + B_1 u_1 \\ y_1 = C_1 x + D_1 u_1 \end{cases}$$

(9)

Assuming stator current and rotor flux as state variables and using Equations (2) and (3), the elements of state-space representation in  $\alpha - \beta$  subspace will be

$$x_1 = \begin{bmatrix} i_{s\alpha} & i_{s\beta} & \psi_{r\alpha} & \psi_{r\beta} \end{bmatrix}^T$$

(10)

$$A_{1} = \begin{bmatrix} \left(-\frac{R_{s}}{\sigma L_{s}} - \frac{1-\sigma}{\sigma T_{r}}\right)I & \frac{L_{m}}{\sigma L_{s}L_{r}}\left(\frac{1}{T_{r}}I - \omega_{r}J\right) \\ \frac{L_{m}}{T_{r}}I & -\frac{1}{T_{r}}I + \omega_{r}J \end{bmatrix}$$

(11)

$$B_1 = \begin{bmatrix} \frac{1}{\sigma L_s} I & O \end{bmatrix}^T$$

(12)

$$u_1 = \begin{bmatrix} v_{s\alpha} & v_{s\beta} \end{bmatrix}^T \tag{13}$$

$$y_1 = \begin{bmatrix} i_{s\alpha} & i_{s\beta} \end{bmatrix}^T \tag{14}$$

$$C_1 = \begin{bmatrix} I & O \end{bmatrix} \tag{15}$$

with

$$I = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}, J = \begin{bmatrix} 0 & -1 \\ 1 & 0 \end{bmatrix}, O = \begin{bmatrix} 0 & 0 \\ 0 & 0 \end{bmatrix}$$

(16)

where  $T_r = L_r / R_r$  is rotor time constant and  $\sigma = 1 - L_m^2 / L_s L_r$  is leakage coefficient.

The state observer of the 6PIM has a similar form of state-space representation except that an additional compensation term based on error of measurable states and observer gain matrix is added to it. The state observer can be written as

$$\begin{cases} \dot{x}_1 = \hat{A}_1 \hat{x}_1 + B_1 u_1 + G_1 (i_s - \hat{i}_s) \\ \hat{y}_1 = C_1 \hat{x}_1 \end{cases}$$

(17)

where the marker  $^{\wedge}$  indicates the estimated values, and  $G_1$  is the observer gain matrix. The matrix  $A_1$  contains unknown parameters of the 6PIM such as the rotor speed and the stator resistance. These parameters can be estimated by the designing of a suitable adaptation control law with a nonlinear theorem such as a Lyapunov stability theorem. It is worth mentioning here that the matrix  $A_1$  also contains the rotor time constant. However, simultaneous estimation of the rotor speed, the rotor time constant, and the stator resistance is challenging because of persistency of excitation conditions problem [32]. Some techniques have recently been developed based on signal injection to provide persistent excitation [33], which suffer from steady-state torque and speed ripples. In this paper, the stator resistance is estimated from additional degrees of freedom of the 6PIM, while the rotor speed is provided using the 6PIM equations in  $\alpha - \beta$  subspace. This procedure provides the stator resistance independent from the rotor speed.

The observer gain matrix  $G_1$  must be designed to ensure stability and good dynamic response of the observer at a wide range of the speeds. Using pole-placement method, the elements of matrix  $G_1$  is provided as [22,34]

$$G_1 = \begin{bmatrix} g_1 & g_2 & g_3 & g_4 \\ -g_2 & g_1 & -g_4 & g_3 \end{bmatrix}^T$$

(18)

where

$$\begin{cases} g_1 = (1 - K_{po})(R_s L_r^2 + R_r L_m^2)/\sigma L_s L_r^2 \\ g_2 = (K_{po} - 1)\hat{\omega}_r \\ g_3 = (K_{po} - 1)(R_s L_s - K_{po} R_s L_r)/L_m \\ g_4 = (1 - K_{po})\hat{\omega}_r \sigma L_s L_r/L_m \end{cases}$$

(19)

where  $K_{po} > 0$  is observer constant gain.

#### 3.2. Stator Resistance Identification

In this paper, a stator resistance adaptation system is proposed using the machine model in the  $z_1 - z_2$  subspace. This method can be utilized for any multi-phase machines. It is completely decoupled from the rotor speed and the rotor time constant, whereas most of the conventional stator resistance estimators, developed for three-phase machines, are related to these parameters. The proposed  $R_s$  estimator only depends on the stator leakage inductance  $L_{ls}$ , which can be approximately assumed to be constant.

The state-space model of 6PIM in the  $z_1 - z_2$  subspace, with consideration of  $i_{sz1}$  and  $i_{sz2}$  as the state variables, can be derived from Equations (7) and (8) as follows:

$$\begin{bmatrix} \dot{i}_{sz1} \\ \dot{i}_{sz2} \end{bmatrix} = \begin{bmatrix} -\frac{R_s}{L_{ls}} & 0 \\ 0 & -\frac{R_s}{L_{ls}} \end{bmatrix} \begin{bmatrix} \dot{i}_{sz1} \\ \dot{i}_{sz2} \end{bmatrix} + \frac{1}{L_{ls}} \begin{bmatrix} v_{sz1} \\ v_{sz2} \end{bmatrix}$$

$$\begin{bmatrix} \dot{i}_{sz1} \\ \dot{i}_{sz2} \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \begin{bmatrix} \dot{i}_{sz1} \\ \dot{i}_{sz2} \end{bmatrix}$$

(20)

In this case, the proposed states observer is given by

$$\begin{cases} \dot{x}_2 = \hat{A}_2 \hat{x}_2 + B_2 u_2 \\ \dot{y}_2 = C_2 \hat{x}_2 \end{cases}$$

(21)

It should be noted that a correction term  $G_2(x_2 - \hat{x}_2)$  is neglected in Equation (21) due to the inherent stability of the observer.

The proposed adaptation law for the stator resistance estimation is

$$\hat{R}_s = K_{pr}\epsilon_{R_S} + K_{ir}\int\epsilon_{R_S}dt$$

(22)

where  $K_{ir}$  and  $K_{pr}$  are the integral and proportional gains, respectively, and  $\epsilon_{R_S}$  is the stator resistance error signal

$$\epsilon_{R_s} = \hat{i}_{sz1}(i_{sz1} - \hat{i}_{sz1}) + \hat{i}_{sz2}(i_{sz2} - \hat{i}_{sz2})$$

(23)

The proof for the stator resistance adaptation law is presented in Appendix A.

#### 3.3. Rotor Speed Estimation

In order to design the speed adaptation law, it is considered as an unknown parameter. First, an appropriate positive definite function is chosen as the Lyapunov candidate. Then, the adaptation law is obtained using the Lyapunov criterion to ensure asymptotic stability of the system. The speed adaptation law is

$$\hat{\omega}_r = K_{p\omega}\epsilon_\omega + K_{i\omega}\int\epsilon_\omega dt \tag{24}$$

where  $K_{p\omega}$  and  $K_{i\omega}$  are proportional and integral gains, respectively, and  $\epsilon_{\omega}$  is the speed error signal as follows:

$$\epsilon_{\omega} = (i_{s\alpha} - \hat{i}_{s\alpha})\hat{\psi}_{r\beta} - (i_{s\beta} - \hat{i}_{s\beta})\hat{\psi}_{r\alpha}$$

<sup>(25)</sup>

The proof for the speed adaptation law is presented in Appendix B.

#### 4. DTC of 6PIM

#### 4.1. ST-DTC Scheme

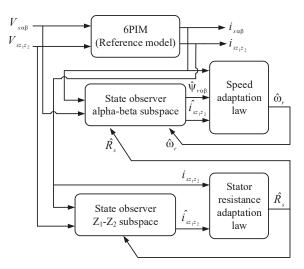

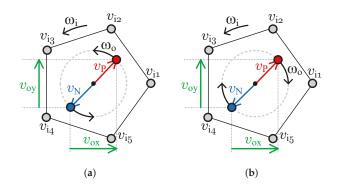

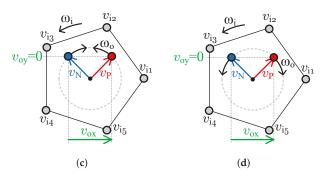

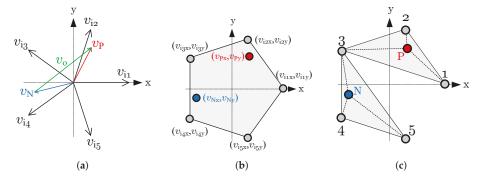

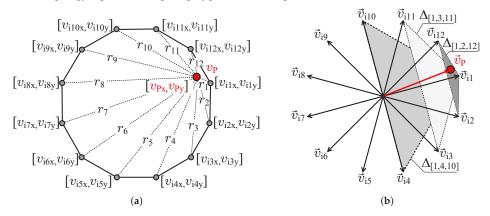

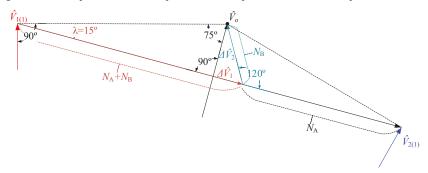

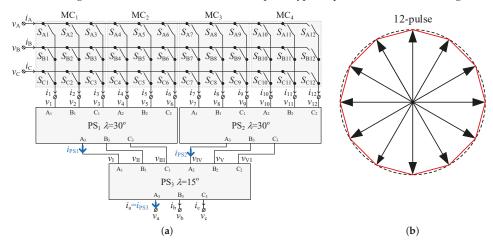

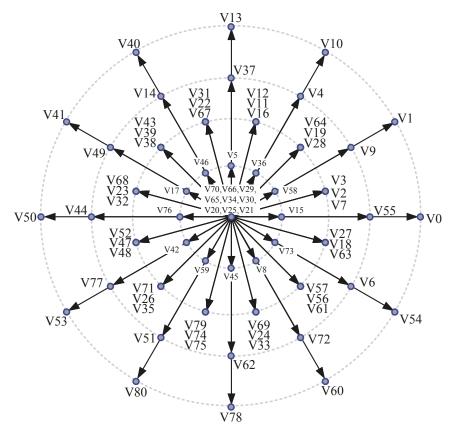

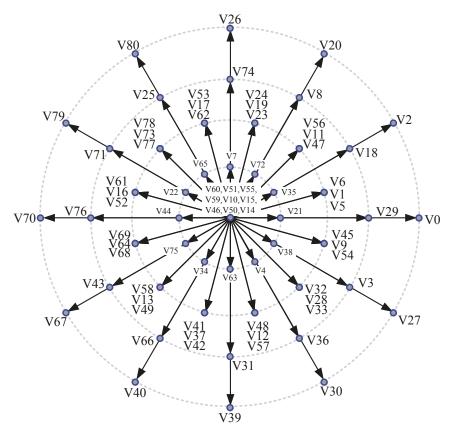

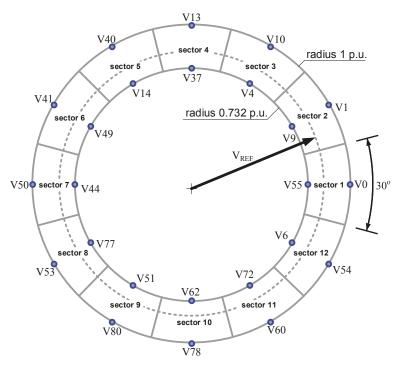

A six-phase VSI contains overall  $2^6 = 64$  different voltage space vectors, 60 active, and four zero vectors, where the active voltage vectors are distributed in four non-zero levels depicted in Figure 3. The electrical angle of each sectors is  $30^\circ$ . The 6PIM phase-to-neutral voltages can be calculated as

$$\begin{bmatrix} V_a \\ V_b \\ V_c \\ V_x \\ V_y \\ V_z \end{bmatrix} = \frac{V_{dc}}{3} \begin{bmatrix} 2 & -1 & -1 & 0 & 0 & 0 \\ -1 & 2 & -1 & 0 & 0 & 0 \\ -1 & -1 & 2 & 0 & 0 & 0 \\ 0 & 0 & 0 & 2 & -1 & -1 \\ 0 & 0 & 0 & -1 & 2 & -1 \\ 0 & 0 & 0 & -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} S_a \\ S_b \\ S_c \\ S_x \\ S_y \\ S_z \end{bmatrix}$$

(26)

where  $S_i = \{0, 1\}, i = \{a, x, b, y, c, z\}$  is the switching state. When  $S_i = 1$  ( $S_i = 0$ ), the corresponding stator terminal is connected to positive (negative) DC-link rail. The voltage space vectors are given by

$$v_s = \frac{1}{3} [V_a + aV_x + a^4 V_b + a^5 V_y + a^8 V_c + a^9 V_z]$$

<sup>(27)</sup>

$$v_z = \frac{1}{3} [V_a + a^5 V_x + a^8 V_b + a V_y + a^4 V_c + a^9 V_z]$$

<sup>(28)</sup>

where  $v_{z} = v_{sz1} + jv_{sz2}$  and  $a = e^{j\pi/6}$ .

The flux estimator is obtained from

$$\psi_{s\alpha} = \int (v_{s\alpha} - \hat{R}_s i_{s\alpha}) dt \tag{29}$$

$$\psi_{s\beta} = \int (v_{s\beta} - \hat{R}_s i_{s\beta}) dt \tag{30}$$

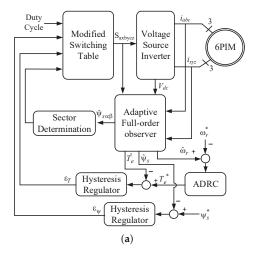

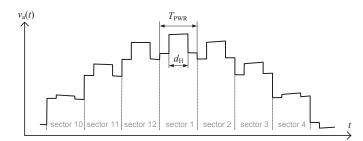

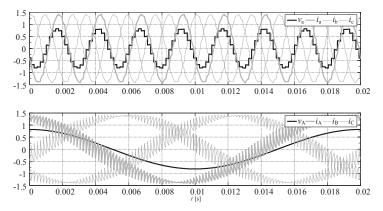

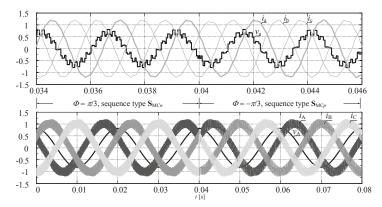

and the toque estimator is obtained from (6). In the traditional ST-DTC, the torque and stator flux errors are applied to hysteresis regulators to provide the sign of torque ( $\epsilon_T$ ) and stator flux ( $\epsilon_{\psi}$ ). According to gained signals and also the position of stator flux, a proper large voltage vector is selected based on Table 1 during each sampling period. From Figure 3, the corresponding voltage vectors in the  $z_1 - z_2$ subspace will produce large current harmonics, when only large voltage vectors are used to control the torque and flux. Hence, it can alleviate the current harmonics through reduction of the  $z_1 - z_2$ components by applying a combined voltage vector during each sampling period. This technique is referred to as duty cycle control, where a virtual vector (synthesized by large and medium voltage space vectors) is applied to the inverter in each sampling period because the large and medium voltage vectors are in the opposite direction in the  $z_1 - z_2$  subspace (see Figure 3). The duration of the applied vectors is calculated in order to reduce the average volt-seconds in the  $z_1 - z_2$  subspace [4]. The block diagram of the proposed sensorless DTC strategy with the adaptive full-order observer is shown in Figure 4a. In this figure, the speed control loop is based on the ADRC strategy, which will be discussed in the next subsection.

**Figure 3.** The  $\alpha - \beta$  (top side) and the  $z_1 - z_2$  (down side) vector subspaces for a six-phase VSI.

Table 1. Switching table of DTC strategy.

| $\epsilon_T$ | $\epsilon_{\psi}$ | Selected Voltage * |

|--------------|-------------------|--------------------|

| 1            | 1                 | $V_{m+1}$          |

| 1            | 0                 | $V_{m+4}$          |

| 0            | 1                 | $V_0$              |

| 0            | 0                 | $V_0$              |

| -1           | 1                 | $V_{m-2}$          |

| -1           | 0                 | $V_{m-5}$          |

|              | * m is            | sector number.     |

Figure 4. Cont.

Figure 4. Block diagram of (a) the proposed sensorless DTC strategy; (b) ADRC.

#### 4.2. ADRC in DTC

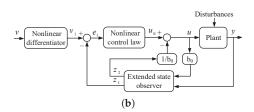

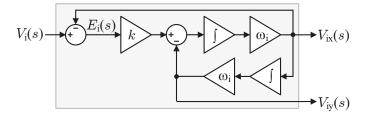

To enhance the robustness of the DTC technique against external disturbances and measurement noises, the ADRC is proposed to replace with the conventional PI regulator in the outer speed control loop. The block diagram of ADRC is shown in Figure 4b. It consists of three main elements: (1) nonlinear differentiator; (2) extended state observer; (3) nonlinear control law.

In some industrial applications, the command values are changed as step function, which is not suitable for the control system because of a sudden jump of output and control signals. To solve this problem, the nonlinear differentiator is used, which makes a reasonable transient profile from command signals for tracking [26]. The nonlinear differentiator can be expressed by

$$\begin{cases} v_1(k+1) = v_1(k) + hv_2(k) \\ v_2(k+1) = v_2(k) + hf_1(v_1(k) - v(k), v_2(k), r_0, h_0) \end{cases}$$

(31)

where  $f_1$  is a nonlinear function as

$$f_1(v_1(k), v_2(k), r_0, h_0) = -\begin{cases} a(k)/h_0 & |a(k)| \le r_0 h_0\\ r_0 \text{sign}(a(k)) & |a(k)| > r_0 h_0 \end{cases}$$

(32)

with

$$a(k) = \begin{cases} v_2(k) + y_0(k)/h_0 & |a(k)| \le r_0 h_0^2 \\ v_2(k) + (a_0(k) - r_0 h_0)/2 & |a(k)| > r_0 h_0^2 \end{cases}$$

$$y_0(k) = v_1(k) + h_0 v_2(k)$$

$$a_0(k) = \sqrt{(r_0 h_0)^2 + 8r_0 |y_0(k)|}$$

where  $r_0$  and  $h_0$  are the parameters of the nonlinear differentiator, and h is sampling period.

The extended state observer is an enhanced version of feedback linearization method to compensate the total disturbances of the system. Using this observer, the state feedback term can be estimated online; hence, it is an adaptive robust observer against model uncertainties and external disturbances. The extended state observer is represented as follows:

$$\begin{cases} z_1(k+1) = z_1(k) + h[z_2(k) - \beta_1 f_2(e(k), \alpha_1, \delta_1) + b_0 u(k)] \\ z_2(k+1) = z_2(k) - h\beta_2 f_2(e(k), \alpha_1, \delta_1) \\ e(k) = z_1(k) - y(k) \end{cases}$$

(33)

where the nonlinear function  $f_2$  is defined as

$$f_2(e(k), \alpha, \delta) = \begin{cases} e(k)/\delta^{1-\alpha} & |e(k)| \le \delta \\ |e(k)|^{\alpha} \operatorname{sign}(e(k)) & |e(k)| > \delta \end{cases}$$

(34)

where  $\alpha_1$ ,  $\beta_1$ ,  $\beta_1$ ,  $\beta_2$ , and  $b_0$  are the parameters of the extended state observer.

The conventional PI controller is based on the linear combination of proportional and integral terms of error, which may degrade the performance of the DTC scheme. Different nonlinear combination of error can be presented to overcome this problem. In this paper, the following nonlinear control law is used:

$$\begin{cases} e_1(k) = v_1(k) - z_1(k) \\ u_0(k) = \beta_3 f_2(e_1(k), \alpha_2, \delta_2) \\ u(k) = u_0(k) - z_2(k) / b_0 \end{cases}$$

(35)

where  $\alpha_2$ ,  $\beta_3$ , and  $\delta_2$  are the parameters of nonlinear control law.

#### 5. Experimental Validation

#### 5.1. Description of Experimental Setup

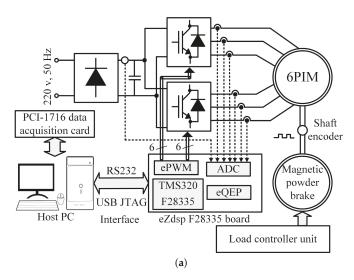

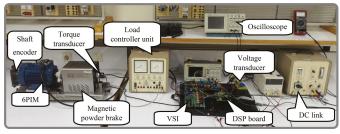

The schematic and photograph of the experimental setup are shown in Figure 5a,b, respectively. The principal elements are

- a TMS320F28335-based digital signal processor (DSP) board.

- two custom-made two-level three-phase VSIs based on BUP 314D IGBTs and LEM LTS 6-NP current transducers.

- an LEM LV25-P voltage transducer.

- an Autonics incremental shaft encoder.

- a magnetic powder brake mechanically coupled to the 6PIM.

- a bridge rectifier.

- a 1-hp three-phase induction motor, which has been rewound to provide an asymmetrical 6PIM. The specifications of the 6PIM are shown in Table 2.

Figure 5. Cont.

(b)

Figure 5. Experimental setup (a) schematic (b) photograph.

| Symbol | Quantity               | Value                                  |

|--------|------------------------|----------------------------------------|

| $T_n$  | Nominal torque         | 2 Nm                                   |

| P      | Pole pairs             | 1                                      |

| $R_s$  | Stator resistance      | $4.08 \Omega$                          |

| $R_r$  | Rotor resistance       | 3.73 Ω                                 |

| $L_s$  | Stator inductance      | 443.6 mH                               |

| $L_r$  | Rotor inductance       | 443.6 mH                               |

| $L_m$  | Magnetizing inductance | 429.8 mH                               |

| J      | Moment of inertia      | $0.000718 \text{ kg} \cdot \text{m}^2$ |

Table 2. The parameters of 6PIM.

#### 5.2. Experimental Results

The performance of the proposed sensorless DTC strategy has been experimentally surveyed using DSP platform, programmed through Code Composer Studio (CCS v.3.3) and MATLAB. The IQmath and digital motor control (DMC) libraries have been used to provide optimized code. A 10 kHz sampling frequency with a 2 µs dead-band has been adopted. The experimental results have been captured using an Advantech PCI-1716 data acquisition card (DAQ) and serial port with LABVIEW and MATLAB, respectively. The serial communications interface (SCI) module has been employed to provide a serial connection between host PC and DSP. An incremental shaft encoder has been used to verify the performance of the speed estimation algorithm. All of the experiments have been carried out in sensorless mode as well as closed-loop adaptation of the stator resistance under various test scenarios, emphasizing on the low-speed region.

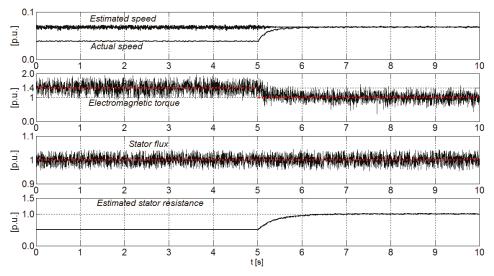

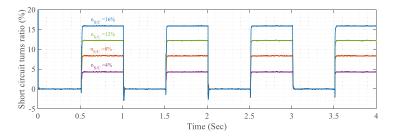

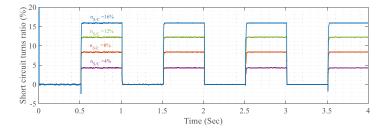

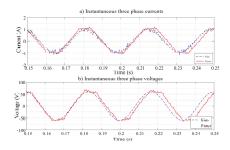

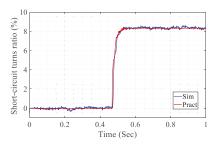

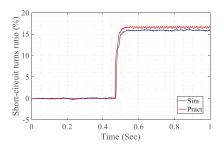

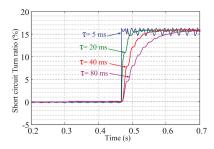

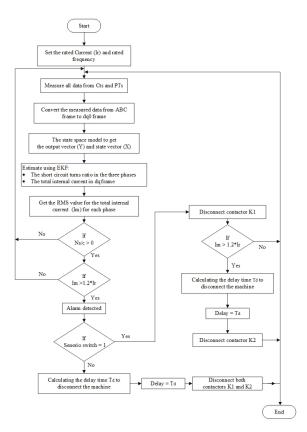

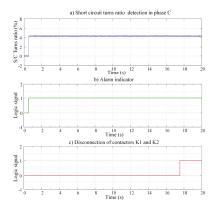

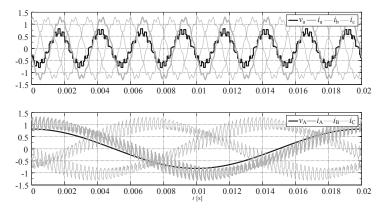

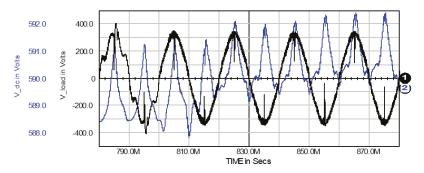

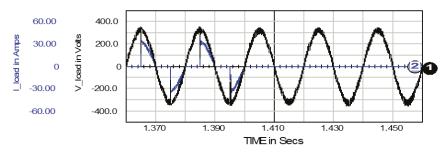

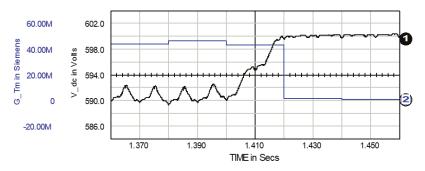

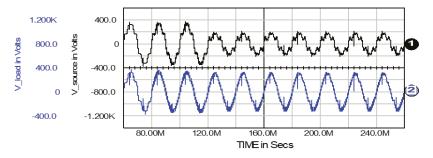

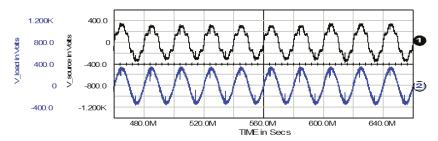

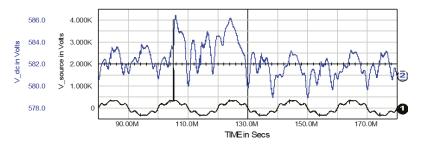

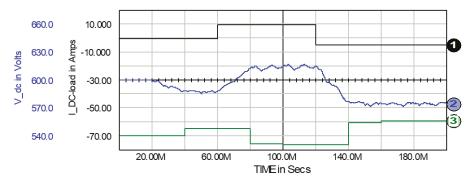

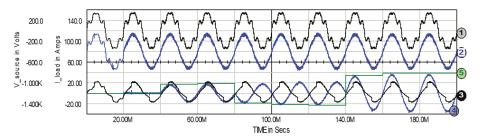

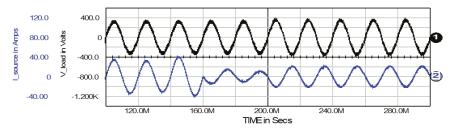

The experimental results of the proposed parallel estimation system of stator resistance and rotor speed under 50% initial stator resistance mismatch are shown in Figure 6. The speed command is 7% rated speed under rated load torque. In this test, the electric drive is allowed to start with a wrong stator resistance. This causes an error in estimated electromagnetic torque and actual speed. However, the estimated speed and the stator flux follow their reference values because of the controller action. It can be seen that the estimation error of the speed and the electromagnetic torque due to detuned stator resistance are removed within short seconds after activation of the stator resistance estimator at t = 5 s.

Figure 6. Experimental results of the proposed parallel estimation system under initial mismatch of stator resistance.

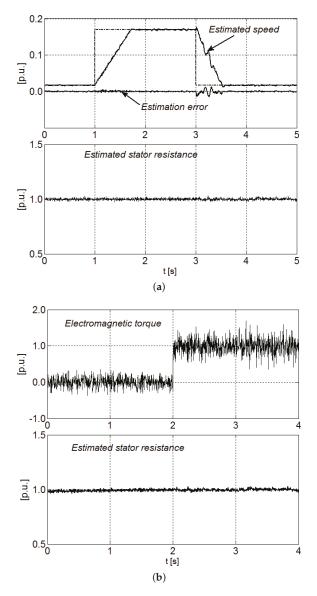

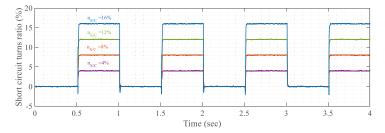

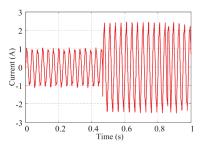

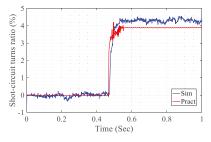

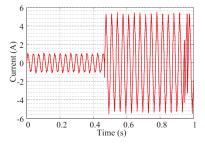

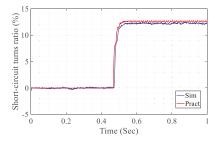

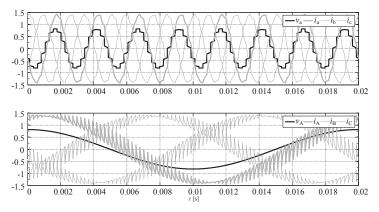

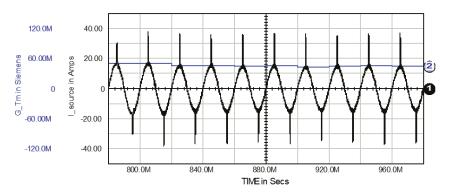

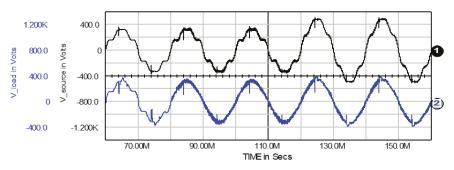

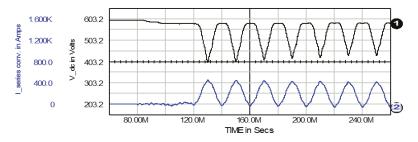

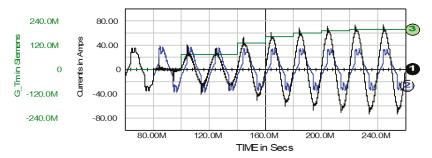

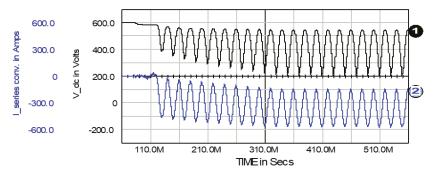

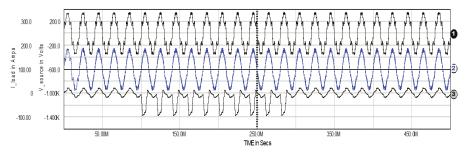

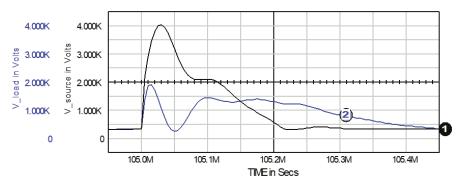

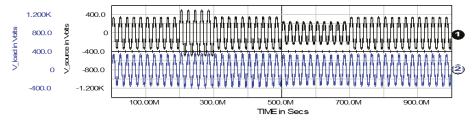

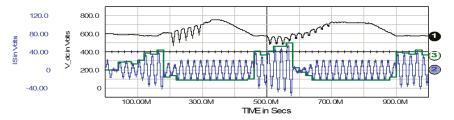

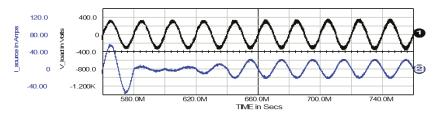

As already mentioned, the proposed parallel estimation system has the merit of avoiding overlap between stator resistance and rotor speed estimators, whereby the stator resistance is independently estimated from rotor speed using additional freedom degrees of 6PIM. The experimental results of estimated stator resistance under speed changes and load change are shown in Figure 7a, b, respectively. In Figure 7a, the speed command is changed as a step function from a very low speed to 17% rated speed, and, in Figure 7b, a load torque is suddenly applied to the motor at t = 2 s. It can be clearly adjudged that the adaptation process of stator resistance is independent of speed and load torque changes.

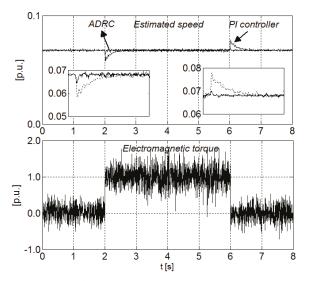

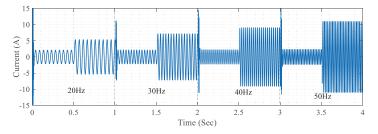

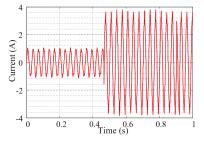

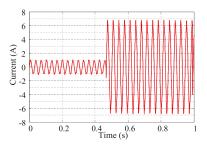

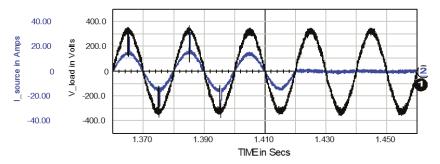

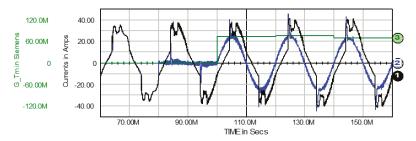

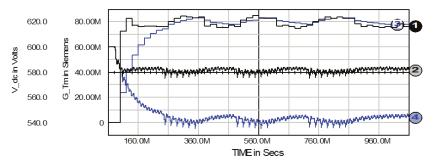

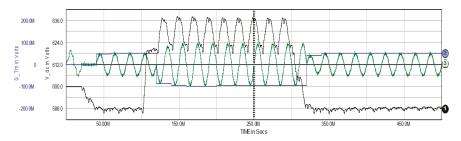

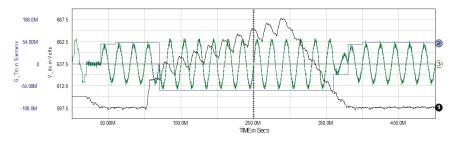

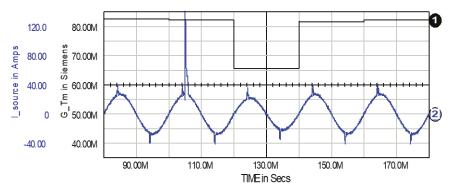

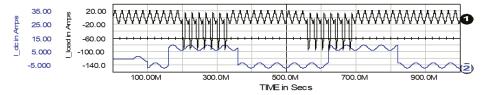

Disturbance-free operation of the ADRC-based speed controller is evaluated through a comparative study of its performance and the conventional PI regulator. The experimental results for the estimated speed under sudden load torque changes at 7% rated speed when the conventional PI and introduced ADRC are utilized as speed controllers are shown in Figure 8. As can be seen, applying the external load torque to the 6PIM leads to a larger overshoot (undershoot), when the conventional PI regulator is employed. The ADRC properly improves the disturbance rejecting capability, which in turn provides a robust performance against load torque changes.

Figure 7. Experimental results of the estimated stator resistance under (a) speed changes (b) load torque change.

Figure 8. Experimental results of the estimated speed with PI and ADRC-based speed controllers under load changes.

#### 6. Conclusions

Multiphase electrical machines and drives have different advantages over their traditional three phase counterparts. In recent years, multiple research works have been published to explore the specific advantages of multiphase machines and drives. In this regard, a parallel estimation system of the stator resistance and the rotor speed for direct torque-controlled 6PIM was proposed in this paper. The speed estimator is based on an adaptive full-order observer, which estimates the speed signal using the 6PIM model in the  $\alpha - \beta$  subspace, while the stator resistance estimator employs the 6PIM model in the  $z_1 - z_2$  subspace. Hence, the stator resistance is identified independently of the rotor speed. The rotor speed- and the stator resistance-adaptation laws were derived using the Lyapunov stability theorem. The performance of the proposed sensorless DTC was experimentally investigated, where the obtained results confirmed its capabilities in terms of accuracy as well as no overlap between the stator resistance and the rotor speed estimators. In order to provide a robust performance for the DTC technique against external load torques, the PI regulator was replaced by an ADRC, as a well-known disturbance-free controller. The better performance of the DTC scheme based on ADRC was verified through a comparative study with the conventional PI regulator.

Author Contributions: Conceptualization, methodology, validation, formal analysis, writing–original draft preparation, H.H., M.H.H.; writing—review and editing, resources, A.R.; project administration, T.V.; investigation, A.K.; funding acquisition, D.V.L.; supervision, A.B. All authors have read and agreed to the published version of the manuscript.

**Funding:** The research has been supported by the Estonian Research Council under grant PSG453 "Digital twin for propulsion drive of autonomous electric vehicle" and was financially supported by Government of Russian Federation (Grant 08-08).

Conflicts of Interest: The authors declare no conflict of interest.

#### Appendix A. The Design of Adaption Law for Stator Resistance Estimation

The quadratic Lyapunov function for asymptotic stability of the proposed stator resistance estimation system is defined as

$$V_r = e_r^{\ T} e_r + \frac{\Delta R_s^2}{\lambda_r} \tag{A1}$$

where  $\lambda_r$  is a positive constant,  $\Delta R_s = \hat{R_s} - R_s$ ,  $\hat{R_s}$  is the estimated stator resistance,  $R_s$  is the real stator resistance, and  $e_r$  is the error matrix of the state variables in the  $z_1 - z_2$  subspace as

$$e_r = x_2 - \hat{x}_2 = \begin{bmatrix} i_{sz1} & \hat{i}_{sz1} & i_{sz2} - \hat{i}_{sz2} \end{bmatrix}^T$$

(A2)

The asymptotic stability of the stator resistance estimator is assured when the Lyapunov candidate function  $V_r$  is positive definite as well as its time derivative  $pV_r$  is negative definite. The time derivative of the Lyapunov candidate function is calculated as

$$pV_r = e_r^T p e_r + p e_r^T e_r + \frac{2}{\lambda_r} \Delta R_s p \hat{R}_s$$

(A3)

With some mathematical manipulation, Equation (A3) can be written as

$$pV_r = e_r^T (A_2 + A_2^T) e_r - [e_r^T \Delta A_2 \hat{x} + \hat{x}_2^T \Delta A_2^T e_r] + \frac{2}{\lambda_r} \Delta R_s p \hat{R}_s$$

(A4)

The first term of Equation (A4) is inherently negative definite. The stability of the system is eventually assured, when the sum of the last two terms of Equation (A4) is zero as

$$\frac{2}{\lambda_r}\Delta R_s p\hat{R_s} - [\boldsymbol{e}_r^T \Delta A_2 \hat{\boldsymbol{x}}_2 + \hat{\boldsymbol{x}}_2^T \Delta A_2^T \boldsymbol{e}_r] = 0$$

(A5)

which leads to

$$\hat{R}_s = -\frac{\lambda_r}{2} \int \epsilon_{R_s} dt \tag{A6}$$

where the tuning signal  $\epsilon_{R_S}$  is

$$\epsilon_{R_S} = \hat{i}_{sz1}(i_{sz1} - \hat{i}_{sz1}) + \hat{i}_{sz2}(i_{sz2} - \hat{i}_{sz2}) \tag{A7}$$

A PI regulator is employed to enhance the dynamic behaviour of the proposed estimator, instead of Equation (A6) as

$$\hat{R}_s = K_{pr}\epsilon_{R_s} + K_{ir}\int\epsilon_{R_s}dt \tag{A8}$$

where  $K_{ir}$  and  $K_{pr}$  are the integral and proportional constants.

#### Appendix B. The Design of Adaption Law for Speed Estimation

The Lyapunov candidate function for asymptotic stability of the speed estimation system is

$$\boldsymbol{V}_{\omega} = \boldsymbol{e}_{\omega}^{T} \boldsymbol{e}_{\omega} + \frac{\Delta \omega_{r}^{2}}{\lambda_{\omega}} \tag{A9}$$

where  $\lambda_{\omega}$  is a positive constant,  $\Delta \omega_r = \hat{\omega}_r - \omega_r$ , and  $e_{\omega}$  is the error matrix of the estimated and real values in  $\alpha - \beta$  subspace as

$$e_{\omega} = x_1 - \hat{x}_1$$

$$= \begin{bmatrix} i_{s\alpha} - \hat{i}_{s\alpha} & i_{s\beta} - \hat{i}_{s\beta} & \psi_{r\alpha} - \hat{\psi}_{r\alpha} & \psi_{r\beta} - \hat{\psi}_{r\beta} \end{bmatrix}^T$$

(A10)

In this case, the first-order time derivative of Lyapunov function can be deduced as

$$pV_{\omega} = e_{\omega}^{T} [(A_1 - G_1C_1) + (A_1 - G_1C_1)^{T}] e_{\omega}$$

$$+ (e_{\omega} \Delta A_2 \hat{x}_2 + \hat{x}_2 \Delta A^{T} e_{\omega}) + \frac{2}{\lambda_{\omega}} \Delta \omega_r p \hat{\omega}_r$$

(A11)

The first term of Equation (A11) is guaranteed to be negative definite by suitable adopting of observer gain matrix  $G_1$ . The Lyapunov stability criterion is satisfied, if the sum of second and third terms of Equation (A11) is zero. With some calculations, the adaptation law for speed estimator is acquired as

$$\hat{\omega}_r = K_{p\omega}\epsilon_\omega + K_{i\omega}\int\epsilon_\omega dt \tag{A12}$$

where the tuning signal  $\epsilon_{\omega}$  is

$$\epsilon_{\omega} = (i_{s\alpha} - \hat{i}_{s\alpha})\hat{\psi}_{r\beta} - (i_{s\beta} - \hat{i}_{s\beta})\hat{\psi}_{r\alpha} \tag{A13}$$

#### References

- Levi, E.; Bojoi, R.; Profumo, F.; Toliyat, H.A.; Williamson, S. Multiphase induction motor drives—A technology status review. *IET Electr. Power Appl.* 2007, 1, 489–516. [CrossRef]

- Heidari, H.; Rassölkin, A.; Vaimann, T.; Kallaste, A.; Taheri, A.; Holakooie, M.H.; Belahcen, A. A novel vector control strategy for a six-phase induction motor with low torque ripples and harmonic currents. *Energies* 2019, 12, 1102. [CrossRef]

- Levi, E. Multiphase Electric Machines for Variable-Speed Applications. *IEEE Trans. Ind. Electron.* 2008, 55, 1893–1909. [CrossRef]

- Holakooie, M.H.; Ojaghi, M.; Taheri, A. Direct Torque Control of Six-Phase Induction Motor With a Novel MRAS-Based Stator Resistance Estimator. *IEEE Trans. Ind. Electron.* 2018, 65, 7685–7696. [CrossRef]

- Che, H.S.; Duran, M.J.; Levi, E.; Jones, M.; Hew, W.P.; Rahim, N.A. Postfault Operation of an Asymmetrical Six-Phase Induction Machine With Single and Two Isolated Neutral Points. *IEEE Trans. Power Electron.* 2014, 29, 5406–5416. [CrossRef]

- Lu, H.; Li, J.; Qu, R.; Ye, D. Fault-tolerant predictive current control with two-vector modulation for six-phase permanent magnet synchronous machine drives. *IET Electr. Power Appl.* 2018, 12, 169–178. [CrossRef]

- Holakooie, M.H.; Ojaghi, M.; Taheri, A. Modified DTC of a Six-Phase Induction Motor With a Second-Order Sliding-Mode MRAS-Based Speed Estimator. *IEEE Trans. Power Electron.* 2019, 34, 600–611. [CrossRef]

- Bojoi, R.; Farina, F.; Griva, G.; Profumo, F.; Tenconi, A. Direct torque control for dual three-phase induction motor drives. *IEEE Trans. Ind. Appl.* 2005, 41, 1627–1636. [CrossRef]

- Singh, G.K.; Nam, K.; Lim, S.K. A simple indirect field-oriented control scheme for multiphase induction machine. *IEEE Trans. Ind. Electron.* 2005, 52, 1177–1184. [CrossRef]

- Gregor, R.; Barrero, F.; Toral, S.L.; Duran, M.J.; Arahal, M.R.; Prieto, J.; Mora, J.L. Predictive-space vector PWM current control method for asymmetrical dual three-phase induction motor drives. *IET Electr. Power Appl.* 2010, 4, 26–34. [CrossRef]

- Zaid, S.A.; Mahgoub, O.A.; El-Metwally, K.A. Implementation of a new fast direct torque control algorithm for induction motor drives. *IET Electr. Power Appl.* 2010, *4*, 305–313. [CrossRef]

- Hoang, K.D.; Ren, Y.; Zhu, Z.Q.; Foster, M. Modified switching-table strategy for reduction of current harmonics in direct torque controlled dual-three-phase permanent magnet synchronous machine drives. *IET Electr. Power Appl.* 2015, 9, 10–19. [CrossRef]

- Tatte, Y.N.; Aware, M.V. Torque Ripple and Harmonic Current Reduction in a Three-Level Inverter-Fed Direct-Torque-Controlled Five-Phase Induction Motor. *IEEE Trans. Ind. Electron.* 2017, 64, 5265–5275. [CrossRef]

- Rassölkin, A.; Vaimann, T.; Kallaste, A.; Kuts, V. Digital twin for propulsion drive of autonomous electric vehicle. In Proceedings of the 2019 IEEE 60th International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON), Riga, Latvia, 7–9 October 2019; pp. 1–4.

- Kuts, V.; Tahemaa, T.; Otto, T.; Sarkans, M.; Lend, H. Robot manipulator usage for measurement in production areas. J. Mach. Eng. 2016, 16, 57–67.

- Sell, R.; Leier, M.; Rassõlkin, A.; Ernits, J.P. Self-driving car ISEAUTO for research and education. In Proceedings of the 2018 19th International Conference on Research and Education in Mechatronics (REM), Delft, The Netherlands, 7–8 June 2018; pp. 111–116.

- 17. Rassölkin, A.; Sell, R.; Leier, M. Development case study of the first estonian self-driving car, iseauto. *Electr. Control Commun. Eng.* **2018**, *14*, 81–88. [CrossRef]

- Kumar, R.; Das, S.; Syam, P.; Chattopadhyay, A.K. Review on model reference adaptive system for sensorless vector control of induction motor drives. *IET Electr. Power Appl.* 2015, 9, 496–511. [CrossRef]

- Gadoue, S.M.; Giaouris, D.; Finch, J.W. Stator current model reference adaptive systems speed estimator for regenerating-mode low-speed operation of sensorless induction motor drives. *IET Electr. Power Appl.* 2013, 7, 597–606. [CrossRef]

- Rashed, M.; Stronach, A.F. A stable back-EMF MRAS-based sensorless low-speed induction motor drive insensitive to stator resistance variation. *IEE Proc. Electr. Power Appl.* 2004, 151, 685–693. [CrossRef]

- Holakooie, M.H.; Taheri, A.; Sharifian, M.B. MRAS Based Speed Estimator for Sensorless Vector Control of a Linear Induction Motor with Improved Adaptation Mechanisms. J. Power Electron. 2015, 15, 1274–1285. [CrossRef]

- Holakooie, M.H.; Ojaghi, M.; Taheri, A. Full-order Luenberger observer based on fuzzy-logic control for sensorless field-oriented control of a single-sided linear induction motor. *ISA Trans.* 2016, 60, 96–108. [CrossRef]

- Habibullah, M.; Lu, D.D.C. A Speed-Sensorless FS-PTC of Induction Motors Using Extended Kalman Filters. *IEEE Trans. Ind. Electron.* 2015, 62, 6765–6778. [CrossRef]

- 24. Lee, K.B.; Blaabjerg, F. Sensorless DTC-SVM for Induction Motor Driven by a Matrix Converter Using a Parameter Estimation Strategy. *IEEE Trans. Ind. Electron.* **2008**, *55*, 512–521. [CrossRef]

- Lascu, C.; Boldea, I.; Blaabjerg, F. Direct torque control of sensorless induction motor drives: A sliding-mode approach. *IEEE Trans. Ind. Appl.* 2004, 40, 582–590. [CrossRef]

- Han, J. From PID to Active Disturbance Rejection Control. *IEEE Trans. Ind. Electron.* 2009, 56, 900–906. [CrossRef]

- 27. Mahmudizad, M.; Ahangar, R.A. Improving load frequency control of multi-area power system by considering uncertainty by using optimized type 2 fuzzy pid controller with the harmony search algorithm. *World Acad. Sci. Eng. Technol.* **2016**, *10*, 1051–1061.

- Wang, G.; Wang, B.; Li, C.; Xu, D. Weight-transducerless control strategy based on active disturbance rejection theory for gearless elevator drives. *IET Electr. Power Appl.* 2017, *11*, 289–299. [CrossRef]

- Li, J.; Ren, H.P.; Zhong, Y.R. Robust Speed Control of Induction Motor Drives Using First-Order Auto-Disturbance Rejection Controllers. *IEEE Trans. Ind. Appl.* 2015, 51, 712–720. [CrossRef]

- Alonge, F.; Cirrincione, M.; D'Ippolito, F.; Pucci, M.; Sferlazza, A. Robust Active Disturbance Rejection Control of Induction Motor Systems Based on Additional Sliding-Mode Component. *IEEE Trans. Ind. Electron.* 2017, 64, 5608–5621. [CrossRef]

- Zhao, Y.; Lipo, T.A. Space vector PWM control of dual three-phase induction machine using vector space decomposition. *IEEE Trans. Ind. Appl.* **1995**, *31*, 1100–1109. [CrossRef]

- Kubota, H.; Matsuse, K. Speed sensorless field-oriented control of induction motor with rotor resistance adaptation. *IEEE Trans. Ind. Appl.* 1994, 30, 1219–1224. [CrossRef]

- Wang, K.; Chen, B.; Shen, G.; Yao, W.; Lee, K.; Lu, Z. Online updating of rotor time constant based on combined voltage and current mode flux observer for speed-sensorless AC drives. *IEEE Trans. Ind. Electron.* 2014, 61, 4583–4593. [CrossRef]

- Yin, Z.; Zhang, Y.; Du, C.; Liu, J.; Sun, X.; Zhong, Y. Research on Anti-Error Performance of Speed and Flux Estimation for Induction Motors Based on Robust Adaptive State Observer. *IEEE Trans. Ind. Electron.* 2016, 63, 3499–3510. [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

## Article Adaptive Maximum Torque per Ampere Control of Sensorless Permanent Magnet Motor Drives

Anton Dianov<sup>1</sup> and Alecksey Anuchin<sup>2,\*</sup>

- <sup>1</sup> Home Appliances Division, Samsung Electronics, Suwon 16677, Korea; anton.dianov@samsung.com

- <sup>2</sup> Electric Drives Department, Moscow Power Engineering Institute, 111250 Moscow, Russia

- \* Correspondence: anuchinas@mpei.ru

Received: 16 August 2020; Accepted: 24 September 2020; Published: 27 September 2020

Abstract: Interior permanent magnet synchronous motor (IPMSM) efficiency can be improved by using maximum torque per ampere control (MTPA). MTPA control utilizes both alignment and reluctance torques and usually requires information about the magnetization map of the electrical machine. This paper proposes an adaptive MTPA algorithm for sensorless control systems of IPMSM drives, which is applicable in industrial and commercial drives. This algorithm enhances conventional control schemes, where the output of the speed controller is the commanded stator current and the direct current is calculated using an MTPA equation; therefore, it can be easily implemented in the previously developed drives. The proposed algorithm does not use any motor parameters for the calculation of the MTPA trajectory, which is important for systems operating in changing environmental conditions, because motor inductances and flux linkage strongly depend on the stator current and the rotor temperature, respectively. The proposed algorithm continuously varies the current phase and in such a way it tries to minimize the magnitude of the stator current at the applied load torque. The main contribution of this paper is the development of a technique to overcome the main disadvantage of seeking algorithms—the necessity of a precision information about the rotor position. The proposed method was verified experimentally.

Keywords: interior permanent magnet motors; maximum torque per ampere; sensorless control; adaptive control

#### 1. Introduction

Interior permanent magnet synchronous motors (IPMSM), compared with machines of other types, have higher torque to weight ratios, higher efficiency, output power per volume and mass per volume values, which make them attractive for use in compact drives, high-efficient drives, drives with high dynamics, etc. At the same time, the high price of rare-earth metals, which are necessary for producing strong magnets, restricts the popularity of permanent magnet (PM) motors. However, over the past decade, the price of rare-earth magnets has decreased; therefore, the area usage of PM motors is widening. As a result, they attract more attention, and many researchers have investigated the control systems of these machines.

The main feature of IPMSMs is their asymmetry along direct and quadrature axes, which creates reluctance torque. At the same time, permanent magnet synchronous machines (PMSM), which have equal direct and quadrature inductance and idle load conditions, demonstrate magnetic asymmetry at load; thus, they may also produce reluctance torque. As a result, modern efficient control systems must consider these facts and utilize the reluctance torque of the PM motors by employing one of the maximum torque per ampere (MTPA) techniques.

Information on rotor position is required to control PM motors; therefore, precision and high-performance drives are equipped with position encoders, whose resolution depends on the desired dynamic and precision of control. At the same time, low-cost systems and motor drives with higher reliability have a tendency to eliminate additional parts, especially moving parts, such as speed and position encoders. Therefore, sensorless control algorithms have almost become a standard in these applications [1,2]. Therefore, modern control systems of PM motors, in order to be used in a variety of applications, have to be sensorless [3] and must be able to implement MTPA techniques [4,5].

An analysis of the operating conditions of PM motors and their impact on the motor parameters showed that motor direct and quadrature inductances strongly depend on the motor stator current and may decrease due to steel saturation by more than 50% [6]. At the same time, the temperature of the rotor impacts the flux linkage of magnets and may decrease it by 10% [7]. Furthermore, magnet degradation during the lifetime of the motor may also decrease the flux linkage by 15%. As a result, it would be beneficial to develop an MTPA algorithm, which can adapt to the variations in motor parameter and provide efficient control of the motor, despite its environment.

The conventional MTPA approach involves the calculation of one of the MTPA equations—e.g., Equation (1) obtained from motor equations:

$$\dot{u}_d = -rac{\psi_m}{4(L_d - L_q)} - \sqrt{rac{\psi_m^2}{16(L_d - L_q)^2} + rac{I_s^2}{2}},$$

(1)

where  $I_s$  represents the stator current,  $\psi_m$  represents the permanent magnet flux linkage,  $L_d$  and  $L_q$  represent the d-axis and q-axis inductances, respectively, and  $i_d$  stands for the direct current component providing the MTPA. This approach is simple and can be easily implemented in a sensorless control systems and is discussed and studied in [8–12]; however, such techniques are sensitive to the variation in motor parameter due to operating conditions. For example, the accurate knowledge of motor parameters was required in [10], but the change in the motor inductances due to the saturation effect was not taken into account.

To solve this problem, different adaptive MTPA techniques were proposed. The authors of [13,14] proposed to enhance the conventional MTPA algorithm with on-line estimation techniques of motor inductances; however, these papers do not suggest a solution for the flux-linkage estimation. Furthermore, these methods need fine-tuning, and the control system has to be equipped with a high-speed processor capable of executing additional calculations at every calculation step, together with basic control routines.

The authors of [15] proposed a method with a fast dynamic response, which uses a recursive least squares (RLS) parameters estimator to track the MTPA trajectory. However, this method calculates many square roots, which significantly load a microcontroller unit (MCU), even with optimizations; therefore, the use of this method is limited.

A group of methods described in [16,17] proposes several similar MTPA techniques which are based on the high-frequency signal injection and the analysis of response. These methods do not need motor parameters, but high-frequency signals cause noises and vibrations, which are undesirable in many drives.

To overcome this problem, the authors of [18–21] proposed an interesting technique called the virtual signal injection (VSI). This method detects the MTPA trajectory analytically by the injection of a virtual signal into a motor model. It does not use motor parameters and does not inject real signals into the system; therefore, undesired noise and vibrations are excluded. However, despite perfect reported results of VSI methods, we do not share the optimism of the authors. We found that these algorithms were very sensitive to the variation in stator resistance, which is not a problem in other algorithms, including the conventional one.

Another approach used for tracking the MTPA trajectory is seeking algorithms, which do not use motor parameters and can effectively operate in a changing environment. An example of this technique is described in [22], where the authors continuously varied the phases of the stator current and tracked the minimum of the current magnitude. The main disadvantages of this idea are lower dynamics and the necessity of a position encoder.

After a detailed analysis of the pros and cons of the existing techniques, the authors found that the seeking algorithm reported in [22] is the best candidate for developing a motor drive, provided that it can be adapted to the operation without a position encoder.

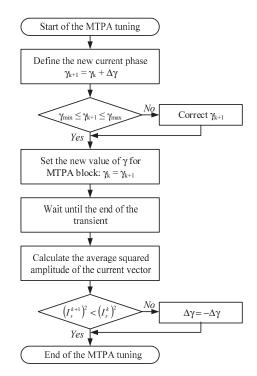

#### 2. MTPA Seeking Algorithm

The seeking algorithm reported in [22], which was selected for further improvements, continuously varies the phase of the stator current  $\gamma$  to provide the minimum stator current  $I_s$  for the given torque. The flowchart of this method is shown in Figure 1. It can be clearly seen that in each calculation step, the motor phase is modified by a small disturbance angle  $\Delta \gamma$ , and the resulting value  $\gamma$  is checked to be inside the limits. After that, the new value of the phase of the stator current is applied, and the control system waits until the end of transient. After that, the tuning algorithm measures the average magnitude of the stator current over the calculation step and compares it to the value measured at the previous step.

Figure 1. Flowchart of the MTPA seeking algorithm.

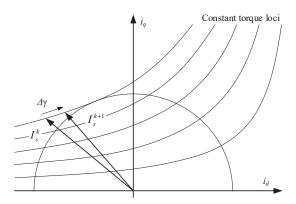

If the current value obtained at the current calculation step is less than the same value from the previous step, the stator current has been rotated in the correct direction, and vice versa. If the stator current has been rotated to the incorrect direction, the sign of disturbance value  $\Delta\gamma$  is reversed, and in the next step the stator vector will be rotated in the proper direction. This process is illustrated in Figure 2, where the current vector rotates to track the constant torque loci.

Figure 2. Variation of stator current phase.

This seeking algorithm has the advantages of being insensitive to motor parameter variation and the possibility of being easily implemented in the previously developed control schemes.

At the same time, this technique demonstrates excellent results only when the rotor position is measured precisely, and may fail when a significant error appear. As can be seen from Figure 2, the minimum current for the constant torque curve is not strongly pronounced, and the variation of the stator current angle causes only minor changes to the current magnitude. This problem is illustrated by the data in Table 1, calculated for the test motor, the parameters of which are given in the section below. The table illustrates the increase in the magnitude of the stator current when its angle varies with the step of one degree. As can be seen, the variation in stator current is quite small and lies below one percent for a range of  $\pm 5^{\circ}$ . Therefore, to detect the minimum stator current, it is very important to know the rotor position precisely. Unfortunately, sensorless drives contain a position error with a typical value of  $5^{\circ}-10^{\circ}$ , which varies over revolution and restricts the operation of the seeking algorithm in sensorless systems. The original algorithm [22] at the calculation step k applies the stator current with a phase  $\gamma_k$ . In the next calculation step k + 1, the algorithm applies the stator current with a phase  $\gamma_{k+1}$ , which differs from the  $\gamma_k$  at the fixed disturbance angle  $\Delta \gamma$ . During each calculation step, the algorithm measures (integrates) the magnitude of the stator current and then compares these magnitudes. The lower current magnitude corresponds to the phase angle being closer to the true MTPA angle. Thus, if the position error is not constant, the stator current is applied at different phase angles during each calculation step; therefore, its magnitude varies, producing incorrect measurements of the current. In order to overcome this problem and use the advantages of the seeking technique, an advanced method was proposed, which makes the operation of the seeking algorithm in sensorless drives possible.

| Angle                | Increase, % | Angle                | Increase, % |

|----------------------|-------------|----------------------|-------------|

| $\gamma + 1^{\circ}$ | 0.02        | $\gamma - 1^{\circ}$ | 0.02        |

| $\gamma + 2^{\circ}$ | 0.09        | $\gamma - 2^{\circ}$ | 0.10        |

| $\gamma + 3^{\circ}$ | 0.19        | $\gamma - 3^{\circ}$ | 0.22        |

| $\gamma + 4^{\circ}$ | 0.33        | $\gamma - 4^{\circ}$ | 0.39        |

| $\gamma + 5^{\circ}$ | 0.56        | $\gamma - 5^{\circ}$ | 0.62        |

Table 1. Increase in Stator Current due to Angle Variation.

#### 3. Proposed Enhanced Algorithm

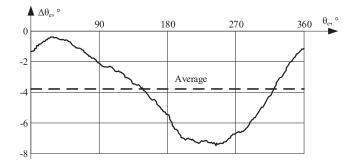

As mentioned earlier, the main problem with the implementation of the seeking algorithms in the sensorless systems is the absence of precision of information on the rotor position. The typical position estimation error of the back-EMF-based estimator is shown in Figure 3. This picture demonstrates

that the estimation error is significant for the seeking technique described. The proposed algorithm belongs to the perturb and observe methods, which involves modifying one parameter of the system and analyzing its response by measuring another parameter. Algorithms such as these may fail if another disturbance appears in the system and impacts the measured parameter. At the same time, our experiments showed that the average value of the position estimation error is stable and mainly depends on the variation in the relationship between the direct and quadrature inductances, while instant error depends on disturbance factors, such as cyclic mechanical load, non-sinusoidal back-emf, etc. Therefore, the previously developed seeking algorithm may operate properly if its calculation step contains an integer number of electrical revolutions. In that case, the average position error at consequent calculation steps will be the same, and the average current magnitudes may be compared. Stator resistance variation due to temperature change affects the average error value, but the seeking algorithm compensates for this error.

Figure 3. Rotor position estimation error.

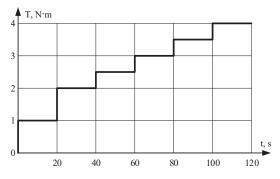

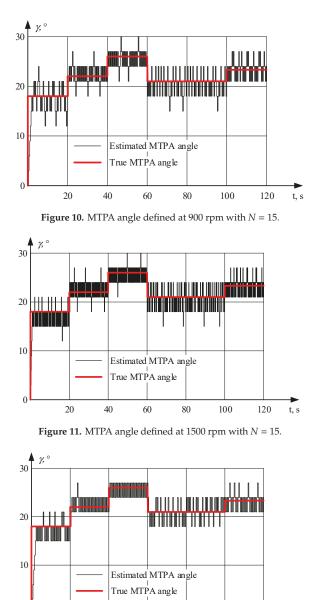

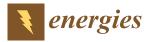

The number of electrical revolutions that are contained in one calculation step is denoted as *N*. Then, the maximum calculation time is denoted as  $T_{max}$ . These parameters define the minimum motor speed  $n_{min}$ , where the proposed algorithm can operate. If the motor speed *n* is less than the minimum speed  $n_{min}$ , the tuning algorithm must be stopped. Then, the length of the current calculation step  $T_{cs}^k$  is defined and compared to the length of the previous calculation step  $T_{cs}^{k-1}$ . If they are the same, the calculations at these intervals may be compared, otherwise they may not. If the consecutive calculation steps are different, the tuning algorithm calculates the squared amplitude of the stator current for the current measurement interval  $(I_s^k)^2$  and proceeds to the next step. If the length of the previous calculation step are the same, the tuning algorithm defines the new MTPA angle  $\gamma$  in the same manner as a basic algorithm, measures the squared amplitude of stator current  $(I_s^k)^2$ , and compares it to the same value from the previous iteration  $(I_s^{k-1})^2$ . If the squared amplitude of the stator current at the current step is less, it means that the MTPA angle  $\gamma$  was modified in the correct direction, and the same disturbance value will be applied in the next step. If the MTPA angle  $\gamma$  was modified in the wrong direction, then the sign of disturbance value  $\Delta\gamma$  in the next step will be reversed. A flowchart of the proposed algorithm is shown in Figure 4.

This algorithm is quite simple, and the most important things are the proper selection of N and  $T_{max}$ , which define the errors, the dynamic response of the algorithm, and its minimum operating speed. The higher the number of electrical revolutions in the calculation step, the more reliable and stable the algorithm operates; however, at the same time, its dynamic response decreases. These parameters are suggested to be selected experimentally by monitoring the performance of the tuning algorithm.

Figure 4. Flowchart of the proposed algorithm.

#### 4. Experimental Setup

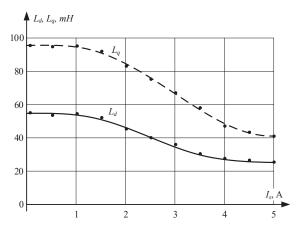

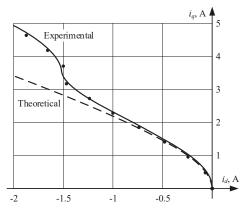

The experimental motor used in the experiments is the mass production (MP) device, the parameters of which are given in Table 2. However, these inductances strongly depend on the motor current and vary, as shown in Figure 5.

| Parameter         | Value  | Units   |

|-------------------|--------|---------|

| Number of poles   | 2P = 6 | -       |

| Rated speed       | 2000   | rpm     |

| Phase resistance  | 1.5    | Ohm     |

| d-axis inductance | 54     | mH      |

| q-axis inductance | 95     | mH      |

| Back-EMF constant | 0.15   | V·s/rad |

Table 2. Motor Rated Parameters.

Figure 5. Motor inductances vs. current.

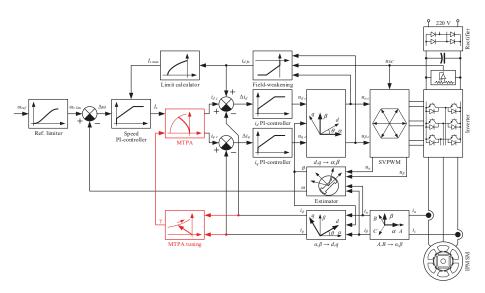

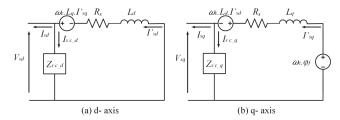

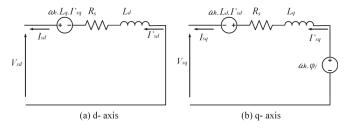

The control system used in the experiment is the same as in MP versions described in [23] (Figure 6). It drives the IPM motor, using the sensorless control, which nowadays can be considered to be a standard for many appliances. This control is based on the back-EMF estimation methods discussed in [24], which is enhanced by the initial position estimation necessary for excluding the reverse rotation while starting. The performance of the implemented estimation algorithm was verified using a quadrature encoder, which proved that the algorithm perfectly operates in the speed range over 10 Hz, with the estimation error being not more than several electrical degrees.

Figure 6. Structure of the sensorless control scheme of the IPM motor drive.

The inverter used for driving the motor is based on the smart power module FSAM10SH60 from "Fairchild" (10 A/600 V), which contains six IGBTs and embedded gate drivers. This drive was developed for a standard 220–240 V, 50/60 Hz supply source. The control system of the drive under test is based on a 60 MIPS Cortex-M3 microcontroller, which operates the inverter at 10 kHz PWM.

This system is equipped with two current sensors and a DC-link voltage sensor, whose signals are processed by a 12-bit ADC of the microcontroller, with a sampling time of 100  $\mu$ s.

The control system of the experimental drive is a conventional vector control system without the position encoder used in MP devices. It involves an outer speed loop and two inner current loops implemented in the dq reference frame, where the electrical position and speed are provided by the estimator. The experimental drive implements open-loop starting and acceleration with immediate closing and the reinitialization of the controllers.

The control system measures two phase currents and DC-link voltage, which are then transformed into phase currents and voltages, respectively. After that, the three phase values, *abc*, are converted into two axis stationary reference frames  $\alpha\beta$ , using the Clarke transformation:

$$\begin{bmatrix} X_{\alpha} \\ X_{\alpha} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} X_{\alpha} \\ X_{b} \\ X_{c} \end{bmatrix}$$

(2)

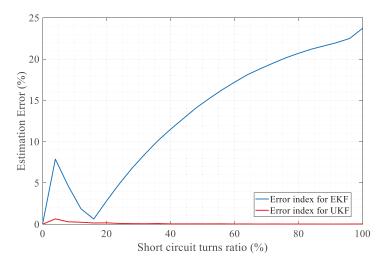

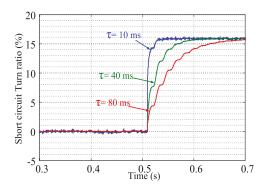

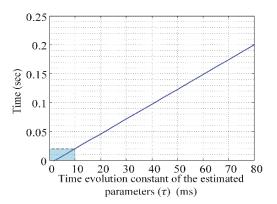

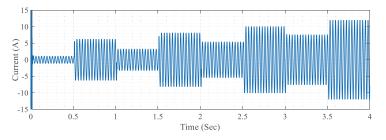

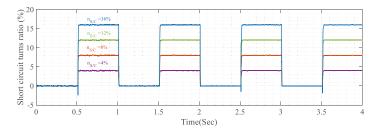

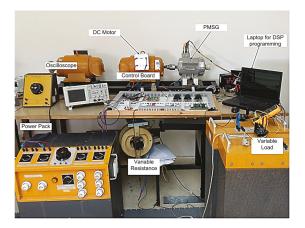

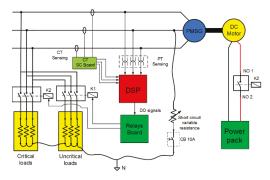

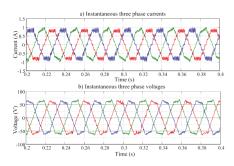

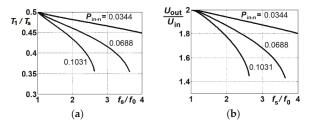

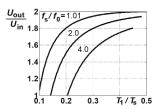

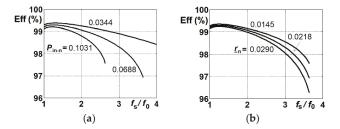

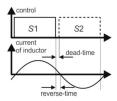

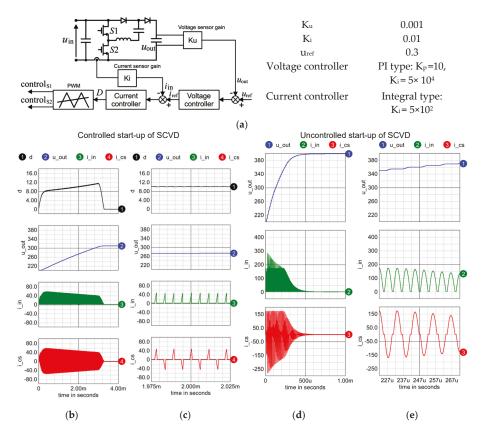

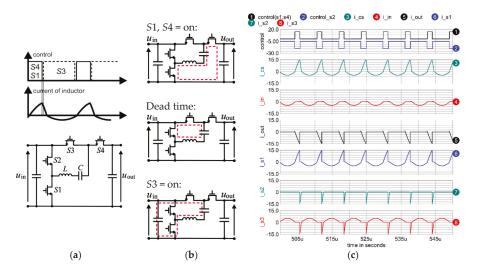

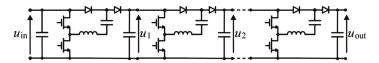

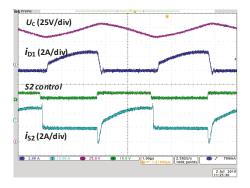

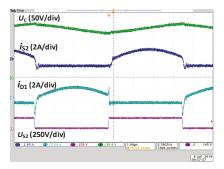

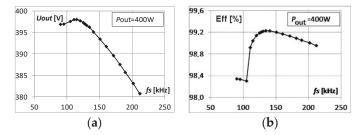

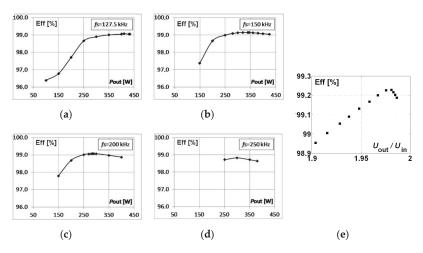

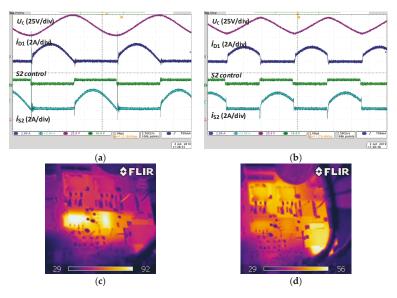

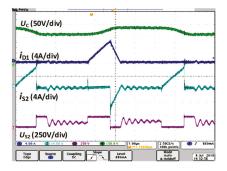

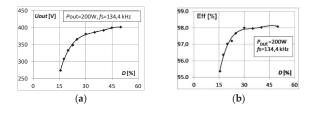

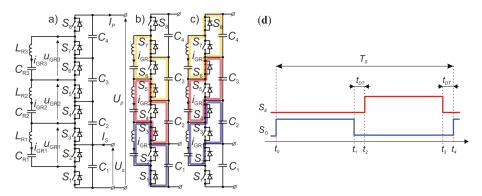

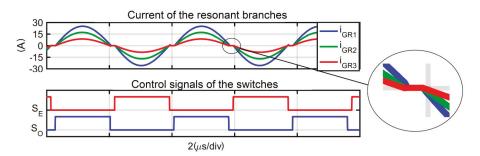

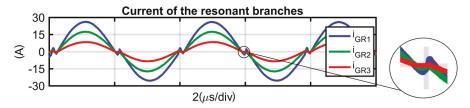

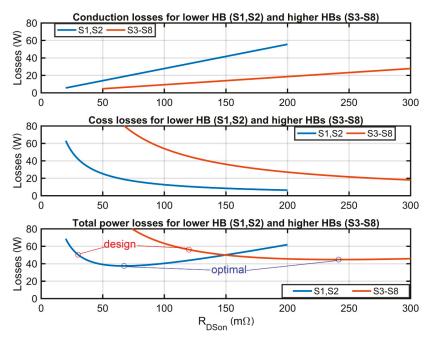

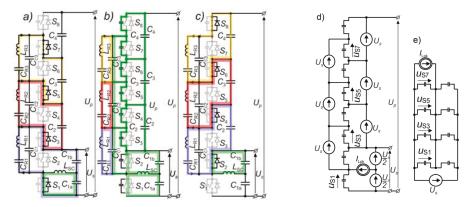

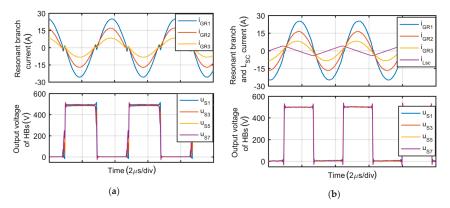

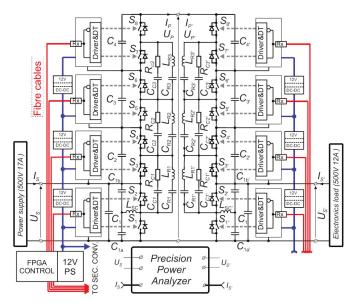

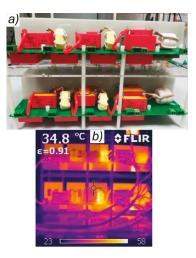

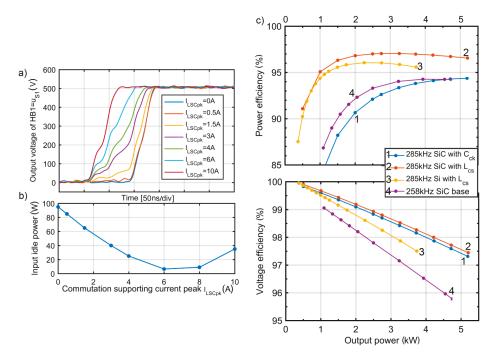

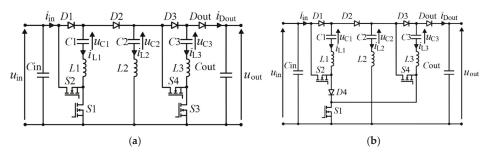

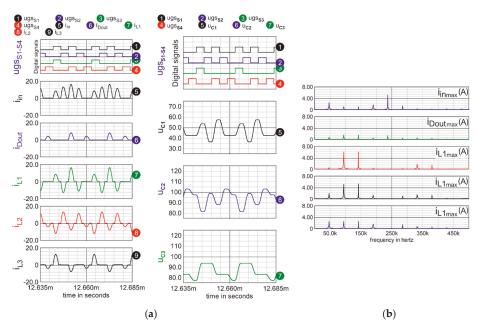

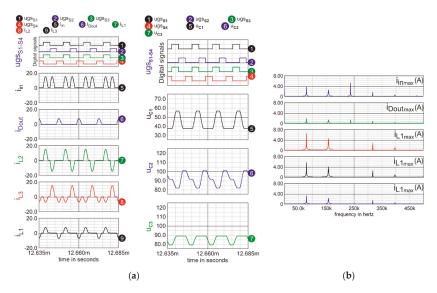

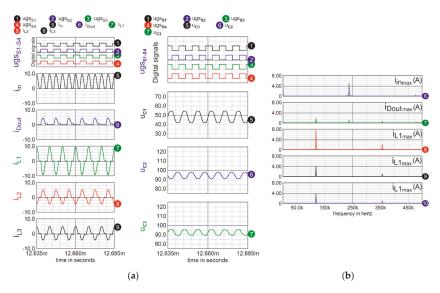

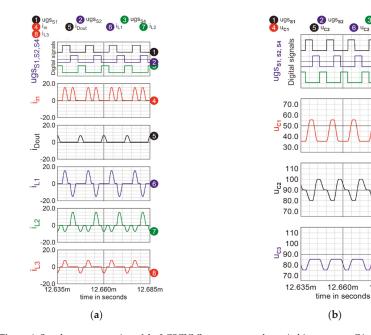

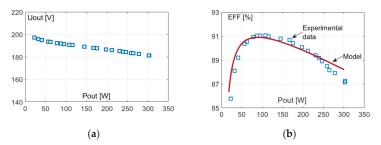

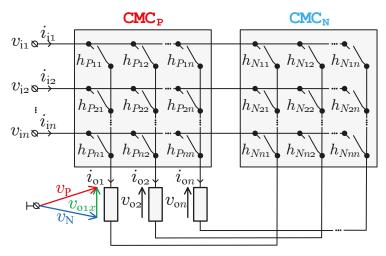

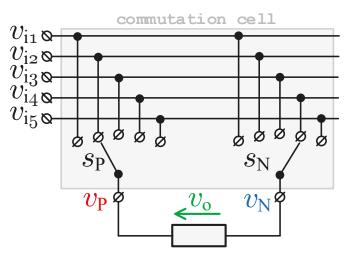

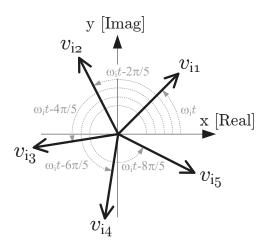

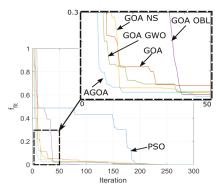

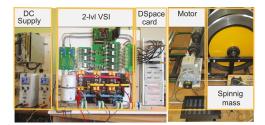

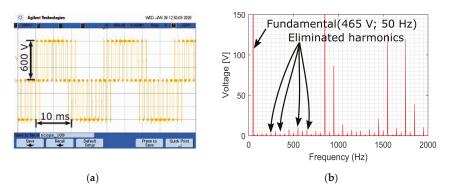

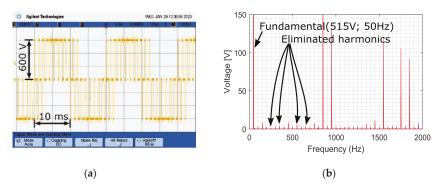

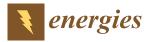

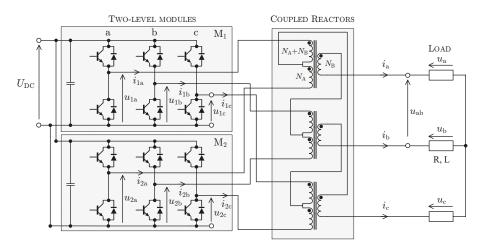

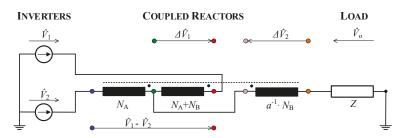

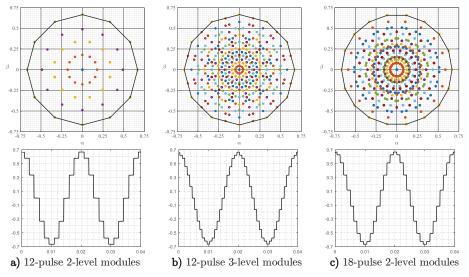

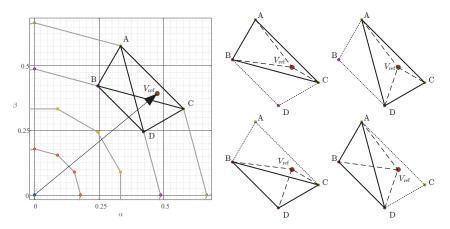

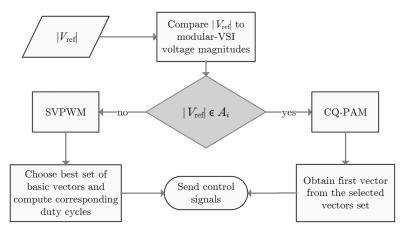

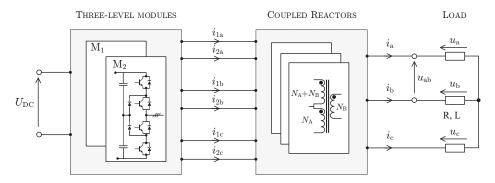

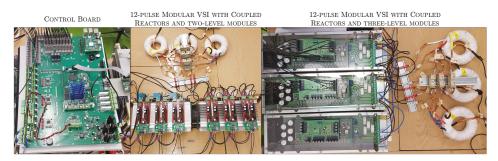

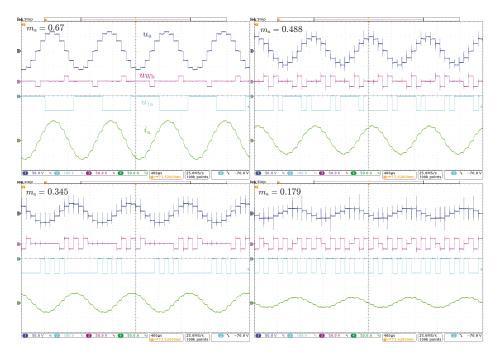

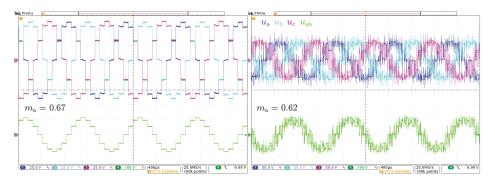

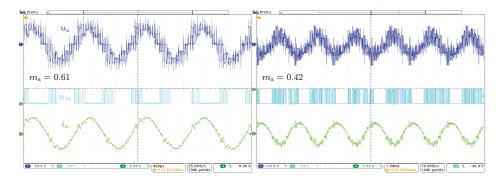

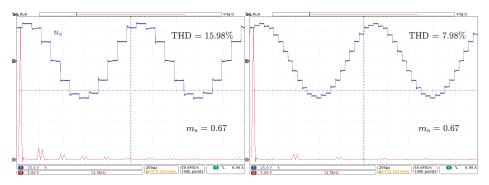

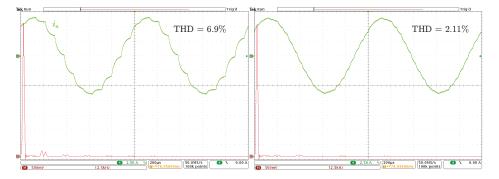

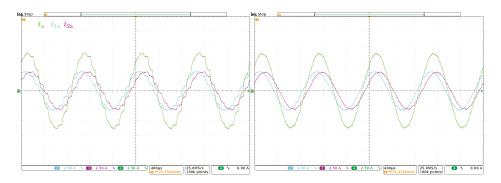

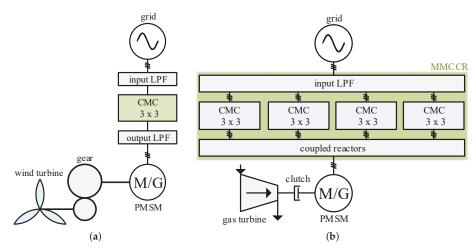

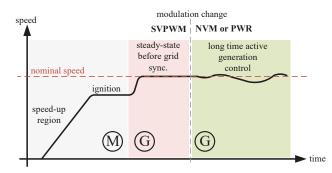

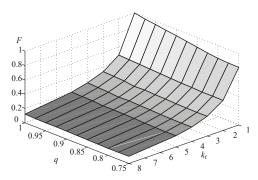

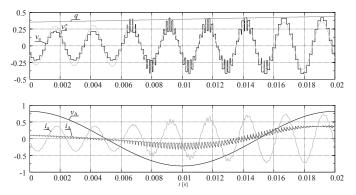

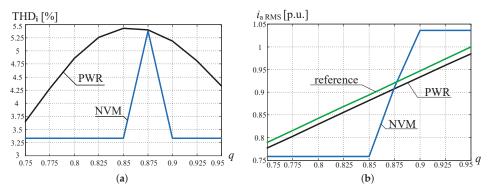

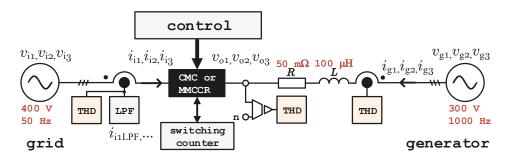

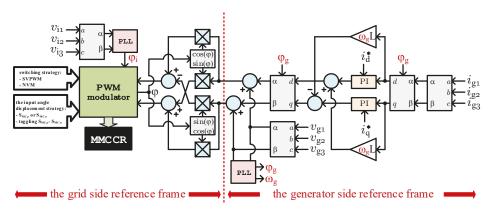

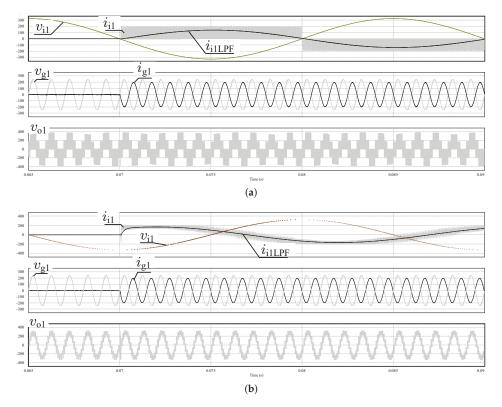

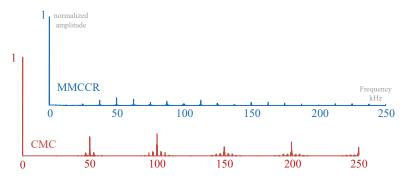

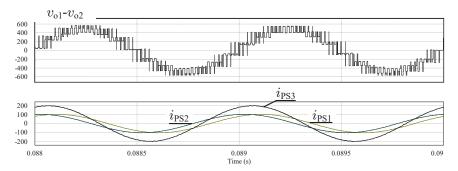

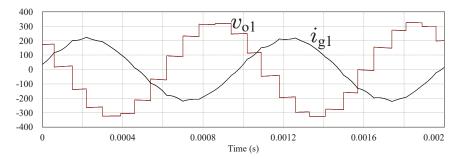

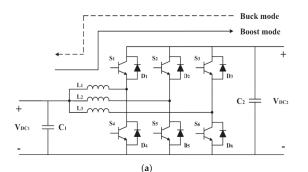

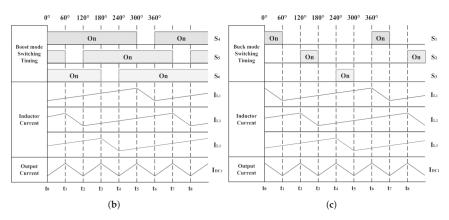

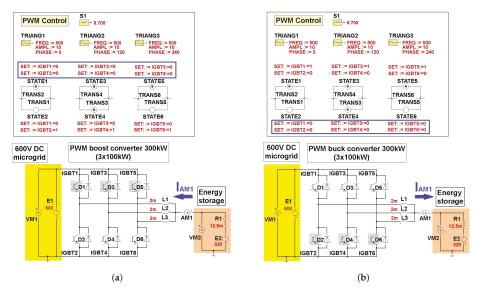

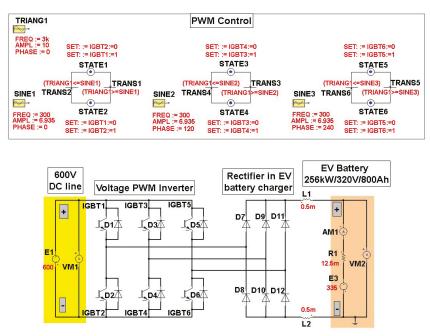

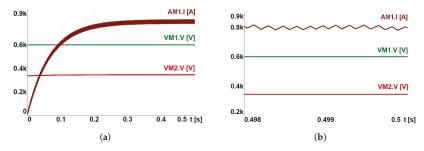

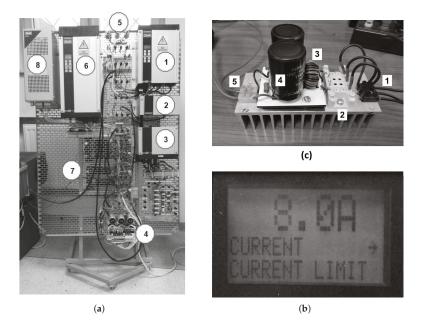

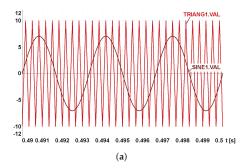

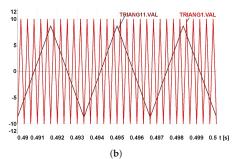

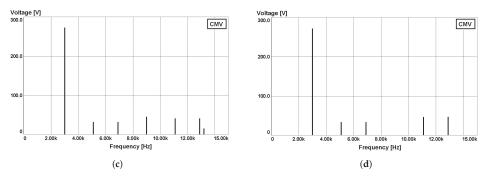

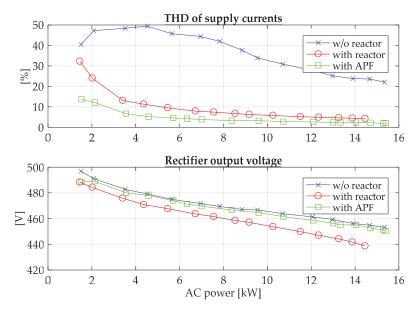

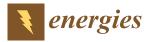

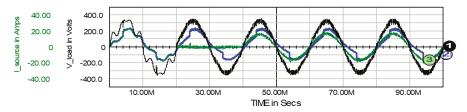

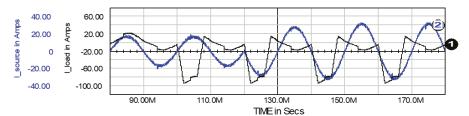

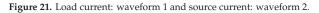

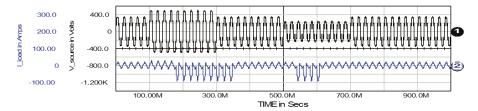

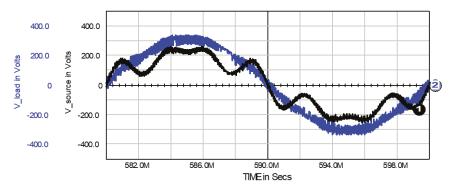

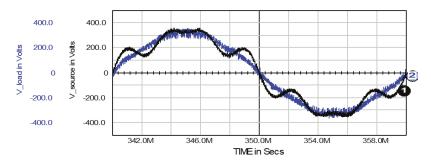

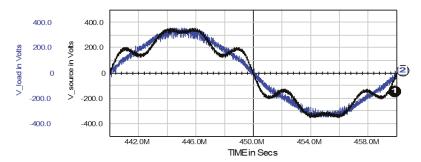

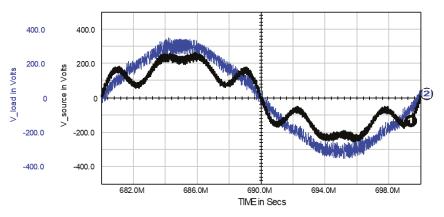

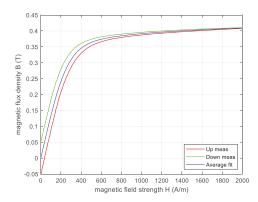

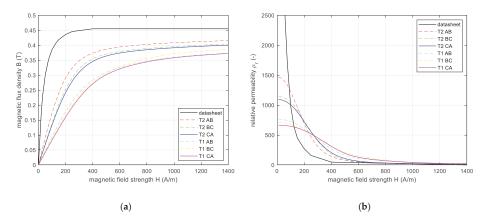

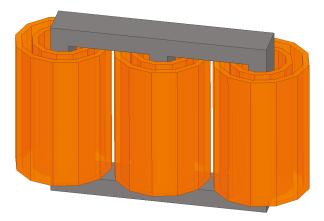

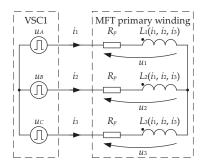

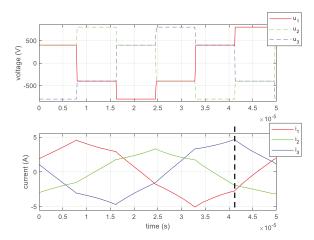

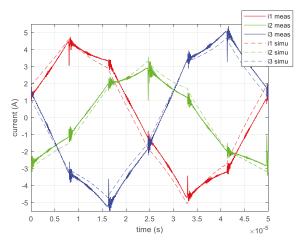

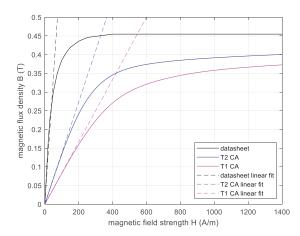

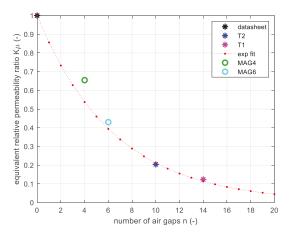

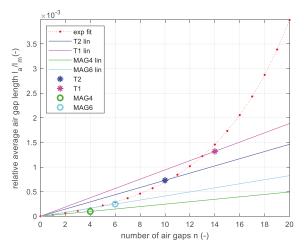

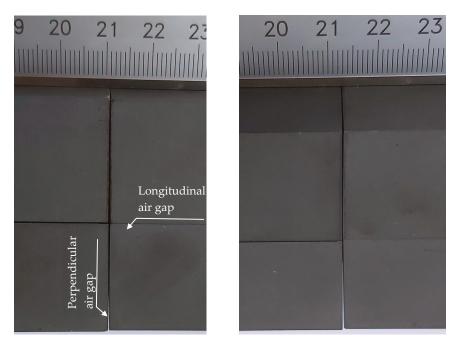

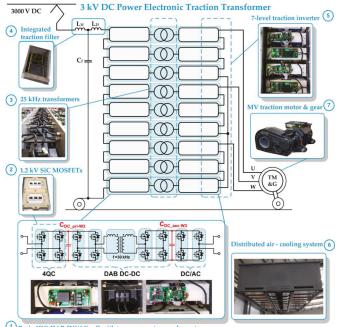

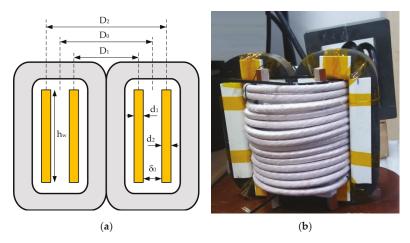

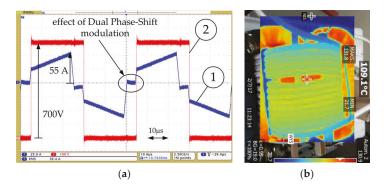

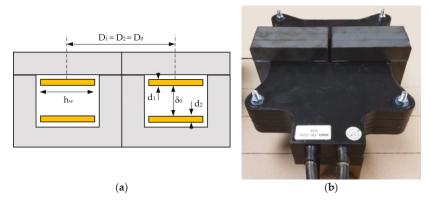

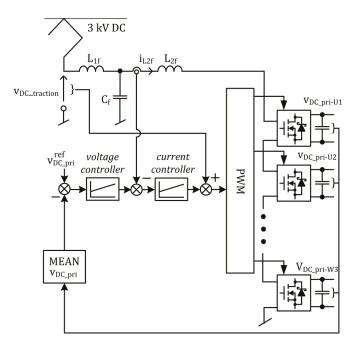

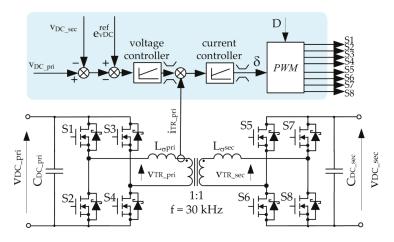

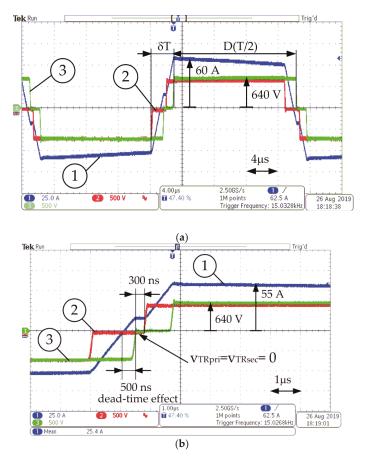

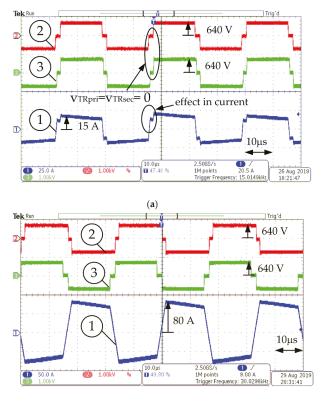

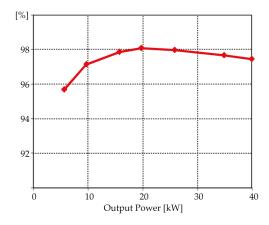

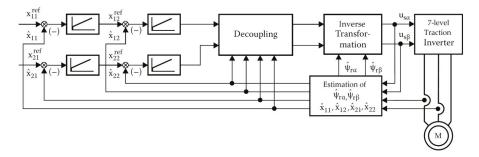

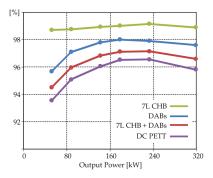

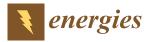

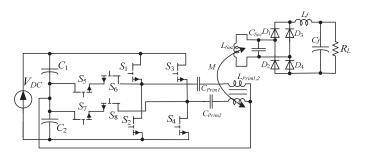

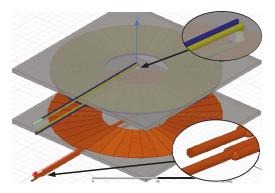

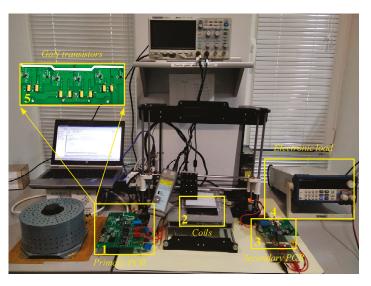

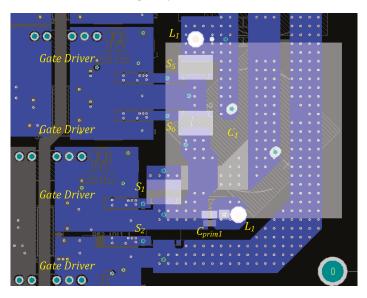

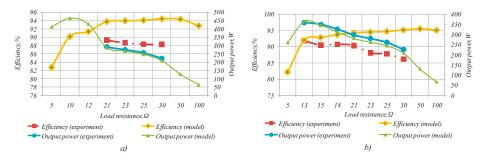

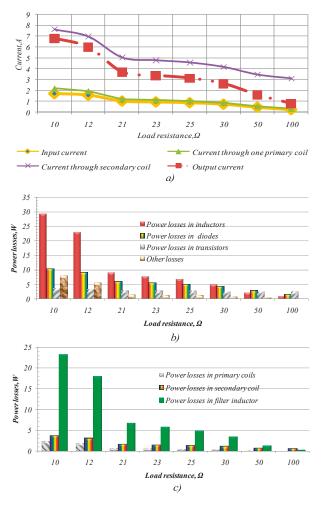

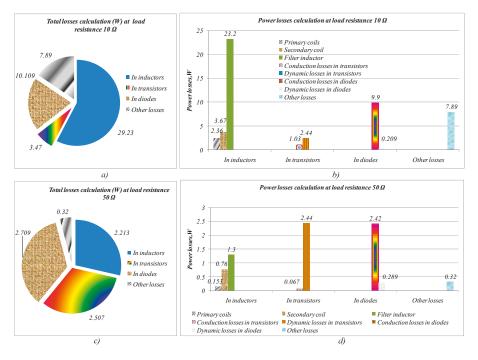

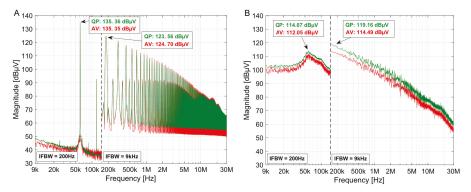

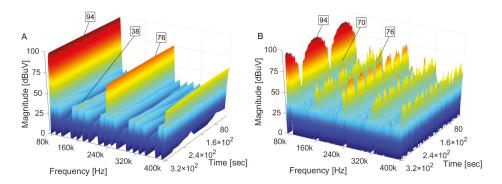

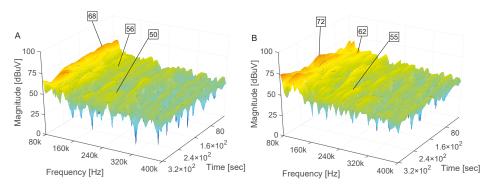

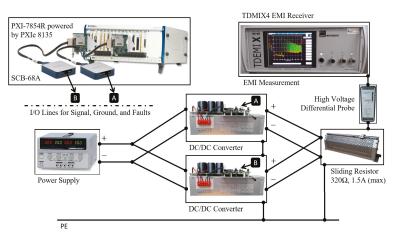

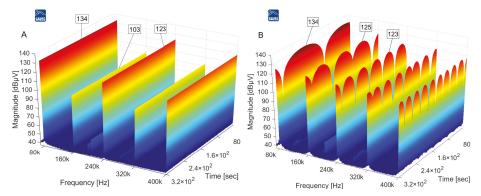

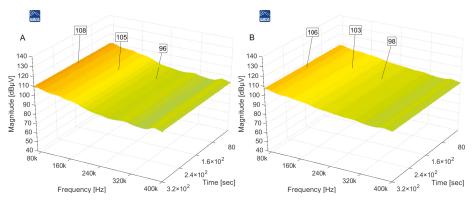

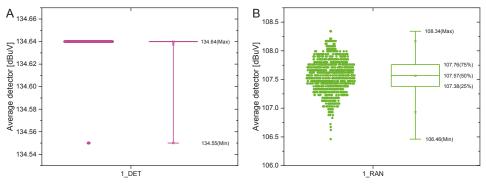

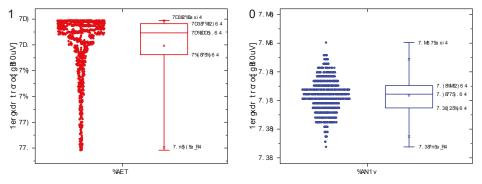

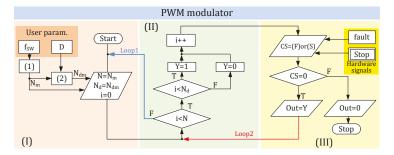

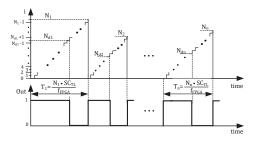

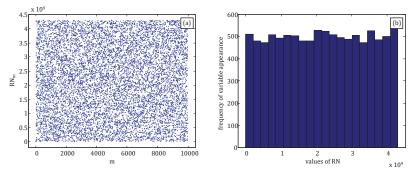

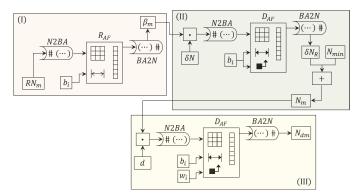

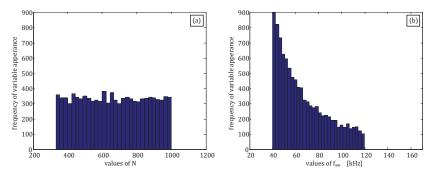

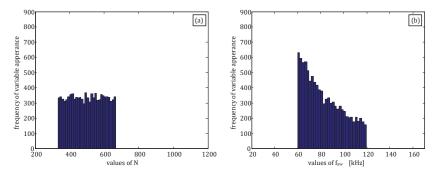

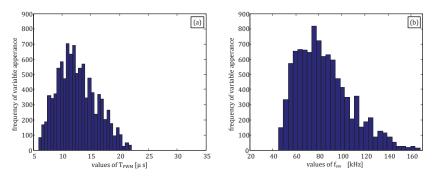

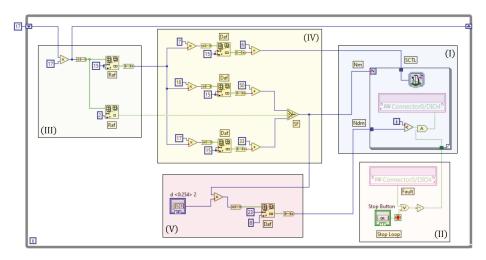

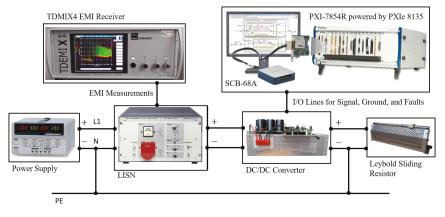

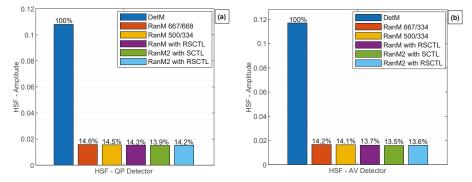

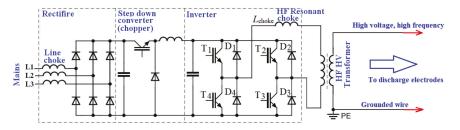

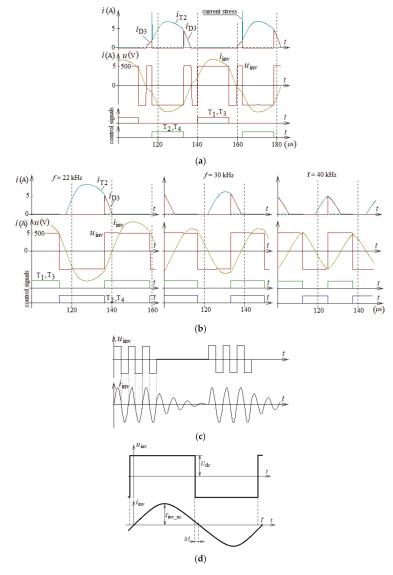

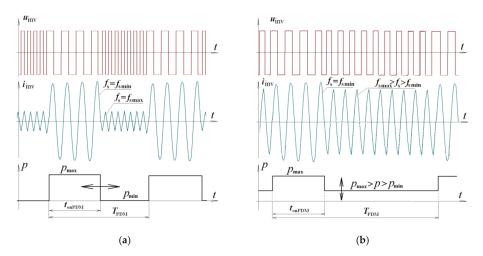

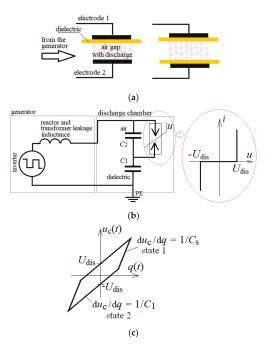

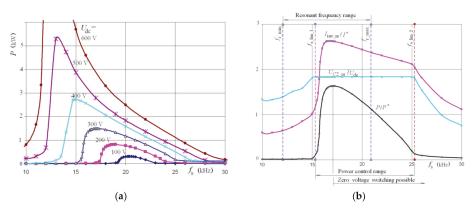

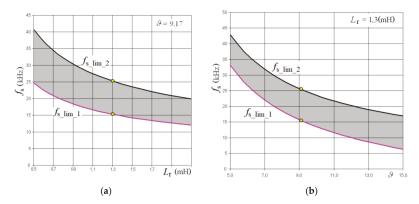

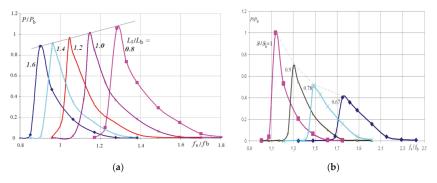

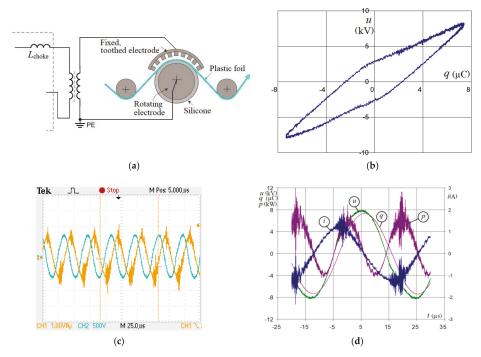

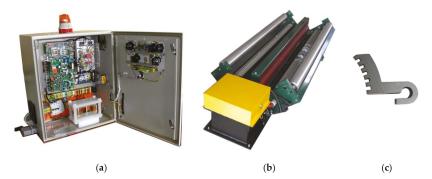

г. т.т. **Т**