# Wide Bandgap Based Devices Design, Fabrication and Applications, Volume II

Edited by

Giovanni Verzellesi

Printed Edition of the Special Issue Published in Micromachines

Wide Bandgap Based Devices: Design, Fabrication and Applications, Volume II

# Wide Bandgap Based Devices: Design, Fabrication and Applications, Volume II

Editor

Giovanni Verzellesi

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

Editor

Giovanni Verzellesi Department of Sciences and Methods for Engineering University of Modena and Reggio Emilia Reggio Emilia Italy

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Micromachines* (ISSN 2072-666X) (available at: www.mdpi.com/journal/micromachines/specialissues/Wide\_Bandgap\_Devices\_Volume\_II).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-3994-2 (Hbk) ISBN 978-3-0365-3993-5 (PDF)

© 2022 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

#### **Contents**

| About the Editor                                                                                                                                                                      | vii |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Giovanni Verzellesi                                                                                                                                                                   |     |

| Editorial for the Special Issue on Wide Bandgap Based Devices: Design, Fabrication and                                                                                                |     |

| Applications, Volume II                                                                                                                                                               | 1   |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 403, doi:10.3390/mi13030403                                                                                            | 1   |

| Justinas Jorudas, Artūr Šimukovič, Maksym Dub, Maciej Sakowicz, Paweł Prystawko and                                                                                                   |     |

| Simonas Indrišiūnas et al.                                                                                                                                                            |     |

| AlGaN/GaN on SiC Devices without a GaN Buffer Layer: Electrical and Noise Characteristics Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 1131, doi:10.3390/mi11121131 | 5   |

|                                                                                                                                                                                       |     |

| Tae-Hyeon Kim, Won-Ho Jang, Jun-Hyeok Yim and Ho-Young Cha                                                                                                                            |     |

| Unidirectional Operation of p-GaN Gate AlGaN/GaN Heterojunction FET Using Rectifying                                                                                                  |     |

| Drain Electrode Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 291, doi:10.3390/mi12030291                                                                            | 19  |

| Yu-Chun Huang, Hsien-Chin Chiu, Hsuan-Ling Kao, Hsiang-Chun Wang, Chia-Hao Liu and                                                                                                    |     |

| Chong-Rong Huang et al.                                                                                                                                                               |     |

| High Thermal Dissipation of Normally off p-GaN Gate AlGaN/GaN HEMTs on 6-Inch                                                                                                         |     |

| N-Doped Low-Resistivity SiC Substrate                                                                                                                                                 |     |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 509, doi:10.3390/mi12050509                                                                                            | 27  |

| Mohammad Abdul Alim, Christophe Gaquiere and Giovanni Crupi                                                                                                                           |     |

| An Experimental and Systematic Insight into the Temperature Sensitivity for a 0.15-m                                                                                                  |     |

| Gate-Length HEMT Based on the GaN Technology                                                                                                                                          |     |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 549, doi:10.3390/mi12050549                                                                                            | 33  |

| Meihua Liu, Yang Yang, Changkuan Chang, Lei Li and Yufeng Jin                                                                                                                         |     |

| Fabrication of All-GaN Integrated MIS-HEMTs with High Threshold Voltage Stability Using                                                                                               |     |

| Supercritical Technology                                                                                                                                                              |     |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 572, doi:10.3390/mi12050572                                                                                            | 45  |

| Nicolò Zagni, Alessandro Chini, Francesco Maria Puglisi, Paolo Pavan and Giovanni                                                                                                     |     |

| Verzellesi                                                                                                                                                                            |     |

| On the Modeling of the Donor/Acceptor Compensation Ratio in Carbon-Doped GaN to                                                                                                       |     |

| Univocally Reproduce Breakdown Voltage and Current Collapse in Lateral GaN Power HEMTs                                                                                                |     |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 709, doi:10.3390/mi12060709                                                                                            | 53  |

| Lung-Hsing Hsu, Yung-Yu Lai, Po-Tsung Tu, Catherine Langpoklakpam, Ya-Ting Chang and                                                                                                  |     |

| Yu-Wen Huang et al.                                                                                                                                                                   |     |

| Development of GaN HEMTs Fabricated on Silicon, Silicon-on-Insulator, and Engineered Substrates                                                                                       |     |

| and the Heterogeneous Integration                                                                                                                                                     |     |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 1159, doi:10.3390/mi12101159                                                                                           | 61  |

| Chao-Tsung Ma and Yi-Hung Tian                                                                                                                                                        |     |

| Design and Implementation of a SiC-Based VRFB Power Conditioning System                                                                                                               |     |

| Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 1099, doi:10.3390/mi11121099                                                                                           | 93  |

| Chao-Tsung Ma and Zhen-Huang Gu                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Review on Driving Circuits for Wide-Bandgap Semiconductor Switching Devices for Mid- to High-Power Applications                                                                                                                                        |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , 12, 65, doi:10.3390/mi12010065                                                                                                                                                                      |

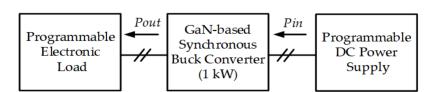

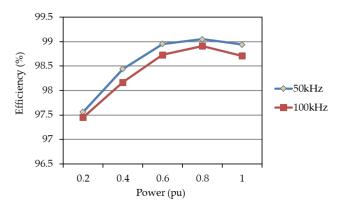

| Chao-Tsung Ma, Zhen-Yu Tsai, Hung-Hsien Ku and Chin-Lung Hsieh  Design and Implementation of a Flexible Photovoltaic Emulator Using a GaN-Based  Synchronous Buck Converter  Reprinted from: Micromachines 2021, 12, 1587, doi:10.3390/mi12121587      |

| Sang-Jo Kim, Semi Oh, Kwang-Jae Lee, Sohyeon Kim and Kyoung-Kook Kim                                                                                                                                                                                   |

| Improved Performance of GaN-Based Light-Emitting Diodes Grown on Si (111) Substrates with $NH_3$ Growth Interruption                                                                                                                                   |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 399, doi:10.3390/mi12040399                                                                                                                                                             |

| Yihsiang Chiu, Chen Wang, Dan Gong, Nan Li, Shenglin Ma and Yufeng Jin<br>A Novel Ultrasonic TOF Ranging System Using AlN Based PMUTs                                                                                                                  |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 284, doi:10.3390/mi12030284                                                                                                                                                             |

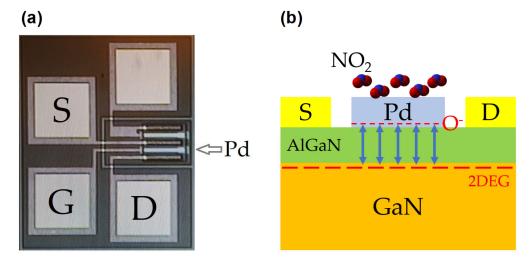

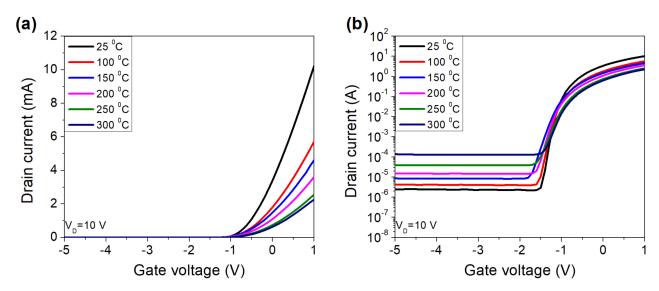

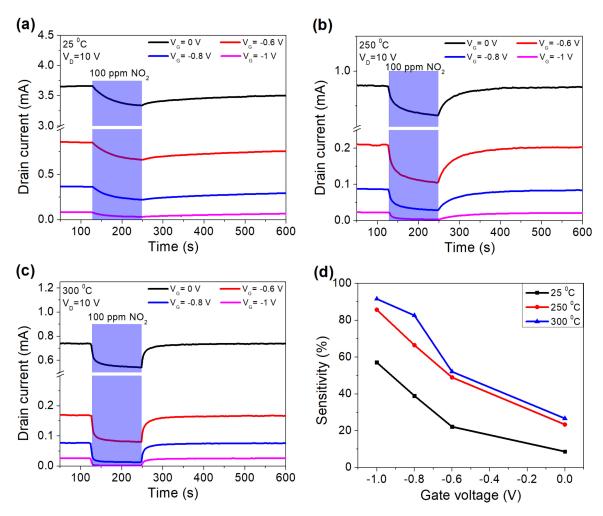

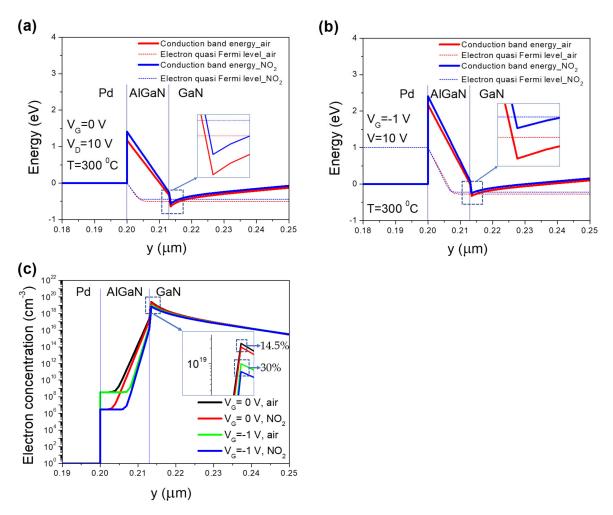

| Van Cuong Nguyen, Kwangeun Kim and Hyungtak Kim Performance Optimization of Nitrogen Dioxide Gas Sensor Based on Pd-AlGaN/GaN HEMTs by Gate Bias Modulation Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 400, doi:10.3390/mi12040400 |

| •                                                                                                                                                                                                                                                      |

| Stefan Thalhammer, Andreas Hörner, Matthias Küß, Stephan Eberle, Florian Pantle and Achim Wixforth et al.                                                                                                                                              |

| GaN Heterostructures as Innovative X-ray Imaging Sensors—Change of Paradigm Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 147, doi:10.3390/mi13020147                                                                                 |

| Simonas Indrišiūnas, Evaldas Svirplys, Justinas Jorudas and Irmantas Kašalynas  Laser Processing of Transparent Wafers with a AlGaN/GaN Heterostructures and  High-Electron Mobility Devices on a Backside                                             |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 407, doi:10.3390/mi12040407                                                                                                                                                             |

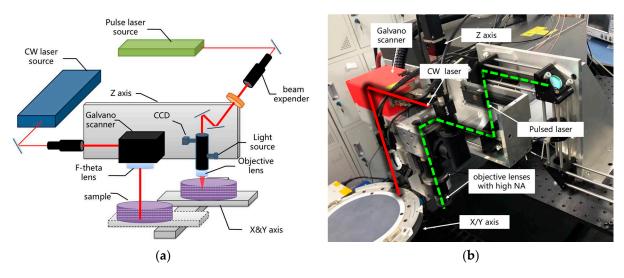

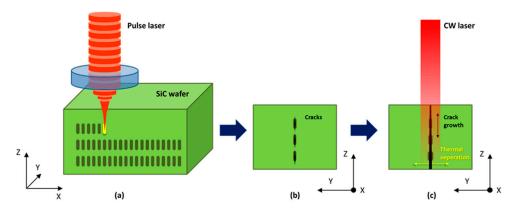

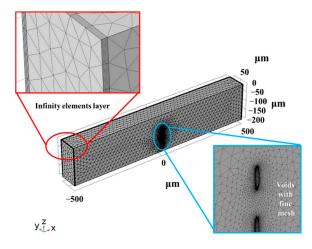

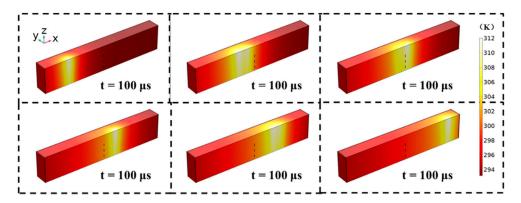

| Zhe Zhang, Zhidong Wen, Haiyan Shi, Qi Song, Ziye Xu and Man Li et al. Dual Laser Beam Asynchronous Dicing of 4H-SiC Wafer                                                                                                                             |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 1331, doi:10.3390/mi12111331                                                                                                                                                            |

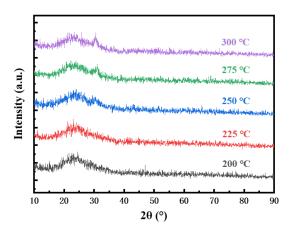

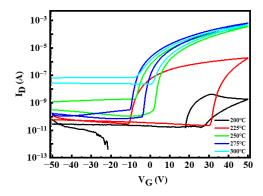

| Muyang Shi, Tian Qiu, Biao Tang, Guanguang Zhang, Rihui Yao and Wei Xu et al.  Temperature-Controlled Crystal Size of Wide Band Gap Nickel Oxide and Its Application in Electrochromism                                                                |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 80, doi:10.3390/mi12010080                                                                                                                                                              |

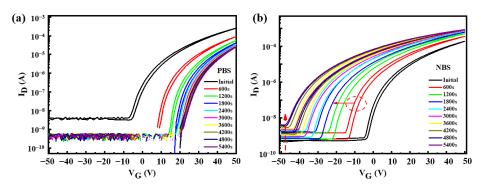

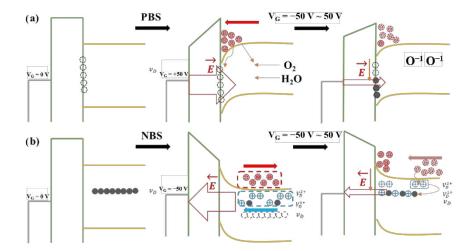

| Rihui Yao, Xiao Fu, Wanwan Li, Shangxiong Zhou, Honglong Ning and Biao Tang et al. Bias Stress Stability of Solution-Processed Nano Indium Oxide Thin Film Transistor                                                                                  |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , <i>111</i> , doi:10.3390/mi12020111                                                                                                                                                     |

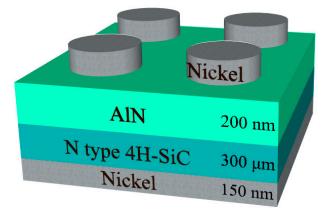

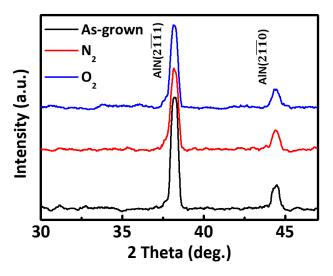

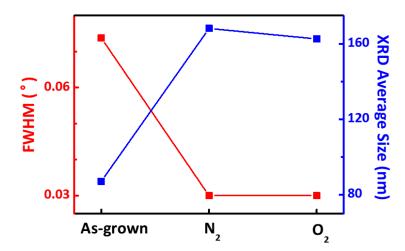

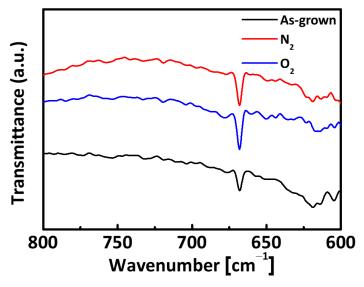

| <b>Dong-Hyeon Kim, Michael A. Schweitz and Sang-Mo Koo</b> Effect of Gas Annealing on the Electrical Properties of Ni/AlN/SiC  Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 283, doi:10.3390/mi12030283                              |

| Loh Kean Ping, Mohd Ambri Mohamed, Abhay Kumar Mondal, Mohamad Fariz Mohamad                                                                                                                                                                           |

| Taib, Mohd Hazrie Samat and Dilla Duryha Berhanuddin et al.  First-Principles Studies for Electronic Structure and Optical Properties of Strontium Doped                                                                                               |

| $-Ga_2O_3$ Reprinted from: <i>Micromachines</i> <b>2021</b> , 12, 348, doi:10.3390/mi12040348                                                                                                                                                          |

| Qian Zhang, Xu Li, Jianyun Zhao, Zhifei Sun, Yong Lu and Ting Liu et al.                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Effect of High-Temperature Nitridation and Buffer Layer on Semi-Polar (10–13) AlN Grown on                                                                                |

| Sapphire by HVPE                                                                                                                                                          |

| Reprinted from: Micromachines 2021, 12, 1153, doi:10.3390/mi12101153 281                                                                                                  |

| Marwa Fathy, Sara Gad, Badawi Anis and Abd El-Hady B. Kashyout Crystal Growth of Cubic and Hexagonal GaN Bulk Alloys and Their Thermal-Vacuum-Evaporated Nano-Thin Films  |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 1240, doi:10.3390/mi12101240 <b>289</b>                                                                    |

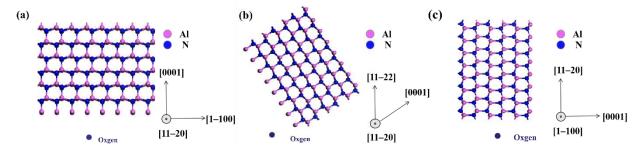

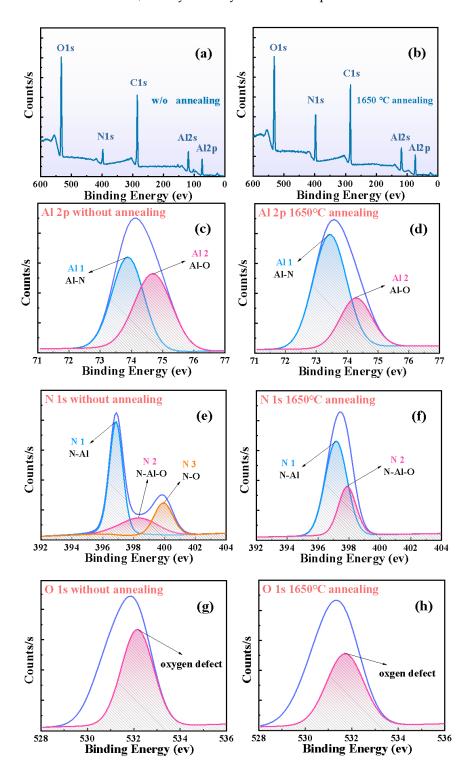

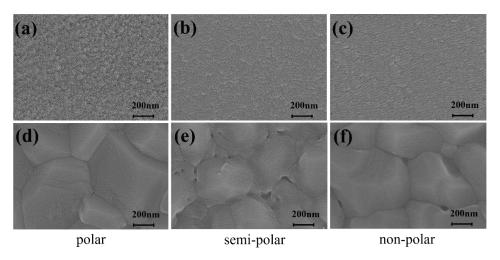

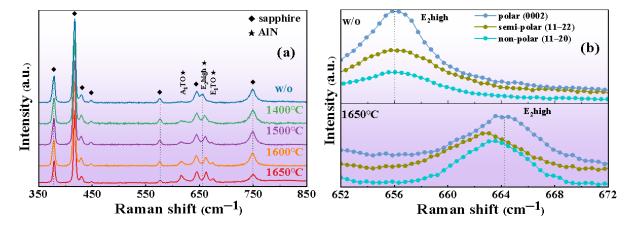

| Yang Yue, Maosong Sun, Jie Chen, Xuejun Yan, Zhuokun He and Jicai Zhang et al. Improvement of Crystal Quality of AlN Films with Different Polarities by Annealing at High |

| Temperature                                                                                                                                                               |

| Reprinted from: Micromachines 2022, 13, 129, doi:10.3390/mi13010129 299                                                                                                   |

#### **About the Editor**

#### Giovanni Verzellesi

Giovanni Verzellesi received the "Laurea" degree in Electrical Engineering from the University of Bologna, Bologna, Italy, in 1989, and the Ph.D. degree also in Electrical Engineering from the University of Padova, Padova, Italy, in 1994. In 1993-1994, he was a visiting graduate student with the University of California, Santa Barbara (CA, USA). From 1994 to 1999, he was with the University of Trento, Italy, as an Assistant Professor of Electronics. Since 1999, he has been with the University of Modena and Reggio Emilia, Italy, where he became Associate Professor in 2000 and Professor in 2006.

His research activity has been concerned with the modeling, simulation, and characterization of semiconductor devices and sensors and has covered, over the years, the following topics: impact-ionization effects in Si bipolar transistors, Si- and SiC-based radiation detectors, GaN LEDs, and GaAs and GaN based field-effect transistors. His current research interests are mainly in field of GaN field-effect transistors for RF and power switching applications and GaN LEDs.

He has coauthored more than 100 papers in international journals and more than 130 papers in proceedings of international conferences.

#### Editorial for the Special Issue on Wide Bandgap Based Devices: Design, Fabrication and Applications, Volume II

Giovanni Verzellesi D

Department of Sciences and Methods for Engineering (DISMI), University of Modena and Reggio Emilia, 42122 Reggio Emilia, Italy; giovanni.verzellesi@unimore.it

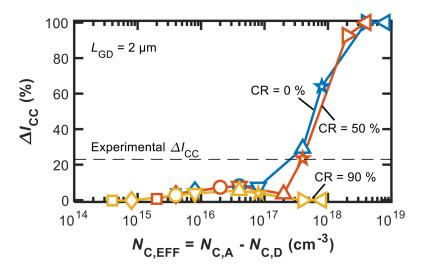

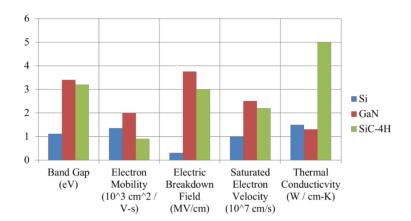

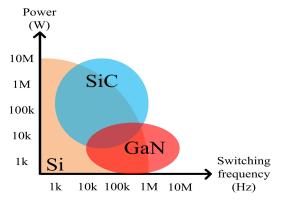

Wide bandgap (WBG) semiconductors are becoming a key enabling technology for several strategic fields of human activities. SiC- and GaN-based transistors are finding their way to market and are expected to become the technology of choice for high-power-density RF amplifiers and high-efficiency power converters, the latter being indispensable elements for the electrification of transports and of energetic systems in industry and buildings. GaN LEDs are the light source technology dominating all segments of the illumination market today. III-nitrides are being evaluated as materials for sensor and transducers. WBG semiconducting oxides are emerging as new materials having potentially superior properties for different applications, such as power conversion, displays and illumination.

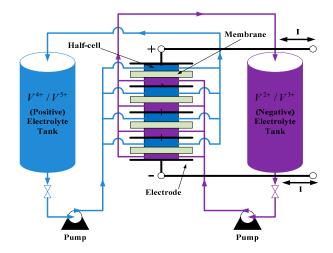

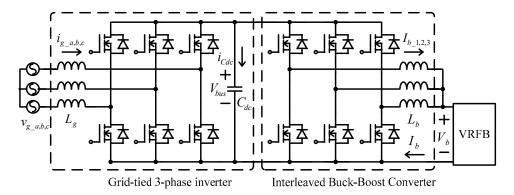

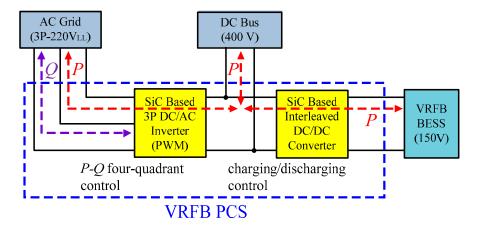

Research is still required for all of the above technologies at different levels, from materials to devices and from circuits to systems, so the success of this Special Issue is not surprising. There are 23 papers published, including 20 articles and 3 review papers providing contributions within the full spectrum of the WBG semiconductor applications delineated above. Not surprisingly, one-third of the papers [1-7] focuses on GaN device technologies, which are important for next-generation high-efficiency power converters and their impellent contribution to the decarbonization of human activities. In addition, three papers [8–10] address GaN and SiC circuital applications in power conditioning systems. One paper deals with GaN LEDs [11], whereas three contributions [12-14] are concerned with III-nitride-based devices for sensing applications. Two papers [15,16] cover advanced processing techniques. The remaining papers [17-23] explore the properties and growth techniques of emerging WBG materials.

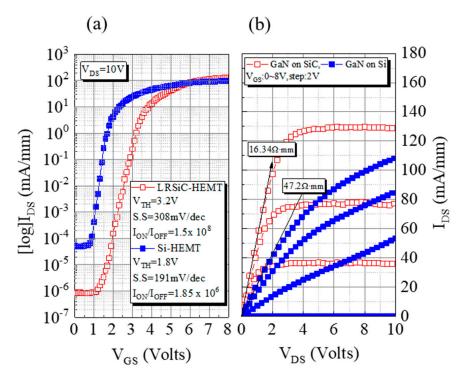

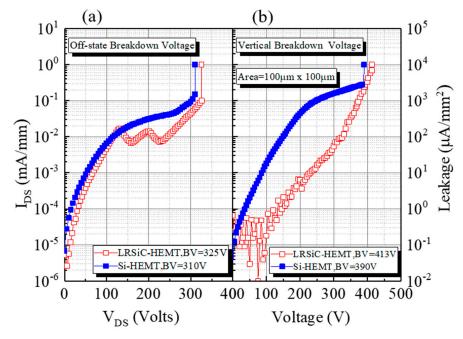

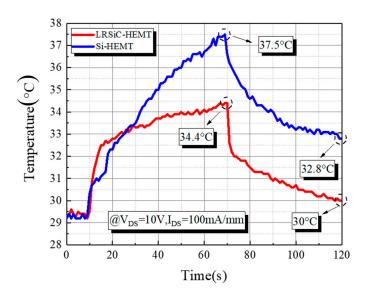

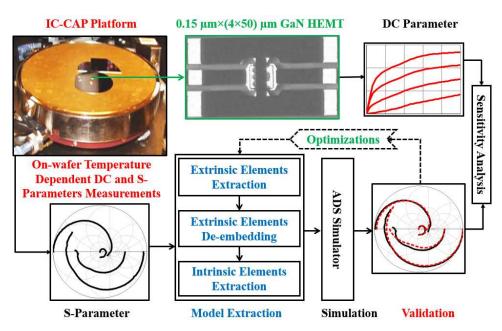

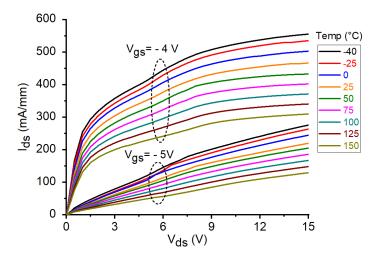

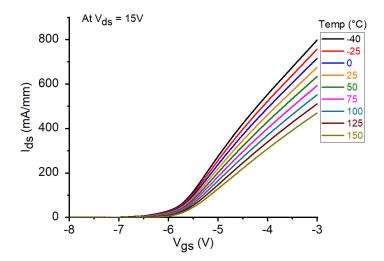

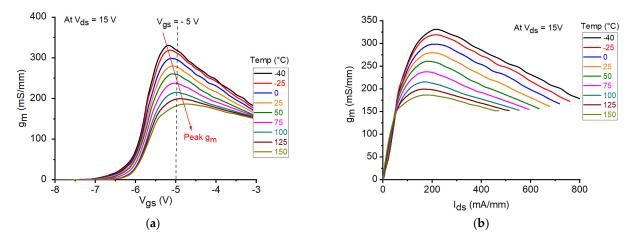

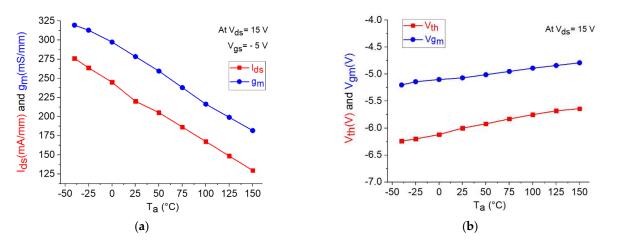

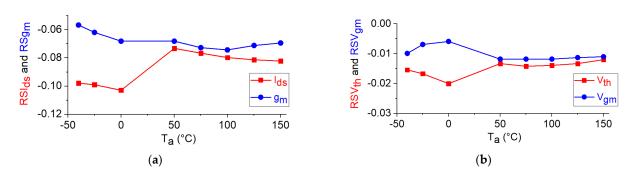

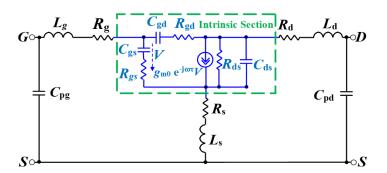

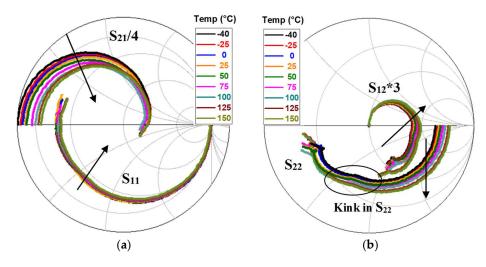

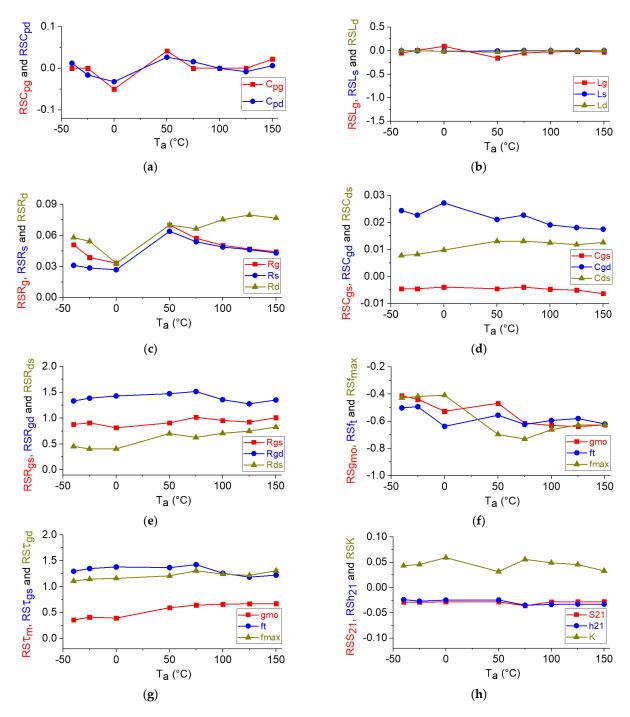

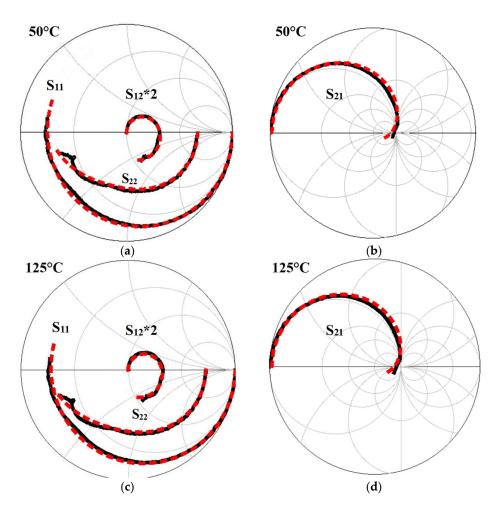

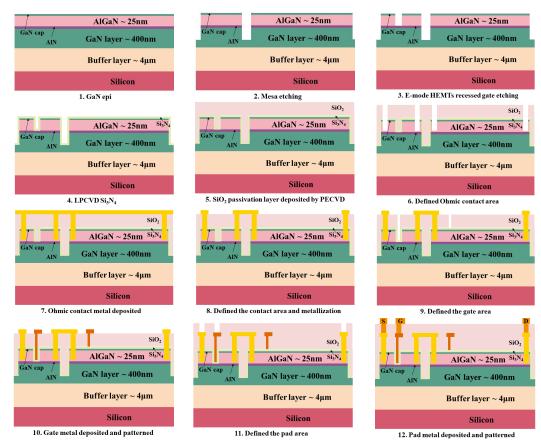

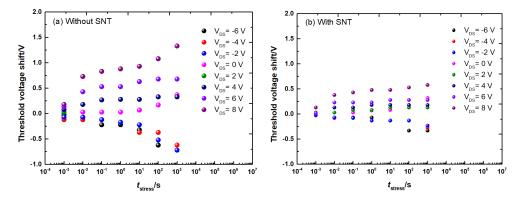

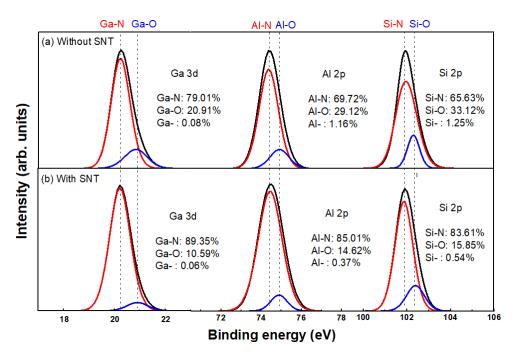

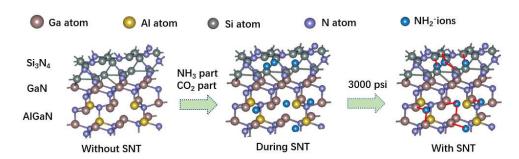

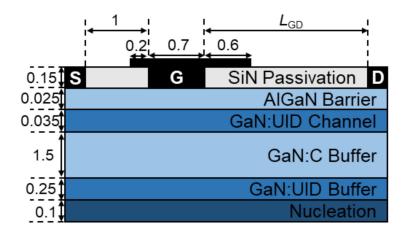

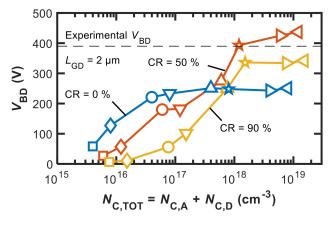

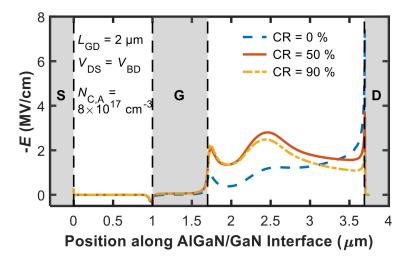

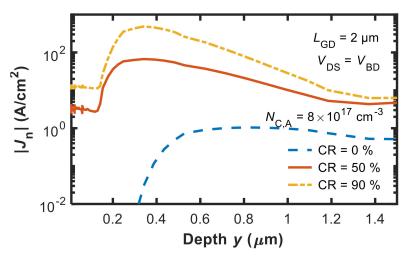

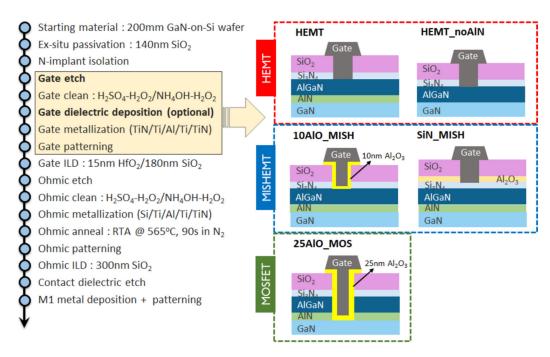

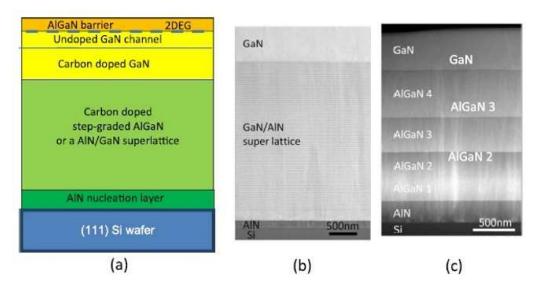

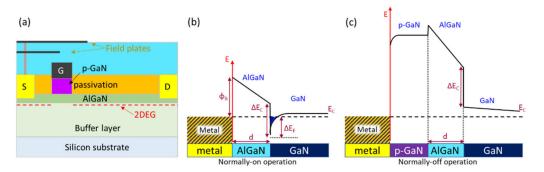

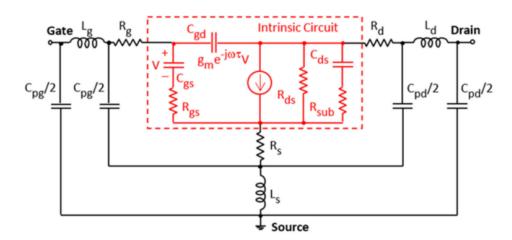

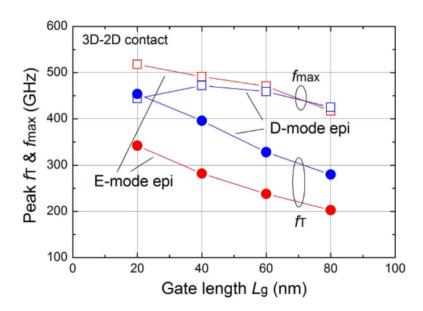

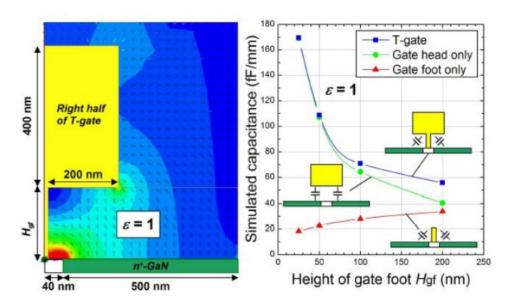

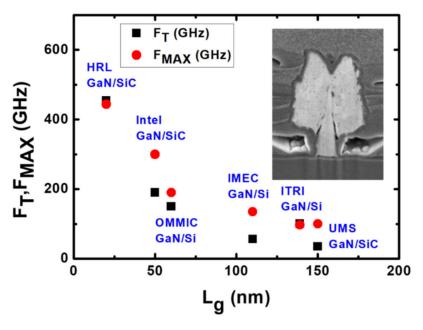

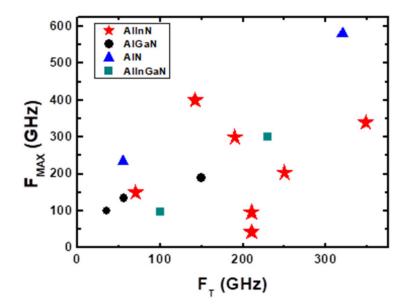

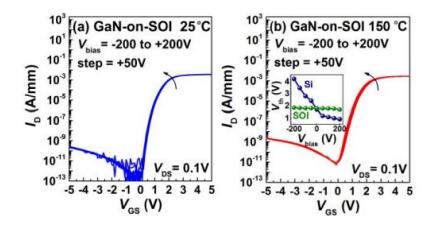

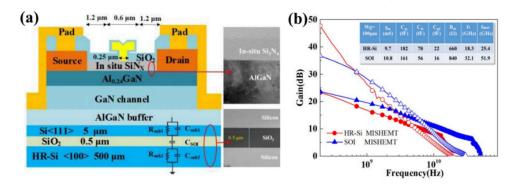

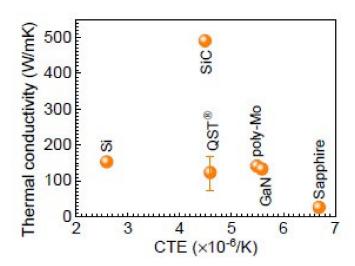

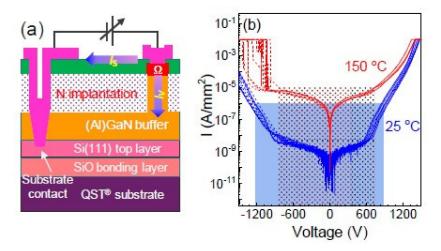

Regarding GaN device technologies, Jorudas et al. [1] presents results from buffer-free, AlGaN/GaN Schottky barrier diodes and HEMTs on SiC substrates, showing uncompromised performance for high-frequency and high-power applications. Kim et al. [2] propose a normally off, p-GaN/AlGaN/GaN HFET, allowing for unidirectional operation by means of a p-GaN drain electrode shorted to the ohmic drain electrode and avoiding the need for a separate reverse blocking device. Huang et al. [3] characterize normally off, p-GaN gate, AlGaN/GaN HEMTs they fabricated on a low-resistivity SiC substrate, guaranteeing efficient heat removal in high-power performance at a price that is lower than high-resistivity SiC. Alim et al. [4] report on a systematic study based on the measurements, an equivalent-circuit model and sensitivity analysis of the temperature-dependent DC and microwave characteristics of 0.15- $\mu m$  ultra-short gate-length AlGaN/GaN HEMTs over a wide temperature range from −40 °C to 150 °C. A novel method to achieve AlGaN/GaN MIS-HEMTs in a Si-CMOS platform along with a process for repairing interface defects by a supercritical NH<sub>3</sub> fluid treatment are reported by Liu et al. [5]. Zagni et al. [6] investigated the compensation ratio between the densities of donors and acceptors introduced by carbon doping in the buffer of GaN power HEMTs, assumed to correctly simulate breakdown voltage and current collapse effects. A comprehensive review of the current status of GaN-on-Si transistor technologies is provided by Hsu et al. [7], along with recent different substrate structures, including silicon-on-insulator, engineered substrates and the 3D hetero-integration of GaN and CMOS technologies.

Citation: Verzellesi, G. Editorial for the Special Issue on Wide Bandgap Based Devices: Design, Fabrication and Applications, Volume II. Micromachines 2022, 13, 403. https:// doi.org/10.3390/mi13030403

Received: 27 February 2022 Accepted: 27 February 2022 Published: 1 March 2022

Publisher's Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affil-

Copyright: © 2022 by the author. Licensee MDPI, Basel, Switzerland This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

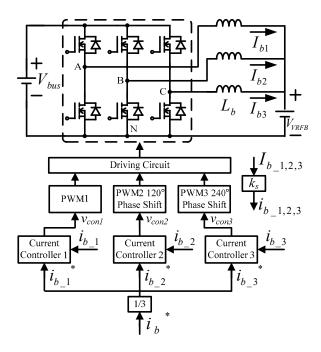

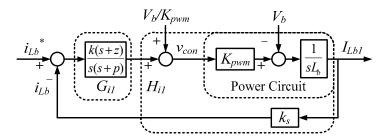

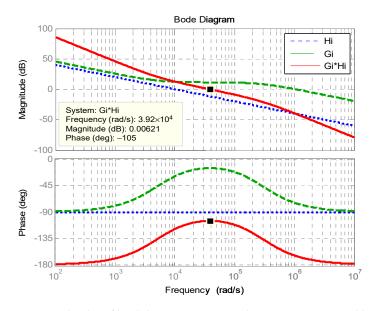

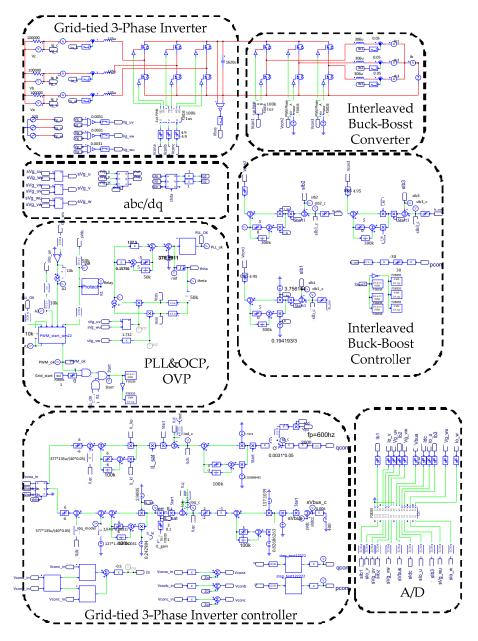

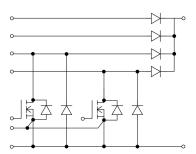

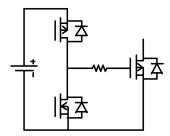

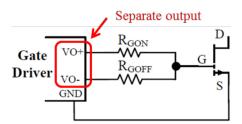

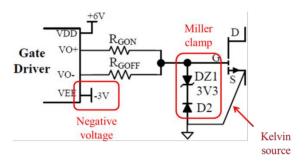

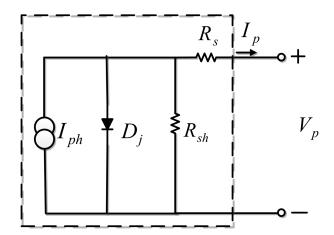

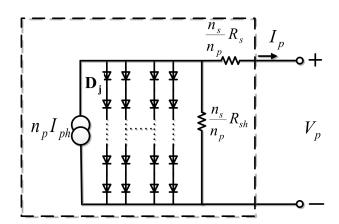

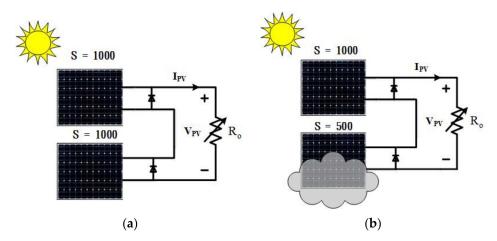

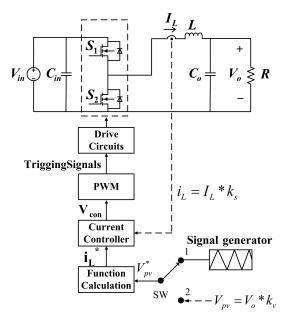

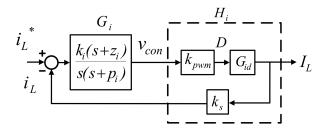

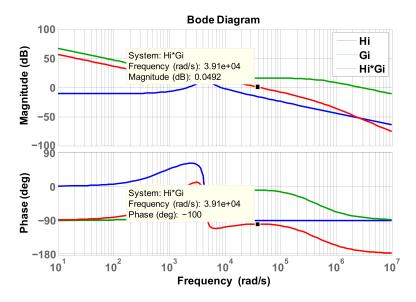

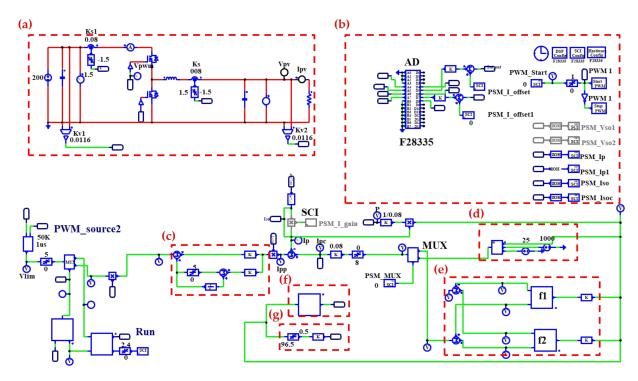

A power conditioning system is designed and built using SiC MOSFETs as switching devices by Ma et al. in [8], which, by leveraging the excellent thermal and voltage capability of SiC MOSFETs, is suitable for grid-level energy storage systems based on vanadium redox flow batteries. A digitally controlled photovoltaic emulator based on an advanced GaN power converter is developed by Ma et al. in [10], whereas in [9], the driving requirements of SiC MOSFETs and GaN HEMTs are illustrated, and the driving circuits designed for WBG switching devices are surveyed.

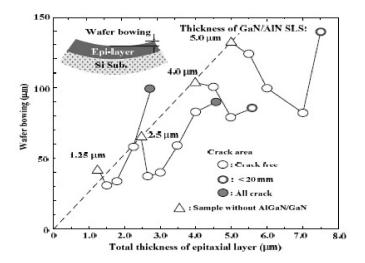

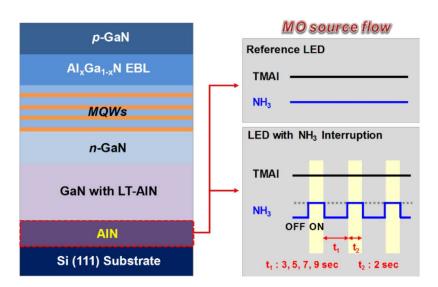

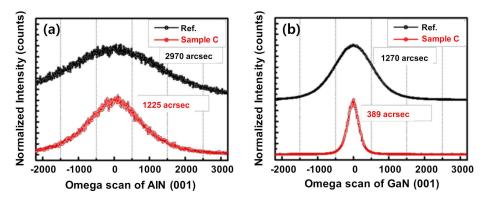

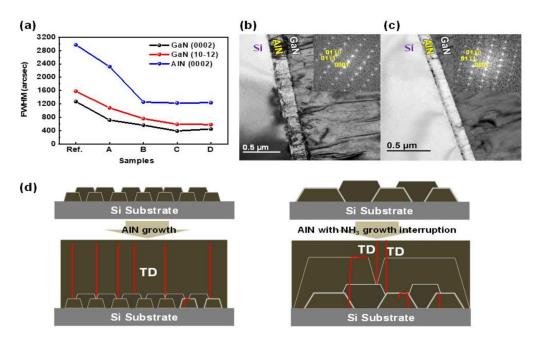

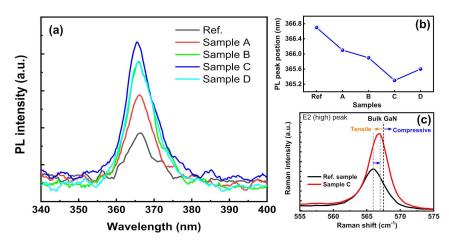

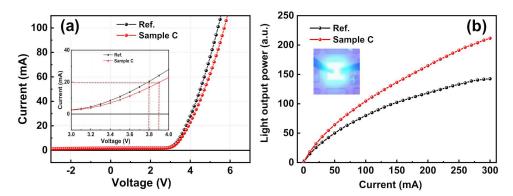

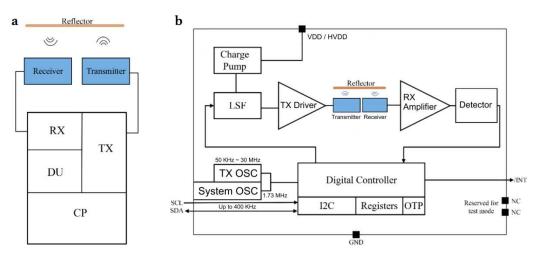

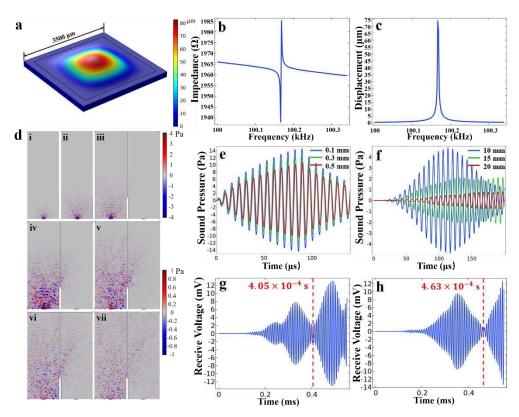

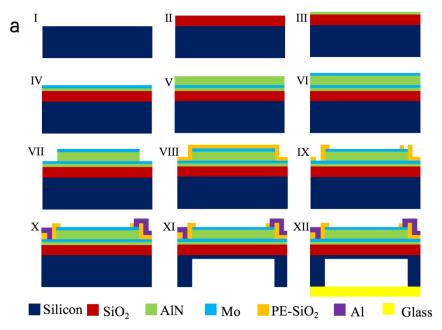

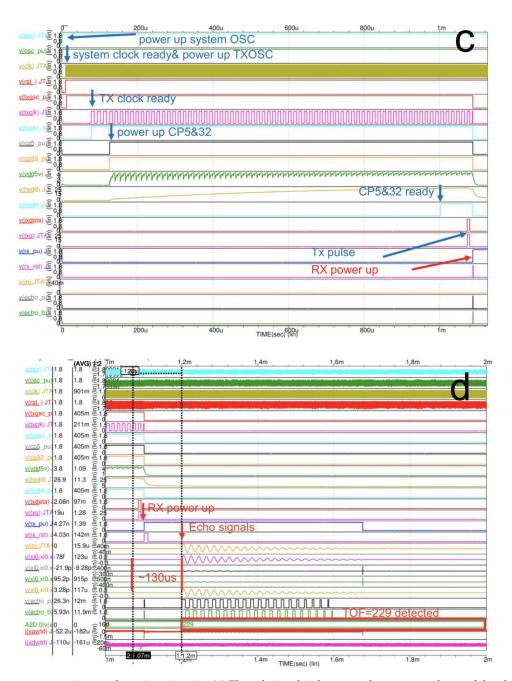

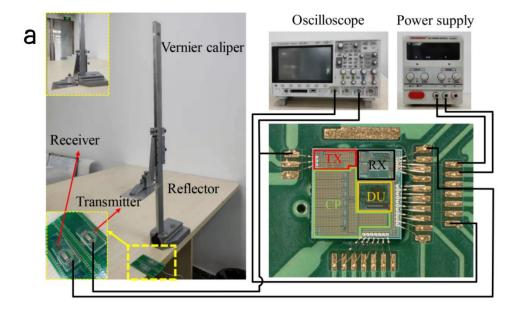

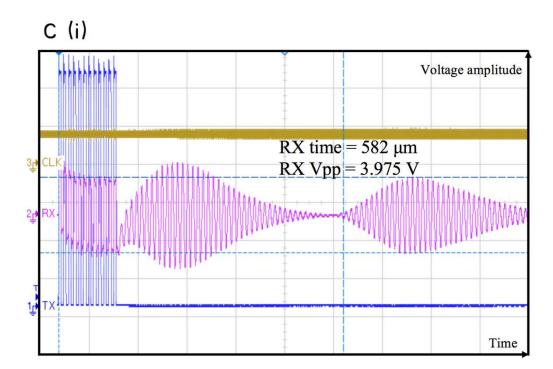

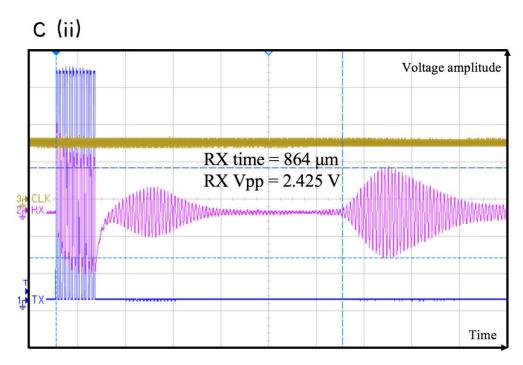

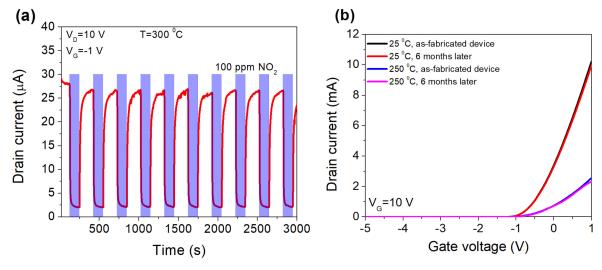

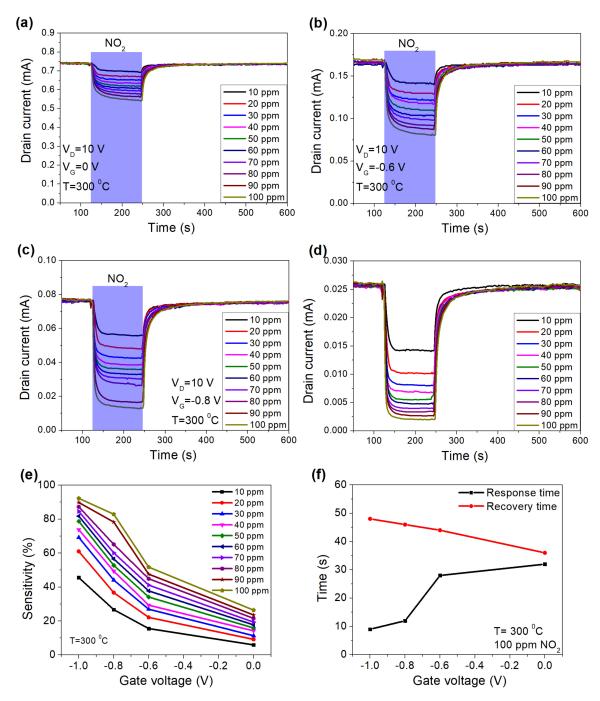

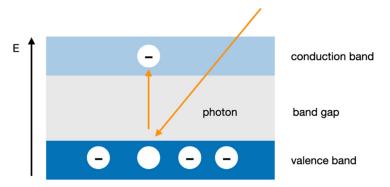

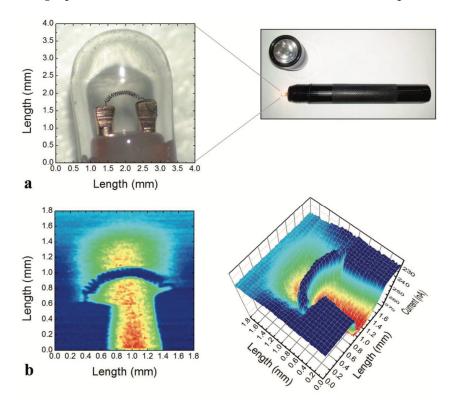

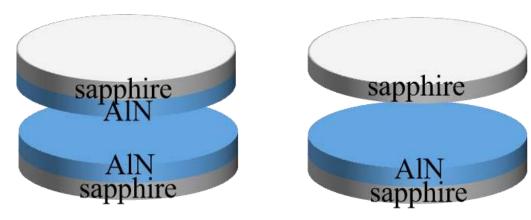

In [11], Kim et al. demonstrate that InGaN/GaN MQW LEDs on Si substrates with an AlN buffer layer grown with NH<sub>3</sub> interruption show improved crystal quality and enhanced optical output compared to LEDs with conventional AlN buffer. On the sensing application side, AlN is exploited by Chiu et al. [12] to fabricate piezoelectric micromachined ultrasonic transducers that are used to build a high-accuracy time-of-flight ranging system. Nguyen et al. [13] investigate the sensing characteristics of NO<sub>2</sub> gas sensors based on Pd-AlGaN/GaN HEMTs at high temperatures, while Thalhammer et al. [14] describe a novel class of X-ray sensors based on AlGaN/GaN HEMTs offering superior sensitivity and the opportunity for dose reduction in medical applications.

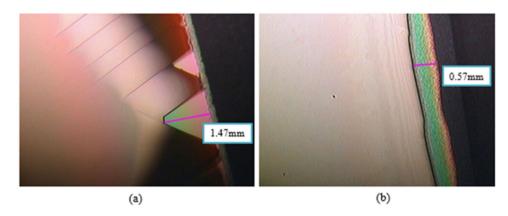

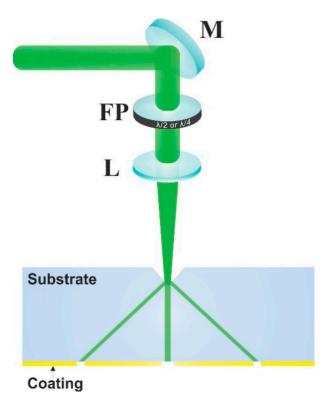

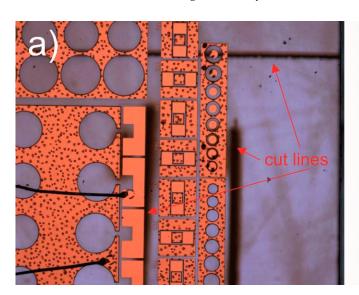

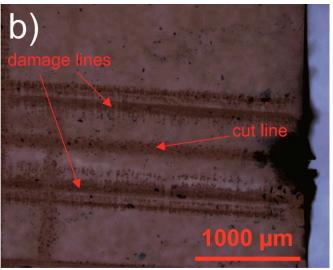

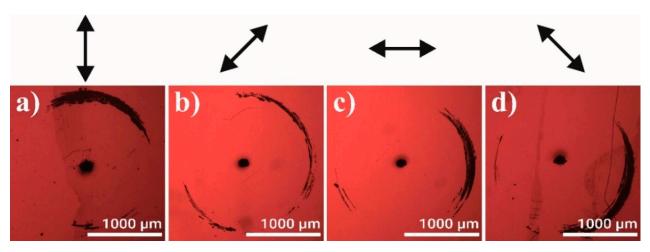

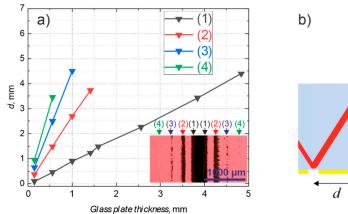

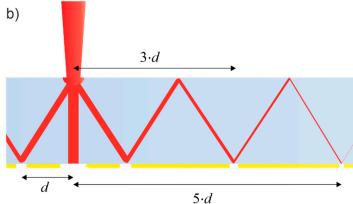

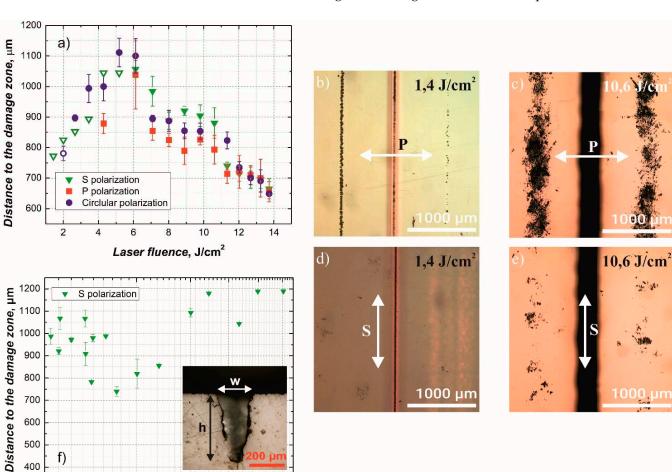

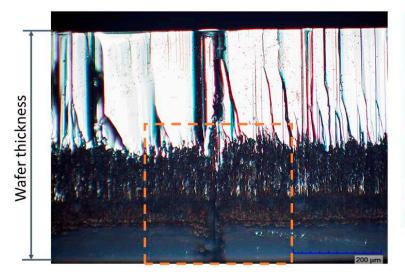

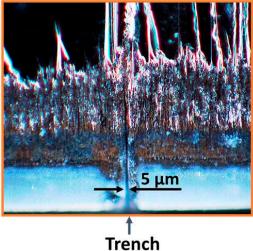

On the advanced processing technique side, laser micromachining on the frontside of SiC and sapphire wafers and the conditions by which the degradation of the performance of GaN HEMT electronics on the backside can be avoided are investigated by Indrišiūnas et al. in [15]. A novel dual laser beam asynchronous dicing method is proposed by Zhang et al. in [16] to improve the cutting quality of SiC wafers.

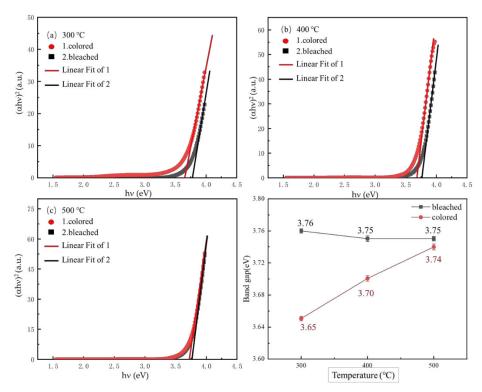

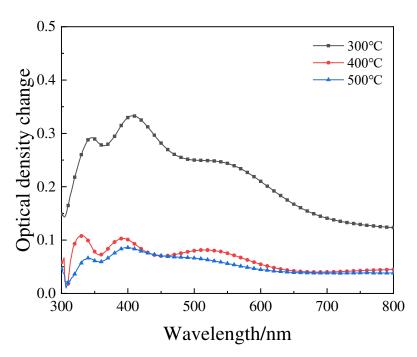

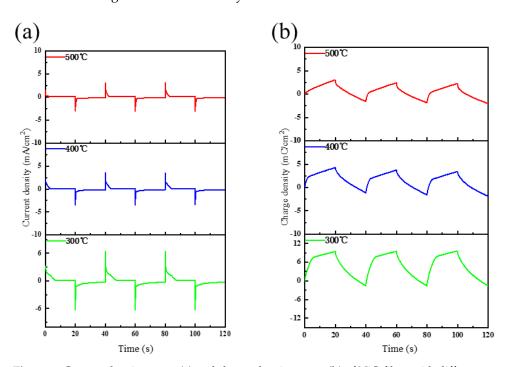

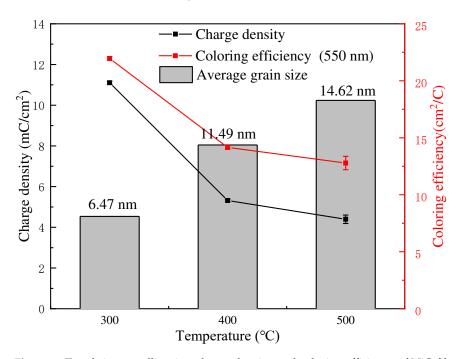

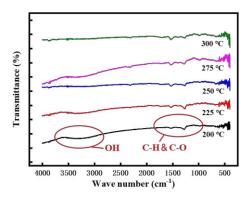

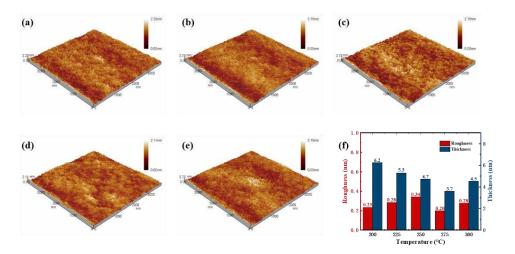

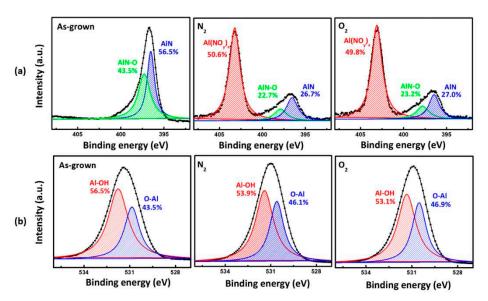

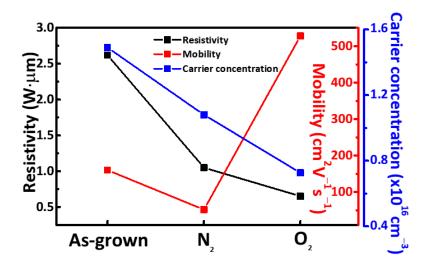

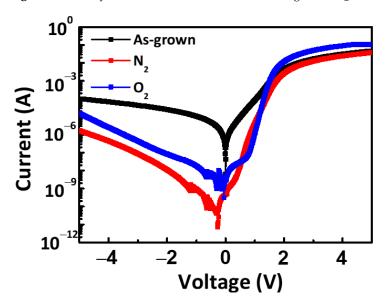

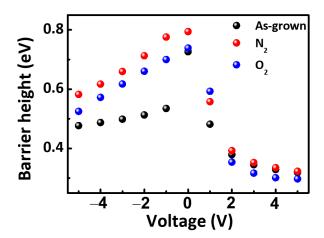

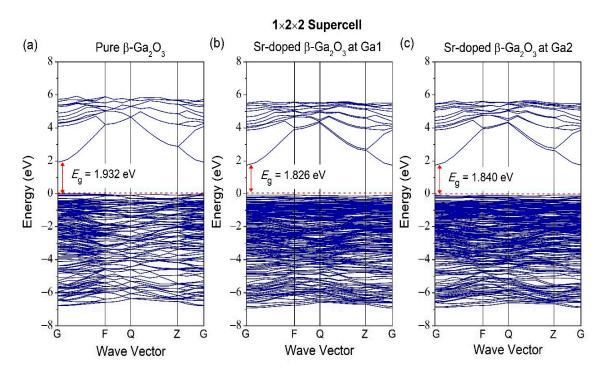

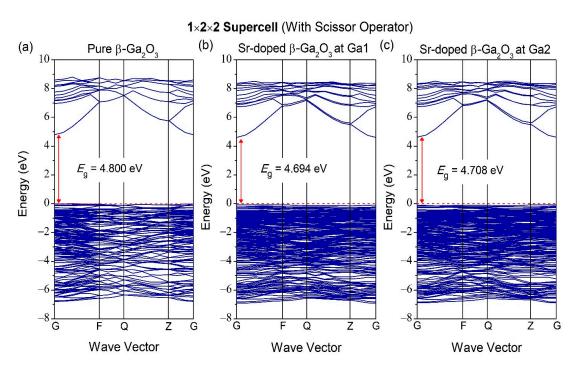

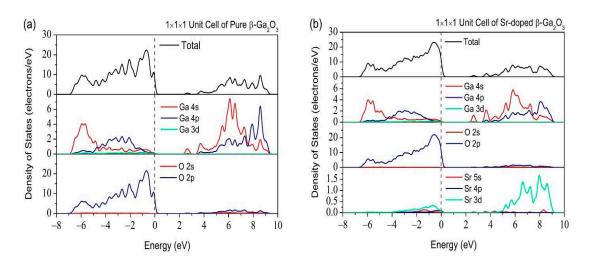

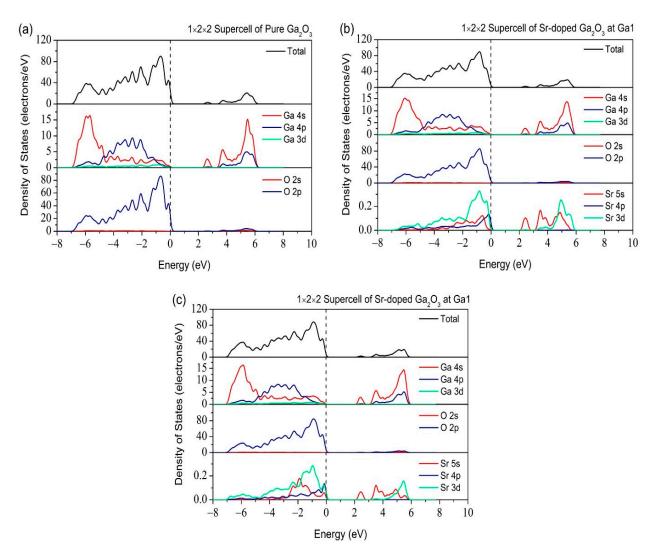

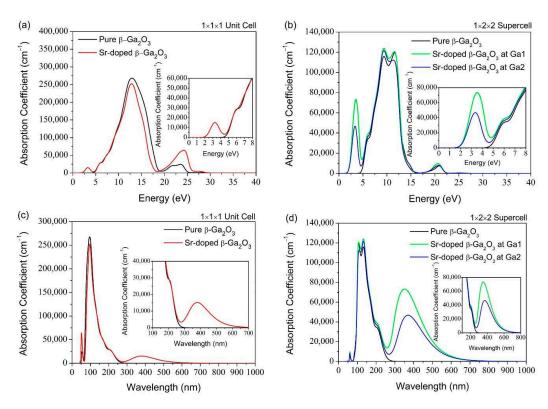

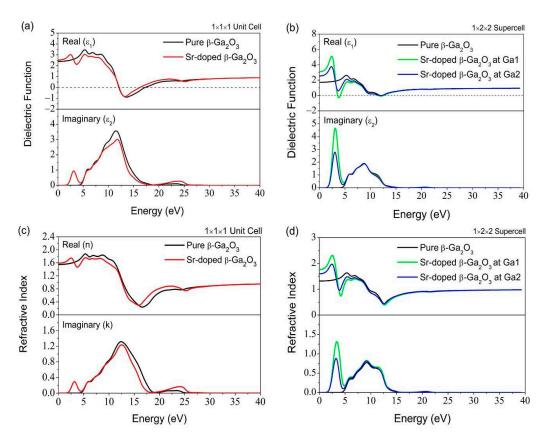

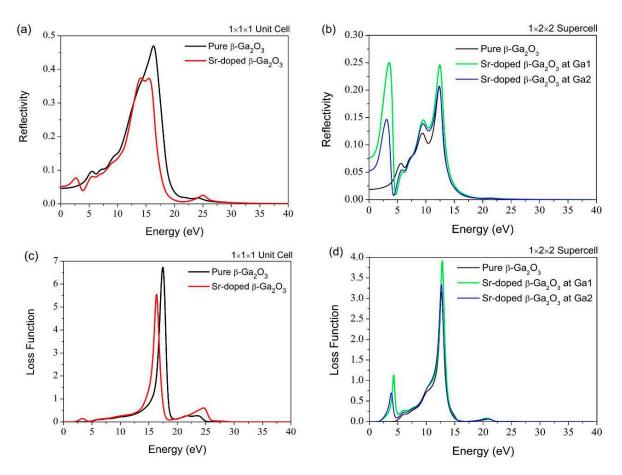

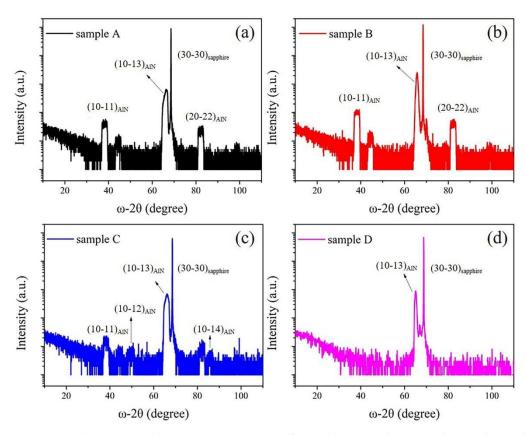

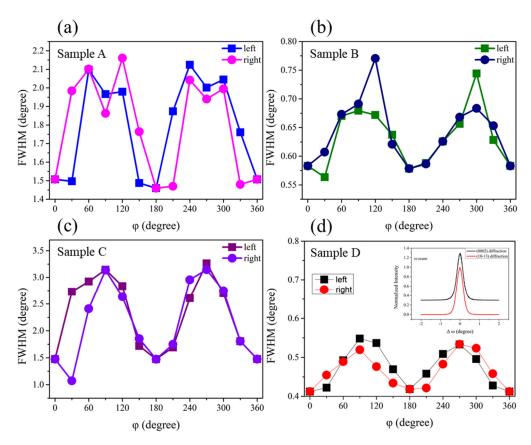

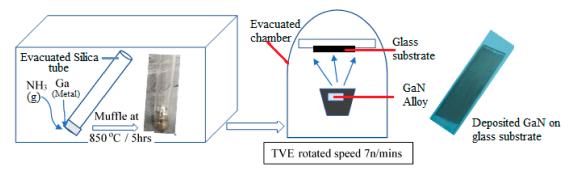

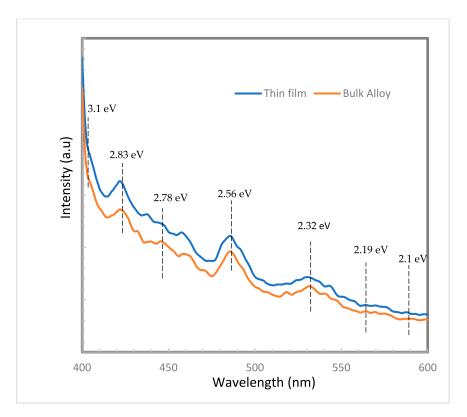

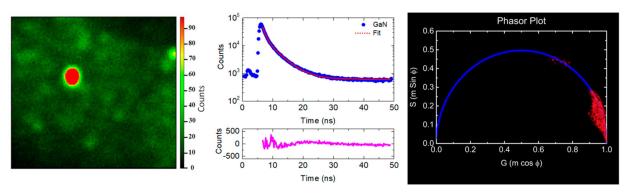

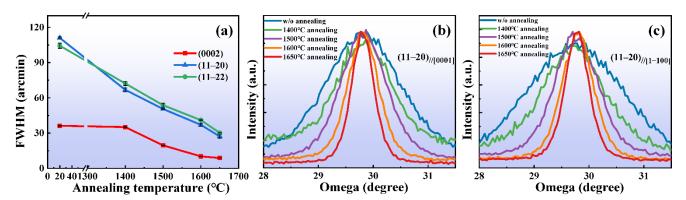

Regarding the properties and growth of emerging WBG materials, a methodology to synthesize gallium nitride nanoparticles by combining crystal growth with thermal vacuum evaporation is proposed by Fathy et al. in [22]. AlN is explored as an ultra WBG material in three papers: annealing Ni/AlN/SiC Schottky barrier diodes in an atmosphere of nitrogen and oxygen is shown to lead to a significant improvement in the electrical properties of the structures by Kim et al. in [19]; the effect of high-temperature nitridation and a buffer layer on semi-polar AlN films grown on sapphire by hydride vapor phase epitaxy is studied by Zhang et al. [21]; and the thermal annealing of AlN films with different polarities and its impact on crystal quality are studied by in Yue et al. in [23]. The effect of the annealing temperature on the microstructure and performance of sol-gel-prepared NiO films for electrochromic applications is analyzed by Shi et al. in [17]. Solution-processed  $In_2O_3$  thin films and TFTs are fabricated, and the factors affecting the stability of these devices are investigated by Yao et al. in [18]. The electronic structure and the optical properties of Srdoped  $\beta$ - $Ga_2O_3$  are studied by Kean Ping et al. [20] using DFT first-principles calculations.

I would like to take this opportunity to thank all the authors for submitting their manuscripts to this Special Issue and all the reviewers for their time and their fundamental help in improving the quality of the accepted papers.

**Conflicts of Interest:** The author declares no conflict of interest.

#### References

- Jorudas, J.; Šimukovič, A.; Dub, M.; Sakowicz, M.; Prystawko, P.; Indrišiūnas, S.; Kovalevskij, V.; Rumyantsev, S.; Knap, W.; Kašalynas, I. AlGaN/GaN on SiC Devices without a GaN Buffer Layer: Electrical and Noise Characteristics. *Micromachines* 2020, 11, 1131. [CrossRef] [PubMed]

- 2. Kim, T.; Jang, W.; Yim, J.; Cha, H. Unidirectional Operation of p-GaN Gate AlGaN/GaN Heterojunction FET Using Rectifying Drain Electrode. *Micromachines* **2021**, *12*, 291. [CrossRef]

- 3. Huang, Y.; Chiu, H.; Kao, H.; Wang, H.; Liu, C.; Huang, C.; Chen, S. High Thermal Dissipation of Normally off p-GaN Gate AlGaN/GaN HEMTs on 6-Inch N-Doped Low-Resistivity SiC Substrate. *Micromachines* **2021**, *12*, 509. [CrossRef] [PubMed]

- 4. Alim, M.; Gaquiere, C.; Crupi, G. An Experimental and Systematic Insight into the Temperature Sensitivity for a 0.15-μm Gate-Length HEMT Based on the GaN Technology. *Micromachines* **2021**, *12*, 549. [CrossRef]

- 5. Liu, M.; Yang, Y.; Chang, C.; Li, L.; Jin, Y. Fabrication of All-GaN Integrated MIS-HEMTs with High Threshold Voltage Stability Using Supercritical Technology. *Micromachines* **2021**, *12*, 572. [CrossRef]

- Zagni, N.; Chini, A.; Puglisi, F.; Pavan, P.; Verzellesi, G. On the Modeling of the Donor/Acceptor Compensation Ratio in Carbon-Doped GaN to Univocally Reproduce Breakdown Voltage and Current Collapse in Lateral GaN Power HEMTs. *Micromachines* 2021, 12, 709. [CrossRef]

- 7. Hsu, L.; Lai, Y.; Tu, P.; Langpoklakpam, C.; Chang, Y.; Huang, Y.; Lee, W.; Tzou, A.; Cheng, Y.; Lin, C.; et al. Development of GaN HEMTs Fabricated on Silicon, Silicon-on-Insulator, and Engineered Substrates and the Heterogeneous Integration. *Micromachines* **2021**, *12*, 1159. [CrossRef]

- 8. Ma, C.; Tian, Y. Design and Implementation of a SiC-Based VRFB Power Conditioning System. *Micromachines* **2020**, *11*, 1099. [CrossRef]

- 9. Ma, C.; Gu, Z. Review on Driving Circuits for Wide-Bandgap Semiconductor Switching Devices for Mid- to High-Power Applications. *Micromachines* **2021**, 12, 65. [CrossRef]

- 10. Ma, C.; Tsai, Z.; Ku, H.; Hsieh, C. Design and Implementation of a Flexible Photovoltaic Emulator Using a GaN-Based Synchronous Buck Converter. *Micromachines* **2021**, *12*, 1587. [CrossRef]

- 11. Kim, S.; Oh, S.; Lee, K.; Kim, S.; Kim, K. Improved Performance of GaN-Based Light-Emitting Diodes Grown on Si (111) Substrates with NH<sub>3</sub> Growth Interruption. *Micromachines* **2021**, *12*, 399. [CrossRef]

- 12. Chiu, Y.; Wang, C.; Gong, D.; Li, N.; Ma, S.; Jin, Y. A Novel Ultrasonic TOF Ranging System Using AlN Based PMUTs. *Micromachines* **2021**, *12*, 284. [CrossRef] [PubMed]

- 13. Nguyen, V.; Kim, K.; Kim, H. Performance Optimization of Nitrogen Dioxide Gas Sensor Based on Pd-AlGaN/GaN HEMTs by Gate Bias Modulation. *Micromachines* **2021**, 12, 400. [CrossRef] [PubMed]

- 14. Thalhammer, S.; Hörner, A.; Küß, M.; Eberle, S.; Pantle, F.; Wixforth, A.; Nagel, W. GaN Heterostructures as Innovative X-ray Imaging Sensors-Change of Paradigm. *Micromachines* **2022**, *13*, 147. [CrossRef] [PubMed]

- 15. Indrišiūnas, S.; Svirplys, E.; Jorudas, J.; Kašalynas, I. Laser Processing of Transparent Wafers with a AlGaN/GaN Heterostructures and High-Electron Mobility Devices on a Backside. *Micromachines* **2021**, *12*, 407. [CrossRef]

- 16. Zhang, Z.; Wen, Z.; Shi, H.; Song, Q.; Xu, Z.; Li, M.; Hou, Y.; Zhang, Z. Dual Laser Beam Asynchronous Dicing of 4H-SiC Wafer. *Micromachines* **2021**, *12*, 1331. [CrossRef]

- 17. Shi, M.; Qiu, T.; Tang, B.; Zhang, G.; Yao, R.; Xu, W.; Chen, J.; Fu, X.; Ning, H.; Peng, J. Temperature-Controlled Crystal Size of Wide Band Gap Nickel Oxide and Its Application in Electrochromism. *Micromachines* **2021**, *12*, 80. [CrossRef]

- 18. Yao, R.; Fu, X.; Li, W.; Zhou, S.; Ning, H.; Tang, B.; Wei, J.; Cao, X.; Xu, W.; Peng, J. Bias Stress Stability of Solution-Processed Nano Indium Oxide Thin Film Transistor. *Micromachines* **2021**, *12*, 111. [CrossRef]

- 19. Kim, D.; Schweitz, M.; Koo, S. Effect of Gas Annealing on the Electrical Properties of Ni/AlN/SiC. *Micromachines* **2021**, *12*, 283. [CrossRef]

- 20. Kean Ping, L.; Mohamed, M.; Kumar Mondal, A.; Mohamad Taib, M.; Samat, M.; Berhanuddin, D.; Menon, P.; Bahru, R. First-Principles Studies for Electronic Structure and Optical Properties of Strontium Doped β-Ga<sub>2</sub>O<sub>3</sub>. *Micromachines* **2021**, *12*, 348. [CrossRef]

- 21. Zhang, Q.; Li, X.; Zhao, J.; Sun, Z.; Lu, Y.; Liu, T.; Zhang, J. Effect of High-Temperature Nitridation and Buffer Layer on Semi-Polar (10–13) AlN Grown on Sapphire by HVPE. *Micromachines* **2021**, *12*, 1153. [CrossRef] [PubMed]

- 22. Fathy, M.; Gad, S.; Anis, B.; Kashyout, A. Crystal Growth of Cubic and Hexagonal GaN Bulk Alloys and Their Thermal-Vacuum-Evaporated Nano-Thin Films. *Micromachines* **2021**, *12*, 1240. [CrossRef] [PubMed]

- 23. Yue, Y.; Sun, M.; Chen, J.; Yan, X.; He, Z.; Zhang, J.; Sun, W. Improvement of Crystal Quality of AlN Films with Different Polarities by Annealing at High Temperature. *Micromachines* **2022**, *13*, 129. [CrossRef] [PubMed]

Article

## AlGaN/GaN on SiC Devices without a GaN Buffer Layer: Electrical and Noise Characteristics

Justinas Jorudas <sup>1,\*</sup>, Artūr Šimukovič <sup>1</sup>, Maksym Dub <sup>2,3</sup>, Maciej Sakowicz <sup>2,3</sup>, Paweł Prystawko <sup>2</sup>, Simonas Indrišiūnas <sup>1</sup>, Vitalij Kovalevskij <sup>1</sup>, Sergey Rumyantsev <sup>2,3</sup>, Wojciech Knap <sup>2,3</sup> and Irmantas Kašalynas <sup>1,\*</sup>

- <sup>1</sup> Center for Physical Sciences and Technology (FTMC), Saulėtekio 3, 10257 Vilnius, Lithuania; arturas.simukovic@ftmc.lt (A.Š.); simonas.indrisiunas@ftmc.lt (S.I.); vitalij@ftmc.lt (V.K.)

- Institute of High Pressure Physics PAS, ul. Sokołowska 29/37, 01-142 Warsaw, Poland; mdub@unipress.waw.pl (M.D.); sakowicz400@gmail.com (M.S.); pprysta@unipress.waw.pl (P.P.); roumis4@gmail.com (S.R.); knap.wojciech@gmail.com (W.K.)

- CENTERA Laboratories, Institute of High Pressure Physics PAS, ul. Sokołowska 29/37, 01-142 Warsaw, Poland

- \* Correspondence: justinas.jorudas@ftmc.lt (J.J.); irmantas.kasalynas@ftmc.lt (I.K.); Tel.: +370-5-231-2418 (I.K.)

Received: 29 November 2020; Accepted: 16 December 2020; Published: 20 December 2020

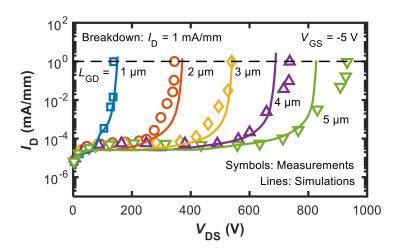

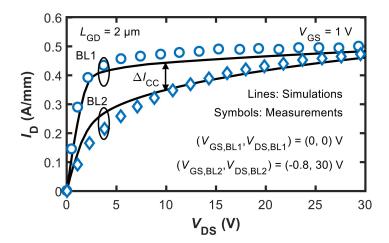

**Abstract:** We report on the high-voltage, noise, and radio frequency (RF) performances of aluminium gallium nitride/gallium nitride (AlGaN/GaN) on silicon carbide (SiC) devices without any GaN buffer. Such a GaN–SiC hybrid material was developed in order to improve thermal management and to reduce trapping effects. Fabricated Schottky barrier diodes (SBDs) demonstrated an ideality factor n at approximately 1.7 and breakdown voltages (fields) up to 780 V (approximately 0.8 MV/cm). Hall measurements revealed a thermally stable electron density at  $N_{2DEG}=1\times10^{13}$  cm<sup>-2</sup> of two-dimensional electron gas in the range of 77–300 K, with mobilities  $\mu=1.7\times10^3$  cm<sup>2</sup>/V·s and  $\mu=1.0\times10^4$  cm<sup>2</sup>/V·s at 300 K and 77 K, respectively. The maximum drain current and the transconductance were demonstrated to be as high as 0.5 A/mm and 150 mS/mm, respectively, for the transistors with gate length  $L_G=5$  µm. Low-frequency noise measurements demonstrated an effective trap density below  $10^{19}$  cm<sup>-3</sup> eV<sup>-1</sup>. RF analysis revealed  $f_T$  and  $f_{max}$  values up to 1.3 GHz and 6.7 GHz, respectively, demonstrating figures of merit  $f_T\times L_G$  up to 6.7 GHz × µm. These data further confirm the high potential of a GaN–SiC hybrid material for the development of thin high electron mobility transistors (HEMTs) and SBDs with improved thermal stability for high-frequency and high-power applications.

**Keywords:** AlGaN/GaN; SiC; high electron mobility transistor; Schottky barrier diode; breakdown field; noise; charge traps; radio frequency

#### 1. Introduction

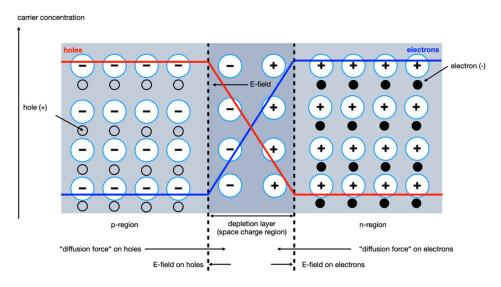

Aluminium gallium nitride/gallium nitride (AlGaN/GaN) high electron mobility transistors (HEMTs) are widely used in high-power and high-frequency applications due to their superior characteristics based on the unique physical properties of III-nitride materials. The AlGaN/GaN heterostructures can be grown on sapphire, silicon, silicon carbide, and native GaN substrates [1–7]. While sapphire and silicon substrates are the most cost-effective, the best characteristics are achieved on transistors fabricated on silicon carbide (SiC) and GaN substrates. Considerable improvements in electrical performance including the low-frequency noise were demonstrated on the AlGaN/GaN/sapphire platform [8,9]. The advantage of the SiC over GaN substrates is higher SiC thermal conductivity and therefore potentially better thermal management of the transistors fabricated using AlGaN/GaN/SiC structures. The common

approach to compensate for lattice mismatch and to reduce the dislocation density in these structures is to grow the aluminium gallium nitride (AlN) nucleation layer (NL) with reduced crystalline quality followed by a several-micrometres-thick GaN buffer doped with deep acceptors such as Fe or C which compensate for residual doping of an *n*-type GaN [10–12]. However, this approach deteriorates the overall thermal resistance of the structure and diminishes the advantage of a SiC substrate operating as a heatsink [13,14]. Also, the acceptor-type impurities in a thick GaN buffer introduce deep charge trapping centres, resulting in the increase of low-frequency noise, and facilitate the current collapse effects in HEMTs [9,15,16].

A new heteroepitaxy approach based on thin GaN–AlN–SiC heterostructures without a GaN buffer has been developed recently [17,18]. Although this approach has already been demonstrated to be promising, there are only a few studies on realistic devices such as transistors [17,19]. Thin GaN–AlN–SiC structures should provide better thermal management of the devices and could potentially reduce short channel effects. One expects also that this technology will reduce the effects of traps from a GaN:C buffer. However, the GaN:C buffer helps in reducing the number of threading dislocations. Therefore, GaN–AlN–SiC structures with the thin buffer may exhibit a higher concentration of threading dislocations, which may deteriorate the characteristics of devices. Indeed, it is well known that the dislocations may act as traps increasing low-frequency noise and current collapse effects and/or lowering maximum voltage breakdown of the devices.

In this work, the GaN–AlN–SiC hybrid material was used to develop thin Schottky barrier diodes (SBDs) and thin HEMTs (T-HEMTs) to study realistic devices under high DC voltages and in radio frequency (RF) regimes. We show that all the devices fabricated on this material have good thermal stability and demonstrate good DC as well as radio frequency (RF) characteristics. By systematic low-frequency noise measurements, we estimated the trap density, showing that avoiding a GaN:C buffer in the GaN–AlN-SiC material does not lead to an increase in active (dislocation related) trap density. We also show that deep trap-related current collapse phenomena are avoided and that all the fabricated devices demonstrate good DC, high voltage, as well as radio frequency (RF) characteristics. This way, we confirm the high potential of a GaN–SiC hybrid material in the development of improved thermal stability HEMTs and SBDs for high-frequency and high-power applications.

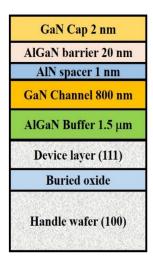

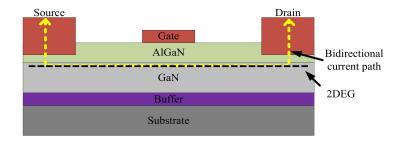

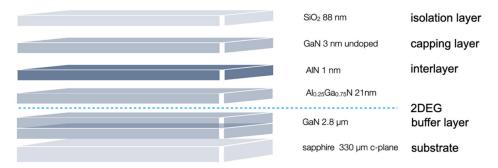

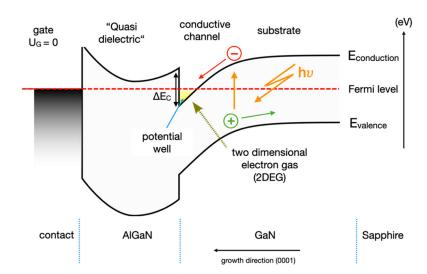

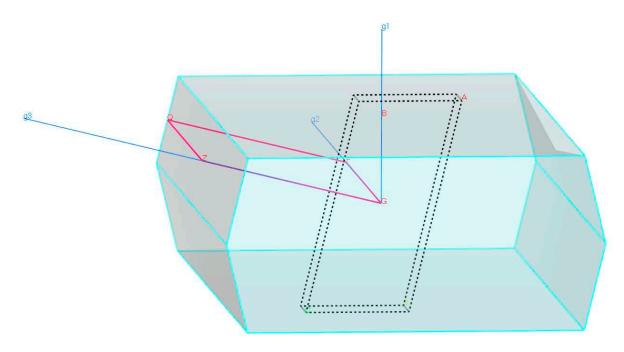

#### 2. Materials and Methods (Experimental Details)

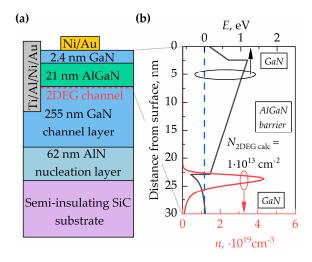

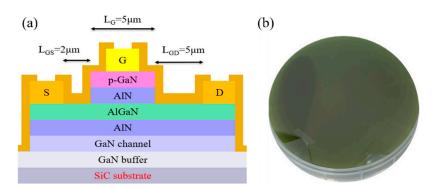

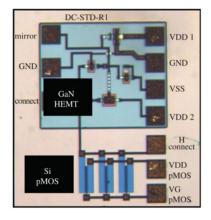

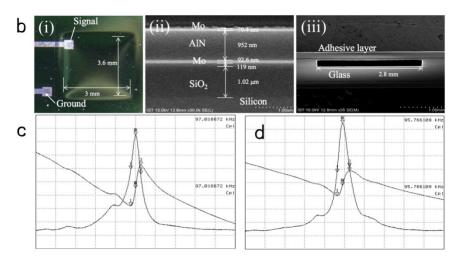

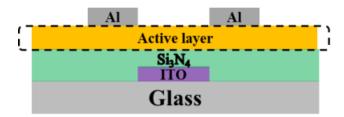

The heterostructures with the sequence of layers shown in Figure 1a were obtained commercially from the "SweGaN" company. They were grown on a 4" diameter, 500-µm-thick semi-insulating SiC substrate. The layers consisted of a 2.4-nm GaN cap, a 20.5-nm  $Al_{0.25}Ga_{0.75}N$  barrier, and a 255-nm GaN channel grown directly on a 62-nm high-quality AlN NL on SiC. The sheet resistance ( $R_{Sh}$ ) of the as-grown T-HEMT structure determined from contactless eddy current measurements was  $380 \pm 10~\Omega/\Box$ . The band diagram and electron distribution were calculated by a 1D Poisson simulator using the nominal thickness of all layers [20,21]. The results are shown in Figure 1b. The density of the two dimensional electron gas (2DEG) was calculated by integrating an electron distribution in the quantum well. Its value was found to be about  $1 \times 10^{13}$  cm<sup>-2</sup>.

The devices were fabricated using standard ultraviolet (UV) photolithography [8,22]. Mesas of 140 nm depth were formed by inductively coupled plasma reactive ion etching (ICP-RIE) (Oxford Instruments, Bristol, UK) using Cl plasma and chemical treatment in tetramethylammonium hydroxide (TMAH) solution (Microchemicals, Ulm, Germany). For ohmic contacts, Ti/Al/Ni/Au metal stacks of thicknesses 30/90/20/150 nm were deposited and annealed in nitrogen ambient for 30 s at 850 °C. The resistance ( $R_c$ ), and the specific resistivity ( $\rho_c$ ) of ohmic contacts were determined by transmission line method (TLM), demonstrating average values of about 1  $\Omega$  × mm and 2 × 10<sup>-5</sup>  $\Omega$  × cm<sup>2</sup>, respectively. Schottky contacts were formed from Ni/Au (25/150 nm).

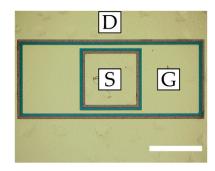

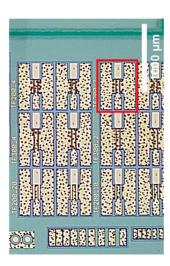

The Schottky diodes (Figure 2) and HEMTs of two different designs (see Figures 3 and 4) were fabricated. Circular SBDs were used by depositing an inner Schottky contact with radius  $r = 40 \mu m$  and an outer ohmic contact of a variable radius in such a way that the distance between the electric contact,

L, ranged from 5  $\mu$ m to 40  $\mu$ m (see Figure 2). The designs of the Schottky diodes and transistors shown in Figures 2 and 4, respectively, do not require mesa isolation. For testing at RF, the transistor design shown in Figure 3 was used (RF T-HEMT).

**Figure 1.** (a) Schematic of the thin high electron mobility transistor (T-HEMT) structure cross section with ohmic and Schottky contacts and (b) the calculated band diagram and electron density distribution in the upper layers of the heterostructure.

**Figure 2.** Microscope image of the fabricated Schottky barrier diode (SBD): L is the separation between the Ohmic and Schottky contacts. The scale bar is 50  $\mu$ m.

**Figure 3.** Microscope image of the radio frequency (RF) T-HEMT (left hand side) and details of the design parameters (right hand side) illustrating the Gate (G), Source (S), and Drain (D) electrodes in a 150-µm pitch implementation.

Figure 4. Microscope image of the fabricated DC T-HEMT: the scale bar is 100 μm.

These RF T-HEMTs consisted of 200  $\mu$ m (RF T-HEMT-1) or 300  $\mu$ m (RF T-HEMT-2)-wide two-finger transistors, each of drain-source distance  $L_{SD}=14~\mu$ m, gate length  $L_{G}=5~\mu$ m, and gate-source distance  $L_{SG}=5~\mu$ m. For comparison, the T-HEMTs with rectangular-type electrodes (see Figure 4), labelled here as DC T-HEMT, were also investigated (see also reference [9]). Similar to RF T-HEMTs, all DC T-HEMTs had the same gate length and gate-source distance of 5  $\mu$ m, but the channel width was of 200  $\mu$ m and the drain-source distances were 17.5  $\mu$ m, 15  $\mu$ m, and 12.5  $\mu$ m for three sample transistors labelled DC T-HEMT-1, DC T-HEMT-2, and DC T-HEMT-3, respectively.

All transistors were measured on the wafer in DC and RF regimes by using Süss Microtech probe station PM8 (SUSS MicroTec SE, Garching, Germany). For the RF measurements, the G-S-G (ground–signal–ground) 150- $\mu$ m pitch high frequency probes, Agilent E8364B PNA Network Analyzer (Agilent, Santa Clara, CA, USA), and E5270B Precision IV Analyzer with IC-CAP software were used (Keysight Technologies, Santa Rosa, CA, USA). The two-step open-short de-embedding method was implemented, and small signal S-parameters were obtained. The unity current gain cut-off frequency ( $f_T$ ) and the unity maximum unilateral power gain frequency ( $f_{max}$ ) were found from de-embedded S-parameter frequency characteristics.

The SBDs were investigated using EPS150 probe station (Cascade Microtech, Beaverton, OR, USA), high voltage source-meter Keithley 2410 (Tektronix, Beaverton, OR, USA), and impedance analyser Agilent 4294A (Agilent, Santa Clara, CA, USA).

The low-frequency noise in transistors was measured in the linear regime with the source grounded. The voltage fluctuations from the drain load resistor,  $R_L$ , were amplified by a low-noise amplifier and analysed using "PHOTON" spectrum analyser (Bruel & Kjaer, Nærum, Denmark). The spectral noise density of drain current fluctuations was calculated in the usual way with  $S_I = S_V ((R_L + R_{DS})/R_L R_{DS})^2$ , where  $S_V$  is the drain voltage fluctuations and  $R_{DS}$  is the total drain to source resistance.

#### 3. Experimental Results and Discussions

The 2DEG density ( $N_{2DEG}$ ), mobility ( $\mu_{2DEG}$ ), and sheet resistance ( $R_{Sh}$ ) were determined in the Hall experiments using Van der Pauw (VdP) geometry. The results are summarized in Table 1. Good agreement between the calculated carrier density, an integral of electron distribution in the quantum well (see Figure 1b), measured sheet resistance using contactless eddy current method, and the results of the Hall experiment were found within a deviation interval of 7%.

**Table 1.** Parameters of 2DEG in T-HEMT heterostructures at 300 K and 77 K.

|                                                 | Hall Measurements   |                     | Simulation | Eddy Current<br>Measurements |

|-------------------------------------------------|---------------------|---------------------|------------|------------------------------|

| Parameter                                       | 300 K               | 77 K                | 300 K      | 300 K                        |

| $N_{2DEG}$ , ×10 <sup>13</sup> cm <sup>-2</sup> | 1.00                | 0.96                | 1.0        | -                            |

| $\mu_{2DEG}$ , cm <sup>2</sup> /V·s             | $1.7 \times 10^{3}$ | $1.0 \times 10^{4}$ | -          | -                            |

| $R_{Sh}$ , $\Omega/\Box$                        | 375                 | 64                  | -          | $380 \pm 10$                 |

These values are typical for the state-of-the-art AlGaN/GaN heterostructures [23–27]. Therefore, we can conclude that elimination of the buffer layer did not worsen the parameters of the 2DEG.

#### 3.1. Performance of SBDs

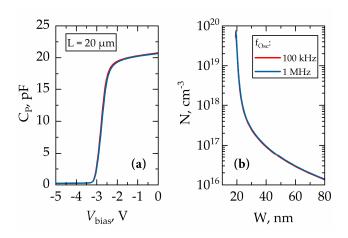

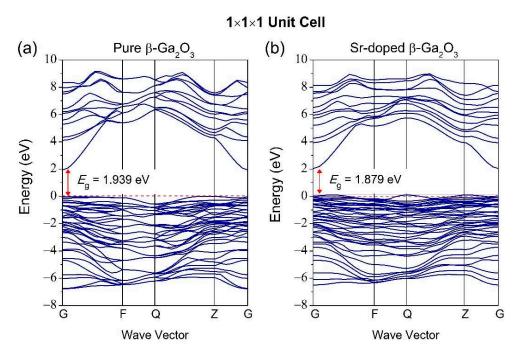

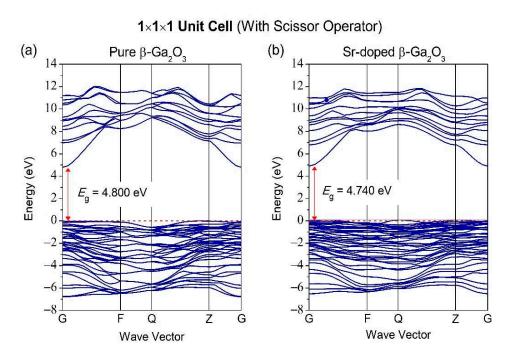

Typical capacitance–voltage (C-V) characteristics of SBD measured at frequencies 100 kHz and 1 MHz are shown in Figure 5a. One can see that frequency dispersion is negligible, indicating that deep levels do not affect the C-V characteristics. The pinch-off voltage ( $V_{po}$ ) needed to fully deplete a 2DEG channel was found to be about -3.1 V. The density of 2DEG under Schottky contact was calculated using the integral capacitance technique [28]:

$$N_{G-2DEG} = \frac{1}{eA} \int_{V_{po}}^{0} C_P(V) dV,$$

(1)

where e is the elementary charge, A is the area of Schottky contact, and  $C_P(V)$  is the capacitance. The carrier density N dependence on the distance from the surface W was found from C-V data using the following formulas [28]:

$$W = \frac{\varepsilon \varepsilon_0 A}{C_P},\tag{2}$$

$$N = \frac{C_P^3}{e\varepsilon\varepsilon A^2} \left(\frac{dC_P(V)}{dV}\right)^{-1},\tag{3}$$

where  $\varepsilon = 8.9$  is the relative permittivity of GaN and  $\varepsilon_0$  is the vacuum permittivity. The obtained N dependence on the parameter W is shown in Figure 5b. The density of 2DEG was found to be  $N_{G\text{-}2DEG} = 0.69 \times 10^{13} \text{ cm}^{-2}$  at 300 K. This density is smaller than that found from the Hall measurements due to depletion by the Schottky barrier built-in voltage [29,30].

**Figure 5.** (a) Capacitance-voltage (C-V) characteristics of SBD with L = 20  $\mu$ m at modulation frequencies of 100 kHz (red line) and 1 MHz (blue line), and (b) carrier distribution N(W) calculated from C-V data using Equations (2) and (3).

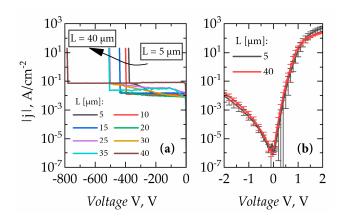

Figure 6 shows examples of the forward and reverse current–voltage characteristics of SBDs. The forward current–voltage characteristics demonstrated an ideality factor of  $n \cong 1.7$ . The barrier height found based on the thermionic emission (TE) model was  $\varphi = 0.75$  eV. These values are typical for Ni/AlGaN Schottky barriers [31]. Under reverse bias, leakage currents were saturated at approximately -5 V and remained constant until the breakdown (see Figure 6b). Moreover, SBDs demonstrated a sufficiently high  $j_{ON}/j_{OFF}$  ratio; for example, for SBD with L = 40 µm, the highest achieved value was found to be more than three orders of magnitude,  $j_{ON}/j_{OFF} \ge 3200$ , taking into account also the reverse-current densities prior to a breakdown which occurred at a voltage of -780 V. Furthermore,

a 2.5 times improvement in the maximum current density was obtained in comparison with previously reported SBDs fabricated on standard AlGaN/GaN HEMT structures with a thick GaN:C buffer [8]. Note the dependence of forward current on the distance between ohmic and Schottky contacts indicating good performance of the fabricated ohmic contacts with negligible losses.

**Figure 6.** (a) Reverse current-voltage characteristics of SBDs and (b) current-voltage characteristics of SBDs with L = 5 and  $40 \mu m$  at low voltages.

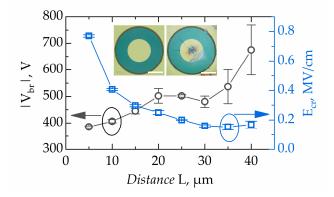

GaN–AlN–SiC buffer-free structures with a thin AlN layer may potentially exhibit a higher concentration of the threading dislocations, which may deteriorate the breakdown characteristics. On the other hand, as discussed in References [17,18], high-quality AlN NL in a T-HEMT structure can serve as a back barrier which enhances the critical breakdown field. Figure 7 shows the breakdown voltage and critical electric field dependences on the distance between ohmic and Schottky contacts.

**Figure 7.** Breakdown voltage and critical electric field dependences on the distance between ohmic and Schottky contacts: *error bars in the critical field data are depicted by the size of the symbols. Inset*: images of  $L = 40 \mu m$  SBD before and after breakdown (scale bar is 50  $\mu m$ ).

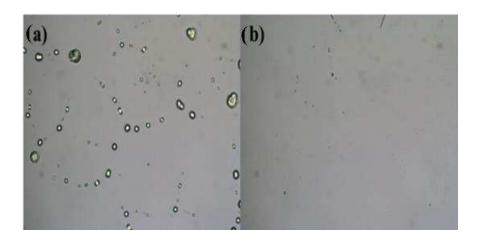

As seen in Figure 7, the breakdown voltage depends on the distance, L, between contacts and ranges from 800 V to 400 V for  $L=40~\mu m$  and  $L=5~\mu m$ , respectively. The average breakdown field for  $L=5~\mu m$  devices was found to be 0.8 MV/cm. It is worth noting that the maximum critical field asymptotically decreased down to 0.2 MV/cm with distance increasing from 5  $\mu m$  to 30  $\mu m$  and was independent of the distance for larger L values. The inset in Figure 7 shows the optical microscope images of a Schottky diode before and after breakdown. One can see that the inner contact is mostly damaged. Lateral breakdown occurs close to the inner Schottky contact, where the electric field has its maximum. A similar reverse breakdown field dependence on the distance between two ohmic contacts fabricated on the T-HEMT with locally removed 2DEG was reported previously in Reference [18]. There, the critical breakdown field values reached 2 MV/cm for a short distance of  $L=5~\mu m$  between

two isolated devices. In our work, realistic devices—SBDs—were investigated in the reverse bias regime, demonstrating similar behaviour for the breakdown field with maximum values close to 0.8 MV/cm for the short distance (5  $\mu$ m) between Schottky and ohmic contacts. Therefore, we conclude that the actual breakdown field is higher than 0.8 MV/cm and the absence of the thick GaN buffer does not deteriorate the breakdown characteristics by much.

#### 3.2. Performance of T-HEMTs

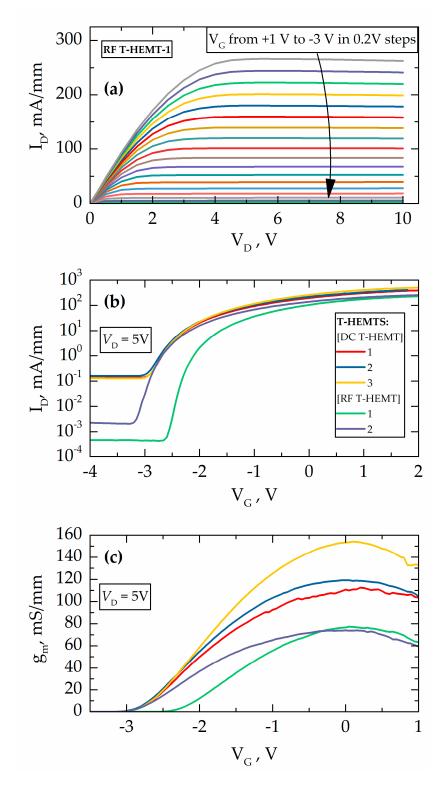

Typical DC characteristics of representative T-HEMT are shown in Figure 8. As seen in Figure 8a, RF T-HEMT demonstrated drain current saturation at the level of 266 mA/mm under DC biases of  $V_D = 10 \text{ V}$  and  $V_G = +1 \text{ V}$ . This translates into an input power value of 2.6 W/mm for T-HEMT with a channel width of 0.4 mm. The drain current in the saturation region fell by 1–2% only. This indicates the advantages of efficient heat removal from the 2DEG channel in AlGaN/GaN with AlN NL that exploits the absence of the buffer layer and high thermal conductivity of the SiC substrate.

The transfer and transconductance ( $g_m$ ) characteristics at  $V_D = 5$  V for various T-HEMTs are shown in Figure 8b,c. The impact of mesa on the device performance can be identified from the transfer characteristics. Indeed, the circular DC T-HEMT devices demonstrated up to two orders of magnitude larger leakage currents in comparison to those measured for RF T-HEMTs. Both the maximum drain current and the transconductance values were found to be higher for the DC T-HEMTs demonstrating values up to 507 mA/mm and 154 mS/mm, respectively. Meanwhile, RF T-HEMTs demonstrated only 266 mA/mm and 77 mS/mm. The pinch-off region is observed beyond a gate bias of -3 V, which is in good agreement with  $V_{\nu\rho}$  obtained from C-V measurements.

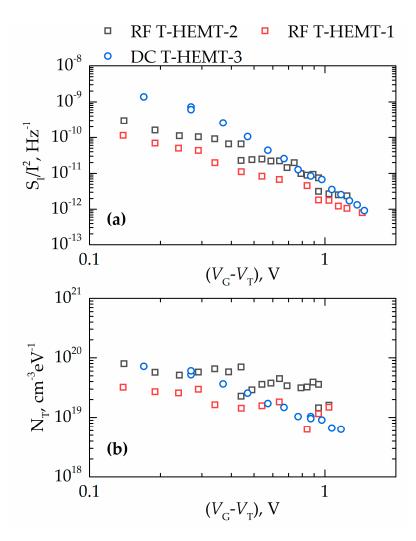

One of the most effective ways to evaluate the quality of the material and the deep level traps is the low-frequency noise measurements. It is well known that low-frequency noise may differ significantly for the devices with almost identical DC characteristics. Elevated noise level is an indication of lower quality of the material, higher concentration of the deep level traps, lower reliability, and reduced lifetime of the devices. In the majority of cases, the low-frequency noise in field effect transistors complies with the McWhorter model [32,33]. In accordance with the model, the 1/f low-frequency noise is a result of tunnelling of the carriers to the layers adjacent to the channel. The model allows for estimation of the effective trap density responsible for noise, which is a good figure of merit for the noise level and overall quality of the material.

The spectra of the drain current fluctuations had the form of 1/f' noise with exponent  $\gamma = 0.9-1.1$ . The dependences of the noise  $S_I/I^2$  on the gate voltage swing  $(V_G - V_T)$  at f = 10 Hz for three representative devices are shown in Figure 9a (here,  $V_T$  is the threshold voltage determined from the transfer current voltage characteristics in the linear regime). As seen, noise depends on the gate voltage as  $(V_G - V_T)^2$  or steeper. It is known that, in many cases, this dependence at high gate voltages may become flat, indicating a contribution of the contact noise. It is seen from Figure 9a that this is not the case for the studied devices and that contacts do not contribute to noise significantly. The effective trap density  $N_T$  in the McWhorter model can be estimated from gate voltage noise as follows [9]:

$$S_{V_G} = \frac{S_I / I^2}{(g_m / I)^2} \tag{4}$$

$$S_{V_G} = \frac{kTN_T e^2}{\gamma f W_{Ch} L_G C^2},\tag{5}$$

where k is the Boltzmann constant, T is the temperature,  $W_{Ch}$  and  $L_G$  is the channel area, C is the gate capacitance per unit area, and  $\gamma$  is the attenuation coefficient of the electron wave function under the barrier, taken to be  $10^8$  cm<sup>-1</sup>.

**Figure 8.** DC characteristics of T-HEMTs under study: (a) DC output characteristics of 0.4 mm wide RF T-HEMT-1 and comparisons of transfer (b) and transconductance (c) characteristics of the RF T-HEMTs and DC T-HEMTs with various values of the channel widths  $W_{Ch}$ . The gate length for all devices is 5  $\mu$ m.

**Figure 9.** (a) Drain current noise  $S_I/I^2$  at frequency f = 10 Hz for T-HEMTs of different channel widths ranging from 0.2 mm to 0.6 mm and (b) the effective trap density  $N_T$  as a function of the gate voltage swing  $(V_G-V_T)$  for the same transistors.

According to the McWhorter model, input gate voltage noise does not depend on access resistance and carrier concentration in the channel [9]. The dependence of the effective trap density on the gate voltage in Figure 9b can be attributed to the dependence of the trap density on energy. The number of traps in this T-HEMT structure was found to be in the range  $10^{19}$ – $10^{20}$  cm<sup>-3</sup> eV<sup>-1</sup>. Some of the devices demonstrated  $N_T < 10^{19}$  cm<sup>-3</sup> eV<sup>-1</sup>. These values are of the same order or even smaller than those reported earlier for AlGaN/GaN HEMTs with a thick buffer layer [9]. Therefore, we conclude that studied T-HEMTs are characterized by the same quality as or even better quality than regular devices with thick buffers.

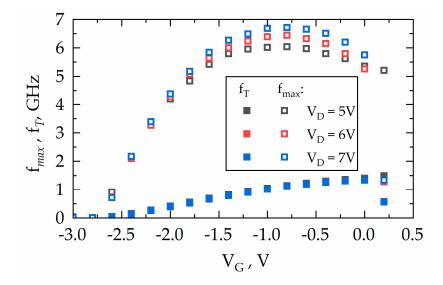

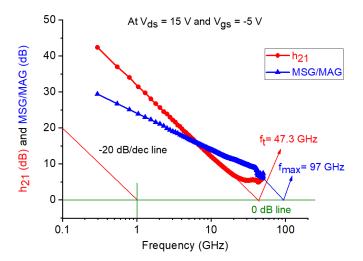

The unity current gain cut-off frequency ( $f_T$ ) and the unity maximum unilateral power gain frequency ( $f_{max}$ ) were found at various voltages down to the threshold voltage. The results are shown in Figure 10. The RF T-HEMTs with a 0.4-mm channel width demonstrated the highest operational frequencies, with values reaching  $f_T = 1.33$  GHz at  $V_{GS} = 0$  V with  $V_D = 5$  V and  $f_{max} = 6.7$  GHz at the bias of  $V_G = -0.8$  V and  $V_D = 7$  V. These results revealed a figure of merit (FOM) factor  $f_T \times L_G$  up to 6.7 GHz  $\times$   $\mu$ m, which is comparable with the best value of 9.2 GHz  $\times$   $\mu$ m reported for the T-HEMTs in Reference [19]. The performance of RF T-HEMTs can be further improved in our processing via optimization of ohmic contact/access resistance and the reduction of channel length  $L_{SD}$  in tandem

with gate length  $L_G$  [34,35]. Note that there is up to 3 times difference between the FOM factor of T-HEMTs and that of standard HEMTs, which requires more detailed investigations in the future [36].

**Figure 10.** Frequencies  $f_T$  and  $f_{max}$  at different biasing conditions extracted from S-parameters measurements of RF T-HEMT-1 with  $W_{Ch} = 0.4$  mm and  $L_G = 5$   $\mu$ m.

#### 4. Conclusions

AlGaN/GaN SBDs and HEMTs without GaN buffer layers have been fabricated on SiC substrates. 2DEG densities of  $1 \times 10^{13}$  cm<sup>2</sup> with mobility of  $1.7 \times 10^3$  cm<sup>2</sup>/V·s and  $1.0 \times 10^4$  cm<sup>2</sup>/V·s at 300 K and 77 K, respectively, were found from the Hall measurements. The unterminated and unpassivated SBDs fabricated on these heterostructures exhibited high breakdown voltages up to -780 V, with the critical breakdown field reaching 0.8 MV/cm. Transistors on these heterostructures, so-called T-HEMTs, demonstrated maximum current density and transconductance values up to 0.5 A/mm and 150 mS/mm, respectively, with a negligible reduction in the drain current. This indicates improved thermal management due to a heterostructure design on the SiC substrate without a GaN buffer layer. By systematic low-frequency noise measurements, we estimated the effective trap density, which in T-HEMT structures was below the level of  $10^{19}$  cm<sup>-3</sup> eV<sup>-1</sup>. This value is similar to or even smaller than previously reported trap densities in heterostructures with thick GaN:C buffers. This means that avoiding a GaN:C buffer in GaN-AlN-SiC material does not lead to an increase in active (dislocation-related) trap density. The unity current gain cut-off and unity maximum unilateral power gain were measured to be 1.3 GHz and 6.7 GHz, respectively. Using this data, the figure of merit  $f_T \times L_G$ is estimated at 6.7 GHz × μm. Therefore, we conclude that a buffer-free design did not compromise the quality of the structures or the performance of the devices. Our results confirm the potential of a GaN-SiC hybrid material for the development of HEMTs and SBDs for high-frequency and high-power applications with improved thermal stability.

**Author Contributions:** I.K., J.J., and S.R. conceived the idea. J.J., P.P., S.I., and V.K. characterized the material and prepared the samples. J.J., A.Š., and I.K. conducted the electrical characterization. J.J., M.D., and S.R. performed the noise characterization. M.S., S.R., W.K., and I.K. acquired funding. All authors contributed to the discussion, data analysis, and manuscript preparation. All authors have read and agreed to the published version of the manuscript.

**Funding:** The work was supported by the Research Council of Lithuania (Lietuvos mokslo taryba) under the "TERAGANWIRE" project (grant No. S-LL-19-1), by the National Science Centre of Poland (grant no. 2017/27/L/ST7/03283), and by the "International Research Agendas" program of the Foundation for Polish Science co-financed by the European Union under the European Regional Development Fund (Nos. MAB/2018/9).

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Koksaldi, O.S.; Haller, J.; Li, H.; Romanczyk, B.; Guidry, M.; Wienecke, S.; Keller, S.; Mishra, U.K. N-Polar GaN HEMTs Exhibiting Record Breakdown Voltage Over 2000 V and Low Dynamic On-Resistance. *IEEE Electron. Device Lett.* **2018**, *39*, 1014–1017. [CrossRef]

- Choi, U.; Kim, H.-S.; Lee, K.; Jung, D.; Kwak, T.; Jang, T.; Nam, Y.; So, B.; Kang, M.-J.; Seo, K.-S.; et al. Direct Current and Radio Frequency Characterizations of AlGaN/AlN/GaN/AlN Double-Heterostructure High-Electron Mobility Transistor (DH-HEMT) on Sapphire. *Phys. Status Solidi* 2020, 217, 1900695. [CrossRef]

- 3. Chandrasekar, H.; Uren, M.J.; Eblabla, A.; Hirshy, H.; Casbon, M.A.; Tasker, P.J.; Elgaid, K.; Kuball, M. Buffer-Induced Current Collapse in GaN HEMTs on Highly Resistive Si Substrates. *IEEE Electron. Device Lett.* **2018**, *39*, 1556–1559. [CrossRef]

- 4. Romanczyk, B.; Mishra, U.K.; Zheng, X.; Guidry, M.; Li, H.; Hatui, N.; Wurm, C.; Krishna, A.; Ahmadi, E.; Keller, S. W-Band Power Performance of SiN-Passivated N-Polar GaN Deep Recess HEMTs. *IEEE Electron. Device Lett.* **2020**, *41*, 349–352. [CrossRef]

- 5. SaifAddin, B.K.; Almogbel, A.S.; Zollner, C.J.; Wu, F.; Bonef, B.; Iza, M.; Nakamura, S.; DenBaars, S.P.; Speck, J.S. AlGaN Deep-Ultraviolet Light-Emitting Diodes Grown on SiC Substrates. *ACS Photonics* **2020**, *7*, 554–561. [CrossRef]

- 6. Alshahed, M.; Heuken, L.; Alomari, M.; Cora, I.; Toth, L.; Pecz, B.; Wachter, C.; Bergunde, T.; Burghartz, J.N. Low-Dispersion, High-Voltage, Low-Leakage GaN HEMTs on Native GaN Substrates. *IEEE Trans. Electron. Devices* **2018**, *65*, 2939–2947. [CrossRef]

- 7. Pashnev, D.; Kaplas, T.; Korotyeyev, V.; Janonis, V.; Urbanowicz, A.; Jorudas, J.; Kašalynas, I. Terahertz time-domain spectroscopy of two-dimensional plasmons in AlGaN/GaN heterostructures. *Appl. Phys. Lett.* **2020**, *117*, 051105. [CrossRef]

- 8. Jakštas, V.; Jorudas, J.; Janonis, V.; Minkevičius, L.; Kašalynas, I.; Prystawko, P.; Leszczynski, M. Development of AlGaN/GaN/SiC high-electron-mobility transistors for THz detection. *Lith. J. Phys.* **2018**, *58*, 135–140. [CrossRef]

- 9. Sai, P.; Jorudas, J.; Dub, M.; Sakowicz, M.; Jakštas, V.; But, D.B.; Prystawko, P.; Cywinski, G.; Kašalynas, I.; Knap, W.; et al. Low frequency noise and trap density in GaN/AlGaN field effect transistors. *Appl. Phys. Lett.* **2019**, *115*, 183501. [CrossRef]

- 10. Chang, S.-J.; Bhuiyan, M.A.; Won, C.-H.; Lee, J.-H.; Jung, H.W.; Shin, M.J.; Do, J.-W.; Cho, K.J.; Lee, J.-H.; Ma, T.P.; et al. Investigation of GaN channel thickness on the channel mobility in AlGaN/GaN HEMTs grown on sapphire substrate. In Proceedings of the 2017 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Seoul, Korea, 30 August–1 September 2017; pp. 87–89.

- 11. Selvaraj, S.L.; Suzue, T.; Egawa, T. Breakdown Enhancement of AlGaN/GaN HEMTs on 4-in Silicon by Improving the GaN Quality on Thick Buffer Layers. *IEEE Electron. Device Lett.* **2009**, *30*, 587–589. [CrossRef]

- 12. Poblenz, C.; Waltereit, P.; Rajan, S.; Heikman, S.; Mishra, U.K.; Speck, J.S. Effect of carbon doping on buffer leakage in AlGaN/GaN high electron mobility transistors. *J. Vac. Sci. Technol. B Microelectron. Nanom. Struct.* **2004**, 22, 1145. [CrossRef]

- 13. Manoi, A.; Pomeroy, J.W.; Killat, N.; Kuball, M. Benchmarking of Thermal Boundary Resistance in AlGaN/GaN HEMTs on SiC Substrates: Implications of the Nucleation Layer Microstructure. *IEEE Electron. Device Lett.* **2010**, *31*, 1395–1397. [CrossRef]

- 14. Cho, J.; Bozorg-Grayeli, E.; Altman, D.H.; Asheghi, M.; Goodson, K.E. Low Thermal Resistances at GaN–SiC Interfaces for HEMT Technology. *IEEE Electron. Device Lett.* **2012**, *33*, 378–380. [CrossRef]

- 15. Uren, M.J.; Moreke, J.; Kuball, M. Buffer Design to Minimize Current Collapse in GaN/AlGaN HFETs. *IEEE Trans. Electron. Devices* **2012**, *59*, 3327–3333. [CrossRef]

- 16. Fang, Z.-Q.; Claflin, B.; Look, D.C.; Green, D.S.; Vetury, R. Deep traps in AlGaN/GaN heterostructures studied by deep level transient spectroscopy: Effect of carbon concentration in GaN buffer layers. *J. Appl. Phys.* **2010**, 108, 063706. [CrossRef]

- 17. Chen, J.-T.; Bergsten, J.; Lu, J.; Janzén, E.; Thorsell, M.; Hultman, L.; Rorsman, N.; Kordina, O. A GaN–SiC hybrid material for high-frequency and power electronics. *Appl. Phys. Lett.* **2018**, *113*, 041605. [CrossRef]

- 18. Lu, J.; Chen, J.-T.; Dahlqvist, M.; Kabouche, R.; Medjdoub, F.; Rosen, J.; Kordina, O.; Hultman, L. Transmorphic epitaxial growth of AlN nucleation layers on SiC substrates for high-breakdown thin GaN transistors. *Appl. Phys. Lett.* **2019**, *115*, 221601. [CrossRef]

- 19. Chen, D.-Y.; Malmros, A.; Thorsell, M.; Hjelmgren, H.; Kordina, O.; Chen, J.-T.; Rorsman, N. Microwave Performance of 'Buffer-Free' GaN-on-SiC High Electron Mobility Transistors. *IEEE Electron. Device Lett.* **2020**, 41, 828–831. [CrossRef]

- 20. Tan, I.; Snider, G.L.; Chang, L.D.; Hu, E.L. A self-consistent solution of Schrödinger—Poisson equations using a nonuniform mesh. *J. Appl. Phys.* **1990**, *68*, 4071–4076. [CrossRef]

- 21. Snider, G.L.; Tan, I.-H.; Hu, E.L. Electron states in mesa-etched one-dimensional quantum well wires. *J. Appl. Phys.* **1990**, *68*, 2849–2853. [CrossRef]

- 22. Kruszewski, P.; Prystawko, P.; Kasalynas, I.; Nowakowska-Siwinska, A.; Krysko, M.; Plesiewicz, J.; Smalc-Koziorowska, J.; Dwilinski, R.; Zajac, M.; Kucharski, R.; et al. AlGaN/GaN HEMT structures on ammono bulk GaN substrate. *Semicond. Sci. Technol.* **2014**, *29*, 75004. [CrossRef]

- 23. Narang, K.; Bag, R.K.; Singh, V.K.; Pandey, A.; Saini, S.K.; Khan, R.; Arora, A.; Padmavati, M.V.G.; Tyagi, R.; Singh, R. Improvement in surface morphology and 2DEG properties of AlGaN/GaN HEMT. *J. Alloys Compd.* **2020**, *815*, 152283. [CrossRef]

- 24. Yang, C.; Luo, X.; Sun, T.; Zhang, A.; Ouyang, D.; Deng, S.; Wei, J.; Zhang, B. High Breakdown Voltage and Low Dynamic ON-Resistance AlGaN/GaN HEMT with Fluorine Ion Implantation in SiNx Passivation Layer. *Nanoscale Res. Lett.* **2019**, *14*, 191. [CrossRef] [PubMed]

- 25. Nifa, I.; Leroux, C.; Torres, A.; Charles, M.; Reimbold, G.; Ghibaudo, G.; Bano, E. Characterization and modeling of 2DEG mobility in AlGaN/AlN/GaN MIS-HEMT. *Microelectron. Eng.* **2019**, 215, 110976. [CrossRef]

- 26. Geng, K.; Chen, D.; Zhou, Q.; Wang, H. AlGaN/GaN MIS-HEMT with PECVD SiNx, SiON, SiO2 as Gate Dielectric and Passivation Layer. *Electronics* **2018**, 7, 416. [CrossRef]

- 27. Lutsenko, E.V.; Rzheutski, M.V.; Vainilovich, A.G.; Svitsiankou, I.E.; Tarasuk, N.P.; Yablonskii, G.P.; Alyamani, A.; Petrov, S.I.; Mamaev, V.V.; Alexeev, A.N. Investigation of Photoluminescence, Stimulated Emission, Photoreflectance, and 2DEG Properties of Double Heterojunction AlGaN/GaN/AlGaN HEMT Heterostructures Grown by Ammonia MBE. *Phys. Status Solidi* 2018, 215, 1700602. [CrossRef]

- 28. Schroder, D.K. Carrier and Doping Density. In *Semiconductor Material and Device Characterization*; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2005; pp. 61–125.

- 29. Pashnev, D.; Korotyeyev, V.V.; Jorudas, J.; Kaplas, T.; Janonis, V.; Urbanowicz, A.; Kašalynas, I. Experimental evidence of temperature dependent effective mass in AlGaN/GaN heterostructures observed via THz spectroscopy of 2D plasmons. *Appl. Phys. Lett.* **2020**, *117*, 162101. [CrossRef]

- 30. Hoon Shin, J.; Je Jo, Y.; Kim, K.-C.; Jang, T.; Sang Kim, K. Gate metal induced reduction of surface donor states of AlGaN/GaN heterostructure on Si-substrate investigated by electroreflectance spectroscopy. *Appl. Phys. Lett.* **2012**, *100*, 111908. [CrossRef]

- 31. Kruszewski, P.; Grabowski, M.; Prystawko, P.; Nowakowska-Siwinska, A.; Sarzynski, M.; Leszczynski, M. Properties of AlGaN/GaN Ni/Au-Schottky diodes on 2°-off silicon carbide substrates. *Phys. Status Solidi* **2017**, 214, 1600376. [CrossRef]

- 32. Handler, P.; Farnsworth, H.E.; Kleiner, W.H.; Law, J.T.; Garrett, C.G.B.; Autler, H.; McWhorter, A.L. Electrical Properties of a Clean Germanium Surface. In *Semiconductor Surface Physics*; Kingston, R.H., Ed.; University of Pennsylvania Press: Philadelphia, PA, USA, 1957; pp. 23–52.

- 33. Christensson, S.; Lundström, I.; Svensson, C. Low frequency noise in MOS transistors—I Theory. *Solid State Electron.* **1968**, *11*, 797–812. [CrossRef]

- 34. Chavarkar, P.; Mishra, U.K. High Electron Mobility Transistors. In *RF and Microwave Semiconductor Device Handbook*; CRC Press: Boca Raton, FL, USA, 2017; pp. 8.1–8.32.

- 35. Schwierz, F.; Liou, J.J. RF transistors: Recent developments and roadmap toward terahertz applications. *Solid State Electron.* **2007**, *51*, 1079–1091. [CrossRef]

- 36. Shinohara, K.; Regan, D.C.; Tang, Y.; Corrion, A.L.; Brown, D.F.; Wong, J.C.; Robinson, J.F.; Fung, H.H.; Schmitz, A.; Oh, T.C.; et al. Scaling of GaN HEMTs and Schottky Diodes for Submillimeter-Wave MMIC Applications. *IEEE Trans. Electron. Devices* **2013**, *60*, 2982–2996. [CrossRef]

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Article

## Unidirectional Operation of p-GaN Gate AlGaN/GaN Heterojunction FET Using Rectifying Drain Electrode

Tae-Hyeon Kim, Won-Ho Jang, Jun-Hyeok Yim and Ho-Young Cha\*

School of Electrical and Electronic Engineering, Hongik University, 94 Wausan-ro, Mapo-gu, Seoul 04066, Korea; jxajxa@g.hongik.ac.kr (T.-H.K.); jwh8904@mail.hongik.ac.kr (W.-H.J.); jhgjhg4@g.hongik.ac.kr (J.-H.Y.)

\* Correspondence: hcha@hongik.ac.kr; Tel.: +82-2-320-3062

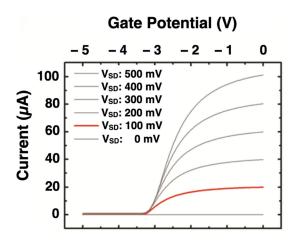

Abstract: In this study, we proposed a rectifying drain electrode that was embedded in a p-GaN gate AlGaN/GaN heterojunction field-effect transistor to achieve the unidirectional switching characteristics, without the need for a separate reverse blocking device or an additional process step. The rectifying drain electrode was implemented while using an embedded p-GaN gating electrode that was placed in front of the ohmic drain electrode. The embedded p-GaN gating electrode and the ohmic drain electrode are electrically shorted to each other. The concept was validated by technology computer aided design (TCAD) simulation along with an equivalent circuit, and the proposed device was demonstrated experimentally. The fabricated device exhibited the unidirectional characteristics successfully, with a threshold voltage of ~2 V, a maximum current density of ~100 mA/mm, and a forward drain turn-on voltage of ~2 V.

Keywords: AlGaN/GaN heterojunction; p-GaN gate; unidirectional operation; rectifying electrode

Citation: Kim, T.-H.; Jang, W.-H.; Yim, J.-H.; Cha, H.-Y. Unidirectional Operation of p-GaN Gate AlGaN/GaN Heterojunction FET Using Rectifying Drain Electrode. *Micromachines* 2021, 12, 291. https://doi.org/10.3390/mi12030291

Academic Editor: Giovanni Verzellesi

Received: 23 February 2021 Accepted: 8 March 2021 Published: 10 March 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

AlGaN/GaN heterojunction field-effect transistors (HFETs) have been extensively studied for high-efficiency power switching and high-frequency applications owing to their properties, such as wide energy bandgap, high critical electric field, and two-dimensional electron gas (2DEG) channels with high electron mobility and electron density [1–7]. While the power switching devices must be operated in a normally-off mode, conventional AlGaN/GaN HFETs exhibit normally-on characteristics. A widely adopted device structure for the normally-off mode is a p-GaN gate AlGaN/GaN HFET, where the gate region has a p-GaN layer to deplete the area underneath the AlGaN/GaN channel [4,8-13]. Such device types have been successfully commercialized and they are currently used in various power modules for different electronic devices, such as fast chargers, switching mode power supplies, and lighting drivers. Some applications of switching devices are to prevent reverse conduction in order to protect the circuit, so-called unidirectional switching characteristics. A reverse blocking device or circuit must be added to the switching device to achieve unidirectional characteristics, which enlarges the chip size and increases the manufacturing cost. Some studies have reported the unidirectional operation of GaN devices without adding extra components [14–18]. In this study, we proposed a unidirectional switching device that is based on a normally-off p-GaN gate AlGaN/GaN HFET in which a drain electrode consisted of a rectifying gating electrode and an ohmic electrode. The proposed device requires no separate blocking device or additional manufacturing costs.

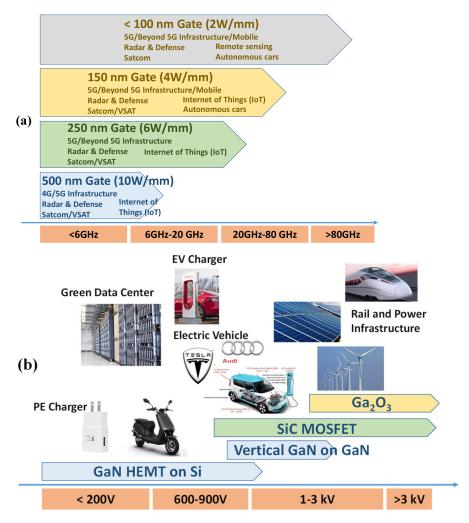

#### 2. Device Structure and TCAD Simulation

#### 2.1. Simulation Details

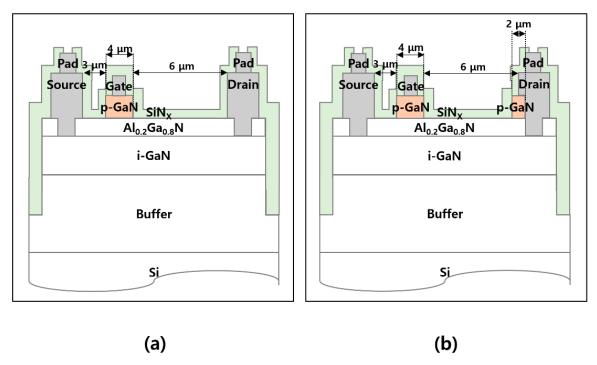

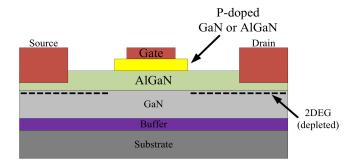

The epitaxial structure used for device simulation consists of a 70 nm p-GaN layer with a p-type doping concentration of 3  $\times$  10  $^{17}$  cm  $^{-3}$ , a 15 nm unintentionally-doped Al $_{0.2}$ Ga $_{0.8}$ N barrier layer with an n-type doping concentration of 1  $\times$  10  $^{16}$  cm  $^{-3}$ , a 35 nm unintentionally-doped GaN channel layer with an n-type doping concentration of 1  $\times$  10  $^{16}$  cm  $^{-3}$ , and a

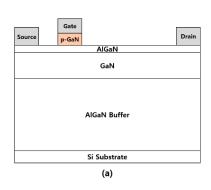

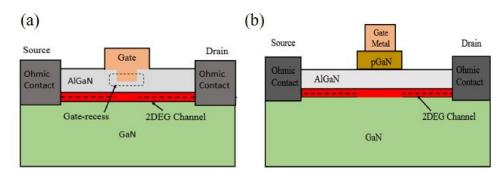

$1.95~\mu m~Al_{0.05}Ga_{0.95}N$  buffer layer. Figure 1a,b demonstrate the cross-sectional schematics of a conventional p-GaN gate AlGaN/GaN HFET and a proposed unidirectional device, respectively, with a gate length of 2  $\mu m$  for both of the structures. The length of the p-GaN drain region was 1  $\mu m$  for the unidirectional device, which was separated from the drain electrode by  $0.5~\mu m$ .

**Figure 1.** Cross-sectional schematics of (a) p-GaN gate AlGaN/GaN heterojunction field-effect transistor (HFET) and (b) unidirectional HFET.

The simulations were carried out using SILVACO ATLAS (Silvaco, Silicon Valley, CA, USA). Figure 2 shows the models used in the simulation code, which was adopted from an example file provided by SILVACO (ganfetex07.in). A detailed explanation of the simulation models can be found in ref [19], which includes a polarization model, a temperature dependent low field mobility model, a nitride specific high field dependent mobility model, a lattice heating model, and a trap model.

------

models consrh auger fermi print temp=300 mobility GaNsat.n models lat.temp ni.fermi mobility albrct.n bn.albrct=3e-05 an.albrct=3e-05 mobility region=5 albrct.p bp.albrct=1e04 ap.albrct=1e04 model ten.piezo psp.scale=0.67 piezo.scale=0.67 calc.strain model region=5 pch.ins

trap region=2 donor e.level=3.2 density=1.27e18 sign=1e-15 sigp=1e-15 degen=2 trap region=2 acceptor e.level=0.36 density=7e17 sign=1e-15 sigp=1e-15 degen=4

thermcontact num=1 name=substrate alpha=2500

-----

**Figure 2.** Physical models and parameters used in simulation code.

#### 2.2. Simulation Result and Disscussion

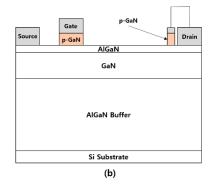

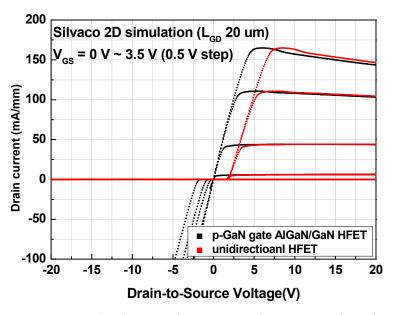

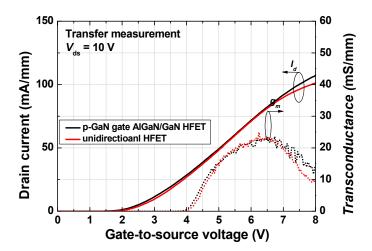

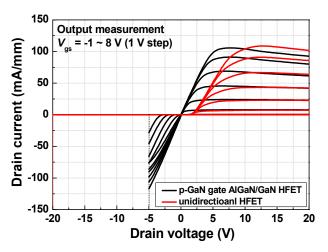

Figure 3 compares the simulation results of the forward and reverse characteristics for two different structures. The conventional device exhibited a typical normally-off operation with reverse conduction characteristics, whereas the proposed structure exhibited the same normally-off operation with reverse blocking characteristics. The threshold voltage was 1.8 V for both devices, which was determined by the p-GaN gate electrode. A positive shift

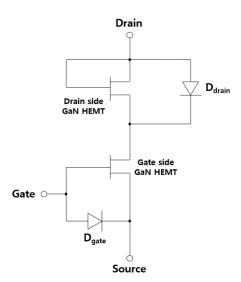

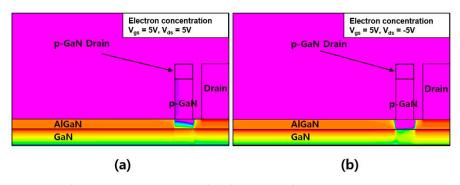

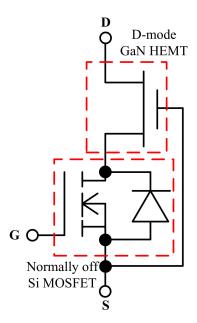

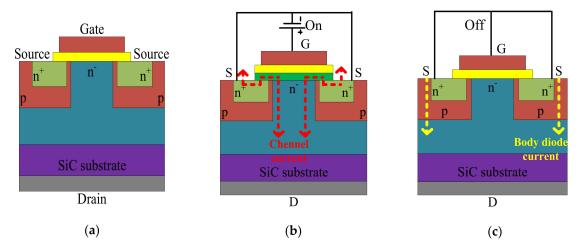

in the forward drain turn-on characteristics was observed for the proposed unidirectional device, which is the same as the gate threshold voltage of the device. The positive shift and reverse blocking characteristics can be explained while using the equivalent circuit that is shown in Figure 4. The p-GaN gate can be represented by a gate electrode of the HFET in conjunction with a PN heterojunction diode. When the p-GaN gate voltage exceeds the threshold voltage (1.8 V), the 2DEG channel is formed between the AlGaN barrier layer and GaN channel layer, creating a conduction path between the source and drain. As the p-GaN gate voltage becomes higher than the forward turn-on voltage of the p-GaN/AlGaN/GaN heterojunction diode, the current flows from the p-GaN gate to the source. On the drain side, the p-GaN region acts as a "gate" electrode, which is electrically shorted to the ohmic electrode. Therefore, the current can flow from the ohmic drain electrode to the source electrode by creating the 2DEG channel under the p-GaN region, as the drain voltage becomes higher than the gate threshold voltage (1.8 V). That is, no current flows when the drain voltage is lower than the gate threshold voltage, which is why the device has forward drain turn-on characteristics that are similar to the gate threshold characteristics. As the drain voltage becomes higher than the forward turn-on voltage of the p-GaN/AlGaN/GaN heterojunction diode, the current can flow from both the p-GaN drain and ohmic drain regions to the source electrode. In the reverse region, when the drain voltage is negative, the p-GaN drain region is reverse-biased and it further depletes the channel, blocking the current flow from the drain. Therefore, the device exhibits reverse blocking characteristics. The electron concentration distributions under forward and reverse modes are compared in Figure 5a,b, respectively. The electron channel exists under the p-GaN drain region in the forward mode that is shown in Figure 5a, where both gate and drain voltages were +5 V. On the other hand, the channel under the p-GaN drain region was depleted in the reverse mode that is shown in Figure 5b where the gate and drain voltages were +5 V and -5 V, respectively.

**Figure 3.** Forward and reverse characteristics of p-GaN gate AlGaN/GaN HFET (black lines) and unidirectional HFET (red lines).

Figure 4. Equivalent circuit of unidirectional HFET.

**Figure 5.** Electron concentration under the p-GaN drain region at (a)  $V_{\rm gs} = 5$  V and  $V_{\rm ds} = 5$  V and (b)  $V_{\rm gs} = 5$  V and  $V_{\rm ds} = -5$  V. Two electrodes (p-GaN drain and drain electrodes) are shorted electrically to each other in the simulation.

#### 3. Fabrication

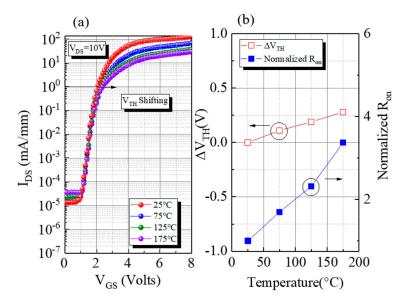

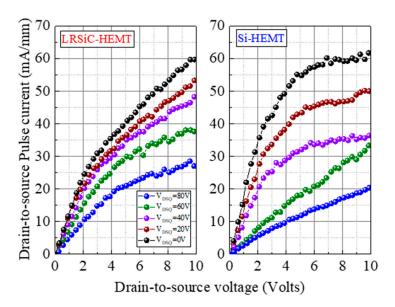

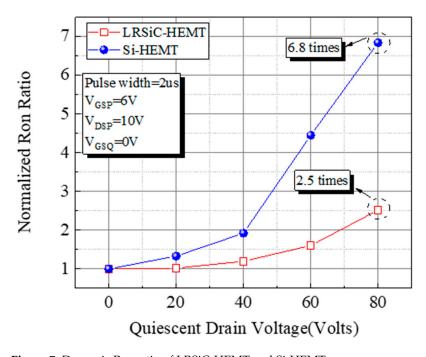

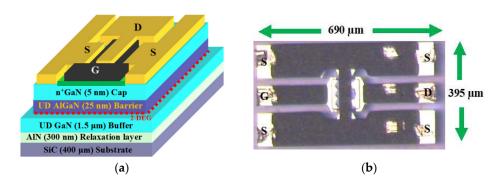

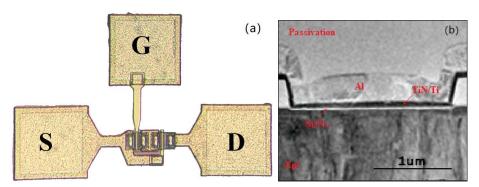

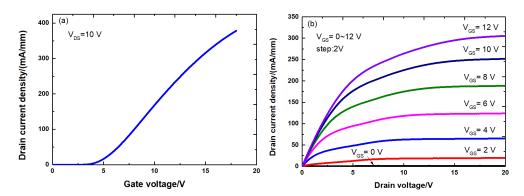

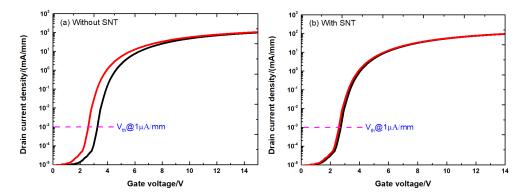

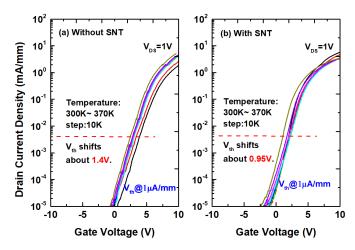

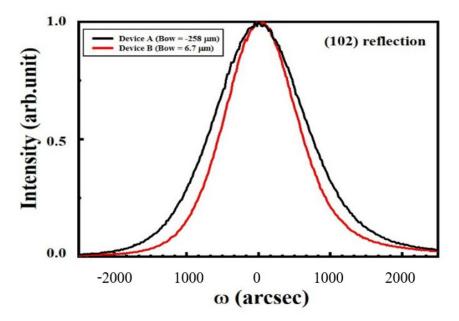

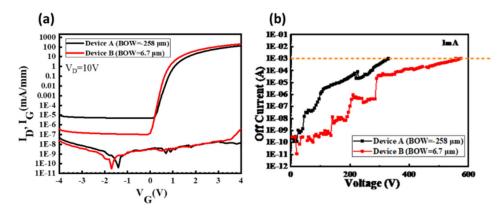

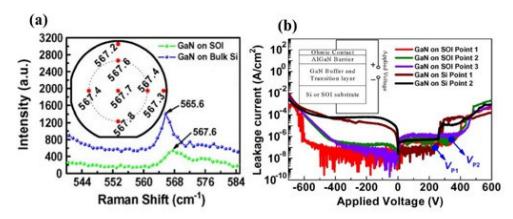

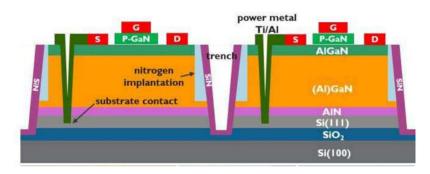

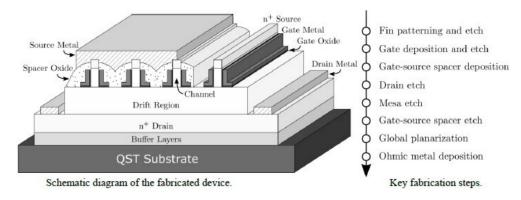

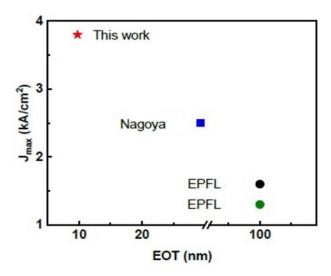

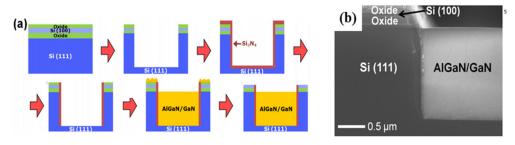

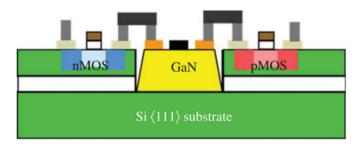

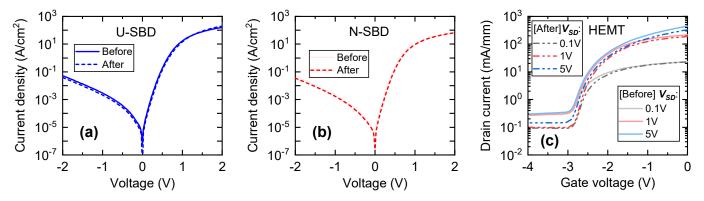

#### 3.1. Device Structure and Fabrication