micromachines

# MEMS Packaging Technologies and 3D Integration

Edited by Seonho Seok Printed Edition of the Special Issue Published in *Micromachines*

MDPI

www.mdpi.com/journal/micromachines

# MEMS Packaging Technologies and 3D Integration

# MEMS Packaging Technologies and 3D Integration

Editor

Seonho Seok

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

*Editor* Seonho Seok C2N (Center for Nanosciences and Nanotechnologies) University-Paris-Saclay Palaiseau France

*Editorial Office* MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Micromachines* (ISSN 2072-666X) (available at: www.mdpi.com/journal/micromachines/special\_issues/MEMS\_Packaging\_Integration).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-4258-4 (Hbk) ISBN 978-3-0365-4257-7 (PDF)

Cover image courtesy of Hyungdal Park

© 2022 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## Contents

| About the Editor                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "MEMS Packaging Technologies and 3D Integration"                                                                                                                                                                                                                                                                |

| Seonho SeokEditorial for the Special Issue "MEMS Packaging Technologies and 3D Integration"Reprinted from: <i>Micromachines</i> 2022, 13, 749, doi:10.3390/mi130507491                                                                                                                                                     |

| HyungDal Park, Wonsuk Choi, Seonghwan Oh, Yong-Jun Kim, Seonho Seok and Jinseok                                                                                                                                                                                                                                            |

| KimA Study on Biocompatible Polymer-Based Packaging of Neural Interface for ChronicImplantationReprinted from: <i>Micromachines</i> 2022, 13, 516, doi:10.3390/mi130405165                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                            |

| <b>Zhen Liu, Mingang Fang, Lei Shi, Yu Gu, Zhuo Chen and Whenhui Zhu</b><br>Characteristics of Cracking Failure in Microbump Joints for 3D Chip-on-Chip Interconnections<br>under Drop Impact                                                                                                                              |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 281, doi:10.3390/mi13020281                                                                                                                                                                                                                                 |

| El-Mostafa Bourim, Il-Suk Kang and Hee Yeoun Kim<br>Investigation of Integrated Reactive Multilayer Systems for Bonding in Microsystem<br>Technology                                                                                                                                                                       |

| Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 1272, doi:10.3390/mi12101272                                                                                                                                                                                                                                |

| Seonho Seok<br>Polymer-Based Biocompatible Packaging for Implantable Devices: Packaging Method,<br>Materials, and Reliability Simulation<br>Reprinted from: <i>Micromachines</i> 2021, <i>12</i> , 1020, doi:10.3390/mi12091020                                                                                            |

| Lun Hao Loo Bin Kuan Li Hai Wan Hung Wallace Chuang Eskart Schollkes and Kivekanu                                                                                                                                                                                                                                          |

| Jun-Hao Lee, Pin-Kuan Li, Hai-Wen Hung, Wallace Chuang, Eckart Schellkes and Kiyokazu<br>Yasuda et al.                                                                                                                                                                                                                     |

| Geometrical Effects on Ultrasonic Al Bump Direct Bonding for Microsystem Integration:                                                                                                                                                                                                                                      |

| Simulation and Experiments<br>Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 750, doi:10.3390/mi12070750                                                                                                                                                                                                   |

| <b>Gil Cherniak, Moshe Avraham, Sharon Bar-Lev, Gady Golan and Yael Nemirovsky</b><br>Study of the Absorption of Electromagnetic Radiation by 3D, Vacuum-Packaged,<br>Nano-Machined CMOS Transistors for Uncooled IR Sensing<br>Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 563, doi:10.3390/mi12050563 |

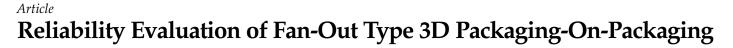

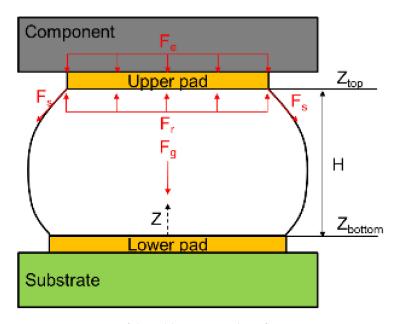

| Pao-Hsiung Wang, Yu-Wei Huang and Kuo-Ning Chiang                                                                                                                                                                                                                                                                          |

| Reliability Evaluation of Fan-Out Type 3D Packaging-On-Packaging<br>Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 295, doi:10.3390/mi12030295                                                                                                                                                             |

| Qian-Yo Lee, Ming-Xuan Lee and Yen-Chun Lee                                                                                                                                                                                                                                                                                |

| A Hybrid Fuzzy Decision Model for Evaluating MEMS and IC Integration Technologies<br>Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 276, doi:10.3390/mi12030276                                                                                                                                            |

| Mengcheng Wang, Shenglin Ma, Yufeng Jin, Wei Wang, Jing Chen and Liulin Hu et al.                                                                                                                                                                                                                                          |

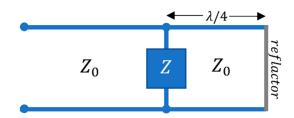

| A RF Redundant TSV Interconnection for High Resistance Si Interposer<br>Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 169, doi:10.3390/mi12020169                                                                                                                                                         |

| <b>Explaned</b> Hold Hill Onwelling <b>Evel</b> , 12, 107, 40110.0070/ Hul2020107                                                                                                                                                                                                                                          |

| Bo Jiang, Shenhu Huang, Jing Zhang and Yan Su                                                         |

|-------------------------------------------------------------------------------------------------------|

| Analysis of Frequency Drift of Silicon MEMS Resonator with Temperature                                |

| Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>12</i> , <i>26</i> , doi:10.3390/mi12010026     |

| Seonho Seok, HyungDal Park and Jinseok Kim                                                            |

| Characterization and Analysis of Metal Adhesion to Parylene Polymer Substrate Using Scotch            |

| Tape Test for Peripheral Neural Probe                                                                 |

| Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 605, doi:10.3390/mi11060605 <b>159</b> |

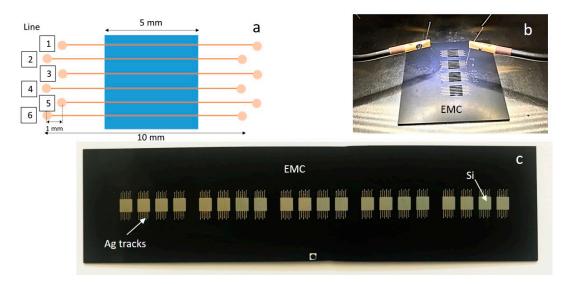

| Ali Roshanghias, Marc Dreissigacker, Christina Scherf, Christian Bretthauer, Lukas Rauter             |

| and Johanna Zikulnig et al.                                                                           |

| On the Feasibility of Fan-Out Wafer-Level Packaging of Capacitive Micromachined Ultrasound            |

| Transducers (CMUT) by Using Inkjet-Printed Redistribution Layers                                      |

| Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 564, doi:10.3390/mi11060564            |

| Michitaka Yamamoto, Takashi Matsumae, Yuichi Kurashima, Hideki Takagi, Tadatomo Suga                  |

| and Seiichi Takamatsu et al.                                                                          |

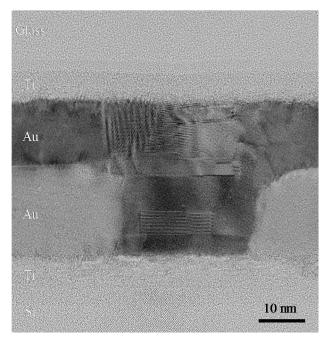

| Effect of Au Film Thickness and Surface Roughness on Room-Temperature Wafer Bonding and               |

| Wafer-Scale Vacuum Sealing by Au-Au Surface Activated Bonding                                         |

| Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 454, doi:10.3390/mi11050454            |

## About the Editor

#### Seonho Seok

Seonho Seok received the M.S. and Ph.D. degrees in electrical engineering from Seoul National University, Seoul, Korea in 1999 and 2004, respectively. He was a postdoctoral researcher at Center for Advanced Transceiver Systems (CATS) in Seoul National University and at IEMN, CNRS in France from 2004 to 2007. He worked as a permanent researcher of CNRS at IEMN from 2007 to 2014. Starting from March 2014, he is working at micro-nano systems and biotechnologies team in C2N (Center for Nanosciences and Nanotechnologies)-University Paris-Saclay.

His current research interests are wafer-level (vacuum) packaging, transfer technique based on adhesion engineering, 3D (heterogeneous) integration, MEMS and sensors, 3D antennas, energy harvesting, and related multi-physics modellings, etc.

# Preface to "MEMS Packaging Technologies and 3D Integration"

MEMS packaging is an essential technique for successful commercialization of MEMS products as MEMS has moving parts and an application-specific nature. A classic approach of MEMS packaging is to bond silicon or glass cap wafers to MEMS wafers. Therefore, it is typically implemented under high pressure and high temperature conditions. Advanced approaches use a thin-film deposition technique and then a cavity for MEMS is realized via sacrificial etch through access holes at the thin film cap. The packaging cap transfer technique is a compromise between the two approaches, since it makes it possible to bond and transfer a thin packaging cap to the released MEMS device. MEMS devices and IC are being integrated in a 3D fashion to achieve a better performance, and implantable devices need special packaging techniques. Thus, this Special Issue gathers research papers, short communications, and review articles that focus on MEMS packaging technologies and related integration methods. This Special Issue will help you to catch the trend of the recent MEMS or electronic device packaging and 3D integration technologies.

> Seonho Seok Editor

### **Editorial Editorial for the Special Issue "MEMS Packaging Technologies and 3D Integration"**

Seonho Seok 🕩

Center for Nanoscience and Nanotechnology (C2N), University-Paris-Saclay, 91400 Orsay, France; seonho.seok@u-psud.fr

As fabrication technologies advance, the packaging of MEMS device is being developed in two main directions: MEMS device packaging and MEMS or sensor system integration. MEMS device packaging is an essential technique for successful commercialization of MEMS product, as MEMS devices inevitably have moving and fragile parts. MEMS devices tend to be packaged in chip-scale, or, namely, zero-level packaging as fabrication technologies advance in place of conventional package of a commercial product such as DIP (Dual Inline Package). For certain MEMS products, vacuum packaging has been achieved with zero-level packaging approaches [1,2]. Such a MEMS packaging has mainly been realized by bonding techniques with joint materials such as metals, polymers, etc. A packaging cap with housing cavity is bonded to a sealing ring surrounding MEMS devices. The lid wafers are generally fabricated with so-called hard materials such as silicon, glass, and so on. For certain MEMS devices, different cap materials, for example, thin films or polymer films, have been adopted for high frequency devices and inertial sensors [3–7]. Thin film packaging is fabricated by conventional semiconductor process and sacrificial etch and thus may have advantages of small package sizes and low costs due to its high throughput. The bonding techniques typically used for MEMS device packaging are interfacial bonding and intermediate layer bonding [8–12]. The interfacial bonding depends on the chemical reaction between two joint materials, while the intermediate layer bonding needs additional materials as adhesive layers. Anodic bonding and silicon fusion bonding are frequently used interface bonding techniques. The interfacial bonding requires high surface cleanness as well as high surface flatness, and it is carried out under high temperature and high applying pressure conditions. Thus, the interfacial bonding has certain constraints for temperature sensitive MEMS devices. Intermediate layer bonding needs good adhesion materials with associated substrates to avoid unwanted delamination of the sealing layers. As the intermediate layer material determines the bonding condition such as temperature, it can be implemented at relatively low temperature. For the packaging based on bonding technologies, attention should be paid to thermal expansion coefficient difference among the associated materials because it would cause undesired high packaging stress. Packaging stress is a principal cause of its reliability, and thus modeling and simulation of electronic and MEMS packages have been frequently performed through FEM (Finite Element Method) to understand mechanical behavior of the packages [13-17]. To obtain reliable simulation results, material properties and their behavior depending on temperature or external load should be well characterized. As an alternative packaging approach, thin film encapsulation integrates the packaging process with the MEMS device process on the same wafer. MEMS structures covered by an additional sacrificial layer are first released by sacrificial etching through channels or holes, and then the access holes are sealed by depositing an overcoat material. The thin-film packaging materials should be deposited or formed without degrading or changing the properties of MEMS structure, and it takes a longer time to release overall packaging cap including the packaged MEMS devices via the accesses of etching solution or gas [18]. MEMS packaging has application-specific features. In other words, it has different

Citation: Seok, S. Editorial for the Special Issue "MEMS Packaging Technologies and 3D Integration". *Micromachines* 2022, *13*, 749. https:// doi.org/10.3390/mi13050749

Received: 29 April 2022 Accepted: 30 April 2022 Published: 9 May 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). approaches depending on application. For example, high-performance inertial sensors may need vacuum packaging fabricated with solid metal-to-metal bonding, but it could not be applied to RF-MEMS packaging because such a metallic sealing ring may create additional loss or undesired parasitic effect at higher frequencies. Another aspect of MEMS product packaging is integration and packaging with integrated circuit (IC) chips, as MEMS output signals should be processed for operation. The integration of MEMS and ICs is implemented through a hybrid multi-chip solution or an SoC solution. SoC solutions have the fabrication and integration of MEMS and IC components implemented on the same substrate, and the fabricated chips are separated only at or near the end of the fabrication process. The hybrid integration of MEMS and IC technology has been implemented by 2D integration approaches. MEMS and IC wafers are fabricated independently and placed on a common printed circuit board (PCB) and then interconnected with wire-bonding. Multi-Chip-Module (MCM) is an advanced integration technique of hybrid integration; MEMS and IC chips are placed side-by-side in a common package and interconnected at the package level, typically via wire and/or flip-chip bonding [19]. This approach has evolved into system-in-packages, also referred to as vertical or stacked multi-chip modules, consisting of chips that are attached on top of each other and interconnected via wire and/or flip-chip bonding, either directly or through additional re-distribution layers. The main benefits of these 3D stacked approaches are their higher integration densities, shorter signal path lengths, and smaller package footprints/volumes in comparison with the 2D multi-chip modules. Moreover, package-level system-on-packaging can integrate optics, wireless communication, and power module along with MEMS and IC on a common package. For the packaging and integration explained earlier, interconnection techniques have been important as the packaging size determines the cost of the final product [20–22]. Interconnect techniques frequently used for MCM packaging are wire-bonding, solder balls, metal stud bumps, and ACF (Anisotropic Conductive Film). Most of the interconnected techniques require certain amount of pressure at elevated temperature for efficient bonding between materials in joint. In case of metallic joints, such as solder balls and metal stud bumps, a relatively thin adhesion or UBM (under bump metallurgy) layer would be critical for the package reliability, as the adhesion layer could be delaminated or disconnected due to intermetallic diffusion. In certain cases, the length of metallic interconnect determines the life-time of the package due to shear stress limit [23].

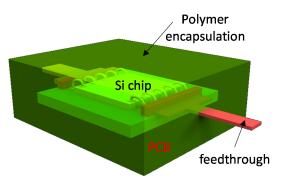

Due to the emergence of novel electronic devices such as flexible electronics or implantable medical devices, the Si IC should be integrated with flexible substrate to comply with new applications. Two-dimensional-material-based circuit approaches are attractive for flexible electronics, but advances in key areas such as robust manufacturing and reliable mechanical characterization are still necessary [24]. The integration of existing IC and novel biocompatible polymeric devices is highly demanded for new implantable medical devices, for example, neural prosthetics [25,26]. Such medical devices should be encapsulated in a biocompatible way for human body implantation. The reliability and life-time of the implant system are highly dependent on both packaging materials and technology. In general, implantable device packaging houses the electronic or mechanical system through the polymer encapsulation [27], welding, or bonding of metal [28,29] and ceramics [30]. Materials of the polymer encapsulation package include epoxies, silicones, polyurethanes, polyimides, silicon-polyimides, parylenes, polycyclic-olefins, silicon-carbons, benzocyclobutenes (BCB), and liquid crystal polymers. Furthermore, the packaging size of the implant should be minimized to avoid unwanted foreign body reaction (FBR) during implantation. The biocompatible packaging has been shown in different implantable medical devices, for example, a cardiac monitoring system implemented with commercial three-axis accelerometer, pressure sensor device mounted on a stent graft, implantable retina stimulator implemented by MFI (MicroFlex Interconnection) technology, thin-film interconnect for 1000-electrode retina prothesis, etc. [31].

In conclusion, MEMS packaging has been evolved from MEMS device packaging to MEMS system packaging as the application of MEMS devices has been widely extended.

Innovative and efficient packaging technologies becomes more and more important as well as new packaging materials. Concerning heterogeneous integration highly demanded for new applications, the interconnection between different material such as silicon and polymers should be adapted in order to reduce mechanical and electrical optimization. This Special Issue presents 12 research papers and 1 review article on recently developed MEMS packaging technologies and 3D integration. It will serve to elucidate the need for new packaging technologies and its recent research trend.

**Conflicts of Interest:** The author declares no conflict of interest.

#### References

- 1. Lee, B.; Seok, S.; Chun, K. A study on wafer level vacuum packaging for MEMS devices. J. Micromech. Microeng. 2003, 13, 663–669. [CrossRef]

- Cherniak, G.; Avraham, M.; Bar-Lev, S.; Golan, G.; Nemirovsky, Y. Study of the Absorption of Electromagnetic Radiation by 3D, Vacuum-Packaged, Nano-Machined CMOS Transistors for Uncooled IR Sensing. *Micromachines* 2021, 12, 563. [CrossRef] [PubMed]

- 3. Santagata, F.; Zaal, J.J.M.; Huerta, V.G.; Mele, L.; Creemer, J.F.; Sarro, P.M. Mechanical Design and Characterization for MEMS Thin-Film Packaging. *J. Microelectromech. Syst.* **2012**, *21*, 100–109. [CrossRef]

- Zekry, J.; Tezcan, D.S.; Celis, J.-P.; Puers, R.; van Hoof, C.; Tilmans, H.A.C. Wafer-level thin film vacuum packages for MEMS using nanoporous anodic alumina membranes. In Proceedings of the 16th International Solid-State Sensors, Actuators and Microsystems Conference (Transducers), Beijing, China, 5–9 June 2011; pp. 974–977.

- 5. Lee, B.-K.; Choi, D.-H.; Yoon, J.-B. Use of nanoporous columnar thin film in the wafer-level packaging of MEMS devices. *J. Micromech. Microeng.* **2010**, *20*, 045002. [CrossRef]

- 6. Seok, S.; Rolland, N.; Rolland, P.-A. Packaging methodology for RF devices using a BCB membrane transfer technique. *J. Micromech. Microeng.* **2006**, *16*, 2384–2388. [CrossRef]

- 7. Kim, J.-G.; Seok, S.; Rolland, N.; Rolland, P.-A. Polymer-based zero-level packaging technology for high frequency RF applications by wafer bonding/debonding technique using an anti-adhesion layer. *Int. J. Precis. Eng. Manuf.* **2012**, *13*, 1861–1867. [CrossRef]

- 8. Bower, R.W.; Ismail, M.S.; Roberds, B.E. Low temperature Si3N4 direct bonding. Appl. Phys. Lett. 1993, 62, 3485–3487. [CrossRef]

- 9. Bourim, E.-M.; Kang, I.-S.; Kim, H.Y. Investigation of Integrated Reactive Multilayer Systems for Bonding in Microsystem Technology. *Micromachines* **2021**, *12*, 1272. [CrossRef]

- Lee, J.-H.; Li, P.-K.; Hung, H.-W.; Chuang, W.; Schellkes, E.; Yasuda, K.; Song, J.-M. Geometrical Effects on Ultrasonic Al Bump Direct Bonding for Microsystem Integration: Simulation and Experiments. *Micromachines* 2021, 12, 750. [CrossRef]

- 11. Yamamoto, M.; Matsumae, T.; Kurashima, Y.; Takagi, H.; Suga, T.; Takamatsu, S.; Itoh, T.; Higurashi, E. Effect of Au Film Thickness and Surface Roughness on Room-Temperature Wafer Bonding and Wafer-Scale Vacuum Sealing by Au-Au Surface Activated Bonding. *Micromachines* **2020**, *11*, 454. [CrossRef]

- Seok, S.; Fryziel, M.; Rolland, N.; Rolland, P.-A. Enhancement of bonding strength of packaging based on BCB bonding for RF devices. *Microsyst. Technol.* 2012, 18, 2035–2039. [CrossRef]

- Seok, S. Fabrication and Modeling of Nitride Thin-Film Encapsulation Based on Anti-Adhesion-Assisted Transfer Technique and Nitride/BCB Bilayer Wrinkling. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1301–1307.

- 14. Ayhan, A.O.; Nied, H.F. Finite element analysis of interface cracking in semiconductor packages. *IEEE Trans. Components Packag. Technol.* **1999**, *22*, 503–511. [CrossRef]

- 15. Wang, P.-H.; Huang, Y.-W.; Chiang, K.-N. Reliability Evaluation of Fan-Out Type 3D Packaging-On-Packaging. *Micromachines* **2021**, *12*, 295. [CrossRef] [PubMed]

- 16. Lee, Q.-Y.; Lee, M.-X.; Lee, Y.-C. A Hybrid Fuzzy Decision Model for Evaluating MEMS and IC Integration Technologies. *Micromachines* **2021**, *12*, 276. [CrossRef]

- 17. Jiang, B.; Huang, S.; Zhang, J.; Su, Y. Analysis of Frequency Drift of Silicon MEMS Resonator with Temperature. *Micromachines* **2021**, *12*, 26. [CrossRef]

- 18. Seok, S.; Rolland, N.; Rolland, P.-A. A theoretical and experimental study of the BCB thin-film cap zero-level package based on FEM simulations. *J. Micromech. Microeng.* **2010**, *20*, 095010. [CrossRef]

- 19. Fischer, A.C.; Forsberg, F.; Lapisa, M.; Bleiker, S.J.; Stemme, G.; Roxhed, N.; Niklaus, F. Integrating MEMS and ICs. *Microsyst. Nanoeng.* **2015**, *1*, 15005. [CrossRef]

- 20. Liu, Z.; Fang, M.; Shi, L.; Gu, Y.; Chen, Z.; Zhu, W. Characteristics of Cracking Failure in Microbump Joints for 3D Chip-on-Chip Interconnections under Drop Impact. *Micromachines* 2022, 13, 281. [CrossRef]

- Wang, M.; Ma, S.; Jin, Y.; Wang, W.; Chen, J.; Hu, L.; He, S. A RF Redundant TSV Interconnection for High Resistance Si Interposer. *Micromachines* 2021, 12, 169. [CrossRef]

- Roshanghias, A.; Dreissigacker, M.; Scherf, C.; Bretthauer, C.; Rauter, L.; Zikulnig, J.; Braun, T.; Becker, K.-F.; Rzepka, S.; Schneider-Ramelow, M. On the Feasibility of Fan-Out Wafer-Level Packaging of Capacitive Micromachined Ultrasound Transducers (CMUT) by Using Inkjet-Printed Redistribution Layers. *Micromachines* 2020, 11, 564. [CrossRef]

- Wu, C.; Liu, J.; Yeung, N. The effects of bump height on the reliability of ACF in flip-chip. Solder. Surf. Mt. Technol. 2001, 13, 25–30. [CrossRef]

- 24. Glavin, N.R.; Muratore, C.; Snure, M. Toward 2D materials for flexible electronics: Opportunities and outlook. *Oxf. Open Mater. Sci.* **2020**, *1*, itaa002. [CrossRef]

- Park, H.; Choi, W.; Oh, S.; Kim, Y.-J.; Seok, S.; Kim, J. A Study on Biocompatible Polymer-Based Packaging of Neural Interface for Chronic Implantation. *Micromachines* 2022, 13, 516. [CrossRef] [PubMed]

- Seok, S.; Park, H.; Kim, J. Characterization and Analysis of Metal Adhesion to Parylene Polymer Substrate Using Scotch Tape Test for Peripheral Neural Probe. *Micromachines* 2020, 11, 605. [CrossRef] [PubMed]

- 27. Hassler, C.; von Metzen, R.P.; Ruther, P.; Stieglitz, T. Characterization of parylene C as an encapsulation material for implanted neural prostheses. *J. Biomed. Mater. Res. Part B* 2010, *93*, 266–274. [CrossRef]

- 28. Kramar, T.; Michalec, I.; Kovacocy, P. The laser beam welding of titanium grade 2 alloy. *GRANT J.* **2012**, *1*, 77–79.

- Schuettler, M.; Ordonez, J.S.; Santisteban, T.S.; Schatz, A.; Wilde, J.; Stieglitz, T. Fabrication and test of a hermetic miniature implant package with 360 electrical feedthroughs. In Proceedings of the 2010 Annual International Conference of the IEEE Engineering in Medicine and Biology, Buenos Aires, Argentina, 31 August–4 September 2010; Volume 2010, pp. 1585–1588.

- 30. Chlebowski, A.L.; Chow, E.Y.; Ellison, C.; Irazoqui, P.P. Integrated LTCC packaging for use in biomedical devices. *Bio-Med. Mater. Eng.* **2012**, *22*, 361–372. [CrossRef]

- 31. Seok, S. Polymer-Based Biocompatible Packaging for Implantable Devices: Packaging Method, Materials, and Reliability Simulation. *Micromachines* **2021**, *12*, 1020. [CrossRef]

HyungDal Park <sup>1,2</sup>, Wonsuk Choi <sup>1,3</sup>, Seonghwan Oh <sup>1,3</sup>, Yong-Jun Kim <sup>2,\*</sup>, Seonho Seok <sup>4,\*</sup> and Jinseok Kim <sup>1,\*</sup>

- <sup>1</sup> Center for Bionics, Korea Institute of Science and Technology (KIST), Seoul 02792, Korea;

- hyungdal@kist.re.kr (H.P.); wonsuk@kist.re.kr (W.C.); emart11@kist.re.kr (S.O.)

- <sup>2</sup> School of Mechanical Engineering, Yonsei University, Seoul 03722, Korea

<sup>3</sup> Department of Biomedical Engineering, Korea University, Seoul 02841, Korea

- <sup>3</sup> Department of Biomedical Engineering, Korea University, Seoul 02841, Korea 4 Center for Nanoscience and Nanotechnology (C2N). University, Paris-Saclay 91

- <sup>4</sup> Center for Nanoscience and Nanotechnology (C2N), University-Paris-Saclay, 91400 Orsay, France

- \* Correspondence: yjk@yonsei.ac.kr (Y.-J.K.); seonho.seok@u-psud.fr (S.S.); jinseok@kist.re.kr (J.K.)

Abstract: This paper proposed and verified the use of polymer-based packaging to implement the chronic implantation of neural interfaces using a combination of a commercial thermal epoxy and a thin parylene film. The packaging's characteristics and the performance of the vulnerable interface between the thermal epoxy layer and polyimide layer, which is mainly used for neural electrodes and an FPCB, were evaluated through in vitro, in vivo, and acceleration experiments. The performance of neural interfaces—composed of the combination of the thermal epoxy and thin parylene film deposition as encapsulation packaging-was evaluated by using signal acquisition experiments based on artificial stimulation signal transmissions through in vitro and in vivo experiments. It has been found that, when commercial thermal epoxy normally cured at room temperature was cured at higher temperatures of 45  $^{\circ}$ C and 65  $^{\circ}$ C, not only is its lifetime increased with about twice the room-temperature-based curing conditions but also an interfacial adhesion is higher with more than twice the room-temperature-based curing conditions. In addition, through in vivo experiments using rats, it was confirmed that bodily fluids did not flow into the interface between the thermal epoxy and FPCB for up to 18 months, and it was verified that the rats maintained healthy conditions without occurring an immune response in the body to the thin parylene film deposition on the packaging's surface.

Keywords: polymer packaging; neural interface; chronic implantation

#### 1. Introduction

Until recently, implantable bioelectronic devices have been developed in various forms for the purpose of monitoring the conditions of diseases through measurements of biological or neural signals and treating or suppressing specific diseases through electrical/optical/magnetic/ultrasound-based stimulations. Basically, implantable bioelectronic devices have been packaged with a material that can minimize the occurrence of an immune response without being damaged or leaking, even when surrounding muscles move after implantations. Most recently, commercialized bioelectronic medical devices have used Ti packaging that can minimize deformations from external forces, such as muscle movements in the main body, and the outside of such packaging is encapsulated with a silicone elastomer that satisfies biocompatibility. At the same time, the packaging has a small number of electrical channels which have millimeter-level diameters, so an individually sealed connector is used to connect it to the main body of implantable bioelectronic devices [1–3]. In addition, since most Ti packaging has relatively bulky dimensions compared to neural electrodes, the implantable site is limited to the subcutaneous area of the chest. For the above reason, the neural electrode and the Ti-packaged main body are connected through a wire while maintaining a certain distance or more. Such a configuration does not cause serious problems when the number of channels for neural signal

Citation: Park, H.; Choi, W.; Oh, S.; Kim, Y.-J.; Seok, S.; Kim, J. A Study on Biocompatible Polymer-Based Packaging of Neural Interface for Chronic Implantation. *Micromachines* 2022, *13*, 516. https://doi.org/ 10.3390/mi13040516

Academic Editor: Nam-Trung Nguyen

Received: 23 February 2022 Accepted: 24 March 2022 Published: 26 March 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). monitoring or stimulation signal transmission is small. However, if the number of channels increases, there is a high possibility of problems due to the plurality of lines connected between the neural electrodes and the main body. In order to prevent failures or the twisting of each wire, a method of winding each line in a circle several times in the body is also applied [4,5]. However, this approach is difficult to utilize as an ultimate solution because it has no choice but to increase the length of the wire inserted into the body and increases the area of the location where the immune response in the body occurs. Recently, demand for a multi-channel neural interface with a high neural signal selectivity and fine local stimulation has increased remarkably. This multi-channel neural interface is being used as an advanced approach to implementing a neural signal-based neuroprosthesis for the daily life recovery of amputees and for electroceuticals, which is rising as a new treatment technology for chronic diseases [6–14]. The multi-channel neural interfaces basically have diverse designs depending on the implant sites (brain, spinal cord, peripheral nerve, and vagus nerve), and each neural electrode is commonly connected to a pre-amplifier device regardless of whether it is wire- or wireless-driven [11–14]. For the connection between the neural electrode and the pre-amplifier device, it is common to use wire bonding or an unsealed connector integrated on a PCB and to mainly use the form of encapsulating the connection part and pre-amplifier device with a biocompatible polymer [15–19]. However, the reason to use the small packaging configuration with the biocompatible polymer can be inferred from the spatial limitation of the implantation site. Moreover, in clinical trials, the system is generally removed again with a surgical procedure after a certain period of an experiment [20–22]. Not only has a finite-element analysis study been based on the characteristics of polymer materials applied to polymer-based packaging and materials used as a diffusion barrier but also a verification study of a lifetime has been reported based on a bodily fluid penetration between the polymer insulation layer and the metal electrodes [23,24]. Consequentially, research on polymer-based packaging methods and characteristic verifications are insufficient, even though the purpose of the neural interface is the capability of chronic implantation with the continuous monitoring of the disease condition and delivering stimulation signals.

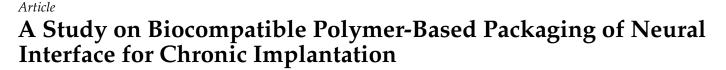

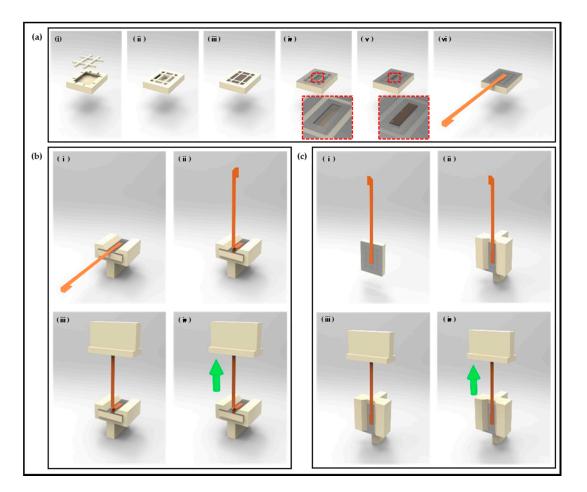

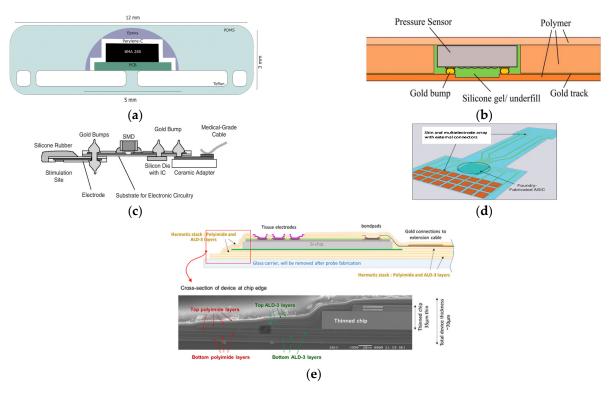

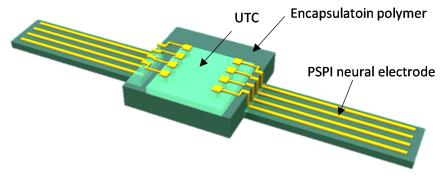

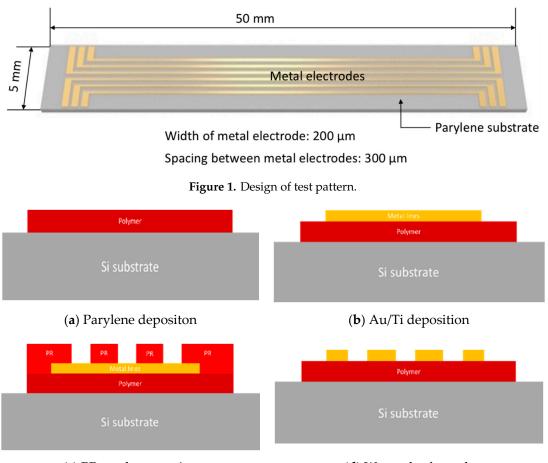

As shown in Figure 1, in this study, we introduce the biocompatible polymer-based packaging approach for chronic implantation with the results of mechanical property evaluations and acceleration experiments between two kinds of polymers (packages and neural interface materials). Finally, verification results of the lifetime of actually developed polymer-based packaging are discussed with the results of in vivo experiments.

**Figure 1.** Scheme of polymer-based packaging for neural interface system. (**a**) Front view and (**b**) bottom view show details of packaging inside, (**c**) overall view, and (**d**) backside view.

#### 2. Materials and Methods

#### 2.1. Design and Fabrication of Polymer-Based Neural Interface Packaging Prototype

The neural interface proposed in this study used SPAE (Spiral Probe Array Electrode) [25], a photosensitive polyimide-based neural electrode developed through previous studies; the neural interface system is constructed by connecting PCB integrated with pre-amplifier (RHS2116 Stim/Amplifier Chip, Intan Technologies, Los Angeles, CA, USA) and FPCB (Flexible Printed Circuit Board).

As shown in Figure 1, the proposed neural interface system was encapsulated using thermal epoxy (EPO-TEK<sup>®</sup> 302, Epoxy Technology, Billerica, MA, USA) from the neural electrode interface to the FPCB interface to connect the PCB substrate and the external system. During the process, square-shaped litmus paper (KA.22-93A, DOOSAN Scientific, Seoul, Korea) responsive to bodily fluids was added to the backside of the PCB in order to enable an intuitive visual leakage check. Thereafter, a thin parylene layer was deposited using commercial parylene deposition equipment (VPC-500, Paco Engineering, Incheon, Korea) to satisfy the biocompatibility of the outer surface of the packaging.

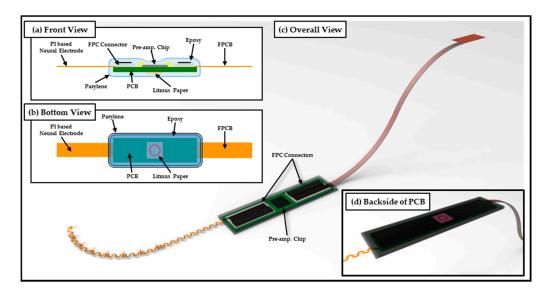

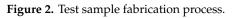

The detailed process of polymer-based packaging of the neural interface is shown in Figure 2a. The fabricated neural electrode and FPCB are individually connected with the PCB through FPC connectors (Molex 502078-3310 and Molex 502078-3760, Molex, Lisle, IL, USA), and the two FPC connectors are electrically connected to the pre-amplifier integrated on the PCB for each channel. In addition, a peeler gauge with a thickness of 50 µm was attached to the backside of the PCB for the convenience of visually checking leakage through litmus paper without any difficulty caused by the contrasting effect of red and green complementary colors (Figure 2a(i)). After integrating each component, encapsulation was performed using thermal epoxy in a state in which a rectangular parallelepiped PDMS (Polydimethylsiloxane, Dow Corning, Midland, MI, USA) structure, which is manufactured with a mixture ratio of 10:1 and a curing condition of  $65 \,^{\circ}\text{C}/1$  h and was attached to the back of a PCB (Figure 2a(ii)). The recommendation of the curing condition of thermal epoxy by the manufacturer was 2 h at room temperature. However, it is possible to improve the adhesion between the thermal epoxy and polyimide by adjusting the curing conditions. It should be noted that all thermal epoxy curing processes have been done at 65 °C for 2 h. (Related information can be found in the Results in Sections 3.2 and 3.3) PDMS has low mechanical strength and adhesion due to weak interactions between molecular chains and a lack of polar groups [26]. Various methods, such as phosphorus and boron synthesis, ultraviolet-ozone treatment, and an oxygen plasma treatment for improving adhesion, have been studied [27-29], but in this study, it is possible to easily remove the PDMS structure after curing the thermal epoxy due to the low adhesion of PDMS. Thereafter, square-shaped litmus paper with a circle pattern with an aqueous marker was attached at the corresponding position, and additional encapsulation was carried out using thermal epoxy (Figure 2a(iii,iv)). The entire thickness of the applied thermal epoxy was approximately 2 mm, and the electrode sites of the neural electrode and the metal electrode of the FPCB for electrical connection were covered with a stretchable polymer film (Parafilm, Bemis Company, Inc., Neenah, WI, USA), and a parylene layer of thickness of 5  $\mu$ m was deposited using a commercial parylene deposition instrument (Figure 2a(v)). After parylene deposition, the stretchable polymer film was removed and the mechanical rigidity was reinforced on FPCB using a heat-shrink tube to complete the manufacturing of the prototype as shown in Figure 2a(vi),b.

**Figure 2.** Packaging sample preparation. (**a**) Fabrication process of neural interface system with polymer-based packaging and (**b**) result of sample preparation.

#### 2.2. Electrophysiological Experiment Setups

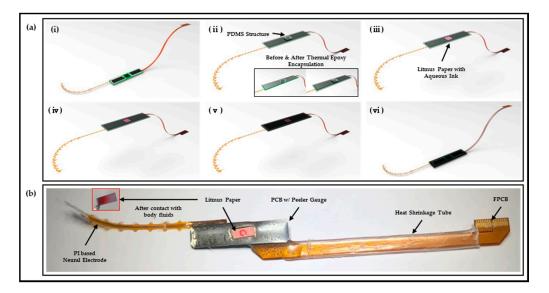

In vitro and in vivo experiments were conducted to verify whether there was a sufficiently applicable performance of the neural interface to which the polymer-based packaging was applied or not. In order to verify the signal acquisition performances of the neural interfaces to be used before the relevant experiment, the impedance at each frequency was measured using electrochemical impedance spectroscopy. The impedances of a total of two neural interfaces were measured, and each measurement result exhibited an average 29.08 kOhm and 32.63 kOhm at 1 kHz. This is a sufficient impedance value suitable for acquiring a neural signal, and the standard deviation of each average impedance was simultaneously analyzed to be 5.02 kOhm and 8.17 kOhm; thus, it was also verified that it had stability. In addition, the neural interface obtained from the measurement result of Figure 3a was used for in vitro experiment, and the neural interface with the impedance of Figure 3b was used for in vivo experiment, respectively. As shown in Figure 3c, the in vitro experiments were configured in a state in which the anode/cathode electrodes, which were connected to the electric pulse generator (HSE-HA stimulator CS for isolated cells, Hugo Sachs Elektronik Harvard Apparatus GmbH, Baden-Württemberg, Germany), and the neural interface and reference electrode, which were connected to the neural signal acquisition equipment (RHS stim/recording system, Intan Technologies, Los Angeles, CA, USA), were immersed in a PBS solution. This experiment was a process to verify the performance and capability of the neural interface that acquired the artificial signal generated through an electric pulse generator, and the stimulation parameter was constructed based on the criteria of the general neural stimulation parameter [30–32]. As shown in Figure 3d, the stimulus parameters were composed of two types (50  $\mu$ A-100  $\mu$ s-10 Hz and 200 µA-100 µs-100 Hz). In addition, the corresponding stimulation signal generated by the electrical pulse generator was acquired and recorded in real time from a total of 32 channel electrodes using a neural signal acquisition device.

**Figure 3.** The results of impedance measurements of (**a**) neural electrode for in vitro experiment and (**b**) neural electrode for in vivo experiment. Electrophysiological experiment setup and stimulation parameters. (**c**) In vitro experiment setup in PBS, (**d**) a couple of stimulation parameters, (**e**) in vivo experiment setup with New Zealand white rabbit, and (**f**) in vivo stimulation parameters.

#### 2.3. In Vivo Experiment Setups

In addition to verification through the in vitro experiment, the in vivo experiments using the New Zealand male white rabbit was configured as shown in Figure 3e. The stimulation probe was connected to the electric pulse generator to apply stimulation, and the neural electrode applied to the neural interface was implanted into the sciatic nerve of the rabbit for signal acquisition. Implantation of the neural electrode was performed using a surgical method established using rats in previous study [25], and a 12-week-old New Zealand male white rabbit was anesthetized through laparoscopic injection of a Zoletil (Virbac, Carros, France)–Rompun (BAYER, Leverkusen, Germany) with composition ratio of 3:1. After anesthetizing, the neural electrode was inserted into the sciatic nerve, which

was exposed through a muscle incision. The verification experiment was conducted under breathing anesthesia, and the stimulation signal interval was set to 1000 ms so that the movement of the leg of the rabbit by the sciatic nerve stimulation could be visually classified. Figure 3e,f show the configuration and results of the in vivo experiment, for which a system capable of acquiring and recording stimulation signals in real time using neural signal acquisition equipment was constructed. All procedures for animal testing were performed through the Institutional Animal Care and Use Committee (IACUC) guidelines of the Korea Institute of Science and Technology (KIST).

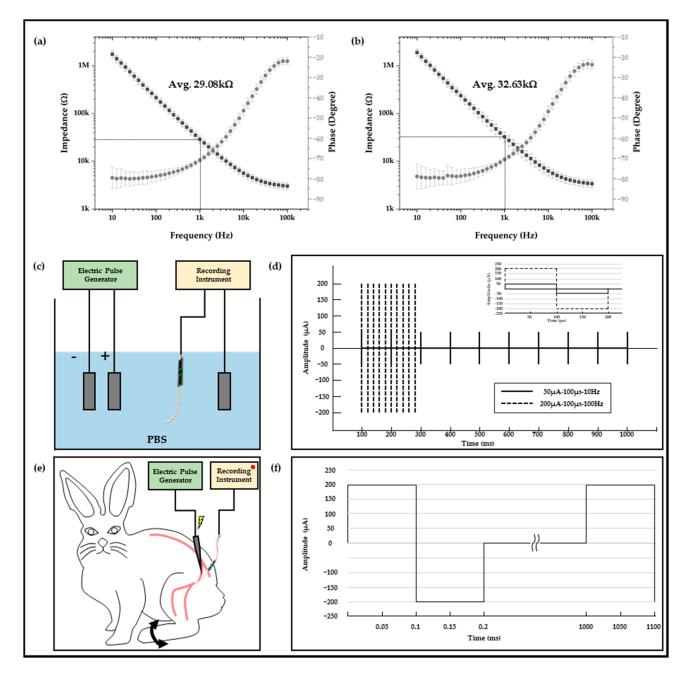

#### 2.4. Test Sample Preparation for Polyimide (FPCB)-Epoxy Peel-Off Test

The polymer-based packaging for neural interface in this study was mainly configured using thermal epoxy encapsulation. After thermal epoxy encapsulation, thin parylene film, which is widely used as a coating material to prevent immune reactions and achieve biocompatibility, was deposited. [33–35] In this configuration, thermal epoxy was applied as a major material for polymer-based packaging, and the adhesion between thermal epoxy and the material forming the neural interface is directly related to the packaging's life and performance. Because the interface is bound to form between thermal epoxy and polyimide, which is the main component of the FPCB applied for electrical connection with the neural interface and external system, this interface in packaging is the most vulnerable site. Accordingly, samples for experiments were manufactured in the order shown in Figure 4 to verify the adhesion between the thermal epoxy and polyimide depending on the curing conditions of the thermal epoxy. The experiment was constructed in a form that could apply tear force and shear force by attaching a specific area of thermal epoxy and FPCB. First, a sample with a specific area of thermal epoxy and FPCB was manufactured as shown in Figure 4a. A structure capable of containing a certain amount of thermal epoxy and a #-shaped structure for preventing the separation of the thermal epoxy from the sample structure during the adhesion measurement experiment were printed by using a commercial 3D printer (CUBICON Single Plus-320C, Cubicon, Seongnam, Korea) and were manually assembled (Figure 4a(i,ii)). Thereafter, thermal epoxy was poured into the structure and cured at room temperature for 2 h as per recommended curing condition of the manufacturer (Figure 4a(iv)), and the thermal epoxy surface was covered except for a pre-determined area with a commercial detachable tape (Scotch<sup>®</sup> Magic<sup>™</sup> tape, 3M, Saint Paul, MN, USA; Figure 4a(v)). The exposed surface area of the thermal epoxy is established by 1 mm offset from the outer line of the FPCB to the inside. This offset was set to prevent the applied thermal epoxy from being attached to the outer line or edge of the FPCB and acting as an obstacle to adhesion measurement of the interface. To specify a volume of the second thermal epoxy through the thickness (about 60  $\mu$ m) of commercial detachable tape, the identical thermal epoxy was spread to the exposed surface and the squeezing method was carried out in stencil printing using a peeler gauge with a thickness of  $100 \,\mu m$ (Figure 4a(v)) [36]. In the final step shown in Figure 4a(v), the second thermal epoxy curing was performed with an FPCB placed thereon and a weight of 3 kg placed on top for conformal attachment. Though different products from the thermal epoxy were used in this research, the curing condition was established based on research results that when the thermal epoxy, for which studies recommend a room-temperature curing condition, is cured at a higher temperature, its curing rigidity can be increased [37]. The thermal epoxy of the sample applied in the experiment was cured at  $45 \text{ }^{\circ}\text{C}/2\text{h}$  and  $65 \text{ }^{\circ}\text{C}/2\text{ h}$ , respectively, which were higher than room temperature.

**Figure 4.** Procedures of adhesion evaluation test sample preparation. (**a**) Process of sample preparation with uniform adhered area between epoxy and FPBC; (**a-i-a-ii**) preparation and assembly of 3D-printed sample holder; (**a-iii**) filling and curing epoxy into vacancy of sample holder; (**a-iv**) covering epoxy surface with detachable tape excluding uniform area; (**a-v**) additional epoxy filling and squeezing epoxy into uncovered area; and (**a-vi**) applying FPCB to uncured epoxy and curing. (**b**) Tear-test procedures. (**c**) Shear-test procedures.

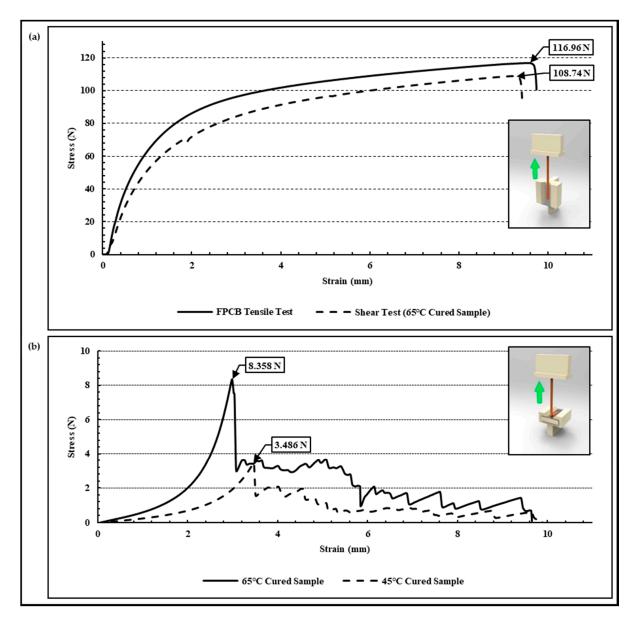

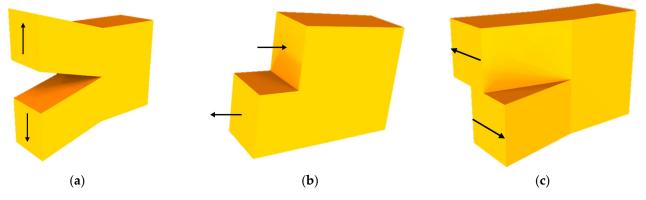

#### 2.5. Peel-Off Test Setup for Polyimide (FPCB) Epoxy

Additional structures capable of applying tear force and shear force for the measurement of adhesion between thermal epoxy and polyimide were configured as shown in Figure 4b,c. A structure for fixing the FPCB thermal epoxy-attached sample to the chuck of the tensile experimental equipment and a structure that can be grasped the end of the FPCB by another chuck of the tensile experimental equipment were output using a 3D printer. The structure for fixing the FPCB thermal epoxy-attached sample was configured to have a difference of 90 degree angle to enable tear force and shear force applications, respectively. In the experiment for evaluating the adhesion between thermal epoxy and polyimide (FPCB) using the prepared sample, commercial tensile experimental equipment (Shimadzu EZ-S machine, Shimadzu, Kyoto, Japan) was used and tensile stroke was applied to one end of the FPCB under conditions of 1 mm/min; the generated force was measured in mN units.

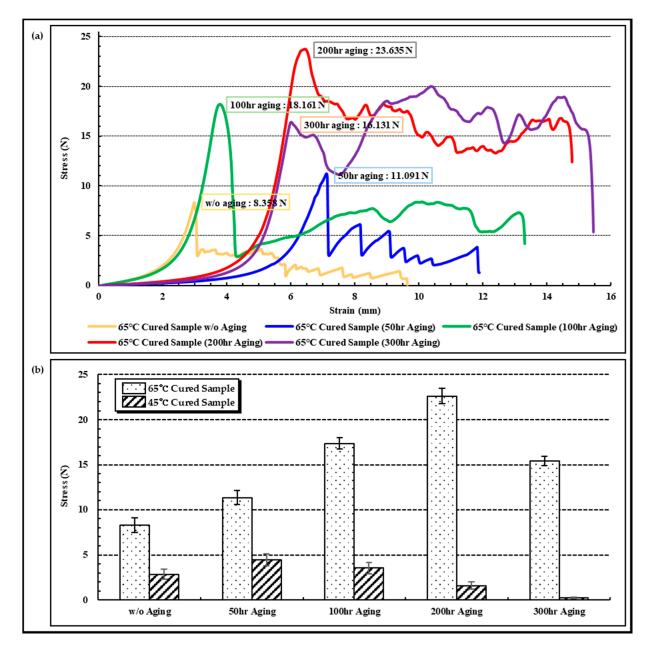

#### 2.6. Acceleration Test Setup

The reliabilities of acceleration experiments using temperature applications higher than the used temperature are generally derived using the Arrhenius equation as shown below in Equation (1).

$$A_T = \frac{\lambda_{T1}}{\lambda_{T2}} = \exp\left[\left(\frac{-E_a}{k}\right)\left(\frac{1}{T_1} - \frac{1}{T_2}\right)\right] \tag{1}$$

where  $E_a$  is the activation energy (eV), k is Boltzmann's constant as  $8.62 \times 10^{-5}$  eV/K,  $T_1$  is the absolute temperature of application condition,  $T_2$  is the absolute temperature of experiment condition,  $\lambda_{T1}$  is the observed failure rate at application condition, and  $\lambda_{T2}$  is the observed failure rate at experiment condition. Although the life of polymerbased packaging according to the acceleration experiment can be predicted based on the Arrhenius equation, an acceleration experiment was constructed on the basis that about 100 days of lifetime verification with 300 h of aging can be performed on an environment 30 °C higher than the usage temperature based on Donaldson's report [38]. Three samples (a total of 24 samples, 12 45 °C cured samples and 12 65 °C cured samples) were each taken out at 50, 100, 200, and 300 h of aging while immersed in a 65 °C PBS solution, and then tear force was applied to evaluate the changes in interfacial adhesion between the thermal epoxy and FPCB.

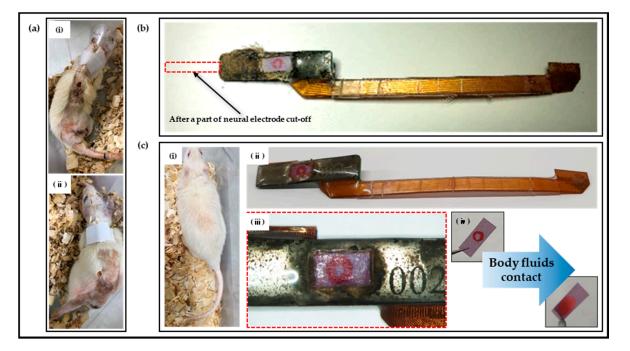

#### 2.7. In Vivo Chronic Implantation

To verify the practical applicability of fabricated neural interfaces to which polymerbased packaging was applied, in vivo experiments were constructed. Neural electrodes were inserted into rats' sciatic nerves, and sites, including PCB and FPCB, were placed in the rats' hind leg muscles and subcutaneously. Insertion surgeries were performed on a total of two individual rats, and the electrodes were extracted at the times of 8 months and 18 months after implantation to check for changes in the conditions of the overall polymer-based packaging, especially applied litmus papers. At the time of extractions, it was difficult to separate the neural electrodes from the sciatic nerves, so the neural electrodes were cut and extracted.

#### 3. Results

#### 3.1. In Vitro and In Vivo Characterizations of Polymer-Based Neural Interface Packaging Prototype

In the PBS solution-based in vitro experiment, two artificial stimulation signals  $(50 \ \mu\text{A}-100 \ \mu\text{s}-10 \ \text{Hz}$  and  $200 \ \mu\text{A}-100 \ \mu\text{s}-100 \ \text{Hz})$  were applied, and the results acquired using 32 electrode channels formed in the neural electrode and commercial neural signal acquisition equipment are shown in Figure 5a. For each artificial stimulation signal, it can be evaluated that signals similar to stimulation signals were acquired from all 32 channels. Similarly, for in the in vivo experiment using a New Zealand male white rabbit, it was confirmed that stimulation signals of 200 µA-100 µs-1 Hz could be obtained from all 32 channels (Figure 5a). In addition, the relevant procedures and results of the in vivo experiment can be confirmed through Video S1, and the contraction of the leg muscles of the rabbit with a certain cycle by a stimulation signal can be clearly verified. Through in vitro and in vivo experiments, it was confirmed that the neural interface to which the polymer-based packaging was applied operated as an initial purpose. In addition, a quantitative analysis of the signals acquired through the experiments was carried out, and the results are summarized in Table 1. The maximum, minimum, average, and standard deviation values were derived from the positive and negative regions of the acquisition signals for a total of three stimulation conditions. Also, the average and standard deviation values of the entire signal amplitude were also calculated. The difference between the maximum and minimum values in each region was up to 342.0  $\mu$ V under 200  $\mu$ A-100  $\mu$ s-10 Hz stimulation conditions, but the standard deviation of the region was  $89.7 \ \mu$ V. Even under other stimulation conditions, the standard deviation in the positive and negative regions was from a minimum of 26.5  $\mu$ V to a maximum of 90.8  $\mu$ V. In a process of acquiring a signal using a neural electrode, the deviation may sufficiently occur depending on system parameters, such as electrode impedance, cross-talk between electrodes, and unknown recording conditions, and the result of impedance measurement research is reported to be different over time in the same system configuration [39]. In comparison, although the maximum/minimum value of the total acquisition signal differs, it cannot be determined that the non-uniform signal was obtained on a single electrode itself because the average and standard deviation of the total signal size specified in Table 1 are not abnormally large. Accordingly, it is determined that every acquired signal amplitude is a result of different distances from the stimulation signal-generation position, the difference in impedance for each electrode, and the cross-talk between electrodes. As a result, it can be evaluated that a sufficient neural signal acquisition performance and post-processing, such as clustering for acquired neural signal analyses, have sufficiently possible signal levels.

| (a) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

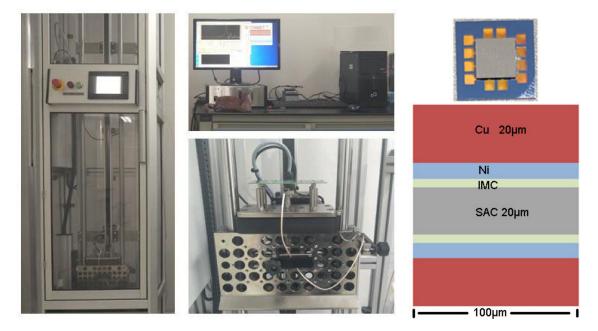

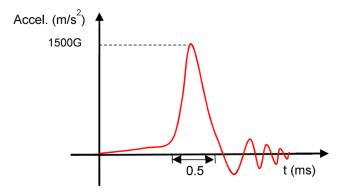

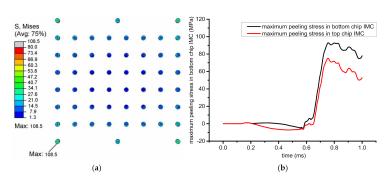

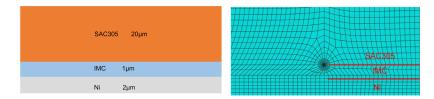

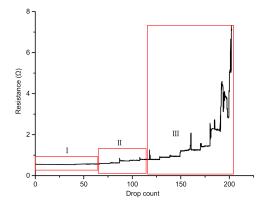

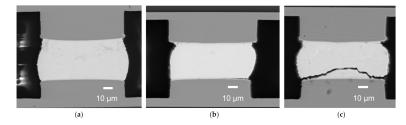

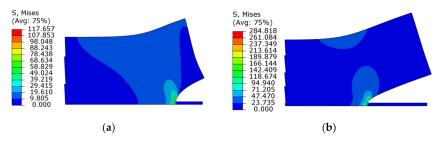

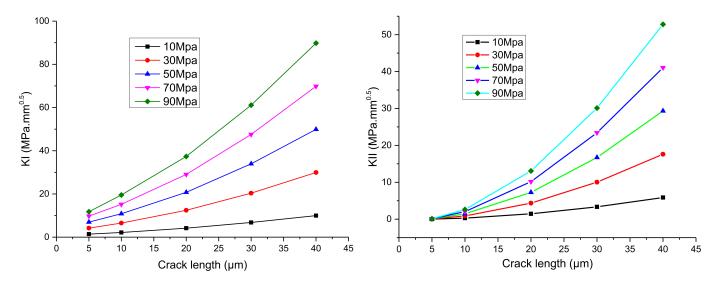

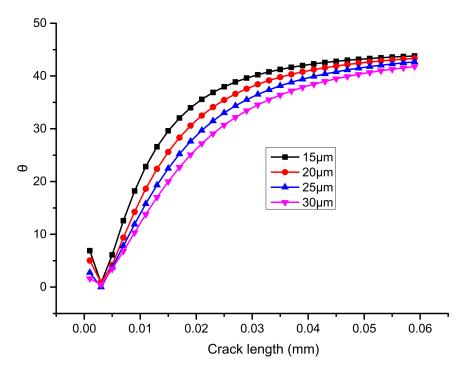

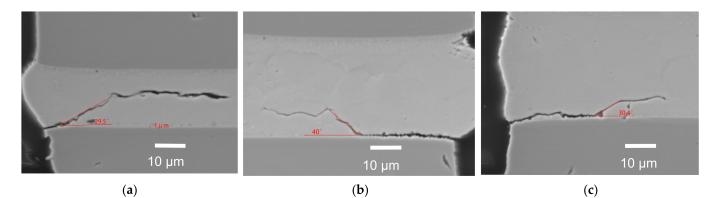

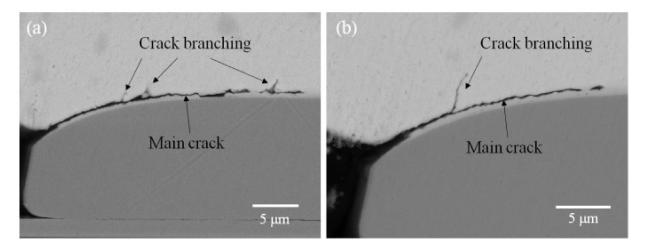

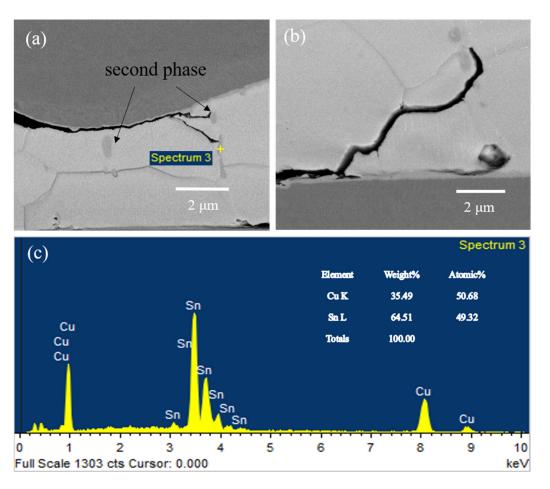

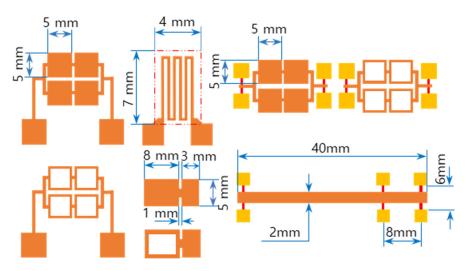

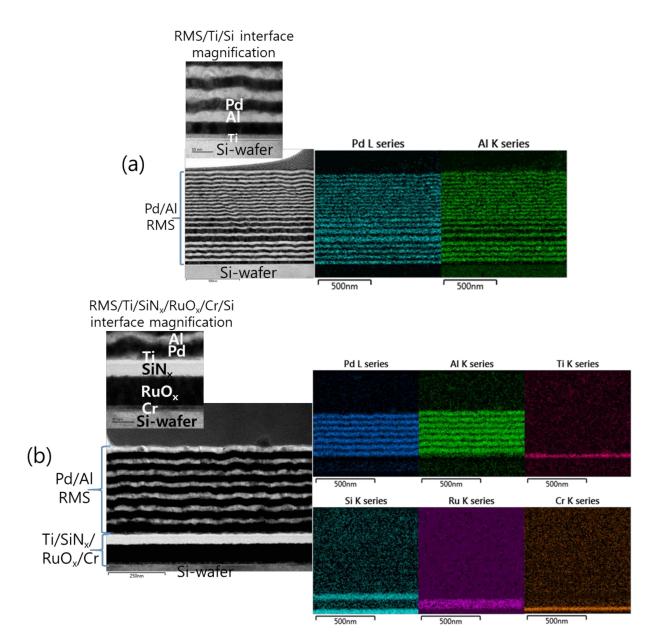

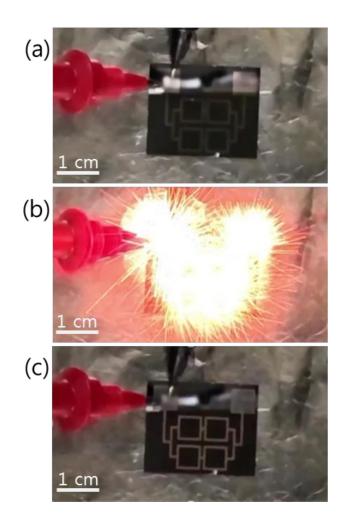

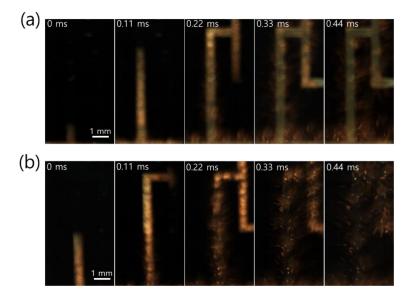

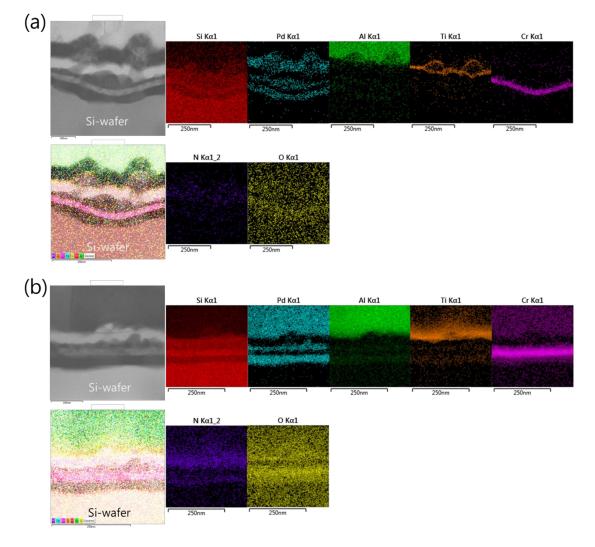

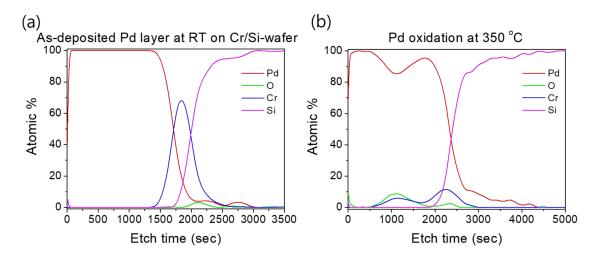

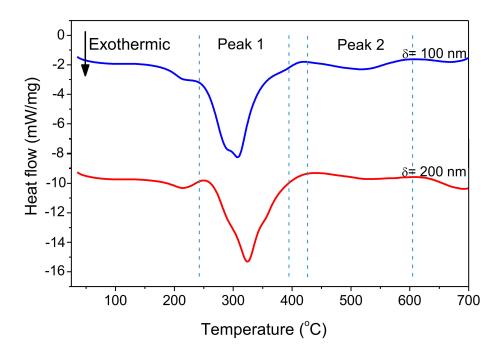

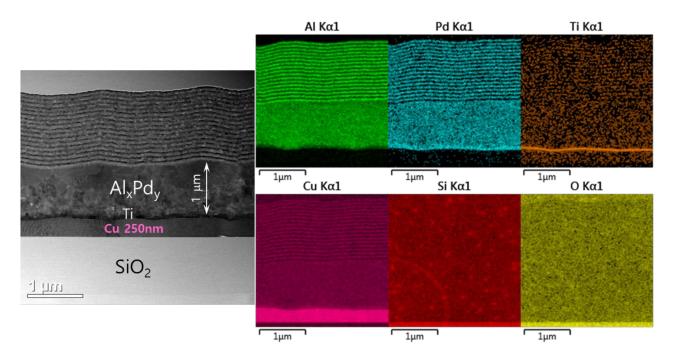

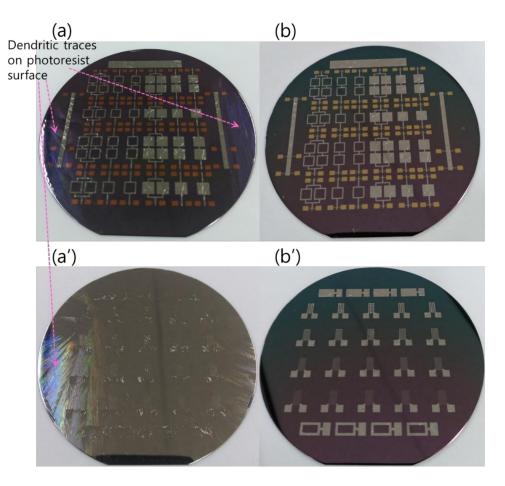

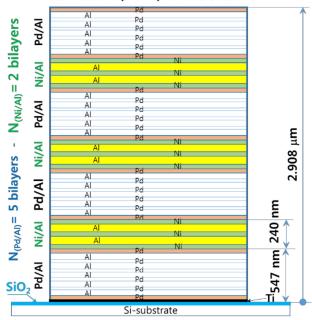

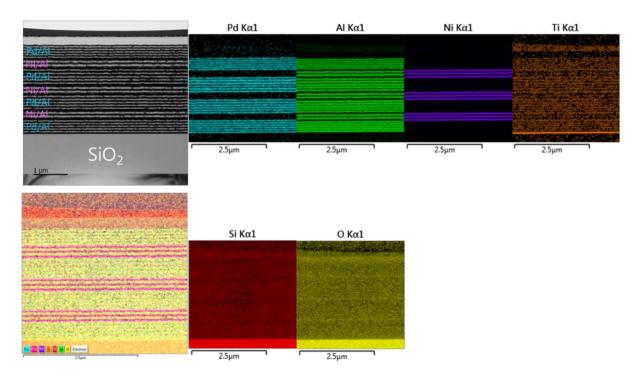

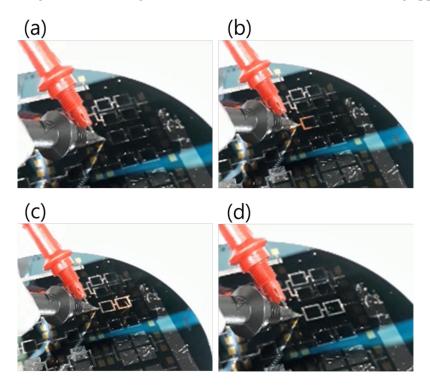

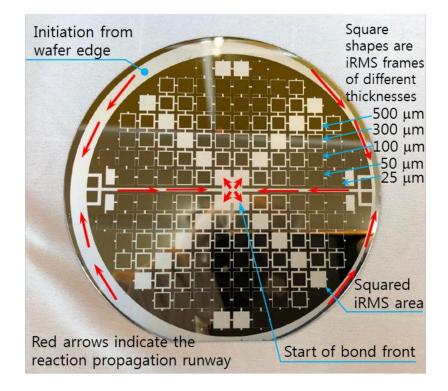

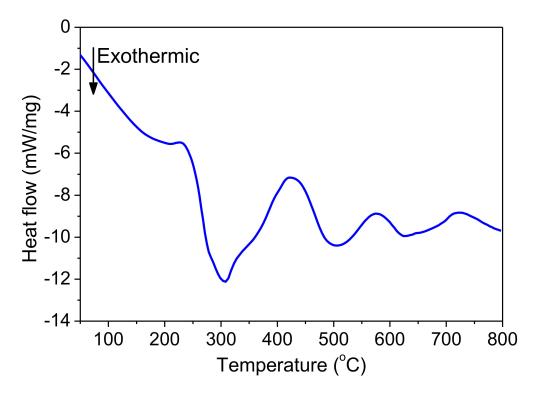

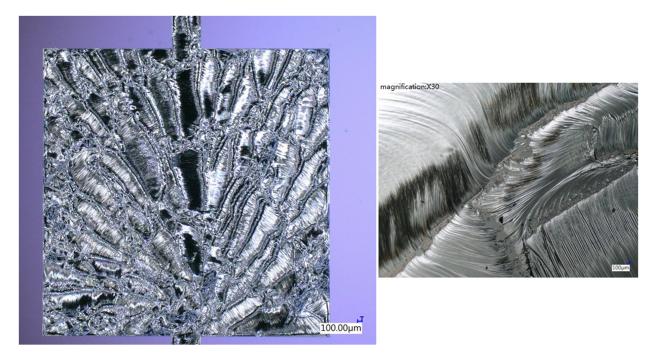

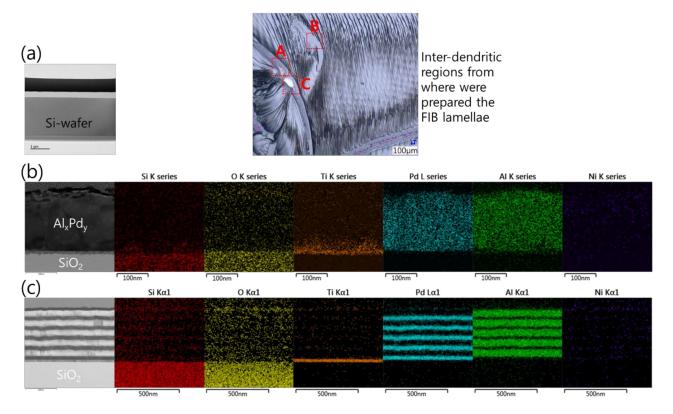

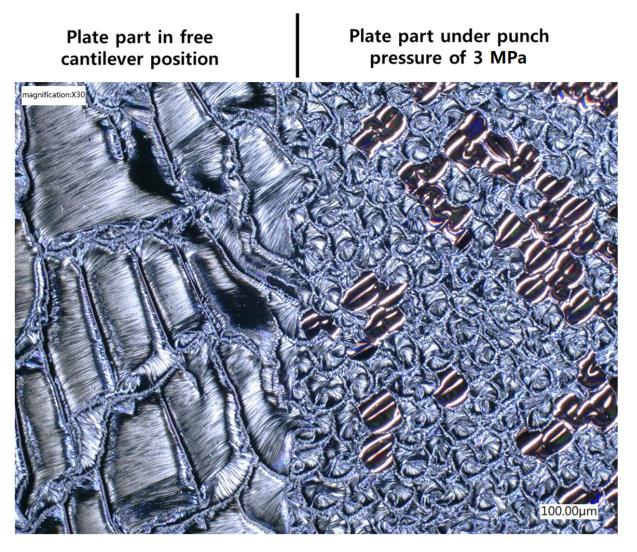

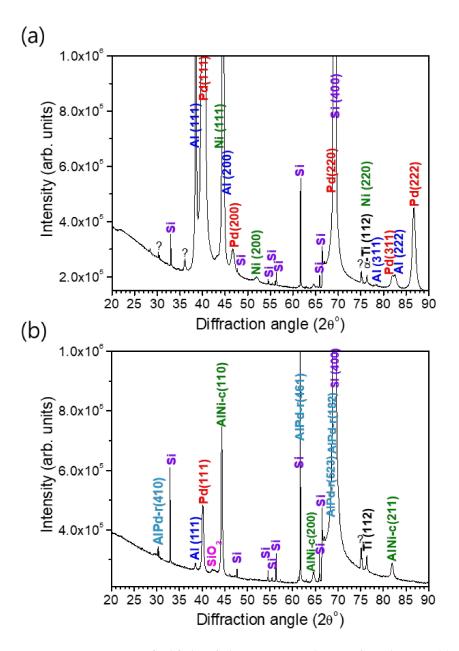

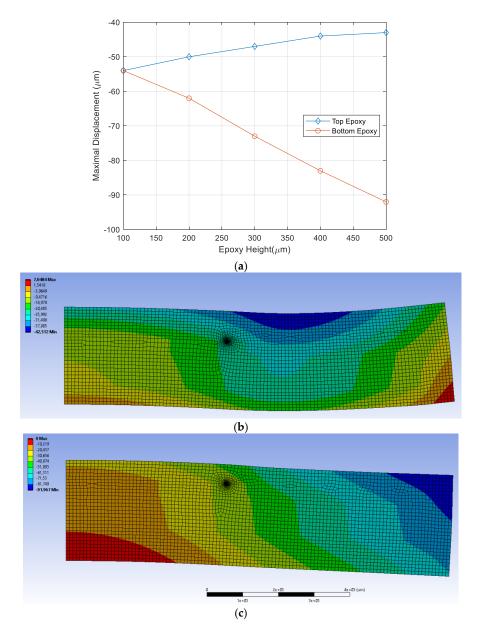

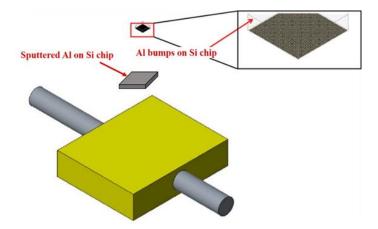

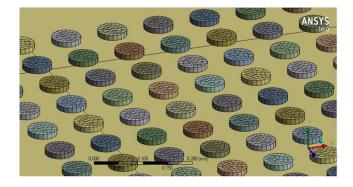

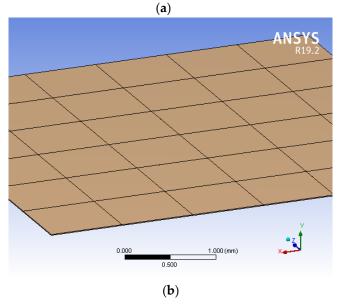

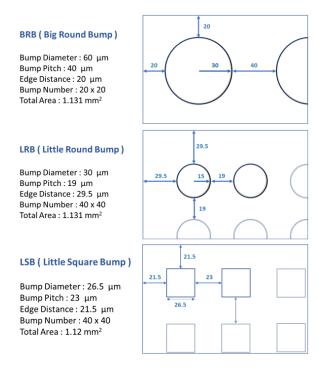

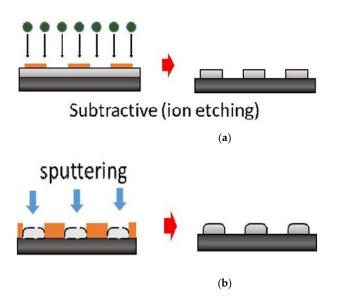

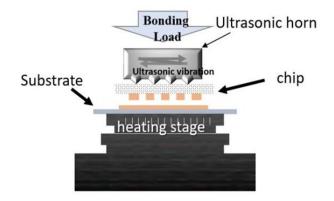

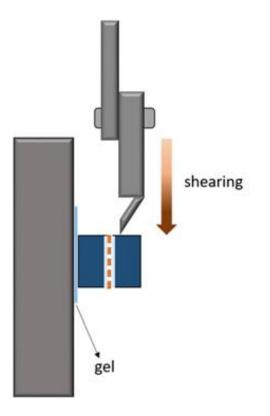

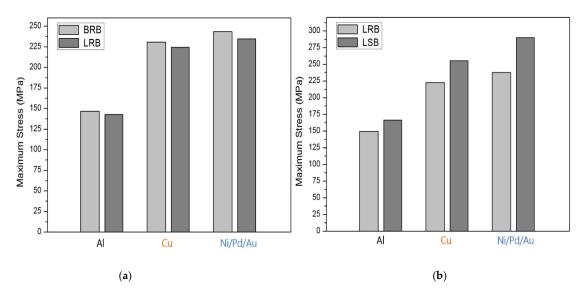

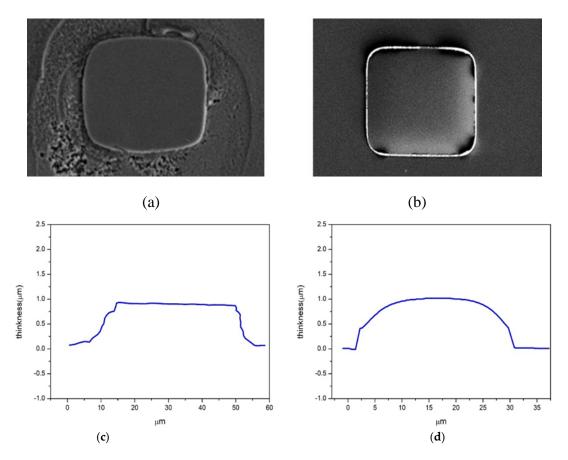

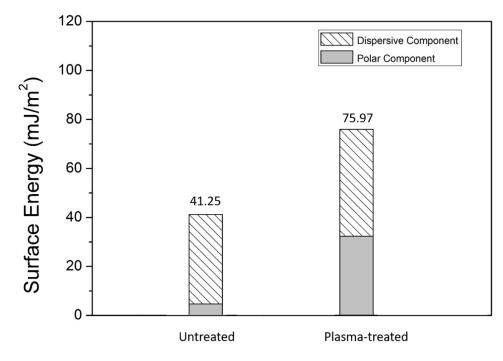

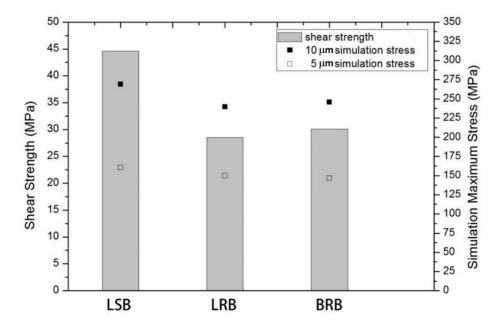

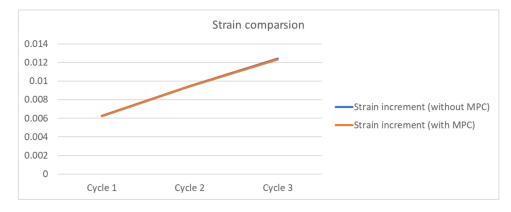

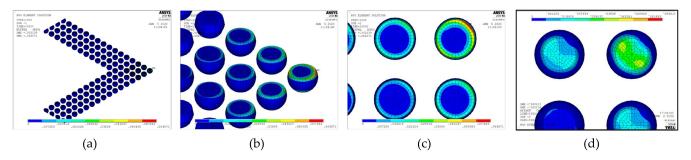

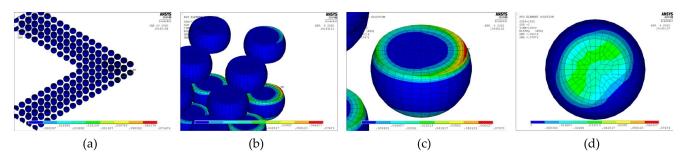

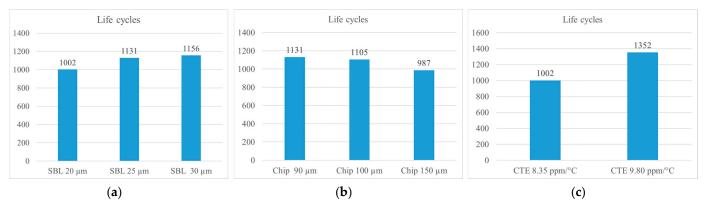

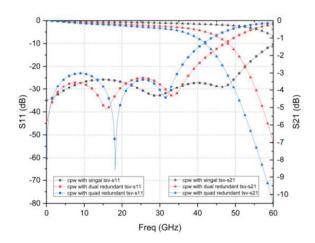

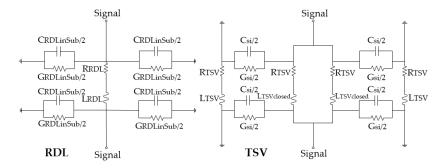

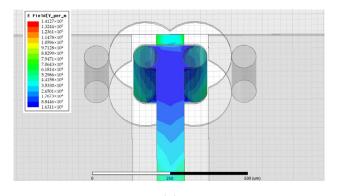

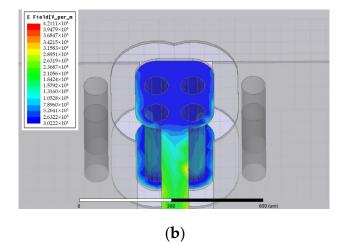

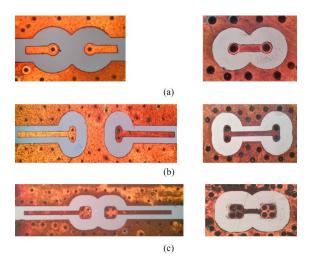

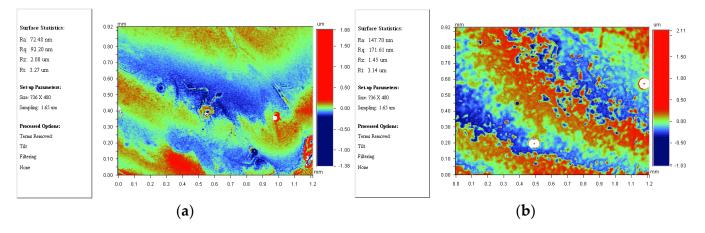

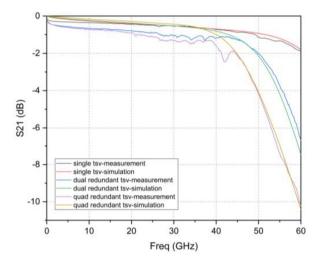

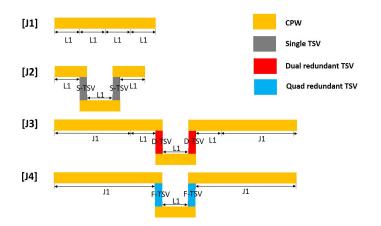

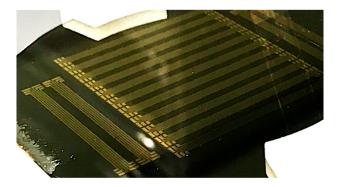

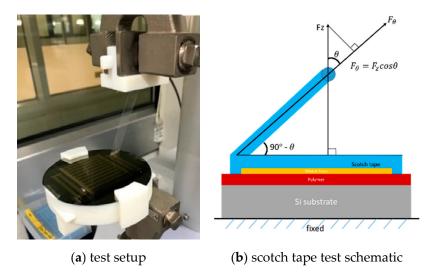

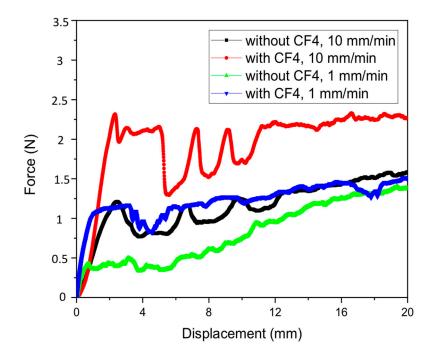

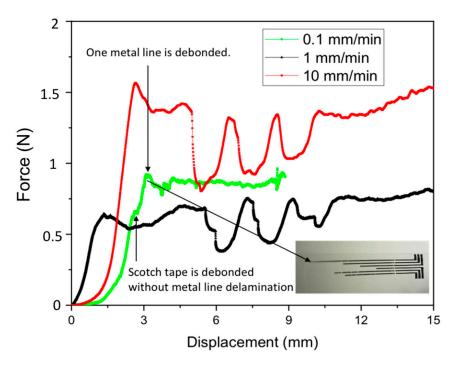

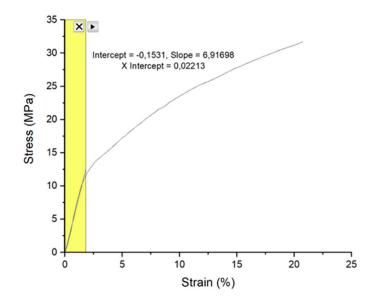

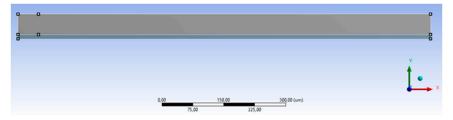

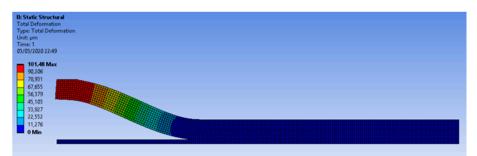

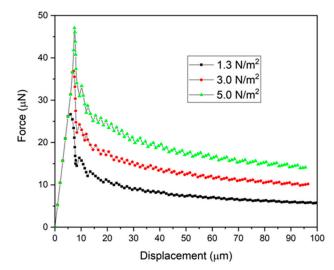

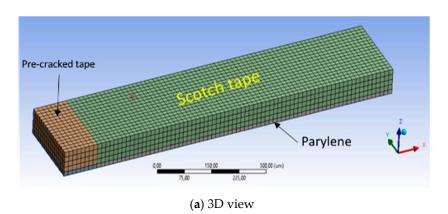

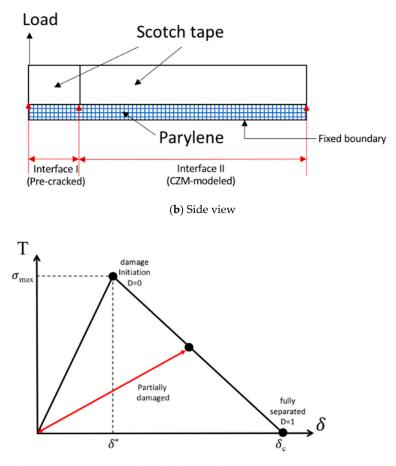

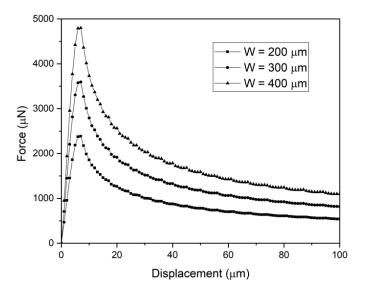

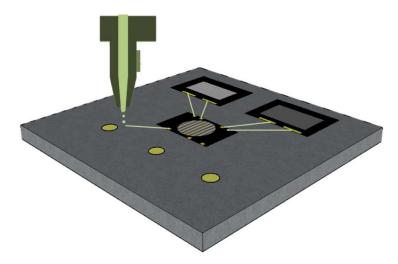

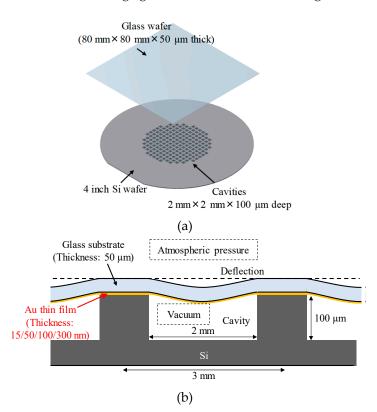

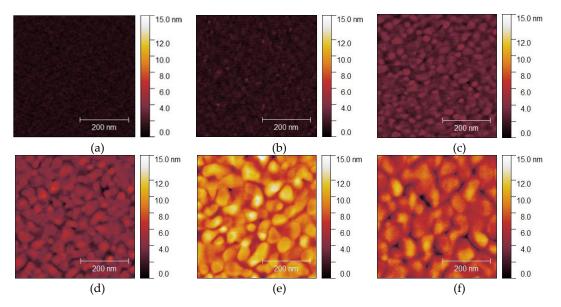

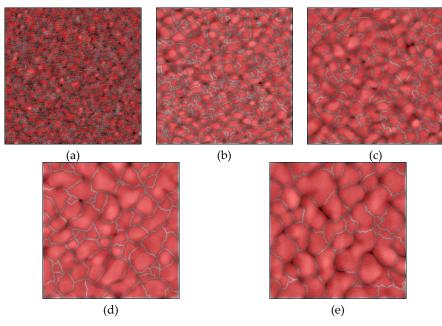

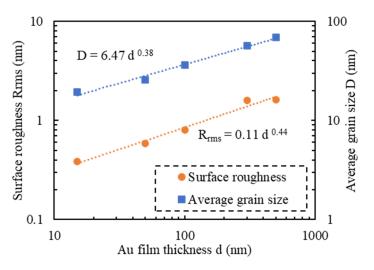

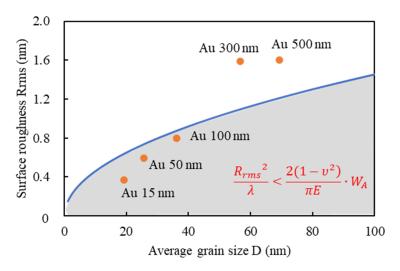

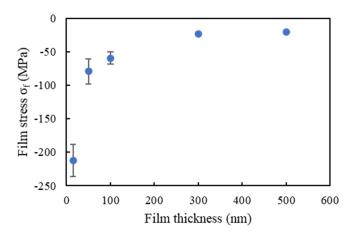

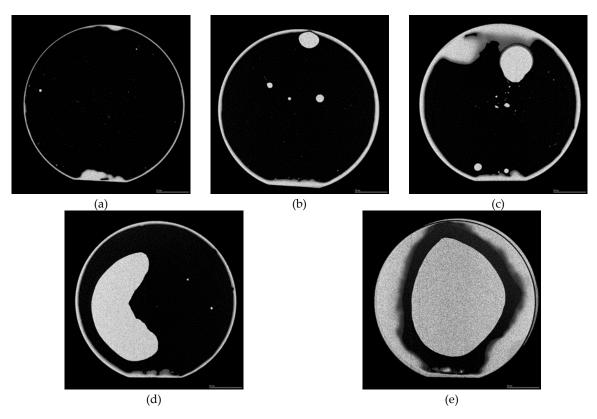

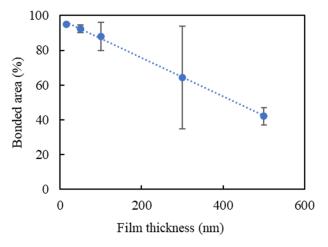

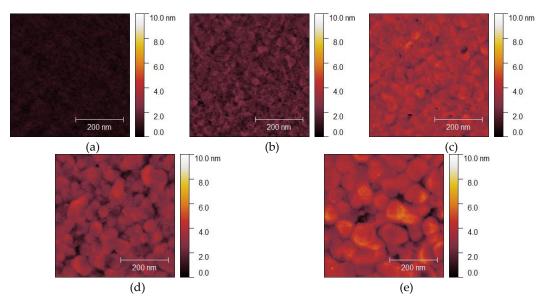

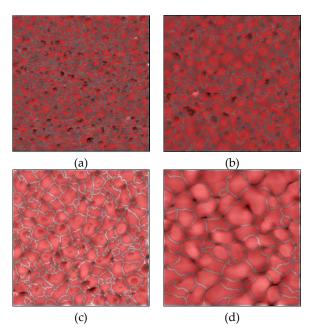

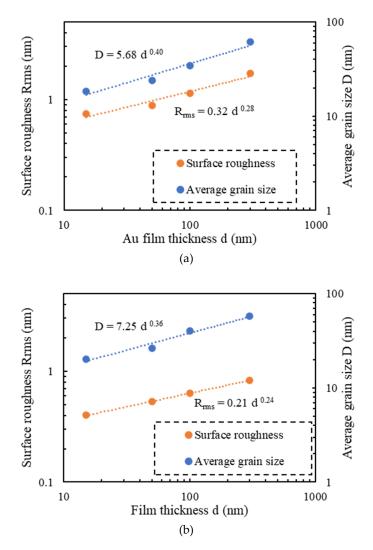

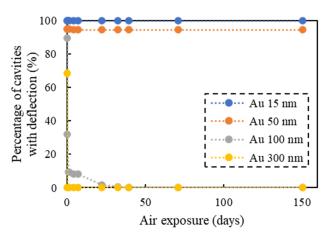

|     | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |