# Miniaturized Transistors, Volume II

Edited by

Lado Filipovic and Tibor Grasser

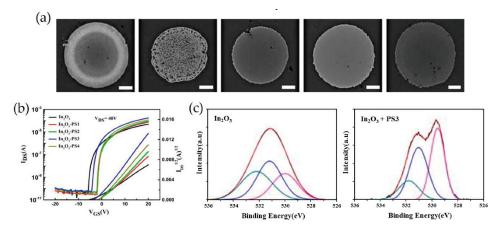

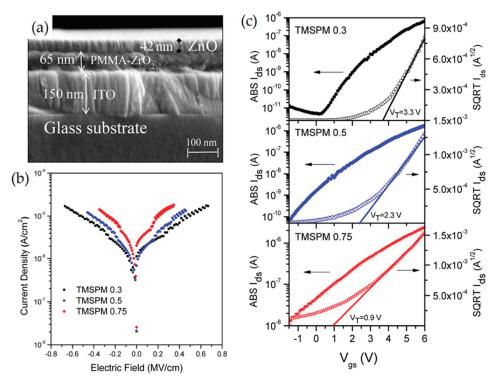

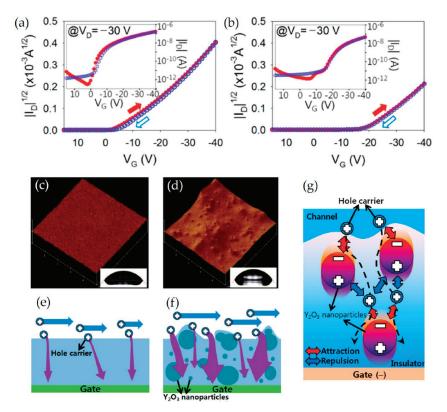

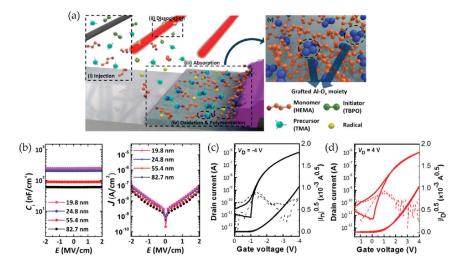

Printed Edition of the Special Issue Published in Micromachines

# Miniaturized Transistors, Volume II

# Miniaturized Transistors, Volume II

**Editors**

Lado Filipovic Tibor Grasser

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

Editors

Lado Filipovic Tibor Grasser

TU Wien TU Wien

Austria Austria

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Micromachines* (ISSN 2072-666X) (available at: https://www.mdpi.com/journal/micromachines/special\_issues/Miniaturized\_Transistors\_Volume\_II).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-4169-3 (Hbk) ISBN 978-3-0365-4170-9 (PDF)

© 2022 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## **Contents**

| About the Editors vii                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lado Filipovic and Tibor Grasser         Special Issue on Miniaturized Transistors, Volume II         Reprinted from: Micromachines 2022, 13, 603, doi:10.3390/mi13040603       1                                                                                                                                                                                            |

| Henry H. Radamson, Xiaobin He, Qingzhu Zhang, Jinbiao Liu, Hushan Cui, Jinjuan Xiang,<br>Zhenzhen Kong, Wenjuan Xiong, Junjie Li, Jianfeng Gao, Hong Yang, Shihai Gu,<br>Xuewei Zhao, Yong Du, Jiahan Yu and Guilei Wang<br>Miniaturization of CMOS                                                                                                                          |

| Reprinted from: <i>Micromachines</i> <b>2019</b> , <i>10</i> , 293, doi:10.3390/mi10050293                                                                                                                                                                                                                                                                                   |

| Jae Won Jeong, Hye Suk Hwang, Dalsu Choi, Byung Chol Ma, Jaehan Jung and Mincheol Chang                                                                                                                                                                                                                                                                                      |

| Hybrid Polymer/Metal Oxide Thin Films for High Performance, Flexible Transistors Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 264, doi:10.3390/mi11030264                                                                                                                                                                                                  |

| Michael Waltl Reliability of Miniaturized Transistors from the Perspective of Single-Defects Reprinted from: Micromachines 2020, 11, 736, doi:10.3390/mi11080736                                                                                                                                                                                                             |

| Bernhard Stampfer, Franz Schanovsky, Tibor Grasser and Michael Waltl Semi-Automated Extraction of the Distribution of Single Defects for nMOS Transistors Reprinted from: Micromachines 2020, 11, 446, doi:10.3390/mi11040446                                                                                                                                                |

| Kin P. Cheung, Chen Wang and Jason P. Campbell Nanoscale MOSFET as a Potential Room-Temperature Quantum Current Source Reprinted from: Micromachines 2020, 11, 364, doi:10.3390/mi11040364                                                                                                                                                                                   |

| Ulrich Wulf  A One-Dimensional Effective Model for Nanotransistors in Landauer–Büttiker Formalism  Reprinted from: Micromachines 2020, 11, 359, doi:10.3390/mi11040359                                                                                                                                                                                                       |

| Cristina Medina-Bailon, Hamilton Carrillo-Nuñez, Jaehyun Lee, Carlos Sampedro, José Luis Padilla, Luca Donetti, Vihar Georgiev, Francisco Gamiz and Asen Asenov Quantum Enhancement of a S/D Tunneling Model in a 2D MS-EMC Nanodevice Simulator: NEGF Comparison and Impact of Effective Mass Variation Reprinted from: Micromachines 2020, 11, 204, doi:10.3390/mi11020204 |

| Hyeonjeong Kim, Songyi Yoo, In-Man Kang, Seongjae Cho, Wookyung Sun and Hyungsoon Shin Analysis of the Sensing Margin of Silicon and Poly-Si 1T-DRAM Reprinted from: Micromachines 2020, 11, 228, doi:10.3390/mi11020228                                                                                                                                                     |

| Yannan Zhang, Ke Han and Jiawei Li A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator Reprinted from: <i>Micromachines</i> 2020, 11, 223, doi:10.3390/mi11020223                                                                                                                                                                              |

| Ke Han, Shanglin Long, Zhongliang Deng, Yannan Zhang and Jiawei Li  A Novel Germanium-Around-Source Gate-All-Around Tunnelling Field-Effect Transistor for Low-Power Applications Reprinted from: <i>Micromachines</i> 2020, 11, 164, doi:10.3390/mi11020164                                                                                                                 |

| T-Channel Field Effect Transistor with Three Input Terminals (Ti-TcFET)  Reprinted from: Micromachines 2020, 11, 64, doi:10.3390/mi11010064                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feng-Tso Chien, Zhi-Zhe Wang, Cheng-Li Lin, Tsung-Kuei Kang, Chii-Wen Chen and Hsien-Chin Chiu 150–200 V Split-Gate Trench Power MOSFETs with Multiple Epitaxial Layers Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 504, doi:10.3390/mi11050504 |

| Hujun Jia, Yuan Liang, Tao Li, Yibo Tong, Shunwei Zhu, Xingyu Wang, Tonghui Zeng and Yintang Yang Improved DRUS 4H-SiC MESFET with High Power Added Efficiency Reprinted from: <i>Micromachines</i> <b>2020</b> , <i>11</i> , 35, doi:10.3390/mi11010035           |

| Huan Li, Jue Wang, Na Ren, Hongyi Xu and Kuang Sheng Investigation of 1200 V SiC MOSFETs' Surge Reliability Reprinted from: <i>Micromachines</i> <b>2019</b> , <i>10</i> , 485, doi:10.3390/mi10070485                                                             |

| Hui Li, Renze Yu, Yi Zhong, Ran Yao, Xinglin Liao and Xianping Chen Design of 400 V Miniature DC Solid State Circuit Breaker with SiC MOSFET Reprinted from: <i>Micromachines</i> <b>2019</b> , <i>10</i> , 314, doi:10.3390/mi10050314                            |

| Huaixin Guo, Tangsheng Chen and Shang Shi Transient Simulation for the Thermal Design Optimization of Pulse Operated AlGaN/GaN HEMTs Reprinted from: <i>Micromachines</i> 2020, 11, 76, doi:10.3390/mi11010076                                                     |

| Shunwei Zhu, Hujun Jia, Xingyu Wang, Yuan Liang, Yibo Tong, Tao Li and Yintang Yang Improved MRD 4H-SiC MESFET with High Power Added Efficiency Reprinted from: <i>Micromachines</i> <b>2019</b> , <i>10</i> , 479, doi:10.3390/mi10070479                         |

| Shunwei Zhu, Hujun Jia, Tao Li, Yibo Tong, Yuan Liang, Xingyu Wang, Tonghui Zeng and Yintang Yang Novel High-Energy-Efficiency AlGaN/GaN HEMT with High Gate and Multi-Recessed Buffer Reprinted from: <i>Micromachines</i> 2019, 10, 444, doi:10.3390/mi10070444  |

| Wen-Teng Chang, Hsu-Jung Hsu and Po-Heng Pao Vertical Field Emission Air-Channel Diodes and Transistors Reprinted from: Micromachines 2019, 10, 858, doi:10.3390/mi10120858 293                                                                                    |

| Cheng Mao, Cheng Yang, Haowen Ma, Feng Yan and Limin Zhang A Smart Floating Gate Transistor with Two Control Gates for Active Noise Control Reprinted from: Micromachines 2019, 10, 722, doi:10.3390/mi10110722                                                    |

| Wenhao Zhi, Qingxiao Quan, Pingping Yu and Yanfeng Jiang A 45 nm CMOS Avalanche Photodiode with 8.4-GHz Bandwidth Reprinted from: <i>Micromachines</i> 2020, 11, 65, doi:10.3390/mi11010065                                                                        |

| Joseph McGhee and Vihar P. Georgiev Simulation Study of Surface Transfer Doping of Hydrogenated Diamond by $MoO_3$ and $V_2O_5$ Metal Oxides                                                                                                                       |

| Reprinted from: Micromachines 2020, 11, 433, doi:10.3390/mi11040433                                                                                                                                                                                                |

### **About the Editors**

#### Lado Filipovic

Lado Filipovic (Dr.) is an Assistant Professor (tenure-track) of Modeling and Simulation of Integrated Semiconductor Sensors at TU Wien. He obtained his venia docendi (habilitation) in Semiconductor Based Integrated Sensors and his doctoral degree (Dr.techn.) in Microelectronics from TU Wien in 2020 and 2012, respectively. He holds a Master's degree in Applied Sciences (MASc.) from Carleton University in Ottawa, Canada, which he obtained in 2009. He is a Senior Member of the IEEE and is an active member of the Technical Program Committee for outstanding IEEE sponsored conferences, such as IEEE Sensors, SISPAD, and IIRW. He has been a Principal Investigator in various research projects funded by, e.g., the EU FP7 and Horizon 2020 programs and the Austrian Research Promotion Agency (FFG). His primary research interest is studying the operation, stability, and reliability of novel semiconductor-based sensors using advanced process and device TCAD approaches. One of his research pillars is combining physical and empirical modeling approaches, specifically in the TCAD process. With his team, he is actively investigating metal oxide semiconductors and two-dimensional materials, e.g., graphene, MoS2, and phosphorene for the detection of environmental pollutants and biomarkers from exhaled breath.

#### **Tibor Grasser**

Tibor Grasser (Prof. Dr.) is a professor of microelectronics reliability and an IEEE Fellow. He has been the head of the Institute for Microelectronics since 2016. He has edited various books, e.g., on the bias temperature instability, hot carrier degradation, and noise (all Springer), is a distinguished lecturer of the IEEE EDS, is a recipient of the Best and Outstanding Paper Awards at IRPS (2008, 2010, 2012, and 2014), IPFA (2013 and 2014), ESREF (2008), and the IEEE EDS Paul Rappaport Award (2011). He currently serves as an Associate Editor for the IEEE Transactions on Electron Devices following his assignment as Associate Editor for Microelectronics Reliability (Elsevier) and has been involved in various outstanding conferences such as IEDM (General Chair 2021), IRPS, SISPAD, ESSDERC, and IIRW. Prof. Grasser's current research interests include theoretical modeling of performance aspects of 2D and 3D devices (charge trapping and reliability), starting from the ab initio level over more efficient quantum-mechanical descriptions up to TCAD modeling. The models developed in his group have been made available in the most important commercial TCAD environments.

Editoria

# Special Issue on Miniaturized Transistors, Volume II

Lado Filipovic \* and Tibor Grasser \*

Institute for Microelectronics, TU Wien, Gußhausstraße 27-29/E360, 1040 Vienna, Austria \* Correspondence: filipovic@iue.tuwien.ac.at (L.F.); grasser@iue.tuwien.ac.at (T.G.)

Due to the great success of the initial Special Issue on Miniaturized Transistors [1], we have decided to continue addressing the ever-advancing progress in microelectronic device scaling with this second volume. Complementary Metal-Oxide-Semiconductor (CMOS) devices continue to endure miniaturization, irrespective of seeming physical limitations to scaling, helped by advancing fabrication techniques. We also observe that miniaturization does not always refer to the latest technology node for digital transistors. Rather, by applying novel materials and device geometries, we note that a significant reduction in the size of microelectronic devices for a broad set of applications can be achieved. The achievements made in the scaling of devices for applications beyond digital logic (e.g., power applications, optoelectronics, and sensors) are taking the front stage in microelectronic miniaturization. Furthermore, all these achievements are assisted by improvements in the simulation and modeling of the involved materials and device structures. In particular, process and device technology computer-aided design (TCAD) has become indispensable in the design cycle of novel devices and technologies.

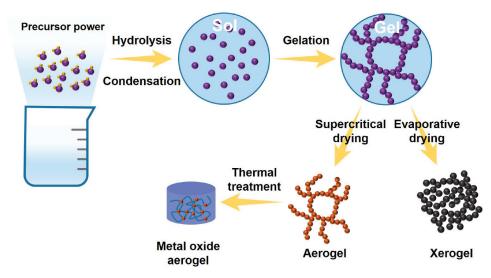

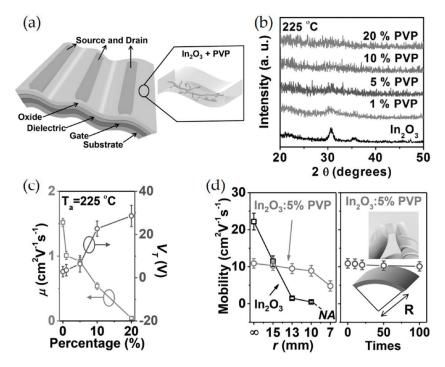

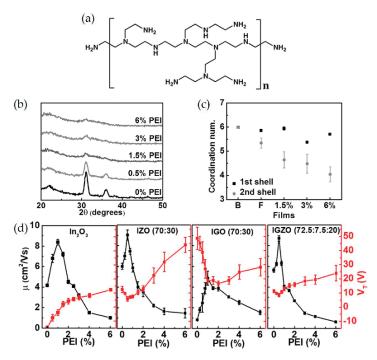

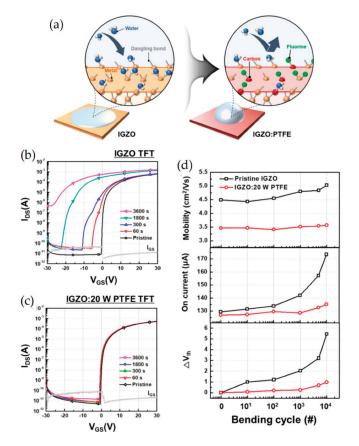

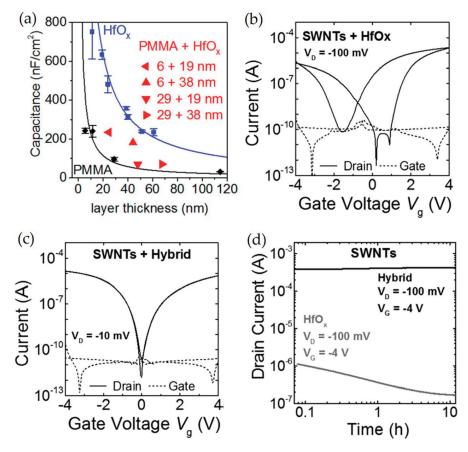

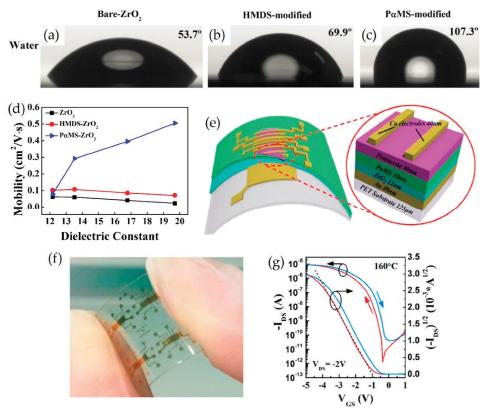

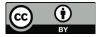

There are 19 research papers published in this Special Issue, covering recent advances in research aspects related to transistor miniaturization, including theoretical assessments of novel device geometries, the application of wide bandgap materials for high-power applications, modeling techniques for highly scaled devices, as well as devices for applications in optoelectronics and sensing. Furthermore, three reviews are included in this Special Issue, one which looks into transistor scaling along Moore's Law and presents ideas about what lies ahead [2], another which investigates the applicability of metal oxide/polymer heterojunctions for flexible and portable electronics [3], and a third which performs an analysis of the reliability of highly scaled devices, where the charging kinetics of single defects play a critical role [4].

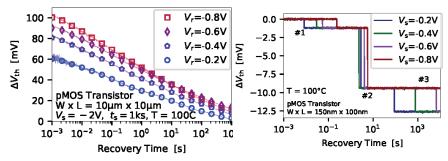

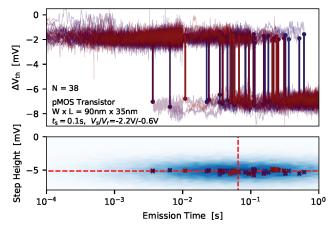

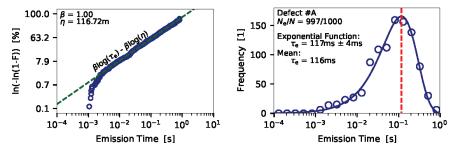

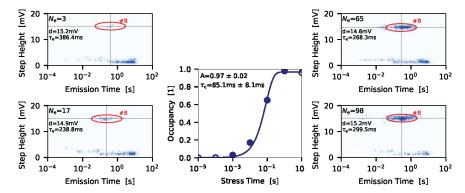

The three review articles which are provided in this Special Issue nicely summarize the impact of miniaturization on the current semiconductor device landscape. They include transistor scaling along Moore's Law and the introduction of new materials and hetero-junctions for exciting new applications in flexible and portable electronics. However, miniaturisation and scaling come at a price, as is discussed in the third review, which looks into the impact of defects in highly scaled devices. Radamson et al. [2] provide a review on the development of the metal-oxide-semiconductor field-effect transistor (MOSFET) over the last decades while following the international technology roadmap of semiconductors (ITRS). They focus on methodologies, challenges, and difficulties when ITRS approaches the end and discuss new and emerging channel materials beyond the Moore era. Jeong et al. [3] provide a thorough review of the application of hybrid polymer/metal oxide films for flexible and wearable devices. These nanocomposites are excellent materials for flexible electronics due to the combined benefits of durability of the polymers and excellent electronic properties of the metal oxides. The authors highlight the advances made in improving the electrical performance of these devices by studying their mobilities and dielectric constants, as well as looking into interface engineering and its impact on the electronic properties. Waltl [4] wraps up this Special Issue with a thorough look into the reliability of highly scaled semiconductor transistors. As transistors are miniaturized further, single defects play an ever-increasing role in the device performance and reliability.

Citation: Filipovic, L.; Grasser, T.

Special Issue on Miniaturized

Transistors, Volume II. Micromachines

2022, 13, 603. https://doi.org/

10.3390/mil3040603

Received: 8 April 2022 Accepted: 11 April 2022 Published: 12 April 2022

Publisher's Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Waltl takes a look into bias temperature instability (BTI) at the single-defect level to provide an in-depth investigation of charge trapping kinetics of the defects to ultimately provide an accurate assessment of the device lifetime.

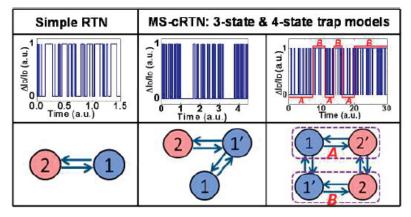

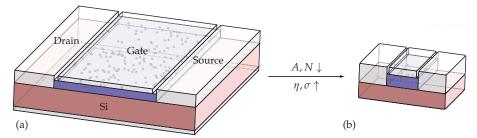

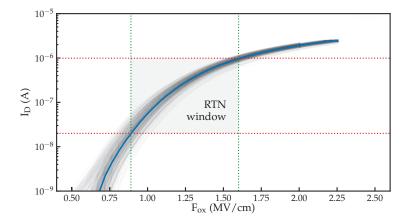

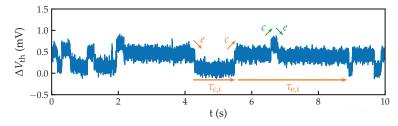

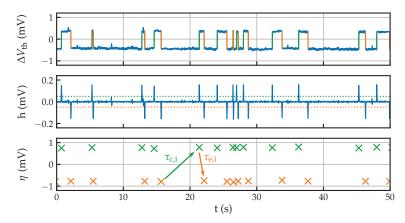

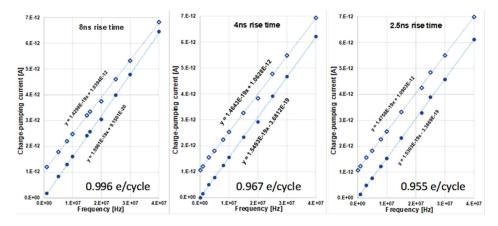

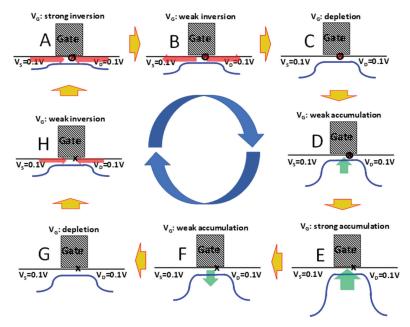

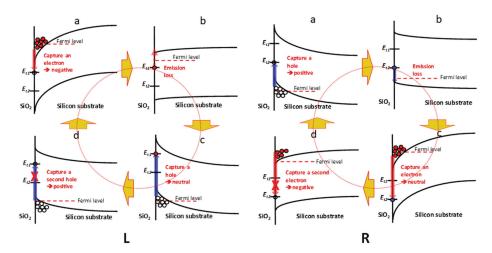

The impact of single defects is also studied by Stampfer et al. [5]. The authors of this paper look at the adverse effects of miniaturization. Mainly, they observe how miniaturization leads to increased variability among nominally identical devices, primarily due to the increased relative impact of oxide traps. With random telegraph noise (RTN) measurements, the authors are able to extract the step heights of defects present at the Si/SiO<sub>2</sub> interface. They note that, contrary to recently published studies, a bimodal distribution in step heights can be observed. Cheung, in [6], on the other hand, explores the potential application of a single-defect MOSFET device towards the realization of the elusive quantized current source. Their experimental results on a single-defect MOSFET shows that the one charge pumped per cycle is valid, encouraging further exploration of charge pumping based on quantum current sources.

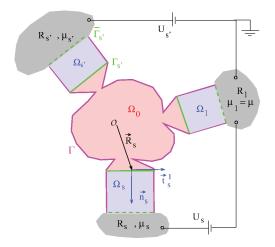

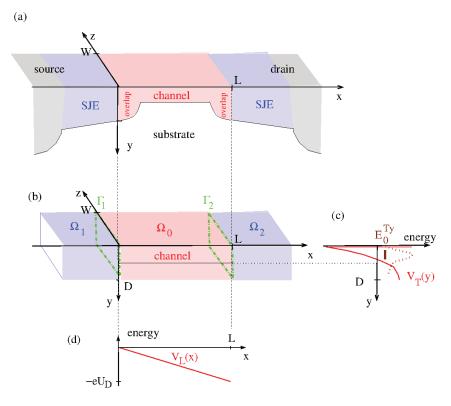

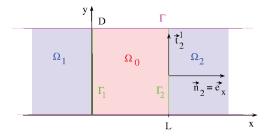

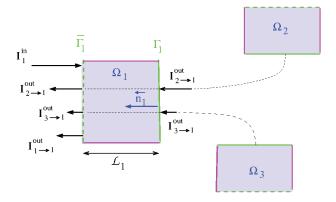

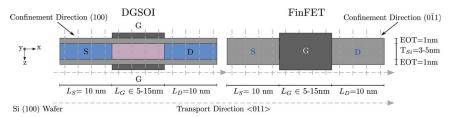

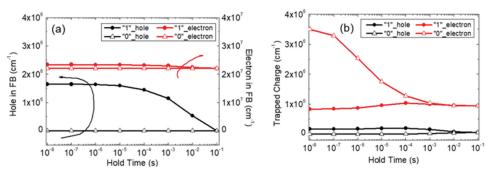

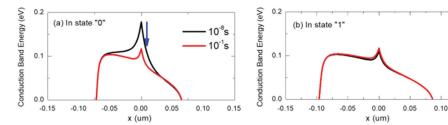

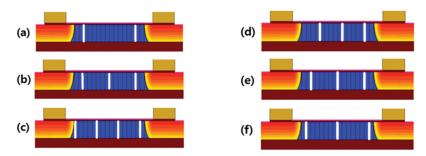

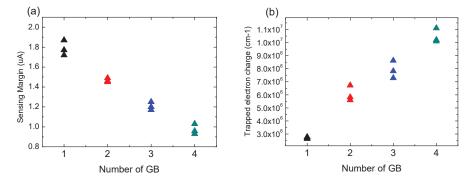

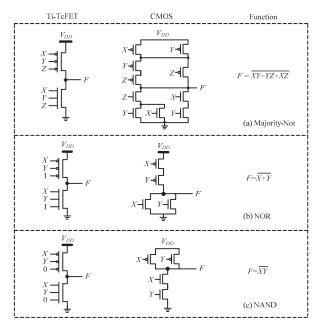

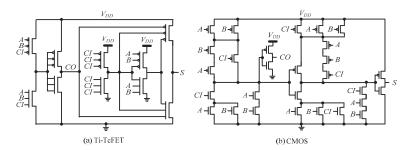

With increased device scaling and the uncertainty of what lies beyond Moore's law once the physical limits are reached, many researchers are theorizing about novel transistor designs. For this, applying advanced TCAD tools is indispensable. It is no longer a reasonable expectation that any potential design can be tested in a lab, as this comes with extremely high costs, especially at the leading technology nodes. Instead, many researchers rely on TCAD as an initial assessment of their proposed device ideas. With this in mind, in [7], Wulf presents a compact nanotransistor model which allows for the extraction of important device parameters such as the effective height of the source-drain barrier, device heating, and the quality of the coupling between the conduction channel and the contacts. This model is then used to quantitatively describe quantum transport in a variety of industrial nano-FETs. Medina-Bailon et al. [8] presented a quantum enhancement of a 2D Multi-Subband Ensemble Monte Carlo (MS-EMC) simulator, specifically to observe transistor behavior at the nanometer scale. Kim et al. [9] use TCAD simulations to examine the differences between the memory mechanisms in poly-silicon and silicon body onetransistor dynamic random-access memory (1T-DRAM) cells. They found that a polysilicon 1T-DRAM can perform memory operations by using grain boundaries (GBs) as storage regions in thin body devices with a small floating body (FB) area. Zhang et al. [10] propose an implementation of a novel core-insulator gate-all-around (CIGAA) nanowire transistor which exhibits low off-state current compared to that of traditional gate-allaround (GAA) nanowire devices, making it ideal for future energy-efficient applications. Han et al. [11] proposed a germanium-based GAA transistor, which shows an all-around improved performance when compared to silicon GAA FETs. Specifically, the germainum GAA FET exhibits a higher ON/OFF ratio compared to silicon and a steady and steep average subthreshold swing. Chen et al. [12] presents a three-input, three-channel field effect transistor (TI-TcFET) design with multiple gate contacts (top, front, and back) in order to increase the gate control of the channel. The authors show that the proposed device could be used to simplify complex circuits by using less transistors than in traditional CMOS technology.

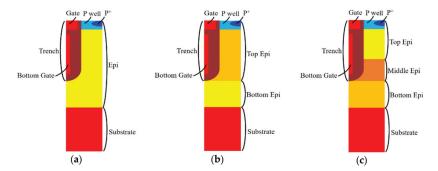

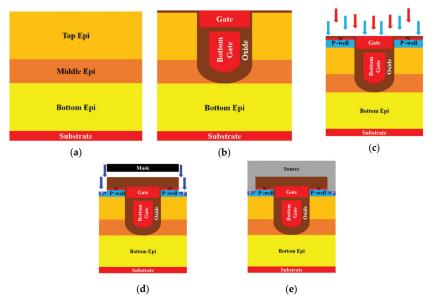

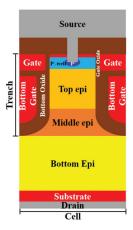

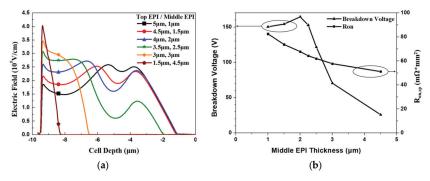

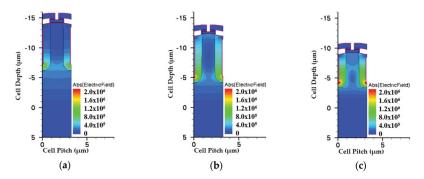

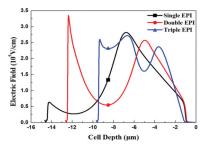

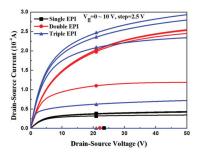

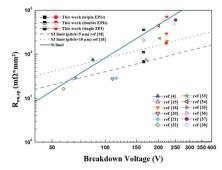

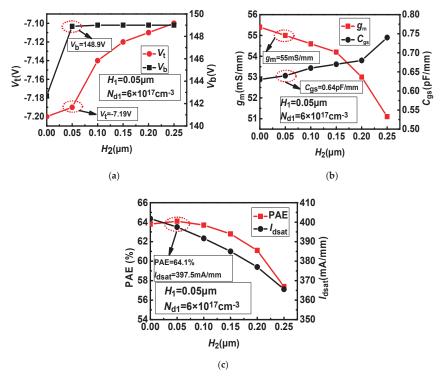

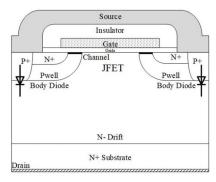

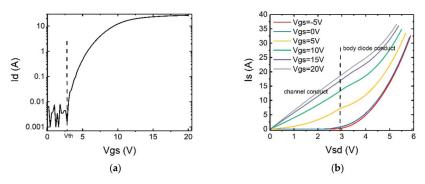

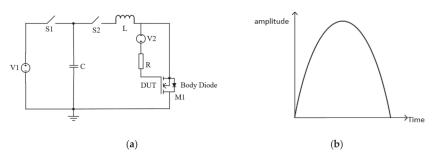

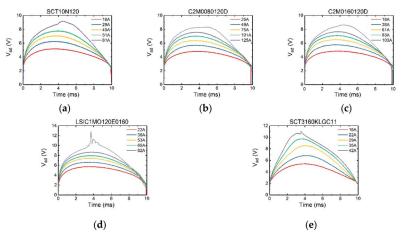

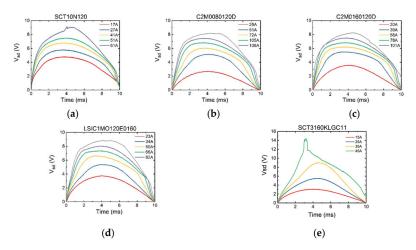

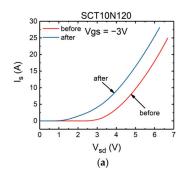

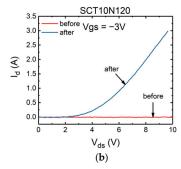

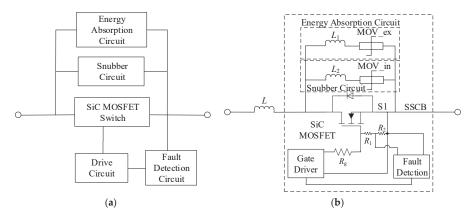

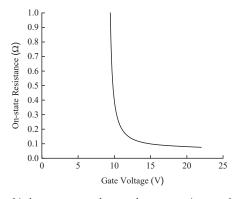

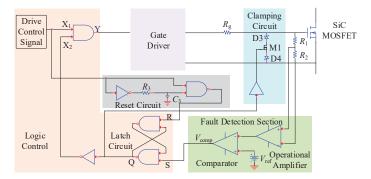

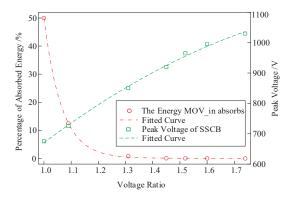

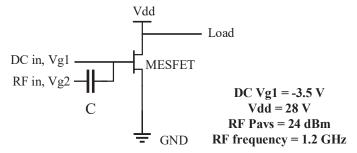

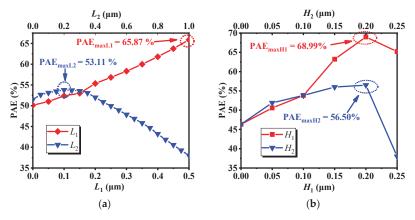

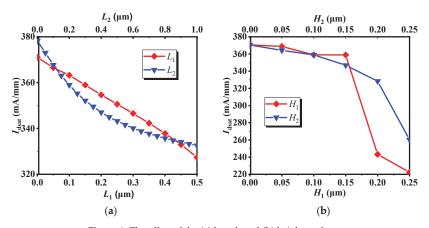

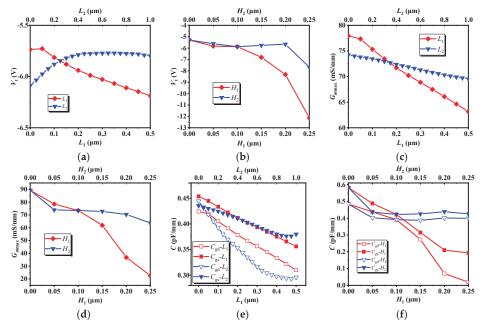

Beyond digital logic, high-power electronic devices are playing a very important role in today's technology development. They are essential components in the push towards autonomous vehicles and safer air and space travel, while also providing important progress towards green energy applications and overall increase in energy efficiency. Six papers in this Special Issue look into novelties related to high-power electronic devices, mostly using wide-bandgap semiconductors such as silicon carbide (SiC) and gallium nitride (GaN). Chien et al. [13] study the application of a split-gate trench (SGT) power metal-oxide-semiconductor field-effect transistor (MOSFET) to reduce specific ON resistance. They note that the bottom epitaxial layer of a double-epitaxy structure can be designed to support the breakdown voltage, while the top one can be adjusted to reduce the ON resistance. Jia et al. [14] present a 4H-SiC metal-semiconductor field-effect transistor (MESFET) with layered doped and undoped regions. After optimizing the thickness of the

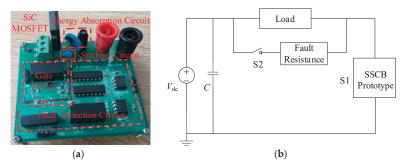

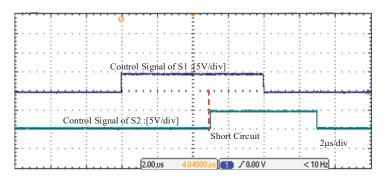

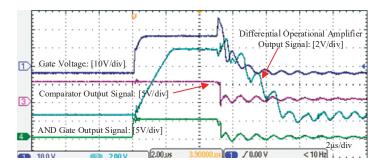

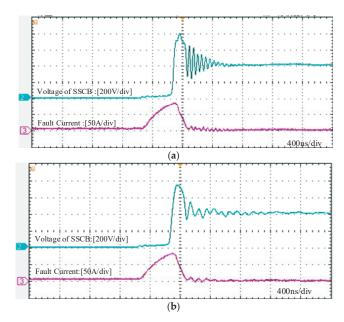

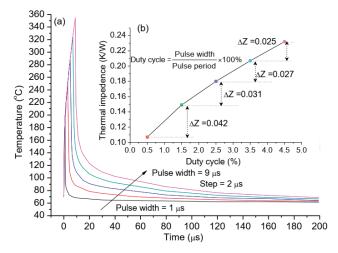

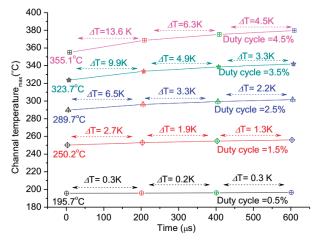

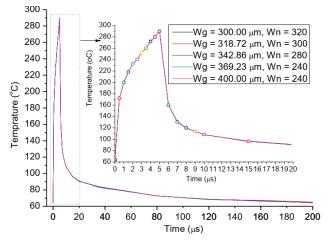

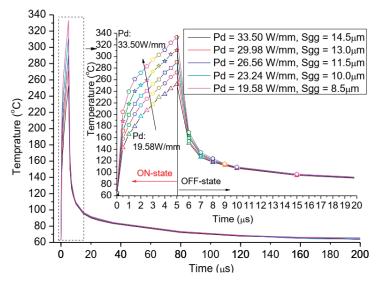

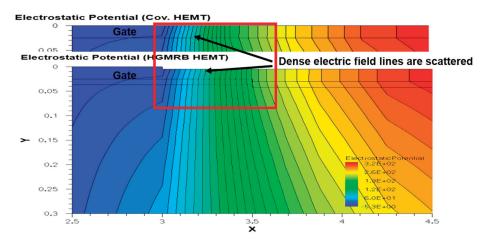

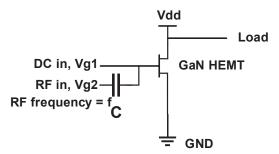

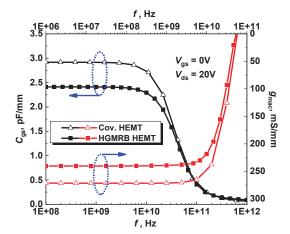

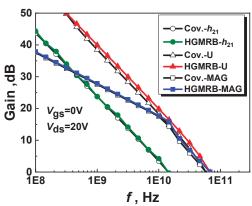

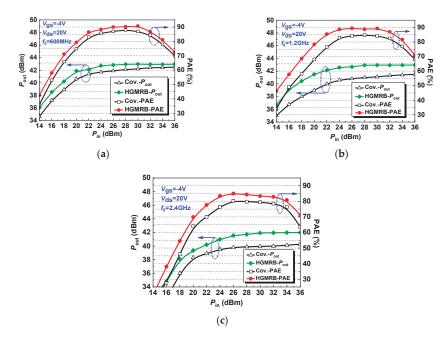

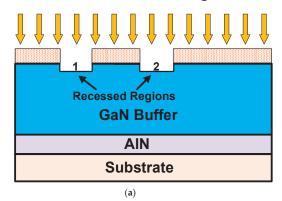

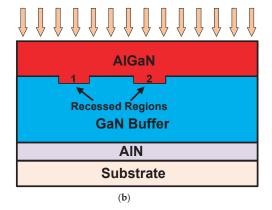

undoped region, the authors obtained an increase in the power-added efficiency (PAE) of 85.8% and a saturation current increase of 27.4%, when compared to the double-recessed 4H-SiC MESFET. Li et al. [15] tested the surge reliability of 1200 V SiC MOSFETs from various manufactures by stressing them until failure. By decapping the failed devices and observing the cross-section of the damaged cell, they found that high temperature caused by excessive current flow through the devices during the surge tests is the main culprit for failure. In a contribution by Li et al. [16], the authors propose and test a SiC MOSFETs device which is able to meet the requirements of DC microgrid protection. Their prototype was developed, tested, and compared to the silicon-based insulated gate bipolar transistor (IGBT) alternative, showing high promise in its application in a solid-state circuit breaker. Guo et al. [17] looked into the thermal characteristics of pulse-operated AlGaN/GaN highelectron-mobility transistors (HEMTs). Their models show that the maximum channel temperature and thermal impedance of the devices are considerably influenced by the pulse width and power density, while the geometry of the gates, i.e., variations in the gate fingers and their width, have no effect on the channel temperature, as long as the total gate width and active area is kept constant. Zhu et al. [18] propose a new design for a multi-recessed double-recessed p-buffer layer 4H-SiC metal semiconductor field effect transistor (IMRD 4H-SiC MESFET) with high PAE. Their design shows an improvement in the PAE of almost 70%, when compared to similar state-of-the-art designs. In an additional contribution from Zhu et al. [19], a novel AlGaN/GaN HEMT is proposed, with a high gate and a multi-recessed buffer (HGMRB) for high-energy-efficiency applications. Their design promises an increase in the breakdown voltage by 16.7%, while the gate-to-source capacitance is decreased by 17%. The radio frequency (RF) simulations showed impressive PAEs of 90.8%, 89.3%, and 84.4% at 600 MHz, 1.2 GHz, and 2.4 GHz, respectively.

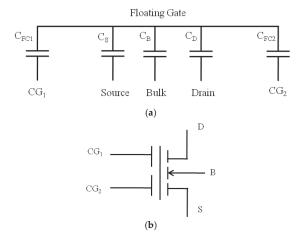

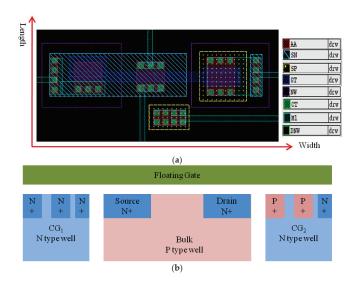

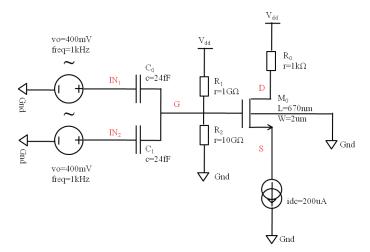

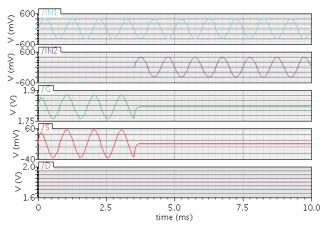

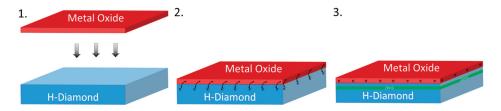

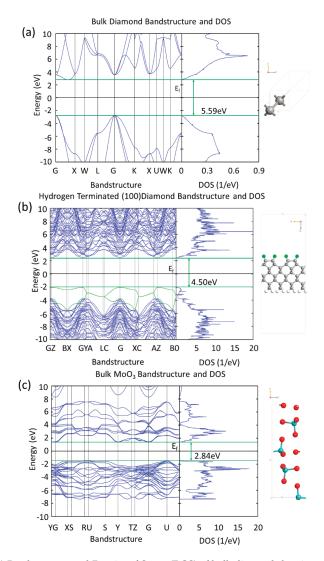

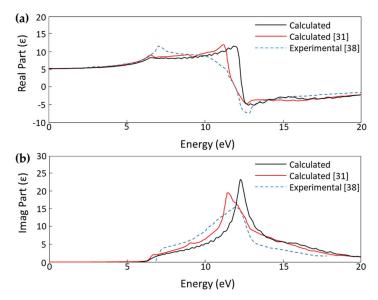

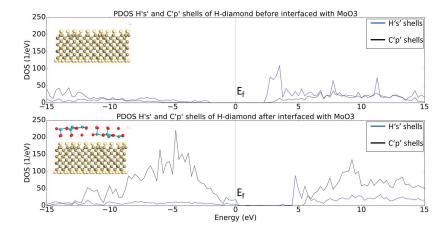

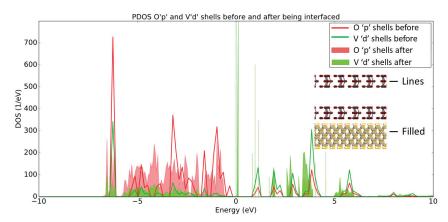

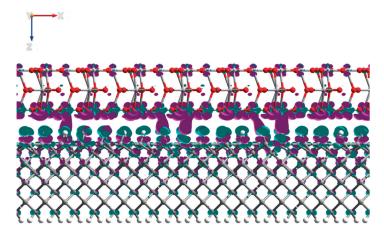

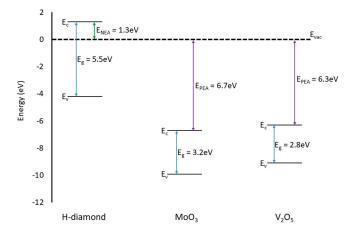

This Special Issue also looks at applications beyond digital logic and high-power applications. Several research papers have been included, which discuss novel sensing and imaging technologies. Cheng et al. [20] studied the potential of using vacuum channel transistors in low-loss and high-speed electronics for operation in high-temperature and high-radiation environments. Their measurements of vertical diodes further show that current and voltage vary based on the pressure and gas composition of the ambient, suggesting a potential application of these devices for gas and pressure sensing. Mao et al. [21] theorized a floating gate transistor with two control gates in order to provide active noise control in bio-electrical measurements. The advantage of their implementation is the ability to use a cost-efficient single-polysilicon CMOS fabrication process. Zhi et al. [22] presented a novel avalanche photodiode (APD) design, which is compatible with Taiwan Semiconductor Manufacturing Company (TSMC)'s standard CMOS process, realizing scaling in these devices by enabling an integration between the optoelectronic and digital components. The fabricated device is able to operate at a wavelength of 850 nm. Finally, McGhee and Georgiev in [23] apply semi-empirical density functional theory (DFT) calculations to study the surface transfer doping process between hydrogen-terminated (100) diamond and the metal oxides  $MoO_3$  and  $V_2O_5$ . Their study shows that both oxides act as electron acceptors and inject holes into the diamond structure, meaning that these metal oxides can be described as p-type doping materials for diamond. The study suggests the ability to use deposited metal oxides in an oxygen-rich atmosphere to enhance the surface transfer doping between diamond and the oxides.

Finally, we would like to take this opportunity to thank all the authors for submitting exceptional and highly relevant research papers to this Special Issue. We would also like to sincerely thank all the reviewers who took precious time to carefully examine and help improve the quality of all submitted manuscripts. Peer review is an essential component of good science, and they deserve recognition for the success of this Special Issue. It is our sincere hope that the results provided in this Special Issue prove useful to scientists and engineers who find themselves at the forefront of this rapidly evolving and broadening field. Now, more than ever, it is essential to look for solutions to find the next disrupting technologies which will allow for transistor miniaturization well beyond silicon's physical

limits and the current state-of-the-art. This requires a broad attack, including studies of novel and innovative designs as well as emerging materials which are becoming more application-specific than ever before.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Filipovic, L.; Grasser, T. Editorial for the Special Issue on Miniaturized Transistors. Micromachines 2019, 10, 300. [CrossRef]

[PubMed]

- 2. Radamson, H.H.; He, X.; Zhang, Q.; Liu, J.; Cui, H.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; Gao, J.; et al. Miniaturization of CMOS. *Micromachines* 2019, 10, 293. [CrossRef] [PubMed]

- 3. Jeong, J.W.; Hwang, H.S.; Choi, D.; Ma, B.C.; Jung, J.; Chang, M. Hybrid Polymer/Metal Oxide Thin Films for High Performance, Flexible Transistors. *Micromachines* 2020, 11, 264. [CrossRef] [PubMed]

- Waltl, M. Reliability of Miniaturized Transistors from the Perspective of Single-Defects. Micromachines 2020, 11, 736. [CrossRef]

[PubMed]

- Stampfer, B.; Schanovsky, F.; Grasser, T.; Waltl, M. Semi-Automated Extraction of the Distribution of Single Defects for nMOS Transistors. *Micromachines* 2020, 11, 446. [CrossRef]

- 6. Cheung, K.P.; Wang, C.; Campbell, J.P. Nanoscale MOSFET as a Potential Room-Temperature Quantum Current Source. *Micromachines* 2020, 11, 364. [CrossRef]

- Wulf, U. A One-Dimensional Effective Model for Nanotransistors in Landauer-Büttiker Formalism. Micromachines 2020, 11, 359. [CrossRef]

- 8. Medina-Bailon, C.; Carrillo-Nunez, H.; Lee, J.; Sampedro, C.; Padilla, J.L.; Donetti, L.; Georgiev, V.; Gamiz, F.; Asenov, A. Quantum Enhancement of a S/D Tunneling Model in a 2D MS-EMC Nanodevice Simulator: NEGF Comparison and Impact of Effective Mass Variation. *Micromachines* 2020, 11, 204. [CrossRef]

- 9. Kim, H.; Yoo, S.; Kang, I.M.; Cho, S.; Sun, W.; Shin, H. Analysis of the Sensing Margin of Silicon and Poly-Si 1T-DRAM. *Micromachines* 2020, 11, 228. [CrossRef]

- 10. Zhang, Y.; Han, K.; Li, J. A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator. *Micromachines* **2020**, *11*, 223. [CrossRef]

- 11. Han, K.; Long, S.; Deng, Z.; Zhang, Y.; Li, J. A Novel Germanium-Around-Source Gate-All-Around Tunnelling Field-Effect Transistor for Low-Power Applications. *Micromachines* 2020, 11, 164. [CrossRef] [PubMed]

- 12. Chen, Z.; Hu, J.; Ye, H.; Chu, Z. T-Channel Field Effect Transistor with Three Input Terminals (Ti-TcFET). *Micromachines* 2020, 11, 64. [CrossRef] [PubMed]

- 13. Chien, F.T.; Wang, Z.Z.; Lin, C.L.; Kang, T.K.; Chen, C.W.; Chiu, H.C. 150–200 V Split-Gate Trench Power MOSFETs with Multiple Epitaxial Layers. *Micromachines* 2020, 11, 504. [CrossRef] [PubMed]

- 14. Jia, H.; Liang, Y.; Li, T.; Tong, Y.; Zhu, S.; Wang, X.; Zeng, T.; Yang, Y. Improved DRUS 4H-SiC MESFET with High Power Added Efficiency. *Micromachines* 2020, 11, 35. [CrossRef] [PubMed]

- 15. Li, H.; Wang, J.; Ren, N.; Xu, H.; Sheng, K. Investigation of 1200 V SiC MOSFETs' Surge Reliability. *Micromachines* 2019, 10, 485. [CrossRef] [PubMed]

- 16. Li, H.; Yu, R.; Zhong, Y.; Yao, R.; Liao, X.; Chen, X. Design of 400 V Miniature DC Solid State Circuit Breaker with SiC MOSFET. *Micromachines* 2019, 10, 314. [CrossRef]

- 17. Guo, H.; Chen, T.; Shi, S. Transient Simulation for the Thermal Design Optimization of Pulse Operated AlGaN/GaN HEMTs. *Micromachines* **2020**, *11*, 76. [CrossRef]

- 18. Zhu, S.; Jia, H.; Wang, X.; Liang, Y.; Tong, Y.; Li, T.; Yang, Y. Improved MRD 4H-SiC MESFET with High Power Added Efficiency. *Micromachines* 2019, 10, 479. [CrossRef]

- 19. Zhu, S.; Jia, H.; Li, T.; Tong, Y.; Liang, Y.; Wang, X.; Zeng, T.; Yang, Y. Novel High-Energy-Efficiency AlGaN/GaN HEMT with High Gate and Multi-Recessed Buffer. *Micromachines* **2019**, *10*, 444. [CrossRef]

- 20. Chang, W.T.; Hsu, H.J.; Pao, P.H. Vertical Field Emission Air-Channel Diodes and Transistors. *Micromachines* **2019**, *10*, 858. [CrossRef]

- Mao, C.; Yang, C.; Ma, H.; Yan, F.; Zhang, L. A Smart Floating Gate Transistor with Two Control Gates for Active Noise Control. Micromachines 2019, 10, 722. [CrossRef] [PubMed]

- Zhi, W.; Quan, Q.; Yu, P.; Jiang, Y. A 45 nm CMOS Avalanche Photodiode with 8.4-GHz Bandwidth. Micromachines 2020, 11, 65.

[CrossRef] [PubMed]

- 23. McGhee, J.; Georgiev, V.P. Simulation Study of Surface Transfer Doping of Hydrogenated Diamond by MoO<sub>3</sub> and V<sub>2</sub>O<sub>5</sub> Metal Oxides. *Micromachines* **2020**, *11*, 433. [CrossRef] [PubMed]

Review

## **Miniaturization of CMOS**

Henry H. Radamson <sup>1,2,3,\*,†</sup>, Xiaobin He <sup>1,†</sup>, Qingzhu Zhang <sup>1,4,†</sup>, Jinbiao Liu <sup>1,†</sup>, Hushan Cui <sup>5,†</sup>, Jinjuan Xiang <sup>1,†</sup>, Zhenzhen Kong <sup>1,†</sup>, Wenjuan Xiong <sup>1,2,†</sup>, Junjie Li <sup>1,2,†</sup>, Jianfeng Gao <sup>1,†</sup>, Hong Yang <sup>1,2,†</sup>, Shihai Gu <sup>1,6,†</sup>, Xuewei Zhao <sup>1,7,†</sup>, Yong Du <sup>1,2,†</sup>, Jiahan Yu <sup>1,†</sup> and Guilei Wang <sup>1,2,\*,†</sup>

- Key Laboratory of Microelectronics Devices & Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China; hexiaobin@ime.ac.cn (X.H.); zhangqingzhu@ime.ac.cn (Q.Z.); liujinbiao@ime.ac.cn (J.L.); xiangjinjuan@ime.ac.cn (J.X.); kongzhenzhen@ime.ac.cn (Z.K.); xiongwenjuan@ime.ac.cn (W.X.); lijunjie@ime.ac.cn (J.L.); gaojianfeng@ime.ac.cn (J.G.); yanghong@ime.ac.cn (H.Y.); gushihai@ime.ac.cn (S.G.); zhaoxuewei@ime.ac.cn (X.Z.); duyong@ime.ac.cn (Y.D.); yujiahan@ime.ac.cn (J.Y.)

- <sup>2</sup> Microelectronics Institute, University of Chinese Academy of Sciences, Beijing 100049, China

- Department of Electronics Design, Mid Sweden University, Holmgatan 10, 85170 Sundsvall, Sweden

- State Key Laboratory of Advanced Materials for Smart Sensing, General Research Institute for Nonferrous Metals, Beijing 100088, China

- Fert Beijing Institute, Big Data Brain Computing (BDBC), Beihang University, Beijing 100191, China; cuihusan@ime.ac.cn

- School of Artificial Intelligence, University of Chinese Academy of Sciences, Beijing 100049, China

- School of Microelectronics, University of Science and Technology of China, Anhui 230026, China

- \* Correspondence: rad@ime.ac.cn (H.H.R.); wangguilei@ime.ac.cn (G.W.); Tel.: +86-010-8299-5793 (G.W.)

- † The authors have equally contributed in this article.

Received: 3 March 2019; Accepted: 11 April 2019; Published: 30 April 2019

**Abstract:** When the international technology roadmap of semiconductors (ITRS) started almost five decades ago, the metal oxide effect transistor (MOSFET) as units in integrated circuits (IC) continuously miniaturized. The transistor structure has radically changed from its original planar 2D architecture to today's 3D Fin field-effect transistors (FinFETs) along with new designs for gate and source/drain regions and applying strain engineering. This article presents how the MOSFET structure and process have been changed (or modified) to follow the More Moore strategy. A focus has been on methodologies, challenges, and difficulties when ITRS approaches the end. The discussions extend to new channel materials beyond the Moore era.

Keywords: FinFETs; CMOS; device processing; integrated circuits

#### 1. Introduction

In 1965, Gordon Moore, the founder of Intel, published his famous paper describing the evolution of transistor density in integrated circuits. Although his first insight was to establish a business roadmap to increase the profit of the company, he later built the fundaments for technology roadmap in the semiconductor industry. Moore's idea was based on doubling the transistor density in the chip every 18 months, which causes the transistors to become smaller in size and consumes lower power while performing at higher speed [1].

With years of continuing MOSFETs (metal oxide effect transistor) down-scaling, different non-ideal factors e.g., short channel effects (SCEs), poor electrostatics integrity, and large device variability appeared. Therefore, conventional bulk FinFET and fully depleted silicon on the insulator (FDSOI) are proposed to improve the above problems by applying low gate voltage to fully deplete the ultra-thin silicon [2]. Currently, bulk FinFET has been widely used in mass production from 22 nm to 10 nm

node and will be extended to the 5-nm node [3–6]. In fact, the critical dimension (CD) of the device, e.g., gate length ( $L_g$ ), applied voltage ( $V_{\rm DD}$ ), and effective oxide thickness (EOT) are not strictly scaling, according to the Moore's law. The foundries seek an improvement of driving current ( $I_{\rm DS}$ ) at the same leakage or achieve the smaller leakage at the same  $I_{\rm DS}$ . On the approach to the end of the technology roadmap, the 3-nm node and the traditional bulk FinFET technologies would suffer from enormous challenges [7]. Thus, new device structures, new materials, and new integration approaches have to provide new solutions. Therefore, novel promising device architectures like fin-on-insulator (FOI) FinFET [8–11], scalloped fin FinFET [12], nanowire (NW) FETs, and the stacked NW device [13–15] have demonstrated great improvement for short channel effects (SCEs), leakage control, and higher electron and whole mobility. The fin-on-insulator (FOI) FinFET, fabricated on the bulk Si substrate with a special process takes both advantages of bulk FinFET and SOI technologies. Therefore, it may be one of the most promising candidates for further device scaling. In addition, the low cost and fully Metallic Source and Drain (MSD) process is extensively investigated for the FOI FinFET [9].

Other architecture such as scalloped fin FinFETs with mainstream all-last HKMG (high-*k* and metal-gate) technology could provide a larger control area and obtain a great improvement for SCEs. Stacked gate-all-around (GAA) NW or nano-sheet is also receiving increasing attention among all device structures. This is considered to be the most promising candidate beyond FinFET technologies for a 3-nm node due to its special characteristic, such as quasi-ballistic transport, steep sub-threshold slope, and one-dimensional channel geometry [13,14].

3D-monolithic or 3D sequential CMOS technology is based on stacking active device layers on top of each other with very small 3D contact pitch (similar pitch as a standard contact) [16,17]. This approach could achieve a 14-nm circuit performance by using 3D sequential CMOS technology with lower parasitic resistance, capacitor, and signal delay. In addition, this integration scheme offers a wide spectrum of applications including (i) increasing integration density beyond device scaling, (ii) enabling neuromorphic integration where RRAM is placed between top and bottom tiers, and (iii) enabling low-cost heterogeneous integration for e.g., smart sensing arrays. However, such an integration process faces the challenges of fabricating high-performance devices in the top tier without degrading the electrical characteristics of the bottom tier [18,19].

The CMOS scaling-down in process,  $V_{DD}$ , and temperature (PVT) are becoming a major issue for the nanoscale IC design. The need for low power induces supply voltage scaling, which makes voltage variations a significant design challenge. Moreover, the operation frequency is sensitive to die temperature variations. Therefore, it is increased at high junction temperatures. It is known that process variations are a serious concern due to uncertainty in the device and interconnects characteristics. Process variations negatively impact the speed, stability, and power consumption of traditional transistor designs.

With the continuing scaling of devices, the driving current would become bigger and the frequencies of transmitted signals become higher [20,21].

This article presents how the technology roadmap deal with miniaturization of CMOS including advanced lithography for patterning nano-scaled transistors, process integration, (wet and dry) etching, strain engineering with an emphasis on SiGe epitaxy for source/drain (S/D), dopant implantation, gate formation including deposition of high-k material, and the metal gate using the atomic layer deposition (ALD) technique, and III-V materials for high carrier mobility in the channel for FinFETs. The discussions have a focus on the challenges and difficulties of the path of More Moore and even provide a glimpse of the beyond Moore era for CMOS.

#### 2. Miniaturization Principles

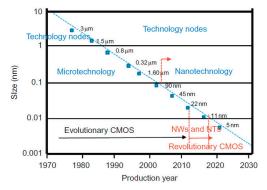

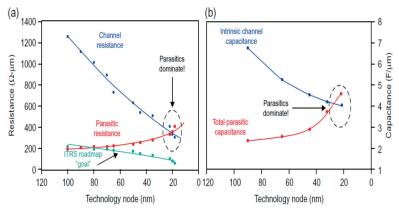

Figure 1 shows the official technology roadmap, which was originally established in the early 1970s and the semiconductor industries began to down scale the transistors [22]. In 2003, when the transistor size shrunk to sub 100 nm, the nano-electronic era was inaugurated. The continuation of down-scaling lead to the parasitic capacitance and the resistance increased. Lastly, the 2D transistors

were abandoned and 3D FinFETs were introduced. This is considered as a revolutionary design in the transistor world, which paved the path for sub 22 nm FinFETs with high performance and full control on the carrier transport in the channel.

**Figure 1.** Miniaturization of the transistor gate length in different technology nodes and production years [22].

The down-scaling of the transistors results in operation at lower supply voltages as well as switching with less current.

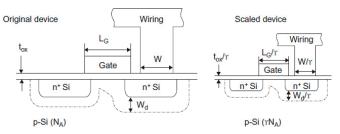

On one hand, the shorter channel causes lower gate capacitance and higher drive current resulting in faster transistors. On the other hand, the shorter channels contribute to higher S/D and Gate leakage since gate oxide becomes thinner. The smaller transistors have both lower  $V_{DD}$  and threshold voltage  $(V_T)$  or, in principle, lower dynamic power is obtained. The main rules to miniaturize MOSFET with a factor of  $\gamma$  is demonstrated in Figure 2 [23]. This task is performed for transistors when the gate length and width, oxide thickness, junction depth, and substrate doping are downscaled. Therefore, both supply and threshold voltages are also scaled by a factor of  $\gamma$ . In this way, the electric field is maintained constant. Meanwhile, the density of transistors is increased by factor of  $\gamma^2$ . In this design, the ratio between gate length and width is also unchanged.

Figure 2. A schematic drawing of MOSFET downscaling [23].

However, information on the size of the pitch in nanometer technologies and the freedom in choosing the size of the transistors can be different. Simply, the pitch parameter may not follow the same trend as the general miniaturization of technologies.

#### 3. Lithography of Nano-Scaled Transistors

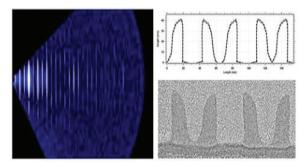

A state-of-the-art lithography seeks sharp patterns with high reproducibility. For 20-nm and 14-nm node technology, 193 nm ArF immersion with multiple patterning has been mainly used [24]. Meanwhile, 193-nm immersion with self-aligned double patterning (SADP) and self-aligned quadruple patterning (SAQP) techniques is intended to be used for a 7-nm technology node [24].

SADP is a technique which applied spacer transfer process for small pitch whereas SAQP is applied twice self-aligned double patterning to develop very narrow features [25].

There is a strong effort to apply extreme ultraviolet (EUV) lithography and 193 nm immersion with multi-patterning for a 7-nm node. Although EUV simplifies the patterning process for the 7-nm node, EUV still has issues with resists and mask infrastructure as well as the power source, which have to be solved before high-volume manufacturing.

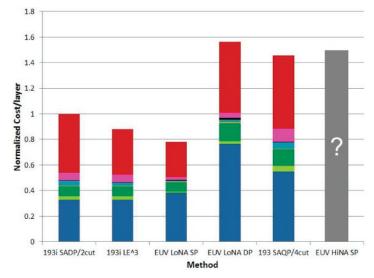

Figure 3 indicates that the lithography cost depends on the layer and, therefore, the cost of applying either 193i triple patterning or 193i SADP are roughly equal to single-patterning with EUV. This means that the choice of the lithography method depended more on the performance-involved trade-offs [26]. For 7-nm and 5-nm nodes, there is a risk that quad-patterning may occur from 193i and double-patterning from existing EUV tools, or single-patterning from as-yet undelivered high numerical aperture (NA) EUV tools.

Figure 3. Normalized cost/layer vs. lithography method.

To apply 193 nm immersion lithography with multiple patterning for 7-nm and 5-nm nodes has difficulties. The main problem is overlay, which involves the ability of a scanner to align the various mask layers accurately on top of each other. There may be too many masks at each new node. This slows down throughput in the mask shop, increases the possibility that errors will be introduced, and raises the cost at the same time.

Recently, it has demonstrated excellent industrialization progress of its pellicle, with tests confirming that pellicles can withstand 245 W source power and an offline power lifetime test indicating 400 W capability. Compared to the 7-nm logic node, the requirements for EUV masks is tighter for 5 nm. Meanwhile there is good progress to support 5 nm in areas such as reducing mask blank defects [27,28].

The EUV mask infrastructure is the need to manufacture defect-free photo masks where an actinic mask review capability is a critical success factor [29,30]. The ongoing development for an EUV pellicle solution alleviates industry concern about one significant source of line-yield risk [31]. Because pellicles are currently unavailable for EUV lithography, other measures need to be taken to deal with contamination that can occur during mask transport and usage. Such contamination can indeed occur, and it has been observed by practitioners of EUV lithography. This may occur with sufficient frequency, which justifies the concern for repeating defects that can reduce the yield significantly [32].

In addition to the high EUV sensitivity, low local CD uniformity, and high patterning resolution, the next generation resist systems should also efficiently solve the issues of pattern collapse, resist homogeneity, etch resistance, UV out of band, outgassing, high volume manufacturing (HVM) compatibility, defects, and shelf-life [33].

To improve throughput in HVM, the resist sensitivity to the 13.54-nm wavelength radiation of EUV needs to be improved while the line-width roughness (LWR) specification must be held to low single-digit nm. With a 250 W source and 25 mJ/cm² resist sensitivity, an EUV stepper should be able to process ~100 wafer-per-hour (wph), which should allow the affordable process when matching with other lithography technologies.

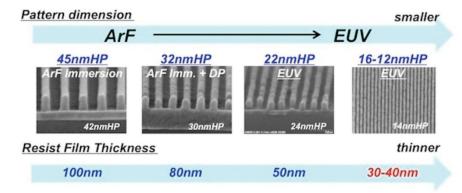

Figure 4 shows that higher absorption allows the use of thinner resist, which mitigates the issue of line collapse. Resistance as thin as 18 nm has been patterned over a 70-nm thin Spin-On Carbon (SOC) layer without the need for another Bottom Anti-Reflective Coating (BARC).

**Figure 4.** Evolution of the lithography technique where the pattern becomes denser and smaller in each new technology node. To prevent pattern collapse, the thickness of resist is reduced proportionally to the minimum half-pitch (HP) of lines/spaces.

#### 4. Process Integration of New Transistor Architecture

#### 4.1. Process Flow of 2D and 3D Transistors

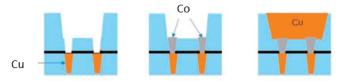

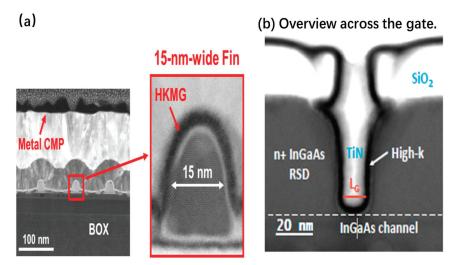

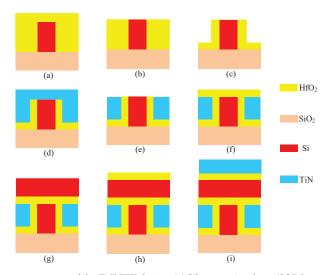

The process flow of FinFETs consists of the SADP technique, followed by oxide filling, planarization using CMP (chemical mechanical polish), and etching to reach the fin active region and form shallow trench isolation (STI). Afterwards, the process flow is similar to the planar transistors e.g., well doping, dummy gate deposition and patterning, spacer formation, SiGe-epi, and S/D formation, interlayer dielectric zero (ILD0), chemical mechanical polish (CMP), dummy gate etch, high-k and metal-gate (HKMG) process, self-aligned contacts (SACs) for silicide and metal formation, local interconnects (LI), and back-end-of-line (BEOL) interconnect construction [34–36], as shown in Figure 5.

Fin patterning vs. planar active region patterning

Oxide filling, planarization, and recessing

Doping to form well isolation

Gate oxide growth, and dummy gate deposition, planarization and patterning

Doping to form S/D extentions

Spacer deposition and patterning

Epitaxy forming S/D regions (embedded SiGe and raised Si)

ILDO& CMP

Dummy gate removal

Replacement of high-k & metal gate stack

Self-aligned contact formation

Back end of line

Figure 5. Process flow for the bulk FinFETs or planar transistors. The FinFETs process are underlined [36].

On the path of CMOS miniaturization, the smaller contact size leads to higher contact resistance and contact-to-gate capacitance. Normally, the parasitic effects had no big impacts on the transistor performance because they were significantly smaller than the resistance and capacitance of the channel. However, both these effects becomes proportional to the gate length, which has been significantly reduced during past years. The parasitic effects became comparable or even larger than the intrinsic channel (gate and body) capacitance and resistance, as is shown in Figure 6.

Figure 6. (a) Parasitic resistances and (b) capacitances in each technology node [22].

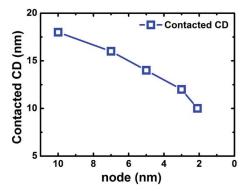

The contacted CD of FinFET or lateral GAA NW device is 18 nm for the 10-nm node and the contacted CDs are expected to be 16 nm, 14 nm, and 12 nm for 7 nm, 5 nm, and 3 nm in the future, respectively [37], as is shown in Figure 7. The contacted resistivity has reached sub  $10^{-9}~\Omega\cdot\text{cm}^2$  for advanced CMOS FinFET beyond 7 nm, and the values need to be smaller in the future [38].

Figure 7. Values of contacted CD for advanced device.

#### 4.2. Challenges in FinFETs' Process

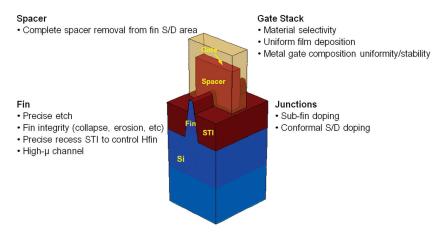

Electrical characteristics of FinFETs are related to the fins' profile and dimensions [39]. In order to transport higher current, longer fins are required, which leads to several challenges to manufacture transistors, as shown in Figure 8.

Figure 8. New challenges in the miniaturization of FinFETs [36].

The process of long Si fins creates difficulty for the integration of poly gate, spacer, and replacement metal gate. One of the problems' roots is not easy to etch the poly gate with a high aspect ratio [39]. Charging and micro-loading of etching results in variable  $L_g$ . An over-etch process is needed to clean the poly residual, and to remove the offset spacers on the fin-sidewalls [40,41]. Unfortunately, both these over-etchings result in damages of the Si fins. A remarkable Si loss may occur after wet cleaning and the solution has to be more diluted and should be used at low temperatures. Therefore, the dry and wet etching need more attention to be optimized to produce 3D gates with minimum  $L_g$  variation and Si loss in fins.

The patterning of fins is performed by SADP [42]. In this process, the depth of fin etching is usually determined by time. Meanwhile, the fins located at the edge of the wafer may show larger profile variation compared to those in the middle. To obtain uniform fin dimensions, dummy features could be used [43]. In this case, some dummy fins are necessary to be cut at the pitch. It is important to mention that, when the fin pitch shrinks and becomes compatible to the overlay limit, cutting fins becomes more difficult. Other steps of the FinFET's process, e.g., fin isolation by STI and channel-stopper doping

become more challenging, because the tighter pitch makes it more difficult to control the STI profile as well as doping variation.

In conclusion, in order to maintain the integrity of fins with a high aspect ratio is a challenging task [32]. The dry etching of fins is not a straight forward task because of the 3D topography. Thus, a plasma pulsing scheme is viable to decrease Si loss [39]. In a similar way, the oxidation of fins is a non-uniform process and it is faster at corner and tip areas.

One of the important issues in the FinFETs process is doping the fins [44,45]. A conformal doping profile in the S/D and extension regions has to be performed to create uniform carrier conduction in the fin-channel. The tight pitch of the fins restricts the incident beam angle in ion implantation (I/I), and may result in shadowing neighboring fins.

During the I/I, the Si fins become amorphous and, later, an annealing treatment is applied for re-crystallization. Unfortunately, this thermal treatment usually leads to poor dopant activation and formation of defects [44]. The poor fin quality has strong impact on the epitaxial quality of SiGe in S/D epitaxy as well as contact resistance in those regions. An increase of Si wafer temperature during I/I could be an appropriate solution to decrease the amorphous depth and fin damage [44,45]. Several reports have presented different innovative doping methods. Solid-source doping, molecular monolayer doping, and conformal plasma doping can improve the doping profile.

#### 5. SiGe Epitaxy of Nano-Scaled Transistors

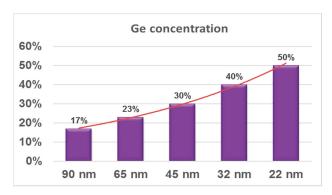

SiGe was integrated in S/D regions as stressor material for the first time in the 90-nm technology node to induce uniaxial strain in the channel region. Selective epitaxy growth (SEG) of SiGe was applied to fill out the recessed S/D regions. The advantage of uniaxial strain to the biaxial one is higher carrier mobility even for high electric fields. The embedded SiGe in S/D regions has been continuously increased from 19% to 45% when the transistors were miniaturized from 90-nm to 22-nm nodes [46–50]. In a 45-nm node, the shape of recess in S/D regions was modified from a round shape to sigma shape in order to further increase the SiGe strain since the layers could be located closer to the channel [51–53].

Beyond the 22-nm node (3D transistors), the SiGe layers are being grown on the Si fin to raise the S/D regions. The summary of Ge contents in S/D regions for different technology nodes is shown in Figure 9.

**Figure 9.** Ge contents in S/D for different technology nodes.

The SEG of SiGe on Si-Fin and nanowires has its own complexity and challenges. The SiGe growth may suffer from a series of problems: facet formation [54,55], defects, micro-loading, non-uniform strain distribution, surface roughness, and the pattern dependency effect [56–60]. Among those problems, the pattern dependency effect occurs when the density and size of the transistor vary in a chip. The reason for the pattern dependency of SEG is mainly non-uniform consumption of reactant gas molecules when the exposed Si area varies in a chip. Hence, more careful optimization of the growth parameters

as well as redesigning chip layout for uniform exposed Si areas could create uniform gas consumption during epitaxy for a successful process [56–60].

Currently, there is a strong attitude to replace the Si channel with SiGe or Ge in FinFETs with a high aspect ratio. The idea behind is to terminate the formed defects close to the fins' sidewall during epitaxial growth. This method is also called high aspect ratio trapping (ART) and by using it, high-quality film in the vertical direction is obtained.

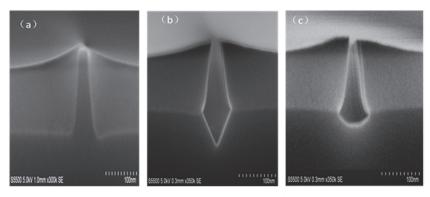

There are two methods to remove the Si and form the trench including the wet etch using Tetramethylammonium hydroxide (TMAH) and the vapor etch using HCl inside the CVD (chemical vapor deposition) chamber. The biggest difference between these two methods is the control of the silicon morphology at the bottom of the trench. A "V-shape" (111)-oriented of Si crystal is formed in the TMAH etch. Meanwhile, the HCl vapor method offers (311)-oriented facets of Si at the bottom of the trench, as shown in Figure 10a-c.

Figure 10. (a) Si fin covered with SiO<sub>2</sub> (b) removal of Si in the fin after wet-etch by TMAH and (c) HCl vapor etch [61].

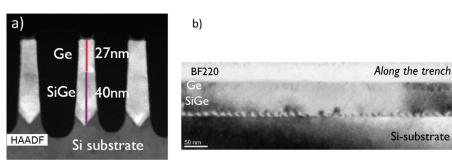

After filling the fins, the Chemical Mechanical Polish (CMP) technique is used to planarize the lateral overgrown part. Later, the STI oxide is removed by diluted HF solution to expose the Ge or SiGe fin. Figure 11 is the process scheme of SiGe or Ge SEG in the channel region in a FinFET structure. The process initiates to form a "V-shaped" Si recess and growth of the strain relaxed buffer (SRB) of Si<sub>0.3</sub>Ge<sub>0.7</sub> [62].

Figure 11. Cross-section TEM of strained Ge-cap/SRB Si<sub>0.3</sub>Ge<sub>0.7</sub> grown in an oxide trench and observed at (a) fin cut and (b) along the trench. The Si was removed by the wet etch prior to epitaxy [62].

Si-substrate

For a better control over a short channel effect, a more aggressive design e.g., the Gate-All-Around (GAA) structure is proposed to be integrated in the near future. For such transistors, SiGe or Ge are proposed to be grown as channel material for high mobility.

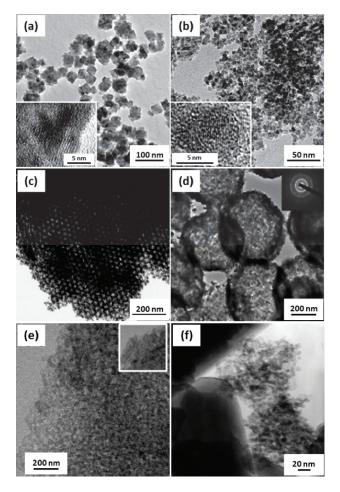

For the sub 10-nm technology node and beyond, the nano-wire device might be one of the promising candidates to obtain better gate control and lower leakage current [63–66]. In this approach, SiGe/Si multi-layers are grown where either SiGe or Si can be etched selectively to form channel regions for NWs. Figure 12 illustrates an image of a multilayer SiGe/Si structure with eight periods for forming vertical NWs.

Figure 12. HRSEM of a multilayer of the SiGe/Si structure with eight periods [66].

#### 6. Monolayer Doping

Monolayer doping (MLD) is a self-assembly doping process, which can be applied for doping NWs. This doping method is dominated by a surface chemical reaction between the semiconductor substrate and dopant-containing organic molecules [67–71]. Compared to conventional implantation, MLD introduces fewer defects into the substrates [72–75] and the dopant-containing molecules could attach uniformly on the surface, which results in a better conformal doping profile [73].

The basic procedure of MLD for nano-sheets is shown in Figure 13 [70]. However, the process could be easily used for NWs. The solution aqueous HF or  $NH_4F$  was first used to remove the native oxide on the surface and to obtain a hydrogen-terminated surface. Later, the substrate will be immersed into dopants containing liquids or solution of organic materials [70–75]. The organic material could be dopant atoms contained in alkene or alkyne. After that, a low temperature treatment or light irradiation will be adopted to enable a reaction, which is called hydrosilylation to form a covalent bond between the dopant containing molecules and Si atoms of the substrate's surface [70]. A conformal doped junction is formed by capping a thin  $SiO_2$  layer and high temperature RTP (rapid thermal processing) annealing to drive the dopant into the substrate.

Figure 13. Schematic of the monolayer doping process [70].

The tuning of doping concentration in the MLD process could be realized by either changing the amount of the dopant atom in a molecule (dopant enriched adsorbate) to improve the packing density or by mixing the dopant adsorbate with molecules that lack dopants to reduce the dopant quantity at the interface. The final junction doping level is always determined by dopant solid solubility of the dopant element [71,74].

#### 7. Plasma Doping

Plasma doping is a method based on when the dopants are adsorbed conformally on the surface of Si during the wafer, which is immersed into the plasma and dopant radicals in plasma. The uniform doping profile can be obtained by plasma doping and the damage to the surface can be suppressed by controlling the plasma energy. Recently, this technology has been improved by introducing ion energy decoupled plasma doping. This is based on a pretreatment to corporate decoupled plasma doping. In this way, the dopant level was remarkably raised and the surface damage could be decreased by heating the wafer during the process [68,75,76].

#### 8. High-k & Metal Gate (HKMG)

In downscaling of MOSFET, SiO<sub>2</sub> high-*k* material was eventually replaced with high-*k* material and the gate formation in the process flow was moved to the last in order to save the high-*k* integrity.

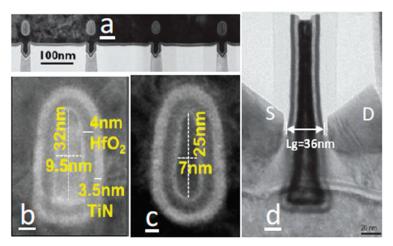

Table 1 summarizes the thickness of the materials in the gate stack (high-k dielectric and SiO $_{\rm x}$ ) from a 45-nm to a 5-nm technology node [77–80]. The thickness of SiO $_{\rm x}$  decreased dramatically from ~1.2 nm in a 45-nm node to ~0.6 nm in a 14-nm node. In a similar way, high-k dielectric (HfO $_{\rm 2}$ ) decreased from ~1.5 nm in a 45-nm node to ~1.2 nm in a 14-nm node. As a result, the equivalent oxide thickness of gate dielectric was decreased. In the 14-nm node CMOS, the thickness of SiO $_{\rm x}$  and HfO $_{\rm 2}$  have significantly decreased to ~0.6 and ~1.2 nm, compared to ~1.1 and ~1.0 nm for transistors in a 22-nm node. The 0.6 nm of SiO $_{\rm x}$  contains only four or five layers of atoms, which is very thin. In addition, for reliability of the gate stack, the thickness of SiO $_{\rm x}$  is an important issue and, consequently, cannot be further decreased. Therefore, it is expected that the thicknesses of SiO $_{\rm x}$  and HfO $_{\rm 2}$  would be considered ~0.5 nm and ~1.0 nm beyond a 5-nm node.

Therefore, for high-k dielectric gate stack beyond the 5nm CMOS, almost the same gate stack (HfO<sub>2</sub> and SiO<sub>x</sub>) will be built and the thickness of these two materials will be nearly unchanged compared with the 14-nm technology node. This is due to the direct tunneling current, which increases exponentially with thinner film thickness.

| Technology Nodes  | Film Thickness (nm) |        |         |      |  |

|-------------------|---------------------|--------|---------|------|--|

| recimology rioues | Thermal Oxide       | High-k | TiAl(N) | TiN  |  |

| 45 nm             | ~1.2                | ~1.5   | ~2      | ~2.1 |  |

| 32 nm             | ~1.2                | ~1.1   | ~1.7    | ~2   |  |

| 22 nm             | ~1.1                | ~1.0   | ~1.2    | ~1.4 |  |

| 14 nm             | ~0.6                | ~1.2   | ~1.2    | ~1.4 |  |

| 5 nm              | ~0.5                | ~1.0   | ~1.0    | ~1.2 |  |

**Table 1.** Material selection of high-*k* dielectric and metal gate from 45-nm to 5-nm nodes.

For the metal-gate, the N metal for NMOSFET (N-type metal-oxide-semiconductor field effect transistor) is still TiAl-based material, and the P metal for PMOSFET (P-type metal-oxide-semiconductor field effect transistor) is TiN. The work function metals for the NMOS (N-type metal-oxide-semiconductor) and PMOS (P-type metal-oxide-semiconductor) in 45 nm and 32 nm node were TiAlN and TiN, respectively [4,81]. Through the tremendous downscaling of CMOS starting from FinFET in a 22-nm node to the GAA (nanowire) structure, the electrostatic gate control is improved. This decreases the requirement of the metal-gate work function [41].

For the GAA structure, the gate-fill is a challenging task, and this increases the requirement of further decreasing the metal-gate thicknesses. Beyond the 5-nm technology node, the thicknesses of the TiAl and TiN metals are expected to be  $\sim$ 1.0 nm and  $\sim$ 1.2 nm, respectively.

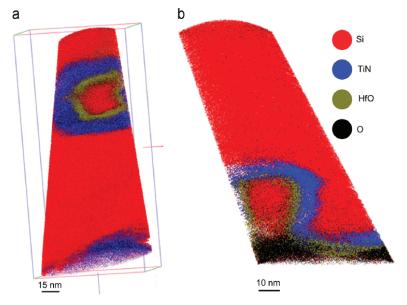

For transistors beyond the 5-nm node, the device performance cannot be further improved by optimizing gate stacks. The high-k dielectric and metal-gate are simply very thin and cannot be further decreased. For the GAA device structure, the deposition of HKMG requires precision in atomic levels. The ALD technique offers a good control for layer thickness of HfO<sub>2</sub> and TiN. However, for NMOSFET, it is relatively difficult to acquire the N-type work function metal due to the precursor limitation. In this field,  $TaC_y$  [82], TaCN [83], TiC [84],  $WC_{0.4}$  [85], and  $ErC_2$  [86] were studied for NMOSFET application. However, in most of these processes, plasma enhanced ALD (or PEALD) was used. To some extent, thermal ALD without plasma damage is more suitable for the metal gate. TiAlX films as the metal gate were developed by Chao et al. by the thermal ALD technique using TiCl<sub>4</sub>, TMA (Al(CH<sub>3</sub>)<sub>3</sub>), and NH<sub>3</sub>. It was demonstrated that NH<sub>3</sub> presence in the TiCl<sub>4</sub> and TMA reaction makes the film more like TiAlN(C) while its absence makes the film turn to TiAlC. The TiAlC film has a smaller effective work function than the TiAlN(C) film [87]. The effective work function can be tailored from 4.49 eV to 4.79 eV by tuning the process conditions [88]. By introducing the triethylaluminum (TEA) into the process, more Al-doping is obtained in the TiAlC film due the reaction of TEA with TiCl<sub>4</sub>. The effective work function of the TiAlC with TEA as a precursor can be tunable from 4.46 eV to 4.24 eV [89]. The deposition of TaAlC films using TMA and TEA has almost the same effective work function as TiAlC films grown by TMA and TEA separately, which provide more choices for metal gate selection [90,91]. The effective work function of different metals for NMOSFET are summarized in Table 2 [82–91].

High-*k* material can be applied for a more complicated transistor design, e.g., negative capacitance FET (NCFET). This type of transistor is a strong potential device beyond the 5-nm node CMOS. The reason for choosing NCFET is due to its dramatic improvement in a sub-threshold swing, which has compatible process flow with the conventional CMOS technology, and on-current enhancement [92]. The high-*k* materials suitable for NCFET are considered to be HfZrO and HfO<sub>2</sub> with a thickness below 5 nm.

| Metal            | Dep. Method | <b>Effective Work Function</b> | Ref. |

|------------------|-------------|--------------------------------|------|

| TaC <sub>v</sub> | PEALD       | 4.77–4.54 eV                   | [84] |

| TaCŃ             | PEALD       | 4.37 eV                        | [85] |

| TiC              | PEALD       | 5.24 eV-4.45 eV                | [86] |

| $WC_{0.4}$       | PEALD       | 4.2+/-0.1 eV                   | [87] |

| $ErC_2$          | ALD         | 3.9 eV                         | [88] |

| TiAlC            | thermal ALD | 4.79-4.49                      | [90] |

| TiAlC            | thermal ALD | 4.46-4.24                      | [91] |

| TaAlC            | thermal ALD | 4.74-4.49                      | [92] |

| TaAlC            | thermal ALD | 4.65-4.26                      | [93] |

|                  |             |                                |      |

**Table 2.** The effective work function of different metals grown by ALD for NMOSFET.

#### 9. Interconnections in CMOS

Tungsten (W) has excellent thermal stability, the highest melting point among all metals, and perfect resistance to electro-migration (EM). The tungsten plug has been used for metal interconnection in integrated circuits to connect different layers of metals to nano transistors. ALD has been widely used for deposition of tungsten. ALD W has been used as gate filling metal (HKMG-last) due to its properties for trench filling [93]. ALD W can be selectively deposited and this is important for advanced sub-10 nanometer transistors, which needs good alignment to underlying structures, and edge definition [94]. W films have an  $\alpha$ -phase and a  $\beta$ -phase with different morphologies and electrical properties. W films with an  $\alpha$ -phase have the lowest resistivity and an important role in the logic MOSFETs.

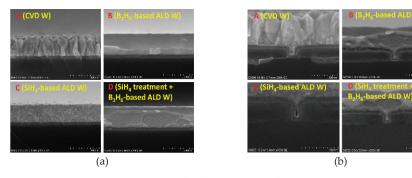

The common precursors used for ALD W are  $SiH_4$  [95–108],  $Si_2H_6$  [99], and  $B_2H_6$  [100–103]. Different precursors will form films with different phases. Qiang Xu et al. studied the adhesion, roughness, and pore filling ability of ALD W films using different growth methods and different precursors for the 22-nm technology node, as shown in Figure 14 [104]. The authors demonstrated that the roughness of the W film grown by the ALD technique is clearly better than that of CVD. The roughness of ALD films grown by  $SiH_4$  is better than that of the  $B_2H_6$  precursors. However, the filling performance of  $SiH_4$  is worse than that of  $B_2H_6$ .

**Figure 14.** Cross-sectional SEM images of W films grown in different conditions: (a) on blank wafers and (b) trenches filling capacity [104].

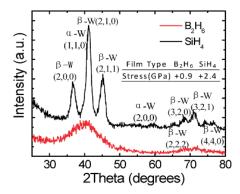

In order to further understand the internal morphology of the ALD W film, Wang et al. measured the morphology of these films by using the XRD technique. It was found that there were two kinds of crystalline phases in the ALD W films grown by  $SiH_4$  as precursors, while the films grown with  $B_2H_6$  were amorphous, as shown in Figure 15 [98].

Figure 15. XRD spectra of ALD W using  $SiH_4$  and  $B_2H_6$  and calculated stress data on a blank substrate [98].

In integrated circuits, ALD W with the  $\alpha$ -phase is commonly used for metal interconnection or electrode filling. One way to grow tungsten films with  $\alpha$ -phase on SiO<sub>2</sub> is to use WF<sub>6</sub> as a precursor and H using hot-wire (HW) assisted atomic layer deposition (HWALD) [105]. Kim et al. demonstrated that tungsten films using B<sub>2</sub>H<sub>6</sub> and WF<sub>6</sub> precursors create large grain size  $\alpha$ -phase tungsten at 450 °C. Meanwhile, at 395 °C and applying a low flow rate of B<sub>2</sub>H<sub>6</sub>, smaller grains could be obtained [106].

The initial nucleation process in the growth of ALD has a great influence on the state of the subsequent films. The main factor affecting the nucleation of ALD is the surface active site density. For example, in the study of selective ALD deposition, it was found that hydroxyl bonds were formed on the surface of  $SiO_2$  after wet cleaning, which resulted in the nucleation of  $SiH_4$  and  $WF_6$  on the surface of  $SiO_2$  [94]. However, the nucleation is greatly delayed after the removal of surface hydroxyl groups by heating or using a precursor, which interact with the surface to change the surface characteristics. For example, when  $B_2H_6$  and  $WF_6$  are used as precursors, pretreatment with  $B_2H_6$  accelerates nucleation. At the same time, the resistivity of the film is reduced.

F.H. Fabreguette presented the Quartz crystal microbalance study of the tungsten atomic layer deposition using WF<sub>6</sub> and Si<sub>2</sub>H<sub>6</sub>. This work found that the growth rate of ALD W was weakly temperature-dependent with an activation energy of 1.5  $\pm$ 0.1 kcal/mol at T < 250 °C and a lower activation energy of 0.6  $\pm$  0.3 kcal/mol at T > 275 °C [99].

At present, there are few research studies on the theory and interfacial states of ALD W. It is a valuable research direction to study the selective deposition on the basis of interfacial states and the formation mechanism for different crystal phases of W in the future. In the aspect of the device application, the process of preventing the diffusion of the F atom and the B atom through the TiN/Ti layer is also a valuable research direction in the integrated circuit.

#### 10. Stressors SiN<sub>x</sub> Contact Etch Stop Layer (CESL) Technology

After integration of the SiGe stressor material in MOSFETs, a large effort was spent to find new methods to increase the strain amount. Among the various methods, stress liner technology, which is based on the  $\mathrm{SiN}_{x}$  contact etch stop layer (CESL) received more attention. The strain in these films could be tuned from highly tensile to highly compressive. The stressed nitride contact liners were incorporated into a high performance CMOS flow. This CESL approach resulted in N-FET/P-FET effective drive current enhancement of 15%/32% and saturated drive current enhancement of 11%/20%. In these transistors, a significant enhancement of 60% was achieved in whole mobility without using SiGe [107].

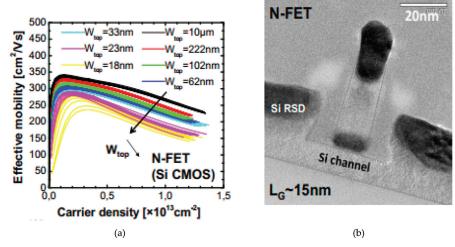

Another example is shown in Figure 16a,b where the CESL was used in  $\Omega$ -gate CMOS NWs with N-FET. The carrier mobility of transistors lied in a range of 250 to 350 cm<sup>2</sup>/Vs for different gate widths [108].

Figure 16. (a) Electron effective mobility in NFET and (b) TEM images  $\Omega$ -Gate CMOS NW transistors for N-FET [108].

#### 10.1. High Tensile Stress CESL

Many growth techniques have been applied to deposit high tensile  $SiN_x$ , e.g., LPCVD (low pressure chemical vapor deposition), ALD, and PECVD (plasma enhanced chemical vapor deposition). It is known that  $Si_3N_4$  films produced by the LPCVD technique possess high tensile stress of 2 Gpa. However, the relatively high thermal process makes the process not compatible with Ni silicide [109]. Therefore, PECVD technology with a low thermal budget process was taken as the best choice to deposit CESL [110].

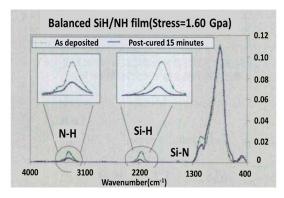

Unfortunately, the hydrogen in PECVD nitride film could not have been pushed out, which pulled down the film tensile stress to about 1 Gpa [111]. There are various reports that demonstrate methods. Plasma treatment and the ultraviolet thermal process (UVTP) can enhance the tensile stress. The latter method breaks Si-H and N-H bonds and pushes out H molecules. This method meets the demand of both high tensile stress, a low thermal budget, and stress amount as high as 1.7 Gpa can be obtained (see Figure 17).

Figure 17. Tensile stress change with a UV cure.

#### 10.2. High Compressive Stress CESL

In order to make high compressive stress CESL, both the RF power source and diluted gas have to be tuned. It is known that the compressive stress has a strong relationship with which a type of diluted gas is used. For example, the compressive value is as low as  $\sim$ 1.2 Gpa when nitrogen is used as diluted gas whereas a mixture of argon and nitrogen could highly increase the compressive stress to  $\sim$ 2.3 Gpa [112]. The compressive strain could be further increased to  $\sim$ 3.1 Gpa by using a diluted gas of hydrogen and argon mixture. The hydrogen reduces the energy loss during bombardment. To obtain further improvement, it is necessary to improve the film's elasticity modulus by applying the carbon element, which could impel hydrogen volatilize (less hydrogen and higher compressive stress). In this case, the SiH<sub>4</sub> precursor has to be replaced with TMS (tetramethylsilane), which contain a carbon element and compressive stress could reach close to 3.5 Gpa.

#### 11. Etching Evolution

Miniaturizing the transistor according to the principles shown in Figure 2 occurred when equivalent oxide thickness (EOT), transistor gate length, and transistor width were scaled down by a constant factor. However, this trend is followed very differently when the CMOS scaling focuses more on low voltages and low power consumption. By entering the 10-nm technology node, the silicon channel is being gradually replaced with silicon-germanium (SiGe), germanium (Ge), or III-V materials because they have remarkably higher carrier mobility [113]. For example,  $40,000 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  for InGaAs [114] (for electrons) and  $1900 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  for Ge [115] (for holes) compared to  $1400 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  for electrons and  $450 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  for holes in silicon [116]. Not only is the channel material changed, but the transistor shape is changed from a simple fin-like shape to a lateral gate all around (LGAA) or vertical gate all around (VGAA) in order to obtain transport control through the channel region. It means that the fabrication of state-of-art transistors need to be modified.

In this case, a dummy gate poly crystalline was initially formed as a replacement metal gate (RMG) as well as silicon dioxide, which was deposited as dummy gate oxide to give the green light for all the high temperature-annealing processes [117]. Eventually, the gate was removed by a wet process using none metal alkaline solutions. The merits of RMG are first addressed to avoid crystallizations of the high-*k* dielectric during the rapid thermal annealing (RTA) process for dopants activation, which may increase leakage current of the gates [117]. Second, it avoids the chemical reactions between the metal-gate and the high-*k* in RTA processes [118] or it avoids the boron diffusion into high-*k* [118,119].

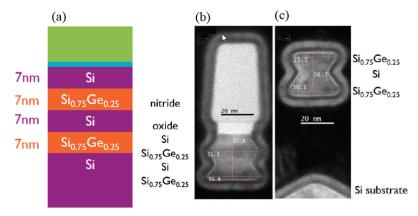

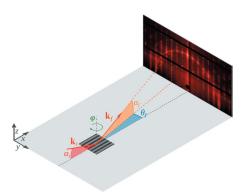

The RMG process is still used and will be applied for the 7 nm and 5 nm technology node, where the sacrificial material is Si and will be selectively removed from the SiGe channel [120]. The exponential decrease in the alkaline etch rate of SiGe with increasing Ge content enables the selective removal of Si to  $Si_{0.75}Ge_{0.25}$ . [121–124]. Alkaline etching of Si has been extensively studied and is well understood [125,126]. The etch rate in Si (001) and (110) directions is remarkably faster compared to the Si (111) crystallographic planes [127]. As shown in Figure 18, the selective etching of Si to SiGe was performed at a TMAH 5% solution at 60 °C. In both pictures, the Si underneath material of the NW stack is completely removed. The 7-nm thick Si layers, which are sandwiched in between the  $Si_{0.75}Ge_{0.25}NWs$  are removed until the (111) limiting planes are formed.

In fabricating the SiGe NWs from the Si/SiGe stack, the conventional alkaline Si etchant such as TMAH (aq) poorly removes the Si sacrificial layer. The selectivity of the Si-vs-SiGe etch is only marginal [128,129]. A surface modifier is employed in ACT® SG-201, which improves the relative etch rates of Si (110) and Si (111) orientations. This solution results in etching selectivity of Si (110)/Si (100) in the range of 1 to 2.5 and Si (111)/Si (100) of about 0.5 or above. By a combination of the Si surface modifier and an effective SiGe corrosion inhibitor in ACT® SG-201, the selectivity of Si (111)/SiGe 25% is significantly improved as compared to the conventional Si etchants. Consequently, ACT® SG-201 is more efficient in removing the sacrificial Si layer in the Si/SiGe stack [130]. The reduced Si etch rate anisotropy in combination with an effective SiGe corrosion inhibitor prevents SiGe loss during the NW release [130].

Figure 18. (a) Schematic picture of a stack of  $\mathrm{Si}_{0.75}\mathrm{Ge}_{0.25}/\mathrm{Si}$  NW used for selective etch and TEM across a section of 30-nm wide Si- $\mathrm{Si}_{0.75}\mathrm{Ge}_{0.25}$  NWs after Si selectively etched (b) in TMAH 5% and (c) without the oxide-nitride HM [127].

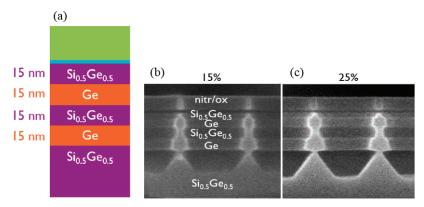

The sacrificial material is SiGe and will be selectively removed from the Ge channel [131–133]. For example, SiGe can be selectively etched to Ge in diluted TMAH 5–25% at 90 °C. Figure 19 shows the  $Si_{0.5}Ge_{0.5}/Ge$  NWs after selective etching in TMAH 15 or 25%. The Ge NW is not etched in the solution while the  $Si_{0.5}Ge_{0.5}$  and substrate are etched anisotropically. The undercut for the 25% TMAH solution is more than for the 15% solution one. The etch rate of the (001), (110), and (111) crystallographic planes of  $Si_{0.5}Ge_{0.5}$  were estimated from these cross-sectional scanning electron microscopy (XSEM) images (see Figure 19b,c). The etch rate of the different planes is decreasing in magnitude from (001) to (111) to (110) plane. If the selective removal of Ge is the goal, then oxidizing solutions, e.g., using SC1 solutions can be used due to the high solubility of the Ge-oxide [122,134].

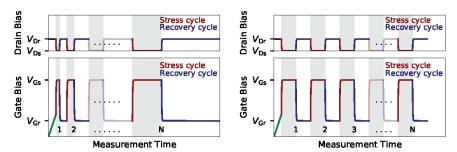

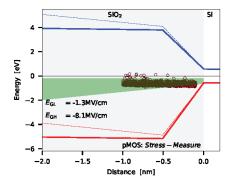

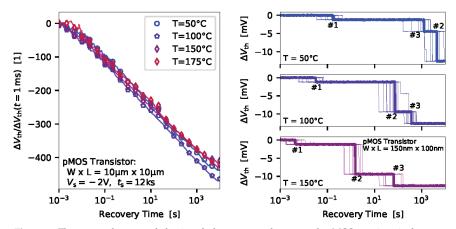

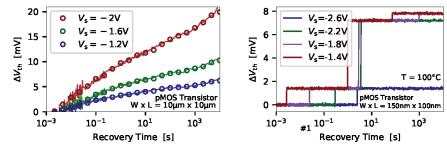

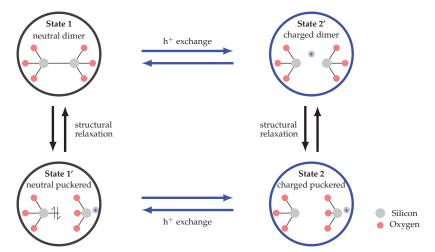

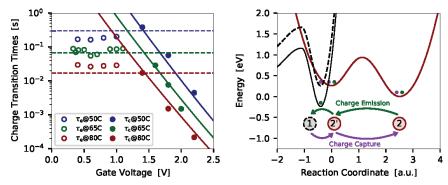

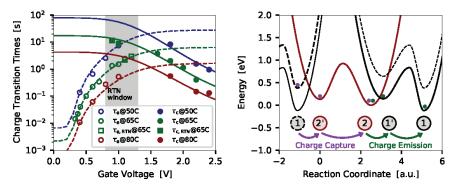

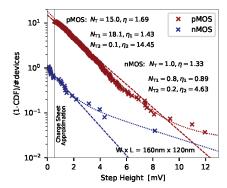

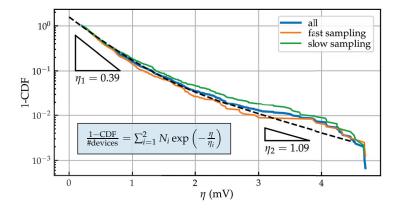

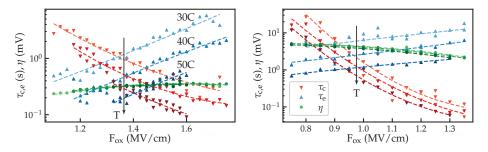

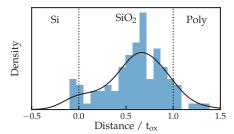

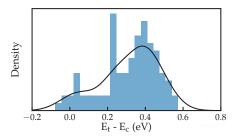

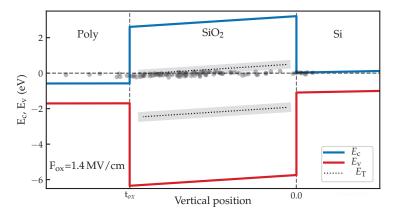

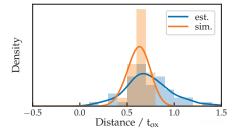

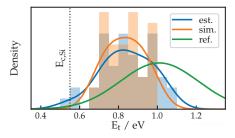

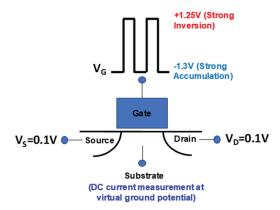

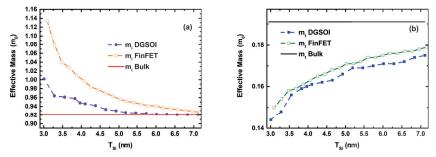

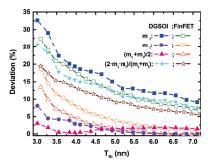

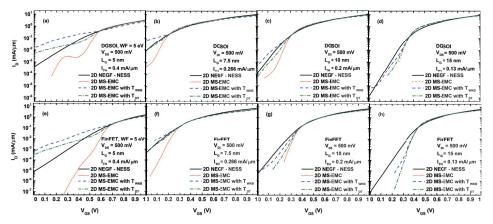

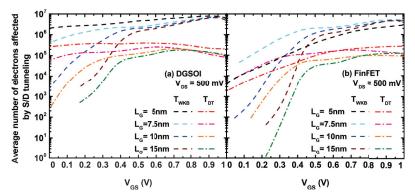

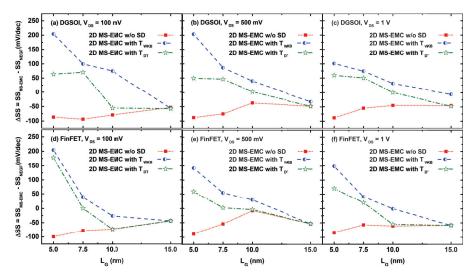

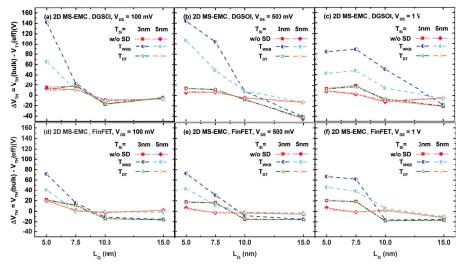

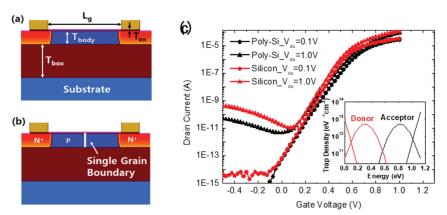

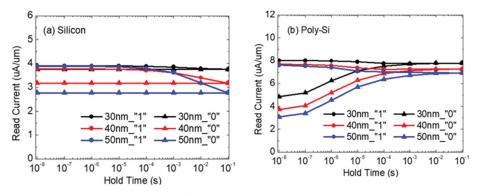

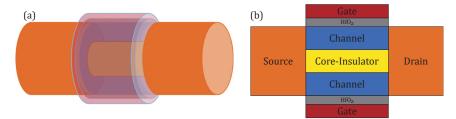

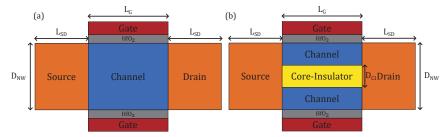

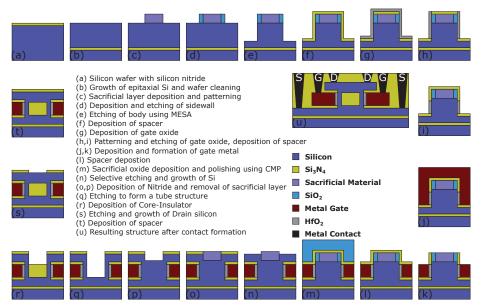

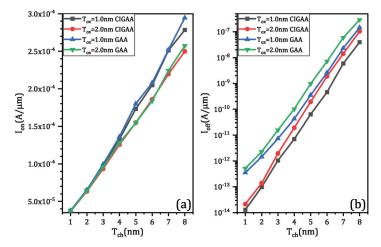

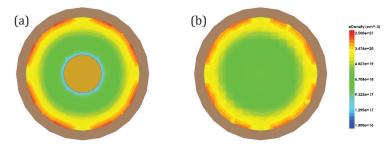

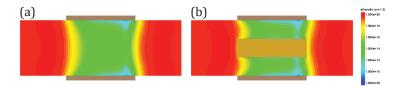

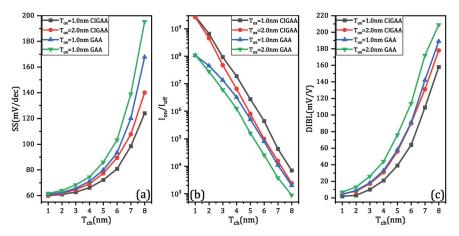

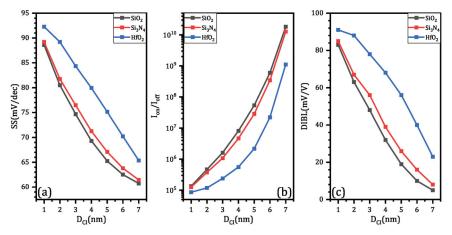

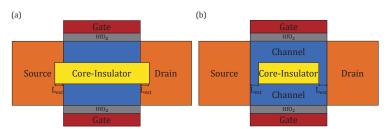

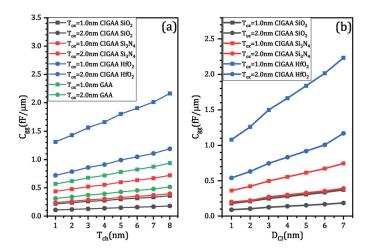

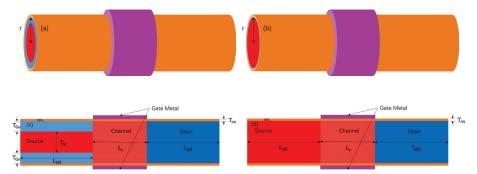

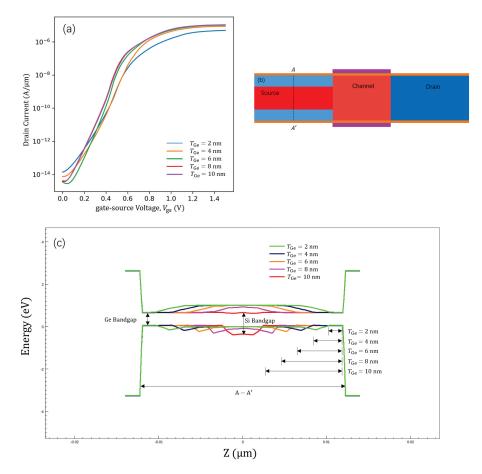

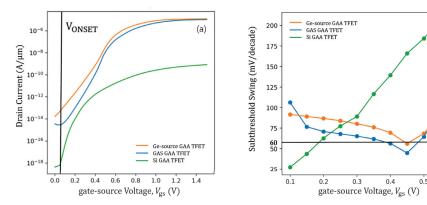

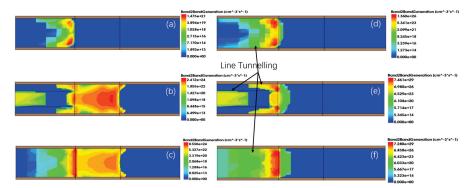

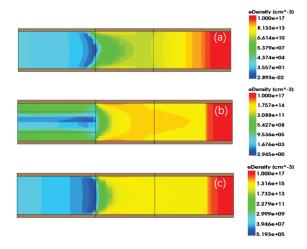

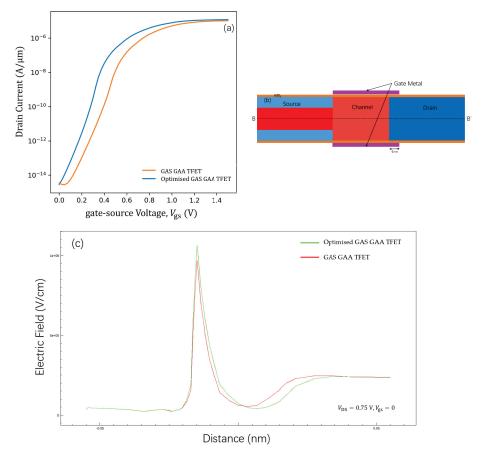

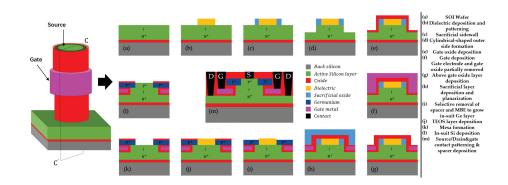

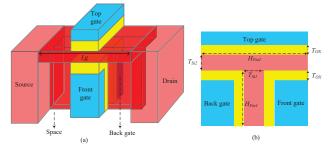

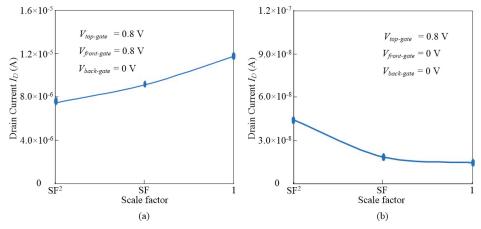

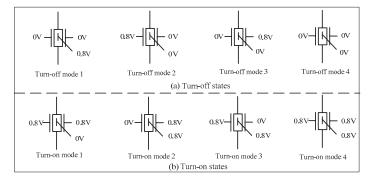

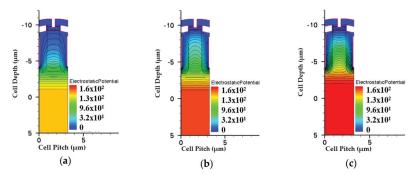

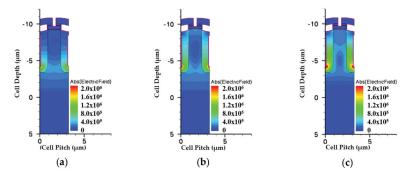

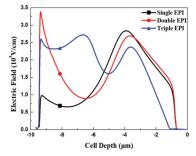

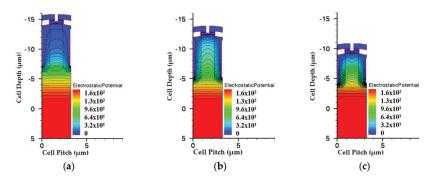

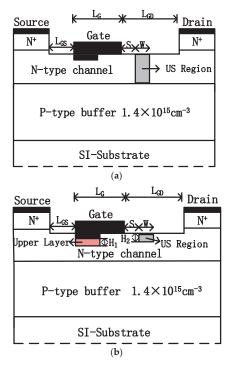

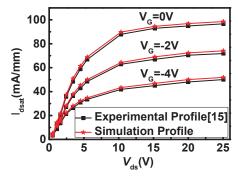

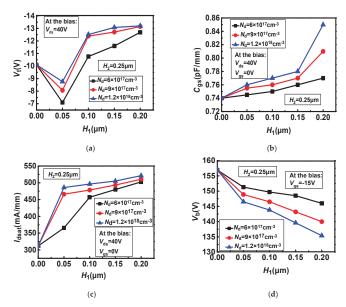

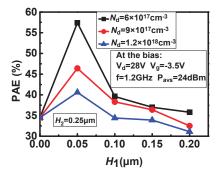

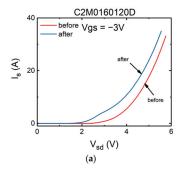

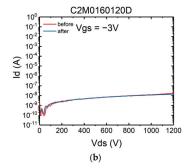

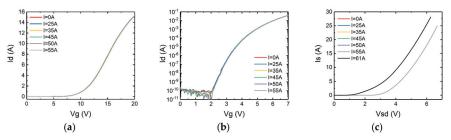

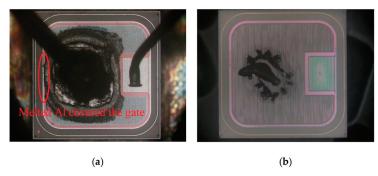

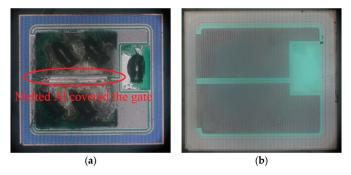

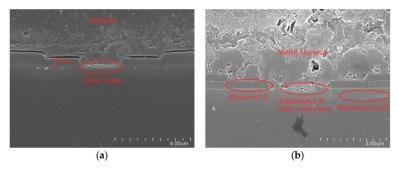

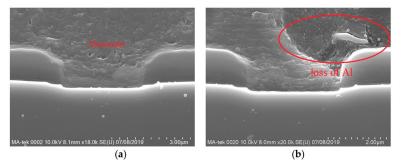

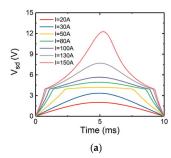

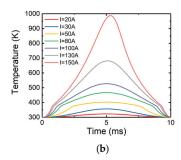

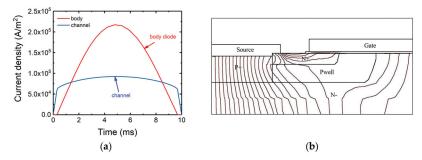

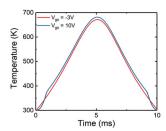

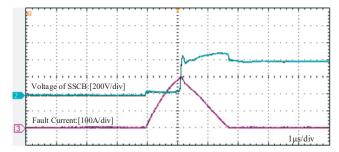

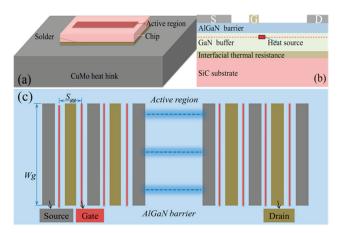

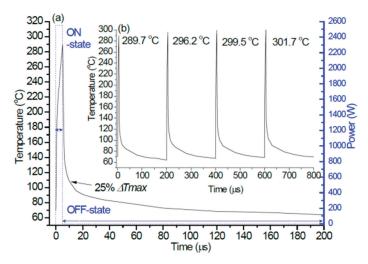

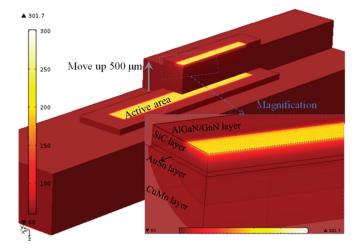

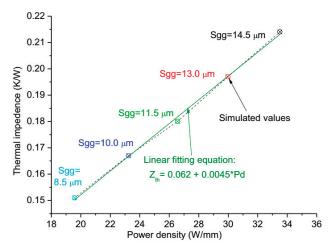

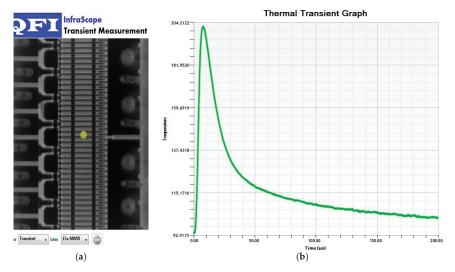

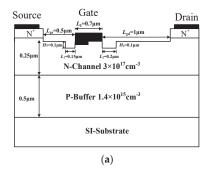

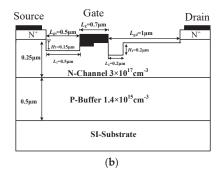

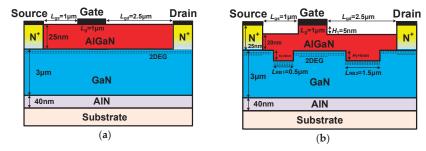

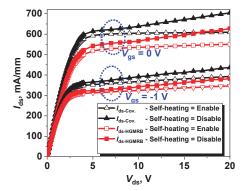

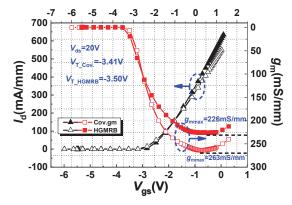

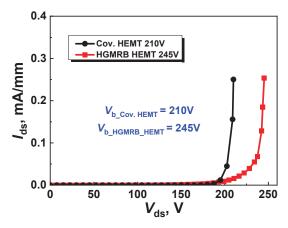

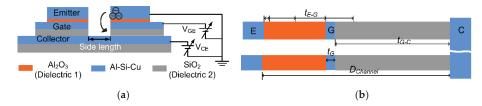

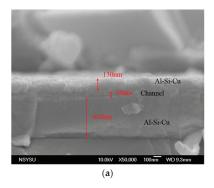

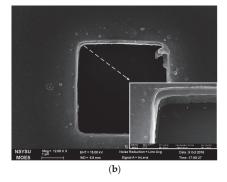

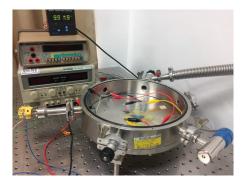

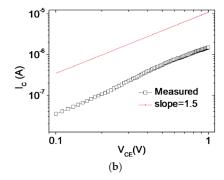

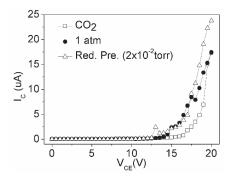

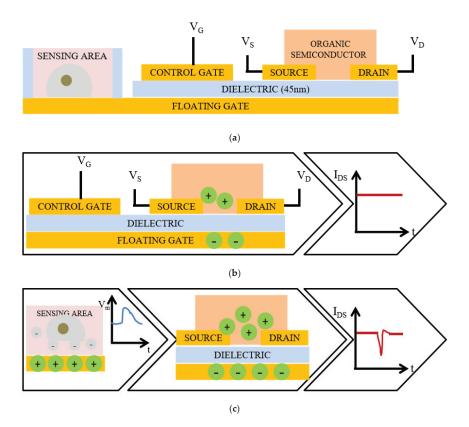

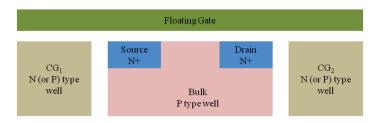

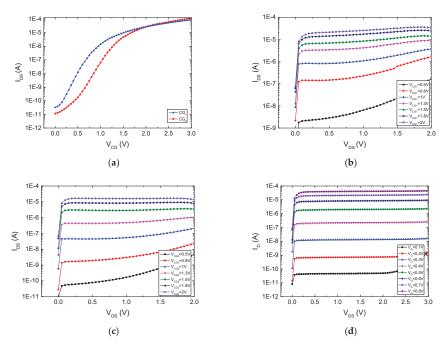

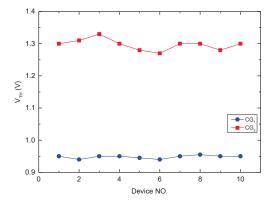

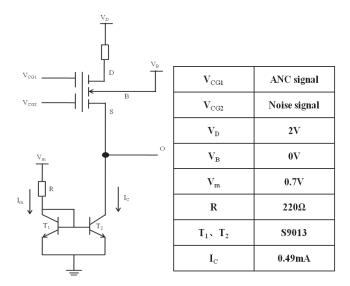

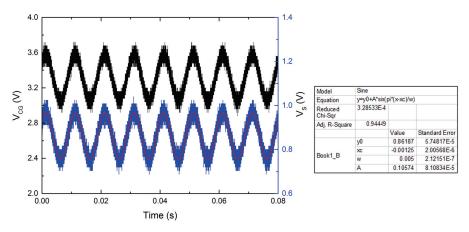

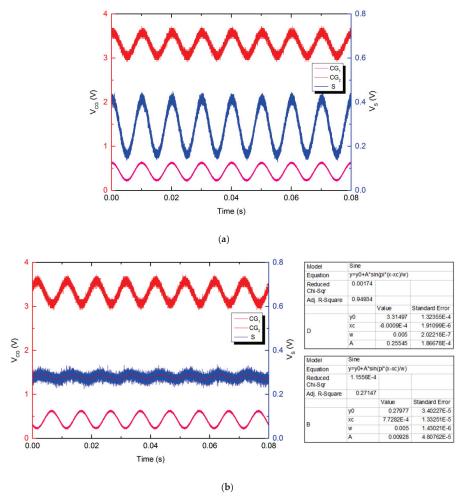

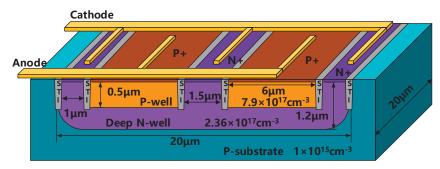

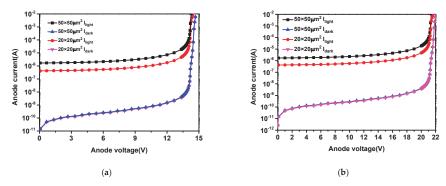

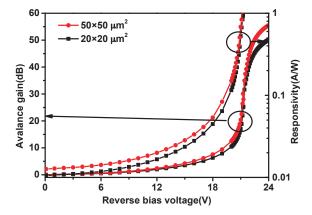

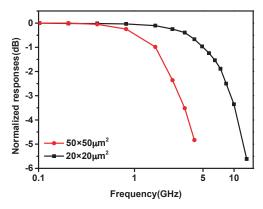

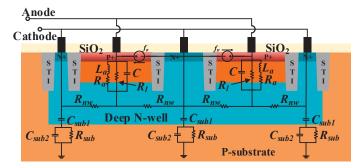

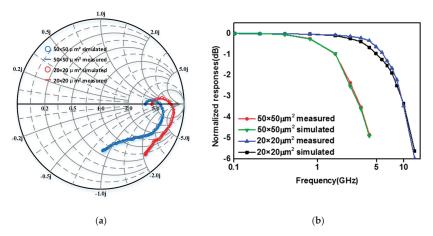

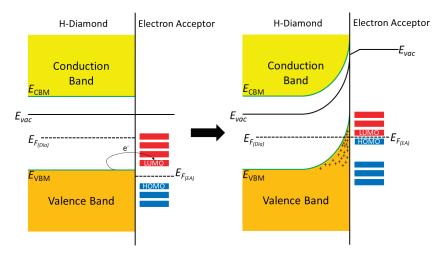

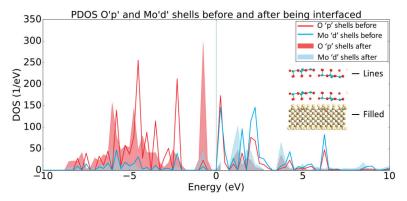

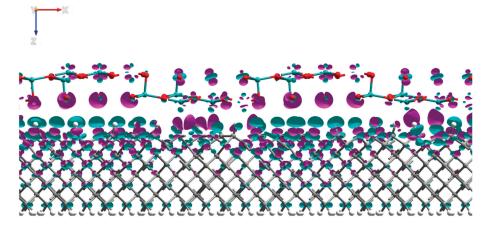

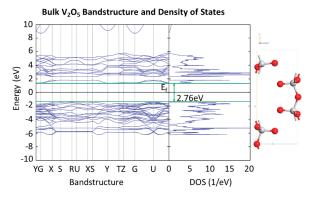

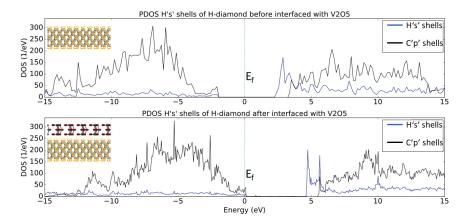

**Figure 19.** (a) Pictorial description of the  $Si_{0.5}Ge_{0.5}/Ge$  NW stacks used for the selective etch test and SEM images of  $Si_{0.5}Ge_{0.5}$ -Ge NWs after selective etch for 10 seconds in TMAH with a concentration of (b) 15% and (c) 25% for 45 and 55 nm wide fins [127].