# Recent Advances in Thin Film Electronic Devices

Edited by

Chengyuan Dong

Printed Edition of the Special Issue Published in Micromachines

# **Recent Advances in Thin Film Electronic Devices**

## **Recent Advances in Thin Film Electronic Devices**

Editor

Chengyuan Dong

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

**Editor**

Chengyuan Dong

Department of Electronic

Engineering

Shanghai Jiao Tong

University

Shanghai

China

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Micromachines* (ISSN 2072-666X) (available at: www.mdpi.com/journal/micromachines/specialissues/Thin\_Film\_Electronic).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-5294-1 (Hbk) ISBN 978-3-0365-5293-4 (PDF)

© 2022 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

#### **Contents**

| About the Editor                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "Recent Advances in Thin Film Electronic Devices" i                                                                                                                                                                                           |

| Chengyuan Dong                                                                                                                                                                                                                                           |

| Editorial for the Special Issue on Recent Advances in Thin Film Electronic Devices                                                                                                                                                                       |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 1445, doi:10.3390/mi13091445                                                                                                                                                              |

| Julio C. Tinoco, Samuel A. Hernandez, María de la Luz Olvera, Magali Estrada, Rodolfo<br>García and Andrea G. Martinez-Lopez                                                                                                                             |

| Impact of the Semiconductor Defect Density on Solution-Processed Flexible Schottky Barrier Diodes                                                                                                                                                        |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 800, doi:10.3390/mi13050800                                                                                                                                                               |

| Zheng Zhu, Wei Cao, Xiaoming Huang, Zheng Shi, Dong Zhou and Weizong Xu<br>Analysis of Nitrogen-Doping Effect on Sub-Gap Density of States in a-IGZO TFTs by TCAD<br>Simulation                                                                          |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 617, doi:10.3390/mi13040617                                                                                                                                                               |

| Min-Kyeong Kim, Yang-Kyu Choi and Jun-Young Park                                                                                                                                                                                                         |

| Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs                                                                                                                                                         |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 124, doi:10.3390/mi13010124                                                                                                                                                               |

| Jia-Ying Chen, Xin-Gui Tang, Qiu-Xiang Liu, Yan-Ping Jiang, Wen-Min Zhong and Fang Luo<br>An Artificial Synapse Based on CsPbI3 Thin Film                                                                                                                |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 284, doi:10.3390/mi13020284                                                                                                                                                               |

| S. Selvendran, J. Divya, A. Sivanantha Raja, A. Sivasubramanian and Srikanth Itapu A Reconfigurable Surface-Plasmon-Based Filter/Sensor Using D-Shaped Photonic Crystal Fiber Reprinted from: <i>Micromachines</i> 2022, 13, 917, doi:10.3390/mi13060917 |

| Moisés do Amaral Amâncio, Yonny Romaguera-Barcelay, Robert Saraiva Matos, Marcelo<br>Amanajás Pires, Ariamna María Dip Gandarilla and Marcus Valério Botelho do Nascimento<br>et al.                                                                     |

| Effect of the Deposition Time on the Structural, 3D Vertical Growth, and Electrical Conductivity                                                                                                                                                         |

| Properties of Electrodeposited Anatase–Rutile Nanostructured Thin Films Reprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 1361, doi:10.3390/mi13081361                                                                                      |

| Nanhong Chen, Honglong Ning, Zhihao Liang, Xianzhe Liu, Xiaofeng Wang and Rihui Yao et al.                                                                                                                                                               |

| Application of Laser Treatment in MOS-TFT Active Layer Prepared by Solution Method Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 1496, doi:10.3390/mi12121496                                                                           |

| Wen Zhang, Zenghui Fan, Ao Shen and Chengyuan Dong Atmosphere Effect in Post-Annealing Treatments for Amorphous InGaZnO Thin-Film                                                                                                                        |

| Transistors with $SiO_x$ Passivation Layers<br>Reprinted from: <i>Micromachines</i> <b>2021</b> , <i>12</i> , 1551, doi:10.3390/mi12121551                                                                                                               |

|                                                                                                                                                                                                                                                          |

| Khwang-Sun Lee and Jun-Young Park N-Type Nanosheet FETs without Ground Plane Region for Process Simplification                                                                                                                                           |

| Reprinted from: <i>Micromachines</i> <b>2022</b> , 13, 432, doi:10.3390/mi13030432                                                                                                                                                                       |

| uping Ding and Jose M. Moran-Mirabal                                                          |    |

|-----------------------------------------------------------------------------------------------|----|

| ficient Multi-Material Structured Thin Film Transfer to Elastomers for Stretchable Electronic |    |

| evices                                                                                        |    |

| eprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 334, doi:10.3390/mi13020334     | 15 |

| -Ming Tzu, Shih-Hsien Hsu and Jung-Shun Chen                                                  |    |

| on-Contact Optical Detection of Foreign Materials Adhered to Color Filter and Thin-Film       |    |

| ansistor                                                                                      |    |

| eprinted from: <i>Micromachines</i> <b>2022</b> , <i>13</i> , 101, doi:10.3390/mi13010101     | 27 |

#### **About the Editor**

#### **Chengyuan Dong**

Chengyuan Dong, associate professor in Department of Electronic Engineering, Shanghai Jiao Tong University. He obtained a Ph.D. degree from Shanghai Jiao Tong University in 2003, and then served some FPD makers in China mainland until 2008. His current research interest is macroelectronics, including physics and fabrication of novel TFT devices, as well as design and application of macroelectronic circuits. Dr. Dong is a committee member in SID Beijing-Chapter and a Guest Editor for *Micromachines*.

## Preface to "Recent Advances in Thin Film Electronic Devices"

Thin film electronic devices have been becoming a hot topic with the rapid development of the related industries, such as flat panel display, flat panel sensors, energy devices, memories, and so on. Generally, the family of thin film electronic devices includes thin film transistors (TFTs), thin film solar cells (TFSCs), thin film sensors (TFSs), thin film memories (TFMs), and many other conventional and novel devices. Although these devices belong to different industrial fields, they share many common material physics, device theories, fabrication methods, and application fundamentals. Therefore, a collection of studies on these devices may broaden our knowledge about this advancing field and lead to some novel ideas about the related research works. Accordingly, the Special Issue "Recent Advances in Thin Film Electronic Devices" in *Micromachines*, the collection of this reprint, is an approach.

There are 1 editorial and 11 papers are included in this reprint. Device fundamentals, fabrication processes, and testing methods of thin film electronic devices are covered. The experimental data, simulation results, and theoretical analysis presented in these studies should push the advances in thin film electronic devices as well as the research activities employed by the researchers in this field.

Special thanks to Editor Tu and the other members of *Micromachines*! With their strong support, this reprint has become possible.

Chengyuan Dong *Editor*

Editorial

### Editorial for the Special Issue on Recent Advances in Thin Film Electronic Devices

Chengyuan Dong

Department of Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, China; cydong@sjtu.edu.cn

Thin film electronic devices have been attracting more and more attention because of their applications in many industry fields, such as in flat panel displays (FPDs), energy devices, sensors, memories, and so on [1–3]. From a fabrication point of view, thin film electronic devices can not only be prepared on rigid substrates (including glass, wafers, etc.) but also on flexible substrates (including polymers, paper, etc.); this makes give thin film electronic devices the potential to be used in some quickly advancing fields, such as the Internet of Things and medical electronics [4,5].

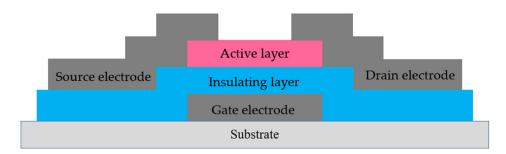

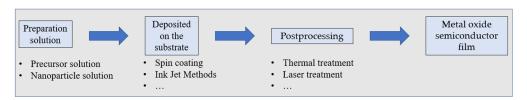

The family of thin film electronic devices includes thin film transistors (TFTs), thin film solar cells (TFSCs), thin film sensors (TFSs), thin film memories (TFMs), and many other conventional and novel devices. To fabricate them, many advanced preparation methods, including magnetron sputtering, chemical vapor deposition (CVD), atomic layer deposition (ALD), lithography, dry etching, as well as solution methods, are employed. To improve the yield for mass productions, some effective testing methods are widely used.

This Special Issue comprises 11 original papers about recent advances in the research and development of thin film electronic devices. Specifically, three research fields are covered: device fundamentals (five papers), fabrication processes (five papers), and testing methods (one paper). These typical studies reveal the recent advances in thin film electronic devices, which are briefly summarized as follows.

Defect density dominates the electrical properties of semiconductor films and devices. In this Special Issue, J. C. Tinoco et al. investigated the impact of the semiconductor defect density on solution-processed flexible Schottky barrier diodes (SBDs) [6]. The simulation analysis and experimental measurements confirmed that it was necessary to consider the presence of a density of states in the semiconductor gap for standard SBDs to understand specific changes observed in their performance.

Nitrogen-doping is an effective method to improve the electrical performance and stability of amorphous InGaZnO (a-IGZO) TFTs. A technology computer-aided design (TCAD) simulation was employed to analyze the nitrogen-doping effect on sub-gap density of states in a-IGZO TFTs [7]. The numerical simulation results displayed that the interface trap states, bulk tail states, and deep-level sub-gap defect states originating from oxygen-vacancy-related defects might be effectively suppressed by an appropriate nitrogen-doping treatment.

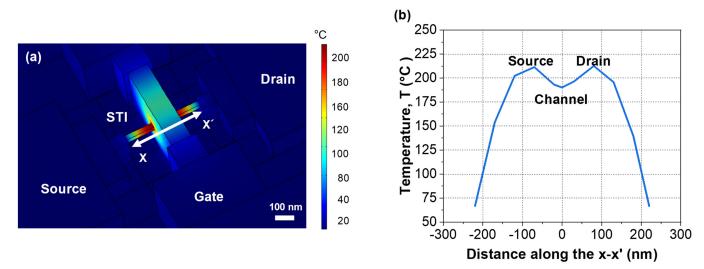

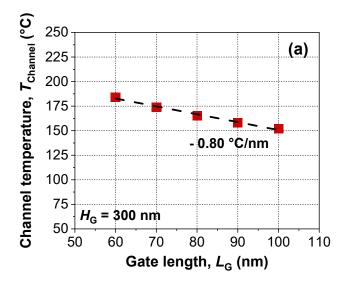

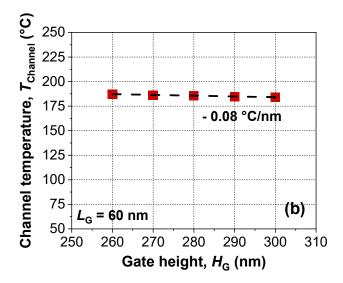

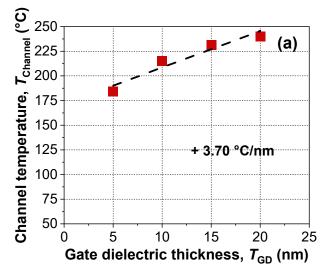

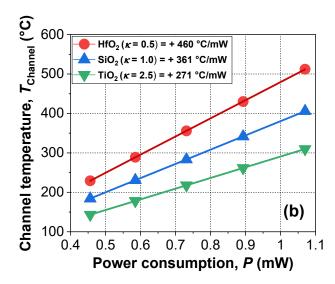

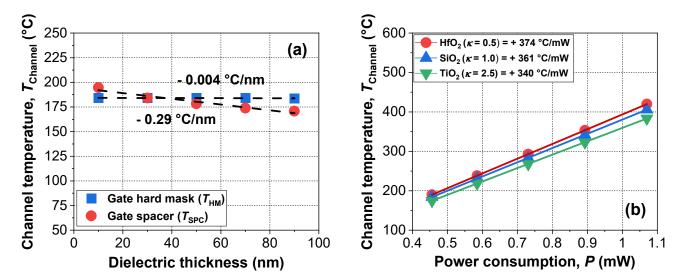

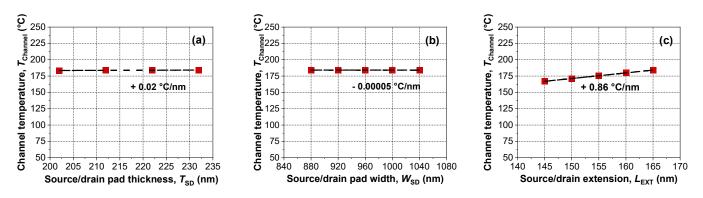

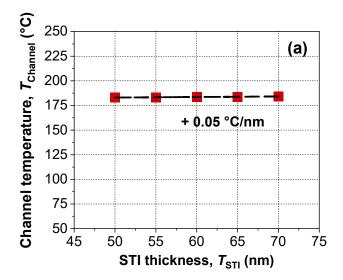

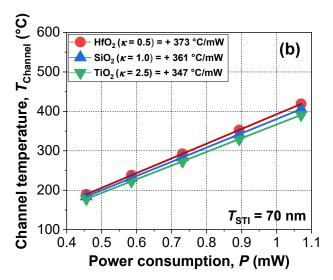

In addition to TFTs, the gate-all-around field-effect transistors (GAA FETs) were also simulated to find the mechanisms about reducing power with punch-through current annealing [8]. To maximize power efficiency during electro-thermal annealing, the application of gate module engineering was confirmed to be more suitable than the isolation or source drain modules.

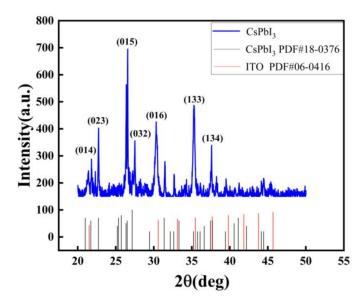

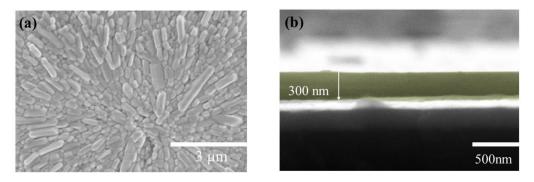

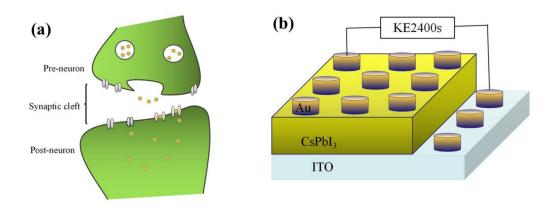

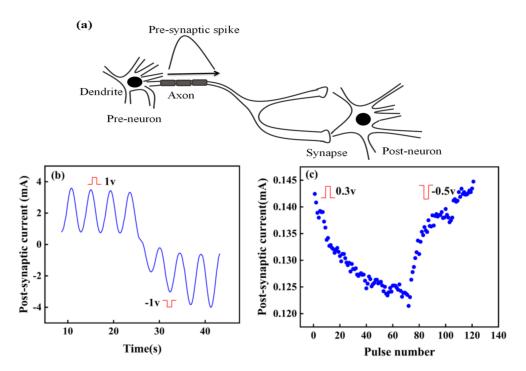

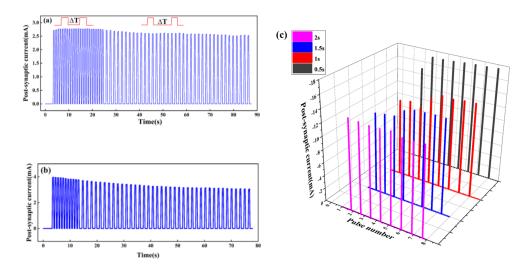

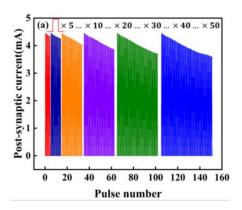

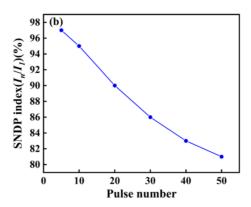

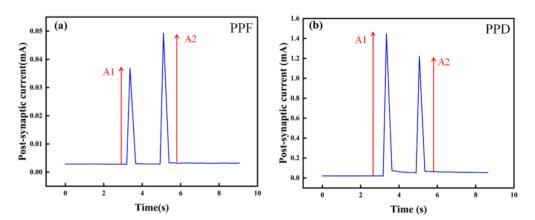

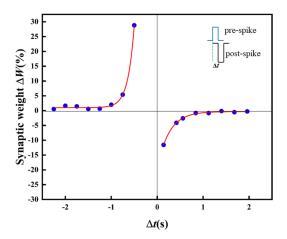

It is interesting that some novel functions could be realized by  $CsPbI_3$  thin films. J. Y. Chen et al. confirmed the learning and memory behavior similar to biological neurons in  $Au/CsPbI_3/ITO$  structure [9]; they also discussed the possibility of forming long-term memory in the device through changing input signals.

Citation: Dong, C. Editorial for the Special Issue on Recent Advances in Thin Film Electronic Devices. *Micromachines* **2022**, *13*, 1445. https://doi.org/10.3390/ mi13091445

Received: 29 August 2022 Accepted: 30 August 2022 Published: 1 September 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

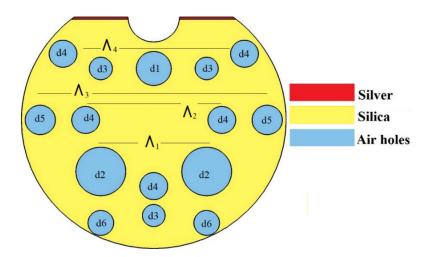

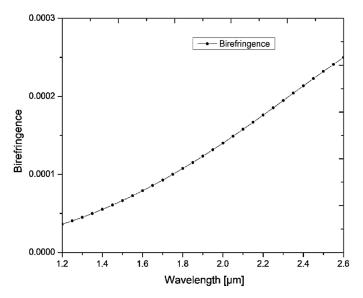

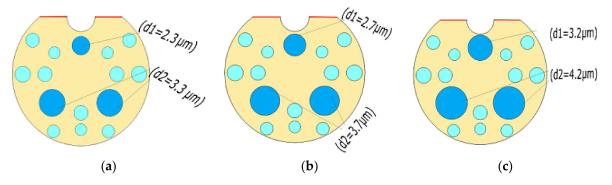

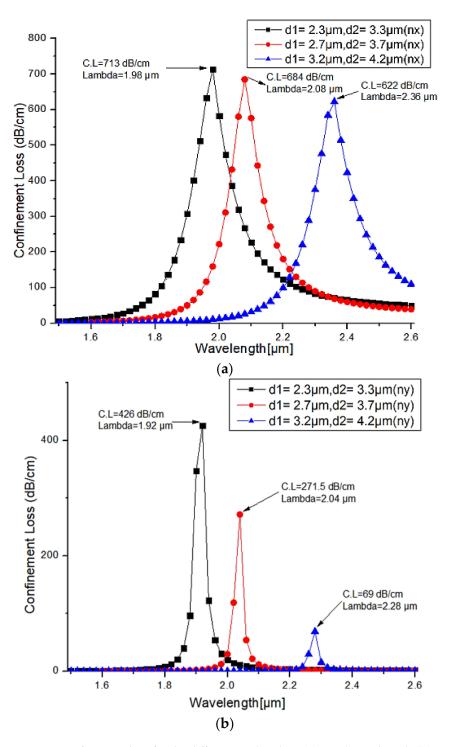

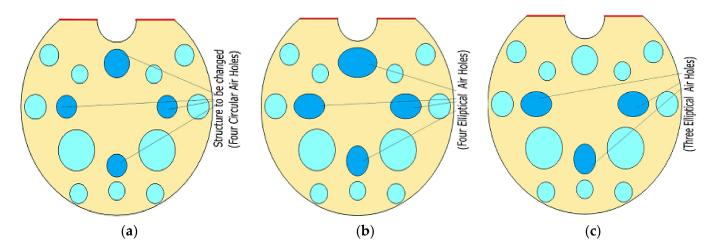

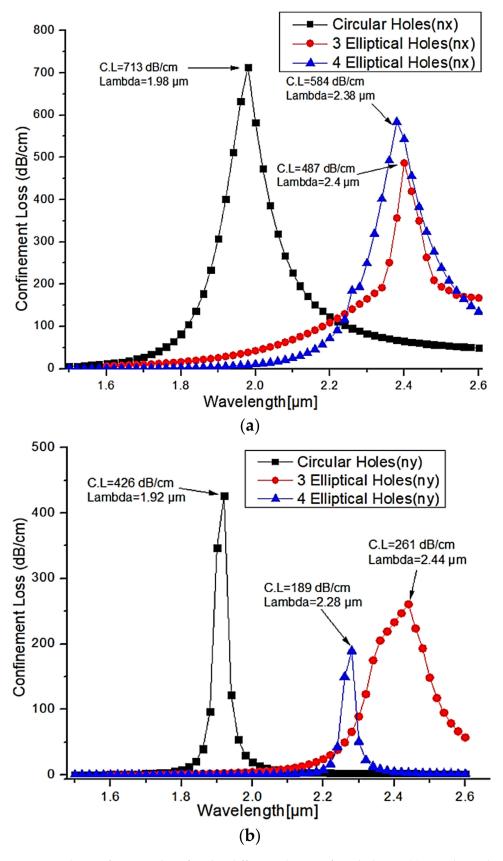

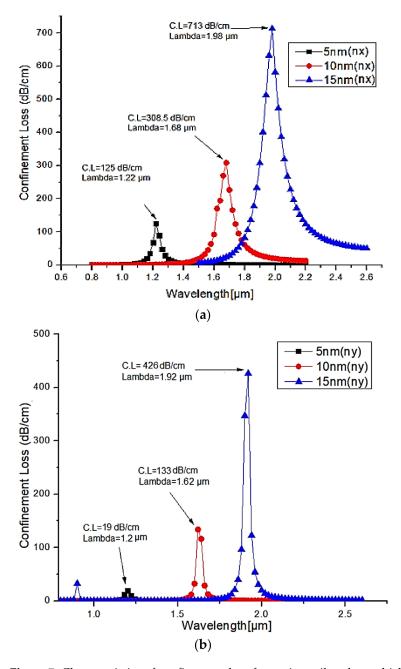

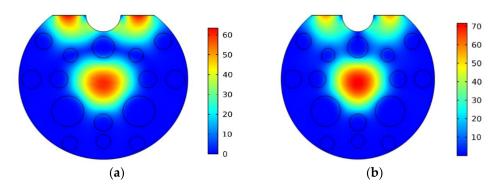

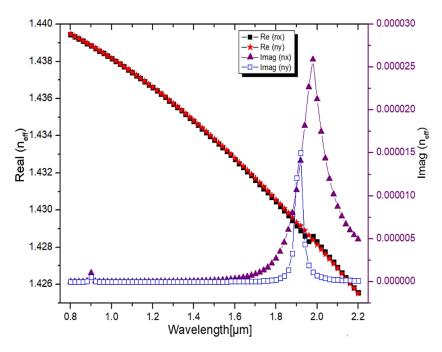

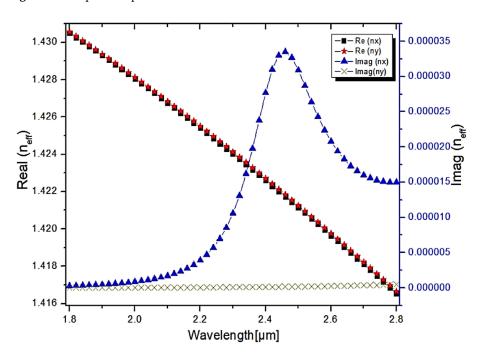

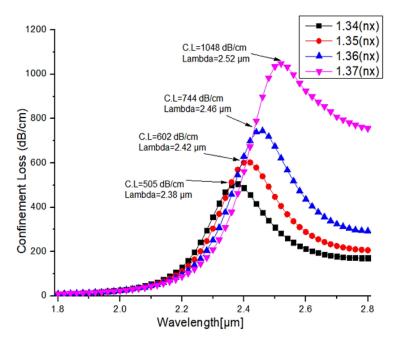

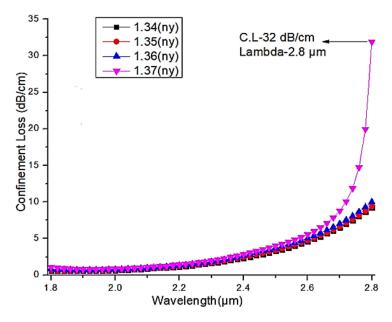

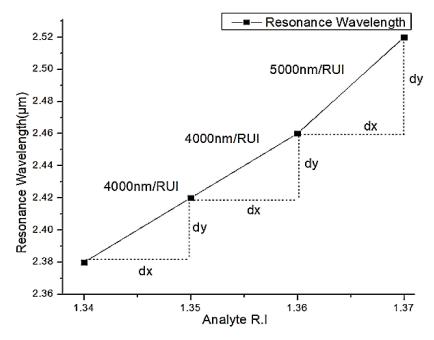

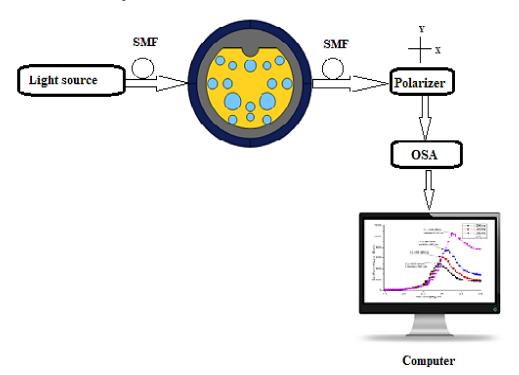

In recent years, many researchers have proposed novel photonic crystal fibers (PCF)-based polarization filters. Here, S. Selvendran et al. [10] used D-shaped PCF to form a reconfigurable surface-plasmon-based filter/sensor; they achieved a maximum confinement loss of about 713 dB/cm at the operating wavelength of 1.98  $\mu m$  in X-polarization by the surface plasmon effect.

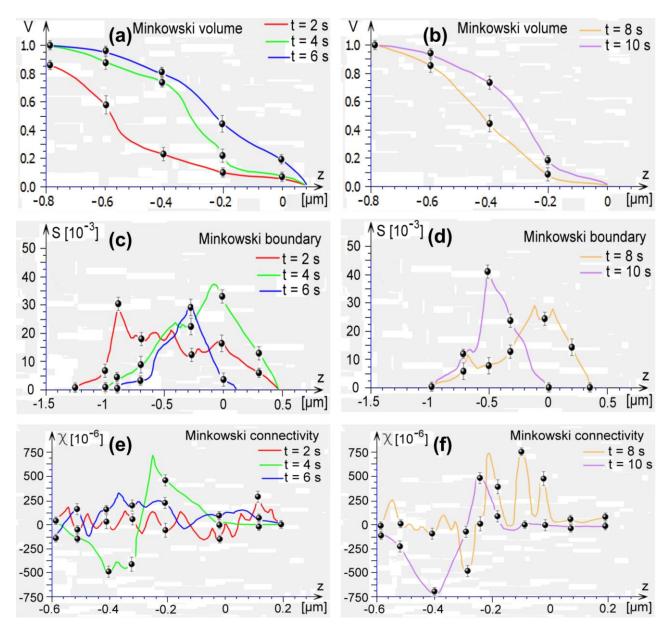

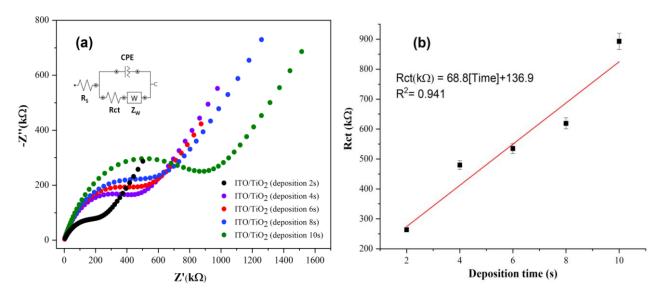

Generally, electrical properties of thin films are influenced by many processing conditions. The effect of the deposition time on the structural and 3D vertical growth and electrical conductivity properties of electrodeposited anatase-rutile nanostructured thin films was studied [11], proving that the deposition time during the electrophoretic experiment consistently evidently affected the structure, morphology, and electrical conductivity of the corresponding films.

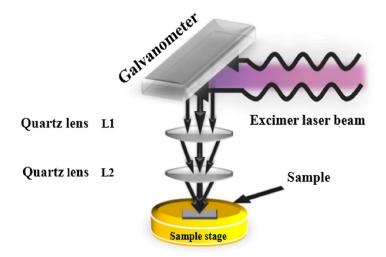

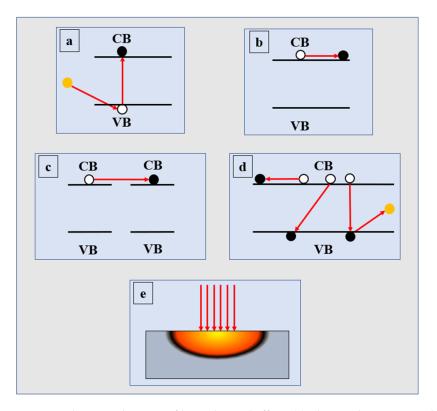

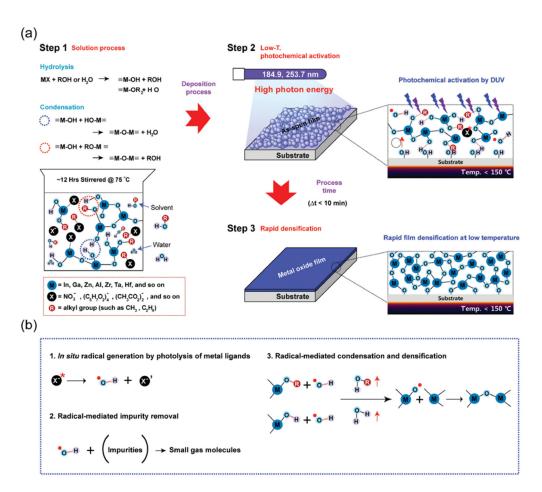

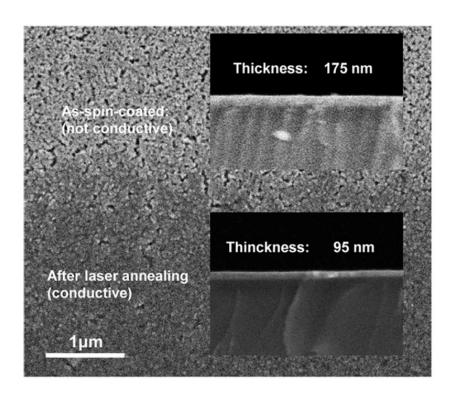

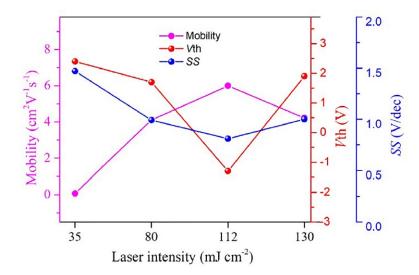

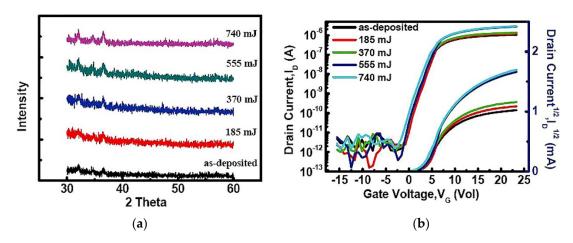

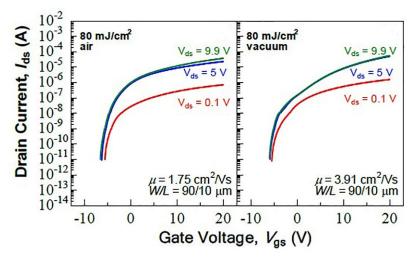

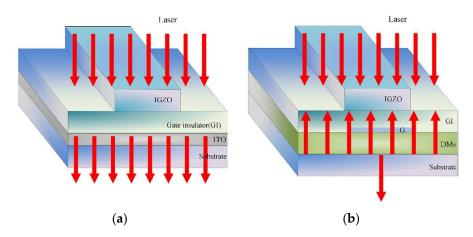

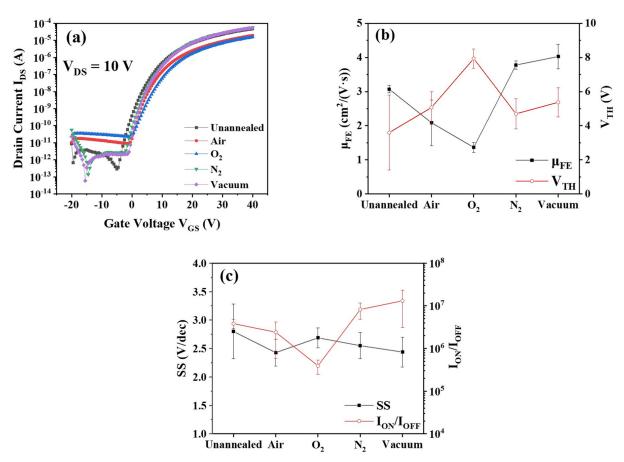

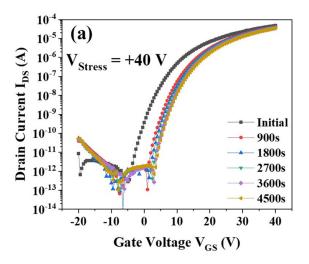

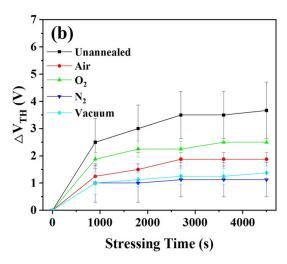

Recently, fabrication improvement in metal oxide TFTs has become a hot topic. Two papers related to this issue are included in this Special Issue [12,13]. N. Chen et al. [12] tried to apply laser treatment in the solution-processing of active layers of metal oxide TFTs, covering laser photochemical cracking of metastable bonds, laser thermal effect, photoactivation effect, and laser sintering of nanoparticles. In addition, W. Zhang et al. [13] investigated atmosphere effect in post-annealing treatments for a-IGZO TFTs with  $\mathrm{SiO}_{x}$  passivation layers, where different atmospheres (air,  $\mathrm{N}_{2}$ ,  $\mathrm{O}_{2}$ , and vacuum) were studied at length.

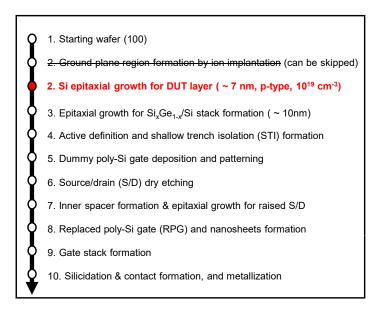

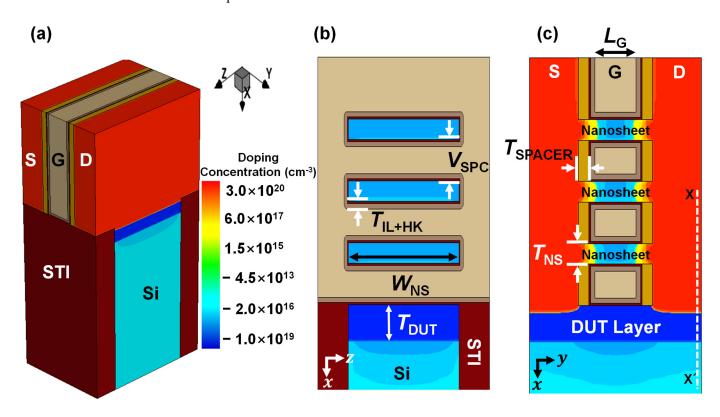

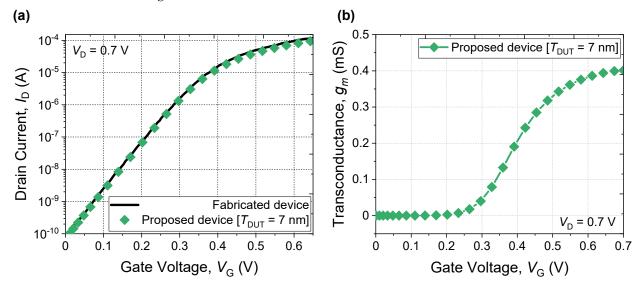

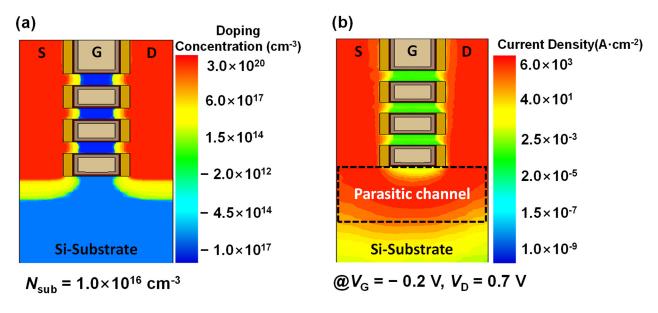

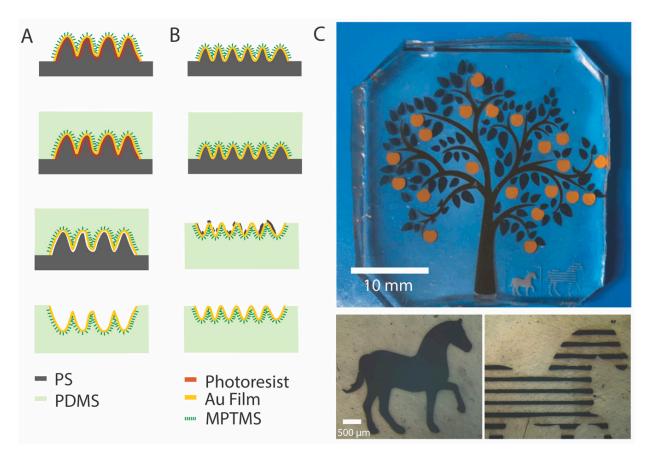

Interestingly, some novel processes relating thin film electronic devices were reported in this Special Issue [14,15]. K. S. Lee employed a process simplification for n-type nanosheet FETs without a ground plane region [14]; the proposed flow could be performed in situ, without the requirement of changing chambers or a high-temperature annealing process. In addition, X. Ding et al. successfully realized the efficient multi-material structured thin film transfer to elastomers for stretchable electronic devices by combining bench-top thin film structuring with solvent-assisted lift-off methods [15].

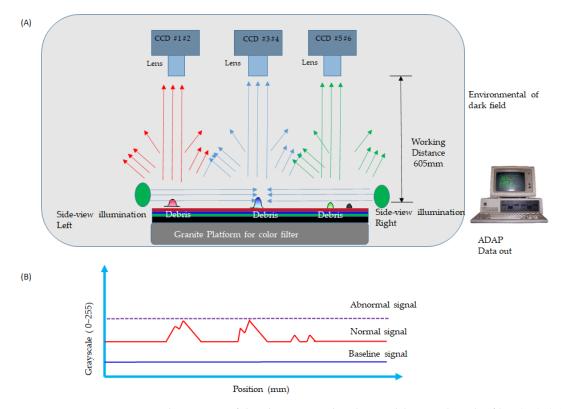

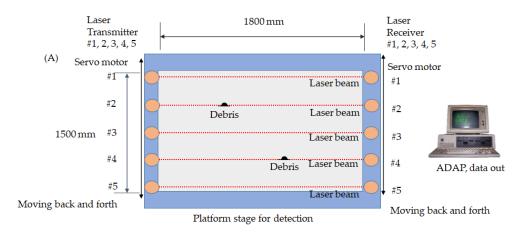

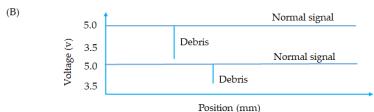

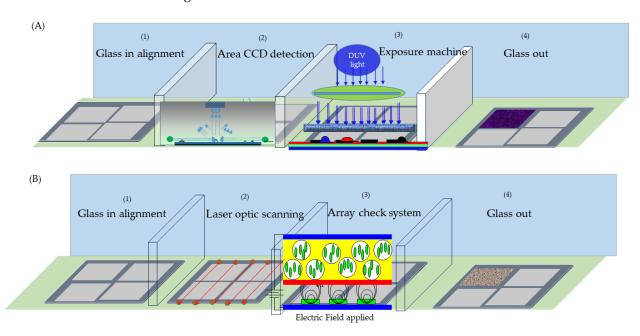

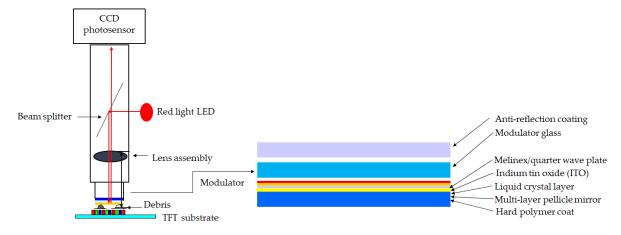

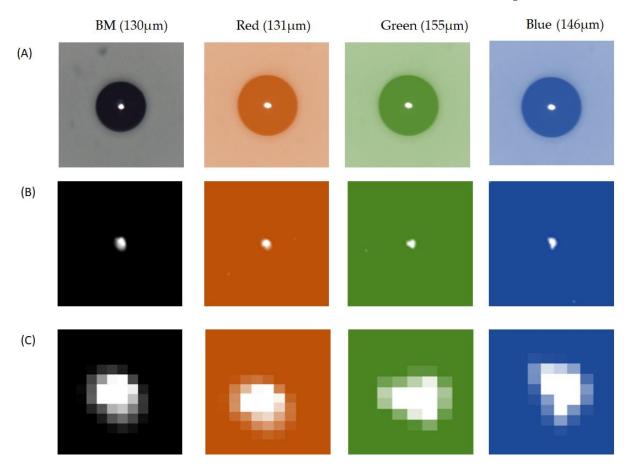

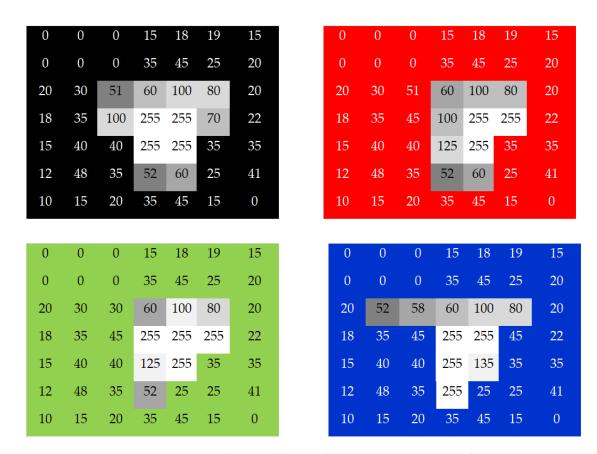

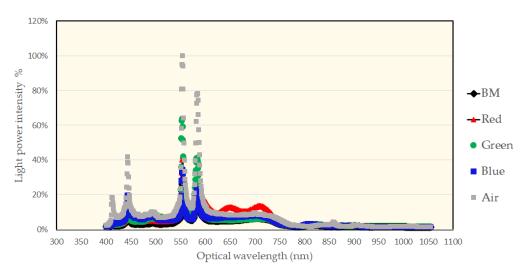

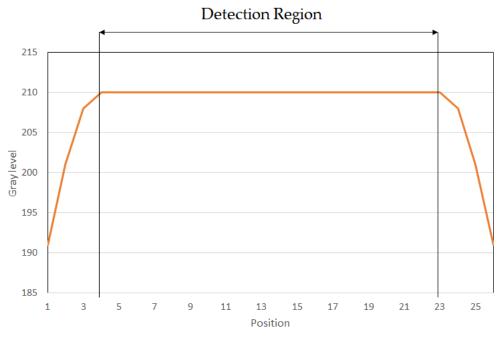

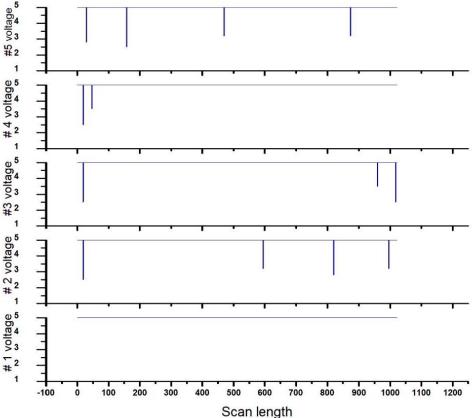

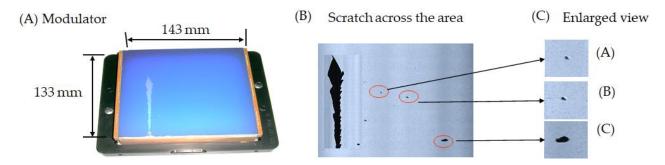

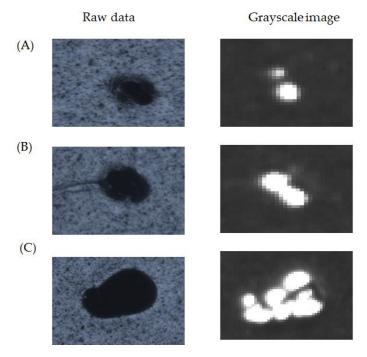

Liquid crystal displays (LCDs) are still the mainstream of FPDs, so it is very important to use effective inspection methods to improve yield in the mass productions of TFT-LCDs. Accordingly, non-contact optical detection of foreign materials adhered to color filters (CFs) and TFTs was investigated by F. M. Tzu et al. [16]. In contrast to the height of the debris material, the image was acquired by transforming the geometric shape from a square for side-view illumination using area charge-coupled devices (CCDs) in this study. The relating experiments presented a successful design to prevent a valuable component malfunction.

I would like to thank all the authors for submitting their papers to the Special Issue "Recent Advances in Thin Film Electronic Devices", as well as all the reviewers and editors for their contributions to improving these submissions.

**Funding:** This work was supported by the Key Research Project of Jiangxi Province (Grant No. 20194ABC28005).

Conflicts of Interest: The author declares no conflict of interest.

#### References

- 1. Kasap, S.; Capper, P. Handbook of Electronic and Photonic Materials; Springer International Publishing: New York, NY, USA, 2007.

- 2. Brotherton, S.D. Introduction to Thin Film Transistors; Springer International Publishing: Cham, Switzerland, 2013.

- 3. Zhou, Y. Semiconducting Metal Oxide Thin-Film Transistors; IOP Publishing Ltd.: Cham, Switzerland, 2021.

- 4. Someya, T. Stretchable Electronics; Wiley-VCH Verlag & Co., KGaA: Weinheim, Germany, 2013.

- 5. Rogers, J.A.; Ghaffari, B.; Kim, D.H. *Stretchable Bioelectronics for Medical Devices and Systems*; Springer International Publishing: Cham, Switzerland, 2016.

- 6. Tinoco, J.C.; Hernandez, S.A.; Olvera, M.L.; Estrada, M.; Garcia, R.; Martinez-Lopez, A.G. Impact of the Semiconductor Defect Density on Solution-Processed Flexible Schottky Barrier Diodes. *Micromachines* **2022**, *13*, 800. [CrossRef] [PubMed]

- 7. Zhu, Z.; Cao, W.; Huang, X.; Shi, Z.; Zhou, D.; Xu, W. Analysis of Nitrogen-Doping Effect on Sub-Gap Density of States in a-IGZO TFTs by TCAD Simulation. *Micromachines* **2022**, *13*, 617. [CrossRef] [PubMed]

- 8. Kim, M.K.; Choi, Y.K.; Park, J.Y. Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs. *Micromachines* **2022**, *13*, 124. [CrossRef] [PubMed]

- 9. Chen, J.Y.; Tang, X.G.; Liu, Q.X.; Jiang, Y.P.; Zhong, W.M.; Luo, F. An Artificial Synapse Based on CsPbI<sup>3</sup> Thin Film. *Micromachines* **2022**, *13*, 284. [CrossRef] [PubMed]

- 10. Selvendran, S.; Divya, J.; Raja, A.S.; Sivasubramanian, A.; Itapu, S. A Reconfigurable Surface-Plasmon-Based Filter/Sensor Using D-Shaped Photonic Crystal Fiber. *Micromachines* **2022**, *13*, 917. [CrossRef] [PubMed]

- 11. Amancio, M.A.; Romaguera-Barcelay, Y.; Matos, R.S.; Pires, M.A.; Gandarilla, A.M.D.; Nascimento, M.V.B.; Nobre, F.X.; Talu, S.; Filho, D.F.F.; Brito, W.R. Effect of the Deposition Time on the Structural, 3D Vertical Growth, and Electrical Conductivity Properties of Electrodeposited Anatase–Rutile Nanostructured Thin Films. *Micromachines* 2022, 13, 1361. [CrossRef] [PubMed]

- 12. Chen, N.; Ning, H.; Liang, Z.; Liu, X.; Wang, X.; Yao, R.; Zhong, J.; Fu, X.; Qiu, T.; Peng, J. Application of Laser Treatment in MOS-TFT Active Layer Prepared by Solution Method. *Micromachines* **2021**, 12, 1496. [CrossRef] [PubMed]

- 13. Zhang, W.; Fan, Z.; Shen, A.; Dong, C. Atmosphere Effect in Post-Annealing Treatments for Amorphous InGaZnO Thin-Film Transistors with SiOx Passivation Layers. *Micromachines* **2021**, *12*, 1551. [CrossRef] [PubMed]

- 14. Lee, K.S.; Park, J.Y. Article N-Type Nanosheet FETs without Ground Plane Region for Process Simplification. *Micromachines* **2022**, 13, 432. [CrossRef] [PubMed]

- 15. Ding, X.; Moran-Mirabal, M. Efficient Multi-Material Structured Thin Film Transfer to Elastomers for Stretchable Electronic Devices. *Micromachines* **2022**, *13*, 334. [CrossRef] [PubMed]

- 16. Tzu, F.M.; Hsu, S.H.; Chen, J.S. Non-Contact Optical Detection of Foreign Materials Adhered to Color Filter and Thin-Film Transistor. *Micromachines* **2022**, *13*, 101. [CrossRef]

Article

## Impact of the Semiconductor Defect Density on Solution-Processed Flexible Schottky Barrier Diodes

Julio C. Tinoco <sup>1,2</sup>, Samuel A. Hernandez <sup>1</sup>, María de la Luz Olvera <sup>3</sup>, Magali Estrada <sup>3</sup>, Rodolfo García <sup>4</sup> and Andrea G. Martinez-Lopez <sup>1,2,\*</sup>

- Micro and Nanotechnology Research Centre (MICRONA), Universidad Veracruzana, Veracruz 94294, Mexico; jutinoco@uv.mx (J.C.T.); samuhernandez@uv.mx (S.A.H.)

- Facultad de Ingeniería de la Construcción y el Hábitat (FICH), Universidad Veracruzana, Veracruz 94294, Mexico

- Solid-State Electronics Section, Electrical Engineering Department, CINVESTAV-IPN, Mexico City 07360, Mexico; molvera@cinvestav.mx (M.d.l.L.O.); mestrada@cinvestav.mx (M.E.)

- <sup>4</sup> University Center UAEM Ecatepec, Universidad Autónoma del Estado de México, Ecatepec de Morelos 55020, Mexico; rzgarcial@uaemex.mx

- \* Correspondence: andmartinez@uv.mx

**Abstract:** Schottky barrier diodes, developed by low-cost techniques and low temperature processes (LTP-SBD), have gained attention for different kinds of novel applications, including flexible electronic fabrication. This work analyzes the behavior of the *I–V* characteristic of solution processed, ZnO Schottky barrier diodes, fabricated at a low temperature. It is shown that the use of standard extraction methods to determine diode parameters in these devices produce significant dispersion of the ideality factor with values from 2.2 to 4.1, as well as a dependence on the diode area without physical meaning. The analysis of simulated *I–V* characteristic of LTP-SBD, and its comparison with experimental measurements, confirmed that it is necessary to consider the presence of a density of states (DOS) in the semiconductor gap, to understand specific changes observed in their performance, with respect to standard SBDs. These changes include increased values of *Rs*, as well as its dependence on bias, an important reduction of the diode current and small rectification values (*RR*). Additionally, it is shown that the standard extraction methodologies cannot be used to obtain diode parameters of LTP-SBD, as it is necessary to develop adequate parameter extraction methodologies for them.

**Keywords:** zinc oxide films; solution-processing electronics; Schottky barrier diodes; semiconductor defects

Citation: Tinoco, J.C.; Hernandez, S.A.; Olvera, M.d.l.L.; Estrada, M.; García, R.; Martinez-Lopez, A.G. Impact of the Semiconductor Defect Density on Solution-Processed Flexible Schottky Barrier Diodes. *Micromachines* 2022, 13, 800. https://doi.org/10.3390/mi13050800

Academic Editor: Chengyuan Dong

Received: 28 April 2022 Accepted: 19 May 2022 Published: 21 May 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

During the last decades, the microelectronics industry has been exploring a technological diversification, which allows the possibility of developing specific electronic systems for nontraditional areas, like medical and health care systems, environmental, biological applications, detection systems for chemical or physical signals, etc. Further development of novel materials and fabrication methodologies is required to produce new devices with the desired features. Some of these applications can require substrates, like flexible, transparent, organic, paper, among others [1]. In this context, film deposition from precursor solutions appears to be a potential tool for novel materials and electronic device fabrication techniques [2,3].

On another hand, Schottky barrier diodes (SBD), based on nanostructured oxide semiconductor films, appear to be potential candidates for different kinds of sensor devices. Furthermore, the possibility of using solution-processing techniques for diode manufacture allows the reduction of the fabrication temperatures to levels which make the full fabrication process compatible with flexible substrates. In recent years, the development of SBD based on solution-processes has become an interesting technological approach for manufacturing flexible and paper-based electronic devices, including a variety of sensor devices.

Up to now, for the analysis of low-cost and low temperature processed SBD, (LTP-SBD), thermionic emission was considered the main conduction mechanism. The diode parameters, such as barrier height ( $\phi_b$ ), ideality factor ( $\eta$ ), and series resistance ( $R_S$ ), are obtained using parameter extraction methodologies developed for high quality, crystalline semiconductor-based SBD, processed at high temperatures.

In LTP-SBD, three main features have been observed in diode parameters, extracted using above mentioned methodologies [4–11]: (i) the rectification ratio ( $RR = I_{ON}/I_{OFF}$ ) is, usually, very small (one or two orders of magnitude); (ii) large ideality factor values ( $\eta > 2$ ), and (iii) relatively large series resistances ( $R_S$ ). Regarding  $\eta$ , values close to 2, even greater than 7, can be found in the literature [4–11]. For SBD processed using high vacuum techniques, like sputtering deposition at room temperature, values of  $\eta$  near to 1 have been found [12,13].

Trying to understand the differences observed in the extracted diode parameters for LTP-SBD, with respect to those obtained for standard SBD, different explanations have been considered, among which are the impact of  $R_S$ , the presence of different conduction mechanisms, barrier height inhomogeneities, and interfacial states [5–7]. However, the physical reasons behind the wide range of values obtained for the LTP-SBD ideality factor are not clear, nor are the strong differences in parameter values observed in different film deposition methods.

In addition to the possible causes of this observed behavior, low temperature processing could jeopardize the semiconductor film quality, since it is well known that noncrystalline materials present a density of localized states (DOS) within the energy gap, which can strongly affect the behavior of devices based on these materials.

In this work, the behavior of the *I–V* characteristic of solution processed, ZnO LTP-SBD is studied. Main diode parameters, obtained by four extraction methods used for standard SBD fabricated at higher temperatures, are analyzed to evaluate the possibility of using them to characterize LTP-SBD. Additionally, simulated *I–V* characteristic of SBD, considering the presence of a density of localized states inside the semiconductor gap, were obtained to analyze the origin of the main characteristics of diodes performance.

#### 2. Experimental Part

#### 2.1. Fabrication Process

ZnO Schottky barrier diodes were obtained as follows: (i) the synthesis of ZnO nanoparticles; (ii) the deposition of a film, consisting of the ZnO nanoparticle colloidal dispersion, on a polyethylene terephthalate (PET) substrate, covered by an indium tin oxide (ITO) film as back-side electrode; (iii) deposition, by screen-printing technique, of a top silver electrode. The fabrication process was limited to a maximum temperature of  $150\,^{\circ}$ C. A detailed fabrication process can be found in [11]. Devices with square shape and different length (L) were manufactured and then electrically characterized.

#### 2.2. SBD Simulation

SBDs were simulated using the ATLAS simulation program from Silvaco [14]. ZnO was considered the semiconductor material and the presence of DOS was included.

As already mentioned, noncrystalline semiconductor materials contain certain distributions of DOS, which dominate the overall device electrical characteristics. Such states are grouped into deep and tail states. For our study, the effect of the tail states is predominant, so we will only consider them in our simulations. Tail state energy distribution can be approximated to an exponential distribution as:

$$g(E) = N_{TA} exp\left(-\frac{E_C - E}{E_{TA}}\right) + N_{TD} exp\left(-\frac{E - E_V}{E_{TD}}\right)$$

(1)

where  $N_{TA}$  and  $N_{TD}$  are, respectively, the acceptor and donor density of the tail states at the corresponding band border.  $E_{TA}$  and  $E_{TD}$  are, respectively, the activation energy of the acceptor and donor tails.

Main material parameters are shown in Table 1. For the DOS, a symmetrical variation for the acceptor and donor tail states was considered, while the value of  $N_{TA}$  and  $N_{TD}$ , was varied from  $10^{18}$  to  $10^{20}$  cm<sup>-3</sup> eV<sup>-1</sup>. For  $E_{TA}$  and  $E_{TD}$ , typical values for metal oxide materials were considered. Two different carrier densities,  $N_B$ , were analyzed. The metal work function  $(\Phi_M)$  was fixed to produce a barrier height of 0.54 eV.

Table 1. Summary of the semiconductor film parameters used in simulations.

| Parameter     | Value                              | Parameter        | Value                                                |

|---------------|------------------------------------|------------------|------------------------------------------------------|

| $E_g$         | 3.2 eV                             | $N_{TA}, N_{TD}$ | $10^{18}$ to $10^{20}$ eV $^{-1}$ cm $^{-3}$         |

| $\chi_s$      | 4.3 eV                             | $E_{TA}$         | 0.105 eV                                             |

| $N_C$ , $N_V$ | $5 	imes 10^{18}~\mathrm{cm}^{-3}$ | $E_{TD}$         | 0.385 eV                                             |

| $\mu_e$       | $10 \text{ cm}^2/\text{Vs}$        | $N_B$            | $5\times10^{16}$ and $5\times10^{18}~\text{cm}^{-3}$ |

#### 3. Traditional Extraction Methods to Obtain SBD Main Parameters from I-V Curves

Considering that the thermionic emission is the main conduction mechanism in SBD, four *I–V* extraction methodologies have been used to determine the diode parameters.

#### 3.1. Ideal Extraction Method

The diode current ( $I_D$ ) of an ideal SBD diode is defined by the general diode equation (GDE) expressed as:

$$I_D = I_0 \left[ exp \left( \frac{qV_D}{\eta kT} \right) - 1 \right] \tag{2}$$

where  $V_D$  is the applied voltage and  $\eta$  is the ideality factor.

The term  $I_0$  is the reverse current, which is defined as:

$$I_0 = AA^*T^2 exp\left(-\frac{q}{kT}\phi_b\right) \tag{3}$$

where *A* is the device area,  $A^*$  is the Richardson constant and  $\phi_b$  is the barrier height formed between the metal and the semiconductor.

There are different procedures to determine the barrier height and the ideality factor. Combining (2) and (3), and considering  $V_D >> kT/q$ , the GDE can be expressed as:

$$ln(I_D) = ln\left(AA^*T^2\right) - \frac{q}{kT}\phi_b + \frac{q}{\eta kT}V_D \tag{4}$$

Therefore, the semilogarithmic plot of the forward characteristic exhibits a linear dependence where the slope is related to  $\eta$  and the *y*-axis intercept with  $\phi_b$ .

#### 3.2. Norde's Function

This method considers the presence of a resistance in series with an ideal diode ( $R_S$ ). The method was developed without considering the ideality factor [15]. Afterwards  $\eta$  was included into the extraction procedure [16].

Considering the series resistance, the GDE is modified as:

$$I_D = I_0 \left[ exp \left( \frac{q(V_D - I_D R_s)}{\eta kT} \right) - 1 \right]$$

(5)

This method is based on the definition of an F function, considering  $V_D >> kT/q$ , as [16]:

$$F(V_D, \gamma) = \frac{V_D}{\gamma} - \frac{kT}{q} ln \left(\frac{I_D}{AA^*T^2}\right)$$

(6)

where  $\gamma$  is an arbitrary constant greater that  $\eta$ .

For values of  $\gamma$  greater than  $\eta$ , the  $F(V_D, \gamma)$  vs.  $V_D$  plot presents a minimum at the point  $(V_0, F_0)$ . That point corresponds with a diode current, of value  $I_0$  [16]. Hence, the

ideality factor can be determined, considering two different values of  $\gamma$  ( $\gamma_1$  and  $\gamma_2$ ) and the corresponding diode current values at the minimum of the *F* function [16]:

$$\eta = \frac{\gamma_1 I_{02} - \gamma_2 I_{01}}{I_{02} - I_{01}} \tag{7}$$

The barrier height and the series resistance can be determined as [16]:

$$\phi_b = F_{01} + \left(\frac{1}{\eta} - \frac{1}{\gamma_1}\right) V_{01} - \frac{kT}{q} \frac{\gamma_1 - \eta}{\eta} = F_{02} + \left(\frac{1}{\eta} - \frac{1}{\gamma_2}\right) V_{02} - \frac{kT}{q} \frac{\gamma_2 - \eta}{\eta}$$

(8)

$$R_s = \frac{kT}{q} \frac{\gamma_1 - \eta}{I_{01}} = \frac{kT}{q} \frac{\gamma_2 - \eta}{I_{02}}$$

(9)

#### 3.3. Cheung's Function

The Cheung's method allows the determination of the ideality factor, as well as the series resistance and the barrier height [17]. Equation (5) can be rewritten, considering the current density ( $J_D = I_D/A$ ) and  $V_D >> kT/q$ , as:

$$V_D = R_s A J_D + \eta \phi_B + \frac{kT}{q} \eta \cdot ln \left( \frac{J_D}{A^* T^2} \right)$$

(10)

The derivative of Equation (10) with respect to the logarithm of the current density is defined as [17]:

$$\frac{dV_D}{dln(J_D)} = R_s A J_D + \frac{kT}{q} \eta \tag{11}$$

As can be seen, a linear dependence with  $J_D$  is present and the ideality factor can be determined from the corresponding y-axis intercept [17].

Moreover, an *H* function is defined as [16]:

$$H(J_D) \equiv V_D - \frac{kT}{q} \eta \cdot ln \left( \frac{J_D}{A^* T^2} \right) \tag{12}$$

Comparing Equations (10) and (12), the *H* function is expressed as [17]:

$$H(J_D) = R_s A J_D + \eta \phi_B \tag{13}$$

Therefore, the plot of H vs.  $J_D$  shows a linear behavior. The slope is related to the series resistance and the y-axis intercept to the barrier height.

#### 3.4. Forward–Reverse (F–R) Function

This method analyses both the forward as well as reverse I–V characteristic. According to Equation (3), the reverse current is bias independent. However, solution-processed devices usually exhibit an important variation of the reverse current with the reverse voltage [4–11]. Considering the image force lowering effect and a very thin semiconductor film, the reverse current density ( $I_R$ ) can be expressed as [11]:

$$J_{R} = A^{*}T^{2}exp\left[-\frac{q}{kT}\left(\phi_{b} - \sqrt{\frac{qV_{R}}{4\pi\varepsilon_{0}k_{d}t}}\right)\right]$$

(14)

where  $V_R$  is the reverse bias,  $k_d$  is the dynamic dielectric constant and t is the electrical semiconductor film thickness.

Hence,  $\phi_b$  can be determined through the *y*-axis intercept of the semilogarithmic plot of  $J_R$  vs.  $V_R^{1/2}$ .

Furthermore, the series resistance can be extracted by the voltage derivative, with respect to the diode current of the forward characteristic  $(dV_F/dI_F)$ , which is expressed as [18]:

$$\frac{dV_F}{dI_F} = \left(\frac{dI_F}{dV_F}\right)^{-1} = R_S + \eta \frac{kT}{q} \left(\frac{1}{I_F + I_0}\right) \tag{15}$$

Therefore,  $R_S$  can be extracted from the y-axis intercept of the plot of the inverse of the current derivative vs. the  $1/(I_F + I_0)$  term [11].  $I_0$  is calculated through (3) using the  $\phi_b$  value obtained from (14). Additionally,  $\eta$  can be extracted, in an independent manner, from the slope of the same plot [11].

#### 4. Results and Discussion

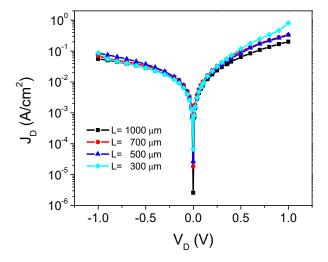

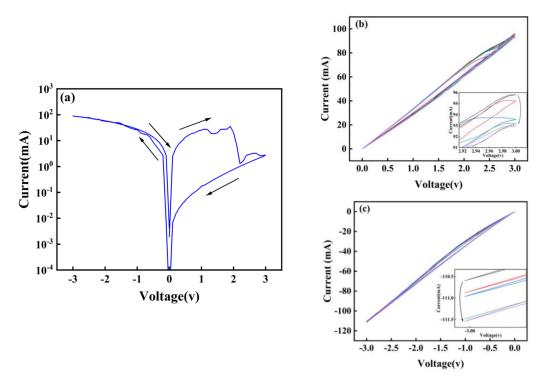

Figure 1 shows the  $J_D$ – $V_D$  characteristics of measured devices with different L. As can be seen, the rectification ratio RR, obtained as diode current at +1 V divided by the current at -1 V, is about one order of magnitude. Contrarily, for crystalline devices, RR can be greater than six orders of magnitude. Moreover, the reverse current density shows a significant dependence on the applied voltage. On the other hand, as expected, the forward current density has similar values for all devices at low applied voltage. Beyond 0.5 V,  $J_D$  starts to increase as the device area is reduced.

Diode parameter extractions, using the different strategies explained in Section 3, were performed with the aim of analysing the diode performance, as well as the unforeseen current density increment, to a deeper level. Table 2 summarizes the extracted values for  $\phi_b$ ,  $\eta$  and  $R_S$ . The overall results agree with the main features previously observed for LTP-SBD [4–11].

**Figure 1.** Plot of the  $J_D$ – $V_D$  characteristic for the different length devices. The diode area is defined as  $A = L^2$ .

**Table 2.** Summary of the extracted Schottky barrier diode through the different extraction procedures.

|                   | Ideal I | Method                 | No  | rde's Func             | tion               | Che | eung's Me              | thod               | F   | -R Metho               | d                  |

|-------------------|---------|------------------------|-----|------------------------|--------------------|-----|------------------------|--------------------|-----|------------------------|--------------------|

| Diode Length (μm) | η       | φ <sub>b</sub><br>(eV) | η   | φ <sub>b</sub><br>(eV) | $R_s$ ( $\Omega$ ) | η   | φ <sub>b</sub><br>(eV) | $R_s$ ( $\Omega$ ) | η   | φ <sub>b</sub><br>(eV) | $R_s$ ( $\Omega$ ) |

| 1000              | 16.5    | 0.48                   | 2.2 | 0.53                   | 592                | 2.4 | 0.54                   | 506                | 4.1 | 0.52                   | 395                |

| 700               | 15.6    | 0.47                   | 2.6 | 0.55                   | 714                | 3.1 | 0.53                   | 546                | 3.2 | 0.52                   | 675                |

| 500               | 14.4    | 0.48                   | 3.0 | 0.56                   | 1478               | 3.1 | 0.53                   | 1189               | 3.1 | 0.52                   | 1300               |

| 300               | 12      | 0.48                   | 3.5 | 0.59                   | 2300               | 2.3 | 0.54                   | 3238               | 3   | 0.53                   | 3300               |

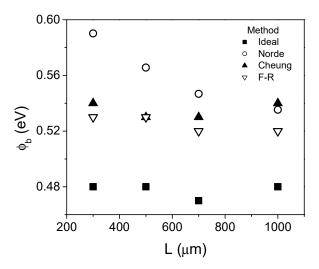

Figure 2 shows the comparison of the extracted barrier height obtained with the different methods. As can be seen, for all devices the extracted values of  $\phi_b$  using the ideal method are about 10% smaller than using the other methods. The Cheung and the F–R methods exhibit close values of  $\phi_b$ , while Norde 's method shows a small difference for large devices, which increases as L is reduced. Nevertheless, the different methods used allow the determination of the barrier height with a relatively small variation of  $\pm 10$  %. It is worth noting that the Norde and Cheung methods allow the extraction of the barrier height after the ideality factor; hence, a reliable  $\eta$  extraction is of main importance. On the contrary, the F–R method allows the determination of the barrier height in an independent form.

**Figure 2.** Comparison of the extracted values of the barrier height using the different methods.

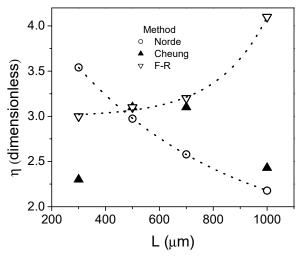

As can be seen from Table 2, the ideality factor presents abnormally large values when the ideal extraction is used. This occurs because the impact on  $R_S$  is neglected. The other methods include the series resistance and, thus, the extracted values of  $\eta$  are reduced. Figure 3 shows the comparison of the  $\eta$  extracted values using the methods which include the series resistance on the extraction methodology. In all cases, the resulting  $\eta$  values are greater than 2 and a significant dispersion is observed. Additionally, Norde and F–R methods show an opposite trend. In the Norde case, the value of  $\eta$  increases as the device area is reduced, while with the F–R method, it reduces. However, there is not a physical reason that could support the variation of the diode ideality factor with the device area.

Figure 3. Comparison of the extracted values of the ideality factor.

Therefore, the standard SBD extraction methods allow the determination of the barrier height into a reasonable deviation. For the ideality factor, however, a significant dispersion and even different trends when varying the diode area are obtained, depending on the method considered. However, the behavior shown in Figure 1 suggests that a single set of parameters is required to define the diode performance up to ~0.4 V, and after that bias, the increment on the current density with the area must be explained.

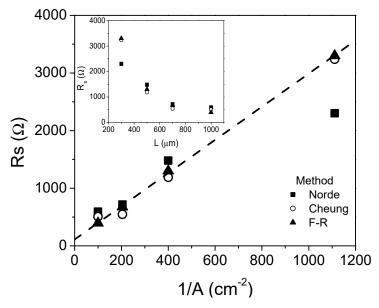

Figure 4 shows the extracted  $R_S$  vs. the inverse of the diode area. In the inset, the  $R_S$  vs. L plot is shown. In general,  $R_S$  has a linear behavior in respect to 1/A. As a first approach, the device can be considered a rectangular semiconductor with electrodes on the top and at the bottom, which produce the observed dependence with the diode area. This fact also suggests a constant value of the resistance normalized with diode area  $(A.R_S)$ .

The above-mentioned analysis implies an issue on the proper determination of the diode parameters utilizing the traditional methodologies, since a single set of parameters cannot explain the experimental diode current. Because of the observed results, a deeper analysis on the LTP-SBD behavior must be performed, as well as the development of specific extraction methodologies for this kind of devices.

Figure 4. Comparison of the extracted values of the series resistance using the different methods.

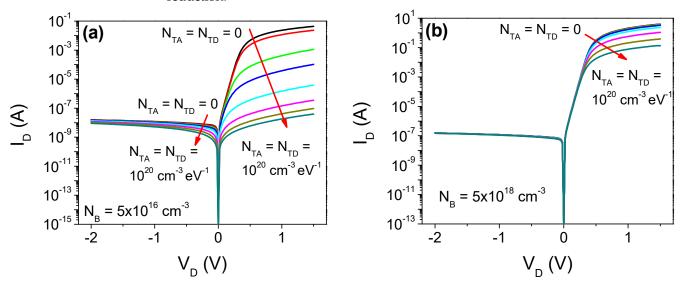

To further analyze the behavior of LTP-SBDs, finite-element numerical simulations were performed. Figure 5a,b show the I–V characteristic for devices simulated in ATLAS, for two doping concentrations and the different DOS parameters shown in Table 1. For comparison, defect-free simulated devices are included. As can be seen, the reverse current exhibits a negligible impact with the presence of DOS. Contrarily, the tail state's presence produces an important reduction in the forward diode current. This can be explained due to the electron-trapping on the defects, which implies a reduction in the overall free carriers in the conduction band and, hence, of the device current. The impact, however, is more important for devices with relatively low free carrier concentration, which implies a highly resistive film. In such cases,  $I_{ON}$  is reduced by several orders of magnitude, which explains the typical rectification ratio experimentally achieved [4–11].

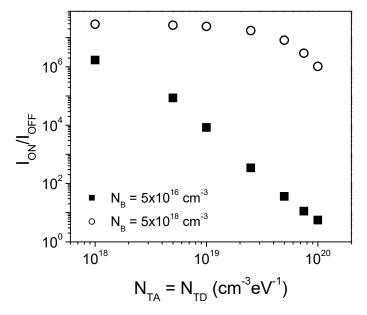

Figure 6 shows the comparison of the RR vs. the defect densities for two values of  $N_B$ . As can be observed, LTP-SBDs with low quality semiconductor films (i.e., high resistivity and high defects densities) exhibit a strong RR reduction, until around one order of magnitude, which are similar to what is observed in experimental devices [4–11]. On the other hand, when the layer has a moderate or high conductivity (which implies a better film quality), the impact of the defects is reduced and the RR value is only slightly reduced, remaining several orders of magnitude as experimentally observed for high

vacuum processing [12,13], even for defect densities in the range of  $10^{20}$  cm<sup>-3</sup>eV<sup>-1</sup>. It can be expected that a further increase of the defect densities will produce a stronger RR reduction.

**Figure 5.** *I–V* characteristic for the simulated SBD considering different densities of localized states for  $N_B$  equal to (**a**)  $5 \times 10^{16}$  and (**b**)  $5 \times 10^{18}$  cm<sup>-3</sup>. For comparison, defect free devices ( $N_{TA} = N_{TD} = 0$ ) are considered.

**Figure 6.** Comparison of the rectification ratio (RR) vs. the defect densities, for both  $N_B$  values used in the simulations.

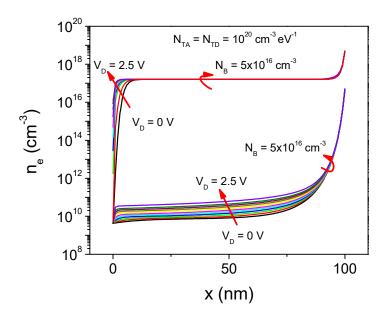

Figure 7 shows the simulated electron concentration ( $n_e$ ) inside the semiconductor film for both  $N_B$  values vs. forward applied voltage. As can be seen, the impact of the film qualities on  $n_e$  is confirmed. Moreover, it is observed that, for high resistivity films,  $n_e$  is modulated by the forward bias. Contrarily, for low resistivity films,  $n_e$  is constant along most of the film thickness.

**Figure 7.** Comparison of the electron concentration ( $n_e$ ) vs. the semiconductor film position (x), for both  $N_B$  values used in the simulations.

As was mentioned above, the diode can be considered as a rectangular semiconductor die. Therefore, the resistance due to a differential film thickness is defined as:

$$dR_S = \frac{1}{q\mu A} \cdot \frac{dx}{n_e(x)} \tag{16}$$

where  $\mu$  is the electron mobility and A is the device area.

The total resistance, due to the semiconductor film, can be calculated integrating (16) along the film thickness (*t*):

$$R_S = \frac{1}{q\mu A} \int_0^t \frac{dx}{n_e(x)} \tag{17}$$

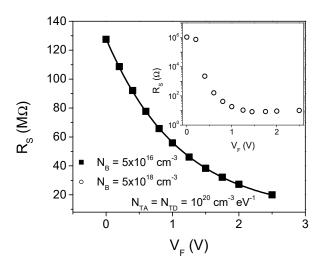

Considering the electron distribution shown in Figure 7, it is possible to determine the series resistance contribution caused by the film. Figure 8 shows the calculated resistance vs. the bias applied for device with  $N_B = 5 \times 10^{16}~\rm cm^{-3}$  and defect densities of  $10^{20}~\rm cm^{-3}~\rm eV^{-1}$ . In the inset, the calculated resistance for a device with  $N_B = 5 \times 10^{18}~\rm cm^{-3}$  is also shown. For the case of low resistivity semiconductor film, the resistance shows an abrupt reduction at small forward bias, from about 1 M $\Omega$  to few k $\Omega$ . When bias is increased above 1 V,  $R_S$  becomes almost constant. On the contrary, for a higher resistivity material with a relatively high defect density, the resistance exhibits extremely high values. At the same time, an important dependence on the applied forward voltage is observed. According to Figure 8,  $R_S$  exhibits an exponential dependence on  $V_D$ , which, as a first approach, can be expressed as:

$$R_S = R_0 exp\left(-\frac{V_D}{\delta}\right) \tag{18}$$

where  $R_0$  is the zero bias resistance and  $\delta$  can be related to the DOS.

Under this scenario, to better represent the behavior of the *I–V* curve for LTP-SBDs, the general diode equation must be modified as:

$$I_{D} = AA^{*}T^{2}exp\left(-\frac{q\phi_{B}}{kT}\right)exp\left\{\frac{q\left[V_{D} - I_{D}R_{0}exp\left(-\frac{V_{D}}{\delta}\right)\right]}{\eta kT}\right\}$$

(19)

This series resistance bias dependence can explain the abnormal current density increment observed as L is reduced in Figure 1. As diode area is reduced, the resistance value is increased, and, therefore, its reduction with the applied voltage becomes more significant. Hence, beyond 0.4 V, the current density starts to increase, due to the  $R_S$  reduction.

**Figure 8.** Calculated series resistance vs. forward bias, for  $N_B$  of  $5 \times 10^{16}$  cm<sup>-3</sup>. In the inset, the corresponding plot for  $N_B$  of  $5 \times 10^{18}$  cm<sup>-3</sup> is shown.

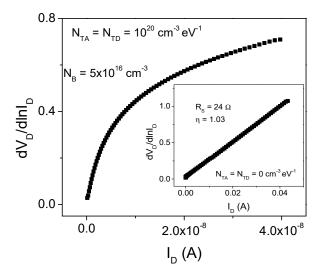

Furthermore, the bias-dependent  $R_S$  would imply an important concern regarding the correct parameter extraction. In order to verify this assumption, Figure 9 shows the corresponding  $dV_D/dln(I_D)$  vs.  $I_D$  plot, according to Equation (11) of Cheung 's method, for the simulated device shown in Figure 8. For comparison, in the inset the plot for a defect free device is shown. As can be seen, the extraction procedure can be properly applied for the defect free device getting the extracted value of  $\eta$  as one. On the contrary, when the high defect density is included in the simulation, the plot does not show a linear behavior at any forward bias region. This fact clearly shows that for low-cost and low-temperature processing SBDs, the film quality compromises the reliable application of the traditional extraction methods due to the bias dependence exhibited by  $R_S$ . Therefore, the extracted parameters can exhibit the important variations shown in Figures 2 and 3. Thus, proper extraction methodologies for low-cost and low-temperature processed SBD are of main importance to adequately understand the diode behavior.

**Figure 9.** Plot of the  $dV_D/dln(I_D)$  vs  $I_D$ , used for  $\eta$  and  $R_S$  extraction in the Cheung extraction method.

#### 5. Conclusions

ZnO LTP-SBDs were analyzed using a single  $I_D$ - $V_D$  characteristic and four traditional extraction methodologies. The barrier height extraction shows a relatively small dispersion of about  $\pm 10\%$ . On the other hand, the ideality factor obtained exhibits a significant dispersion with values from 2.2 to 4.1, depending on the extraction method used. Simulation results show that devices without or with low DOS, as is the case of standard SBD fabricated at higher temperatures, show high values of RR, relatively small values of  $R_S$ , and are almost bias-independent at relatively high forward applied voltage. Thus, traditional parameter extraction methodologies can be properly used. On the other hand, devices fabricated using low-cost techniques (solution-processing techniques, printing strategies, etc.) at low temperatures can produce films with high tail state densities and high resistivity. Simulations showed that the combination of high DOS and low carrier concentration produces a strong impact on diode behavior, which implies an important reduction in the forward current and RR values. For these devices, the series resistance exhibits high values, as well as an exponential dependence on the forward applied voltage. Under these conditions, the traditional extraction methodologies of diode parameters are compromised, so further efforts must be made to develop adequate parameter extraction methodologies for low-cost and very low-temperature processed Schottky barrier diodes.

**Author Contributions:** Conceptualization, J.C.T. and A.G.M.-L.; methodology, J.C.T. and A.G.M.-L.; software, J.C.T., R.G. and M.E.; validation, S.A.H. and A.G.M.-L.; investigation, J.C.T., S.A.H., R.G. and A.G.M.-L.; resources, M.d.I.L.O., M.E. and A.G.M.-L.; writing—original draft preparation, J.C.T. and A.G.M.-L.; writing—review and editing, M.E. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Baeg, K.-J.; Lee, J. Flexible Electronic Systems on Plastic Substrates and Textiles for Smart Wearable Technologies. *Adv. Mater. Technol.* **2020**, *5*, 2000071. [CrossRef]

- 2. Berger, P.R.; Li, M.; Mattei, R.M.; Niang, M.A.; Talisa, N.; Tripepi, M.; Harris, B.; Bhalerao, S.R.; Chowdhury, E.A.; Winter, C.H.; et al. Advancements in Solution Processable Devices using Metal Oxides For Printed Internet-of-Things Objects. In Proceedings of the IEEE Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019. [CrossRef]

- 3. Chan, K.-Y.; Ng, Z.-N.; Au, B.W.-C.; Knipp, D. Visibly transparent metal oxide diodes prepared by solution processing. *Opt. Mater.* **2018**, *75*, 595–600. [CrossRef]

- 4. Rouis, A.; Hizem, N.; Kalboussi, A. Electrical characterizations of Schottky diode with zinc oxide nanowires. In Proceedings of the IEEE International Conference on Design & Test of Integrated Micro & Nano-Systems (DTS), Gammarth, Tunisia, 28 April–1 May 2019. [CrossRef]

- 5. Ahmeda, M.A.M.; Mwankemwa, B.S.; Carleschi, E.; Doyle, B.P.; Meyer, W.E.; Nel, J.M. Effect of Sm doping ZnO nanorods on structural optical and electrical properties of Schottky diodes prepared by chemical bath deposition. *Mater. Sci. Semicond. Processing* **2018**, *79*, 53–60. [CrossRef]

- 6. Caglar, Y.; Caglar, M.T.; Ilican, S. XRD, SEM, XPS studies of Sb doped ZnO films and electrical properties of its based Schottky diodes. *Optik* **2018**, *164*, 424–432. [CrossRef]

- 7. Rana, V.S.; Rajput, J.K.; Pathak, T.K.; Purohit, L.P. Cu sputtered Cu/ZnO Schottky diodes on fluorine doped tin oxide substrate for optoelectronic applications. *Thin Solid Film.* **2019**, *679*, 79–85. [CrossRef]

- 8. Zhang, J.; Zhao, G.; Li, Y.; Ai, T.; Wu, C.; Jia, J.; Yan, F.; Wang, Y. Study on the electrical properties of nano ZnO/PET-ITO heterojunction prepared by hydrothermal method. *J. Electron Spectrosc. Relat. Phenom.* **2019**, 235, 68–72. [CrossRef]

- 9. Ozório, M.S.; Nascimento, M.R.; Vieira, D.H.; Nogueira, G.L.; Martin, C.S.; Lima, S.A.M.; Alves, N. AZO transparent electrodes grown in situ during the deposition of zinc acetate dihydrate onto aluminum thin film by spray pyrolysis. *J. Mater. Sci. Mater. Electron.* **2019**, *30*, 13454–13461. [CrossRef]

- 10. Yilmaz, M.; Cirak, B.B.; Aydogan, S.; Grilli, M.L.; Biber, M. Facile electrochemical-assisted synthesis of TiO<sub>2</sub> nanotubes and their role in Schottky barrier diode applications. *Superlattices Microstruct.* **2018**, *113*, 310–318. [CrossRef]

- 11. Tinoco, J.C.; Hernández, S.A.; Rodrigez-Bernal, O.; Vega-Poot, A.G.; Rodriguez Gattorno, G.; de la L. Olvera, M.; Martinez-Lopez, A.G. Fabrication of Schottky Barrier Diodes based on ZnO for Flexible Electronics. *J. Mater. Sci. Mater. Electron.* 2020, 30, 7373–7377. [CrossRef]

- 12. Zhang, J.; Wang, H.; Wilson, J.; Ma, X.; Jin, J.; Song, A. Room Temperature Processed Ultrahigh-Frequency Indium–Gallium–Zinc-Oxide Schottky Diode. *IEEE Electron Device Lett.* **2016**, *37*, 389–392. [CrossRef]

- 13. Xin, Q.; Yan, L.; Du, L.; Zhang, J.; Luo, Y.; Wang, Q.; Song, A. Influence of sputtering conditions on room-temperature fabricated InGaZnO-based Schottky diodes. *Thin Solid Film.* **2016**, *616*, 569–572. [CrossRef]

- 14. ATLAS User's Manual; SILVACO Inc.: Santa Clara, CA, USA, 2020.

- 15. Norde, H. A modified forward I–V plot for Schottky diodes with high series resistance. *J. Appl. Phys.* **1979**, *50*, 5052–5053. [CrossRef]

- 16. Bohlin, K.E. Generalized Norde plot including determination of the ideality factor. J. Appl. Phys. 1986, 60, 1223–1224. [CrossRef]

- 17. Cheung, S.K.; Cheung, N.W. Extraction of Schottky diode parameters from forward current-voltage characteristics. *Appl. Phys. Lett* **1989**, 49, 85–87. [CrossRef]

- 18. Ortiz-Conde, A.; García-Sánchez, F.J. A new approach to the extraction of single exponential diode model parameters. *Solid State Electron.* **2018**, 144, 33–38. [CrossRef]

Article

## Analysis of Nitrogen-Doping Effect on Sub-Gap Density of States in a-IGZO TFTs by TCAD Simulation

Zheng Zhu<sup>1</sup>, Wei Cao<sup>1</sup>, Xiaoming Huang<sup>1,\*</sup>, Zheng Shi<sup>2</sup>, Dong Zhou<sup>3</sup> and Weizong Xu<sup>3</sup>

- College of Integrated Circuit Science and Engineering, Nanjing University of Posts and Telecommunications, Nanjing 210023, China; 1219023314@njupt.edu.cn (Z.Z.); 1220024107@njupt.edu.cn (W.C.)

- School of Communications and Information Engineering, Nanjing University of Posts and Telecommunications, Nanjing 210023, China; shizheng@njupt.edu.cn

- National Laboratory of Solid State Microstructures, Nanjing University, Nanjing 210093, China; dongzhou@nju.edu.cn (D.Z.); njuphyxwz@126.com (W.X.)

- \* Correspondence: huangxm@njupt.edu.cn

**Abstract:** In this work, the impact of nitrogen doping (N-doping) on the distribution of sub-gap states in amorphous InGaZnO (a-IGZO) thin-film transistors (TFTs) is qualitatively analyzed by technology computer-aided design (TCAD) simulation. According to the experimental characteristics, the numerical simulation results reveal that the interface trap states, bulk tail states, and deep-level sub-gap defect states originating from oxygen-vacancy- (V<sub>o</sub>) related defects can be suppressed by an appropriate amount of N dopant. Correspondingly, the electrical properties and reliability of the a-IGZO TFTs are dramatically enhanced. In contrast, it is observed that the interfacial and deep-level sub-gap defects are increased when the a-IGZO TFT is doped with excess nitrogen, which results in the degeneration of the device's performance and reliability. Moreover, it is found that tail-distributed acceptor-like N-related defects have been induced by excess N-doping, which is supported by the additional subthreshold slope degradation in the a-IGZO TFT.

Keywords: a-IGZO TFTs; sub-gap states; nitrogen-doping; numerical simulation; stability

Citation: Zhu, Z.; Cao, W.; Huang, X.; Shi, Z.; Zhou, D.; Xu, W. Analysis of Nitrogen-Doping Effect on Sub-Gap Density of States in a-IGZO TFTs by TCAD Simulation. *Micromachines* 2022, 13, 617. https://doi.org/ 10.3390/mi13040617

Academic Editor: Chengyuan Dong

Received: 6 March 2022 Accepted: 12 April 2022 Published: 14 April 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

Currently, the backplane technology of amorphous InGaZnO (a-IGZO) thin-film transistors (TFTs) is attracting great attention for its use in pixel switching and driving units for next-generation display applications. The competitive advantage of a-IGZO TFT technology is that it can offer high current-driving capacity, high optical transparency, low power consumption and low process temperature compared with traditional Si-based TFTs [1–3]. Although a-IGZO TFT technology has made remarkable progress since it was first proposed by Nomura et al. in 2004, these devices still cannot achieve the desired performance and reliability due to high-density sub-gap states existing in the bandgap of a-IGZO [4,5]. It has been demonstrated that the sub-gap defects mainly originate from oxygen-vacancyrelated (V<sub>0</sub>-related) defects induced by the structural disorder in a-IGZO [5–7], which degrades the electrical properties and reliability of TFTs by trapping electrons or holes in the channel layer and interfacial region under bias, light, and thermal stress [8–11]. To enhance the device performance and reliability, an in-situ nitrogen-doping (N-doping) approach during the a-IGZO active layer deposition has been proposed to suppress V<sub>0</sub> defect generation [12-14]. For example, it has been demonstrated that N-doping can significantly improve the reliability of a-IGZO TFTs under positive gate-bias stress (PBS) and PBS with light illumination, since the N incorporated into a-IGZO will occupy the Vo sites and suppress V<sub>o</sub>-related defect generation [14,15]. Moreover, it has also been reported that the device performance and reliability are simultaneously enhanced by N and H co-doping, which is ascribed to the passivation of the Vo distributed at the active layer and interface region by forming N—H and Zn–N bonds [16]. Although V<sub>0</sub>-related defects

can be efficiently passivated by N-doping, a fundamental physical understanding of the impact of N-doping on the distribution of sub-gap states in a-IGZO TFTs is lacking. Since the device performance and reliability basically depend upon the nature and density of sub-gap defect states [4,17], an in-depth systematic study of the impact of N-doping on the sub-gap density of states (DOS) in a-IGZO TFTs is the key to future process improvement and optimization.

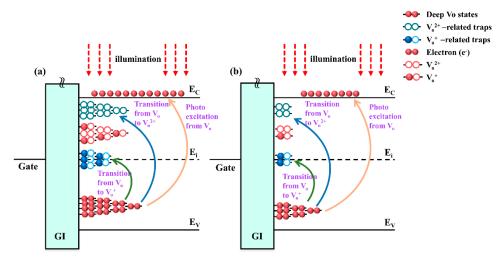

In this work, the influence of N-doping on the sub-gap  $V_o$ -related defects in a-IGZO TFTs is qualitatively analyzed using technology computer-aided design (TCAD) simulation [18]. It is found that the density of the interface  $V_o$  trap states, bulk  $V_o$ -related tail states and deep-level  $V_o$ -related defect states of a-IGZO TFTs are significantly decreased by moderate N-doping, which is validated by the improvement in electrical properties and stability during PBS and sub-band illumination. In contrast, the DOS of a-IGZO TFT is increased when the a-IGZO TFTs are doped with excessive nitrogen atoms, which causes degeneration of the device performance and reliability. Meanwhile, it is confirmed that the tail-distributed acceptor-like N-related defects are formed by excessive N-doping, which leads to the degradation of subthreshold slope (SS) in a-IGZO TFT.

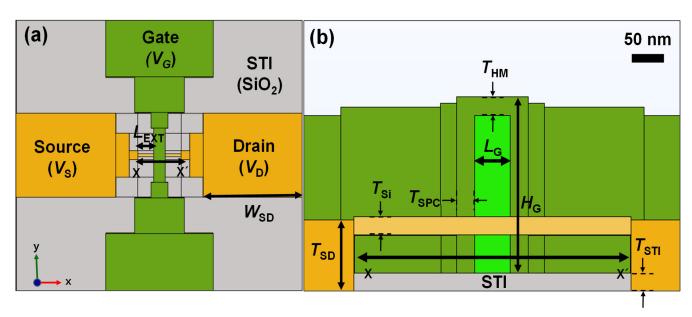

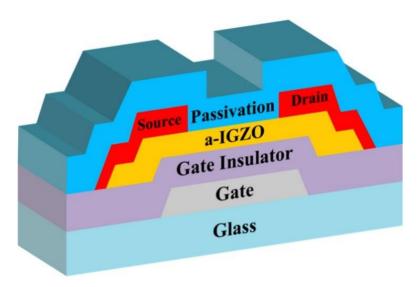

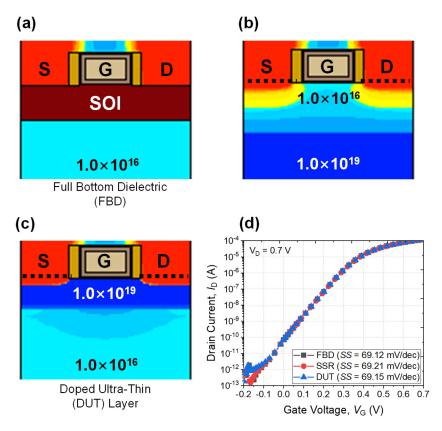

#### 2. Experiments and Modeling Scheme

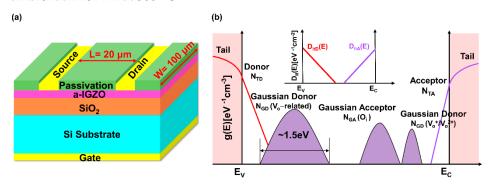

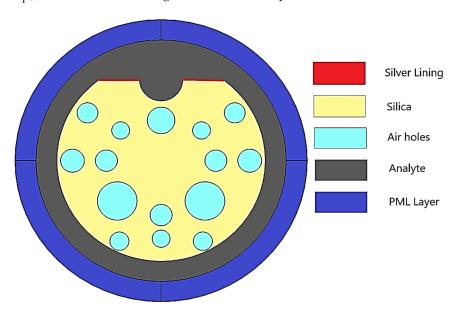

The a-IGZO TFT structure used for numerical simulation is shown in Figure 1a. The devices in this work were fabricated on n-type Si substrate. First, the gate insulator was composed of a 200 nm SiO<sub>2</sub> thin film grown by plasma-enhanced chemical vapor deposition (PECVD) with a rate of ~50 nm/min at 350 °C. The 45-nm-thick a-IGZO thin films were then deposited by direct-current (DC) sputtering system with a various gas mixture of  $N_2/(O_2+N_2)=0\%$ , 20%, and 40% at a fixed Ar flow rate of 30 sccm. The composition of the ceramic target used was In:Ga:Zn = 2:2:1 in atomic ratio. Subsequently, the device active region was patterned by conventional photolithography and wet chemical etching. Next, the Ti/Au (30/70 nm) bi-layer drain/source contact electrodes were evaporated by e-beam evaporation, and is the active region was further patterned using lift-off technique, which resulted in the final device dimensions of W/L = 100  $\mu$ m/20  $\mu$ m. Finally, a 100-nm-thick SiO<sub>2</sub> passivation layer was deposited by PECVD. The fabricated devices were annealed in ambient air for 1 h at 300 °C.

**Figure 1.** (a) Schematic diagram of the a-IGZO TFT with a bottom-gate structure; (b) Schematic illustration of the DOS model in the a-IGZO TFTs. The  $N_{TD}$  and  $N_{TA}$  represent the donor-like and acceptor-like tail states, respectively. The three gaussian curves represent the deep  $V_0$ -related states ( $N_{GD}(V_0$ -related)), oxygen interstitials ( $N_{GA}(O_i)$ ), and shallow donor states ( $N_{GD}(V_0$ - $V_0$ - $V_0$ ), respectively. The inset is the schematic illustration of the interface trap density ( $D_{it}(E)$ ).

In the Silvaco TCAD Simulation tool, ATLAS, a physics-based device simulator, is used to perform the electrical characterization, which can reduce the cost and time needed for experimentation [19]. It is also a powerful tool to predict the electrical behavior of specified semiconductor structures by using the Poisson and the continuity equations, which describe the electronic phenomena and electrical transport mechanism [19]. Based on the DOSs model of the a-IGZO TFTs, the types of the sub-gap states in the TFT channel region and interface region are illustrated in Figure 1b. In the a-IGZO material, the sub-gap

states are mainly classified as acceptor-like and donor-like states, which can be depicted by Gaussian distribution states and exponentially decaying band-tail states. The specific mathematical model is expressed as follows [20–22]:

$$g_{TA}(E) = N_{TA} \exp\left(\frac{E - E_C}{W_{TA}}\right) \tag{1}$$

$$g_{TD}(E) = N_{TD} \exp\left(\frac{E_V - E}{W_{TD}}\right) \tag{2}$$

$$g_{GA}(E) = N_{GA} \exp\left[-\left(\frac{E_{GA} - E}{W_{GA}}\right)^2\right]$$

(3)

$$g_{GD}(E) = N_{GD} \exp\left[-\left(\frac{E - E_{GD}}{W_{GD}}\right)^2\right]$$

(4)

where the  $g_{TD}(E)$  and  $g_{TA}(E)$  denote the density of donor-like tail and acceptor-like tail states. The  $g_{GA}(E)$  and  $g_{GD}(E)$  represent the Gaussian-distributed acceptor-like and donor-like states. The  $N_{TA}$  and  $N_{TD}$  are the effective density at the conduction band minimum ( $E_C$ ) and valence band maximum ( $E_V$ ), respectively. The  $W_{TD}$  and  $W_{TA}$  are the characteristic slope energy of valence-band tail states and conduction-band tail states. The  $N_{GD}$  and  $N_{GA}$  are the total density of Gaussian donor and acceptor states, respectively. The  $E_{GA}$  and  $E_{GD}$  are the corresponding peak energy.  $W_{GA}$  and  $W_{GD}$  are the corresponding characteristic decay energy.

In addition, the interface trap density  $(D_{it}(E))$  at the a-IGZO/dielectric interfacial region can be described as [23]:

$$D_{it}(E) = D_{itA} \exp\left(\frac{E - E_C}{W_{itA}}\right) + D_{itD} \exp\left(\frac{E_V - E}{W_{itD}}\right)$$

(5)

where  $D_{itD}$  and  $D_{itA}$  represent the donor-like and acceptor-like interface trap density, respectively. The  $W_{itA}$  and  $W_{itD}$  denote the corresponding slope energy.

#### 3. Results and Discussion

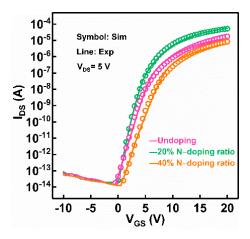

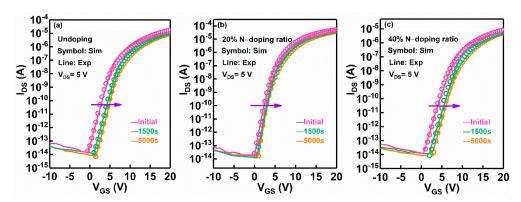

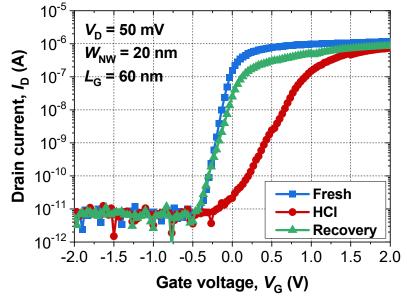

Figure 2 shows the simulated and experimental transfer characteristics of the a-IGZO TFTs under various N-doping conditions at  $V_{DS} = 5$  V. The simulation results, in consistency with the experimental data, were achieved by calibrating the  $D_{itA}$ ,  $N_{TA}$ ,  $N_{GA}(O_i)$  and  $N_{GD}(V_o^+/V_o^{2+})$ , and the simulation parameters are extracted and summarized in Table 1. The total trap density of the 20% N-doping ratio a-IGZO TFT was significantly decreased compared to the undoped a-IGZO TFT. For example, the  $D_{itA}$  is decreased from  $2.5 \times 10^{13} \, \mathrm{eV^{-1} \, cm^{-2}}$  to  $8.0 \times 10^{12} \, \mathrm{eV^{-1} \, cm^{-2}}$ , and the  $N_{TA}$  was reduced from  $8.0 \times 10^{19} \, \mathrm{eV^{-1} \, cm^{-3}}$  to  $1.0 \times 10^{19} \, \mathrm{eV^{-1} \, cm^{-3}}$ . Correspondingly, the subthreshold slope (SS) was decreased from 0.8 V/dec to 0.6 V/dec, and the threshold voltage (Vth) was reduced from 5.0 V to 3.8 V. It has been demonstrated that the interface states and bulk traps in a-IGZO TFTs mainly originate from Vo-related defects [5,15,24]. Therefore, the simulation results confirm that the improved electrical properties of a-IGZO TFTs can be ascribed to the suppression of the generation of Vo-related defects in the device channel and interface region by N-doping. In contrast, when the N-doping ratio was increased to 40%, the number of total trap states was increased compared to the 20% N-doping ratio TFT, as shown in Table 1. Meanwhile, it was observed that the SS and  $V_{th}$  of the 40% N-doping ratio device were increased to 0.9 V/dec and 7 V, respectively, which indicates that Vo-related defects generate when the device is subjected to excessive N-doping. This result can be explained by the fact that the formation of N-Ga bonds is facilitated by heavy N-doping, which then suppresses the bonding of Ga-O in the a-IGZO thin films [14,25].

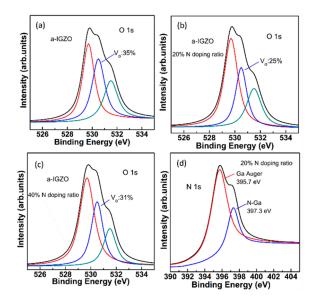

In addition, based on the simulation results, it was found that although the subgap DOS ( $N_{TA}$ ,  $N_{TD}$ ,  $N_{GD}(V_o$ -related),  $N_{GA}(O_i)$ , and  $N_{GD}(V_o^+/V_o^{2+})$ ) existing in the 40% N-doping ratio TFT was significantly higher than that of the 20% N-doping ratio TFT,

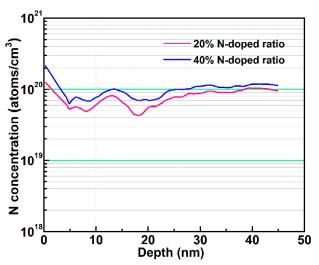

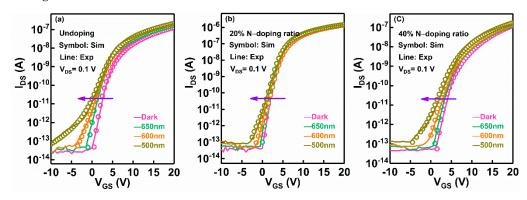

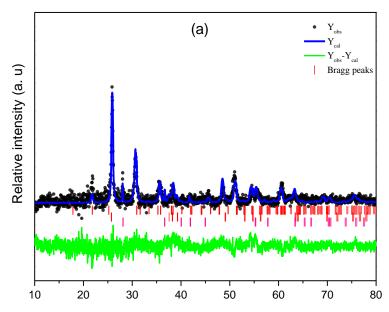

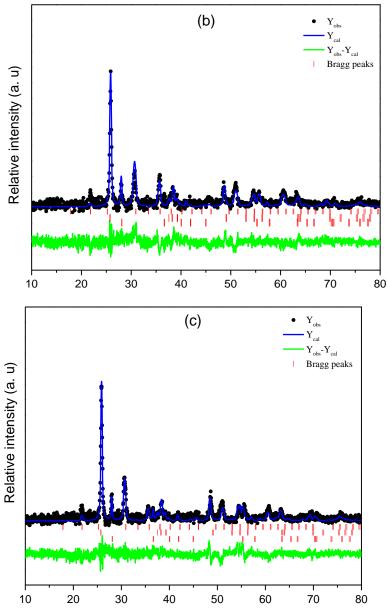

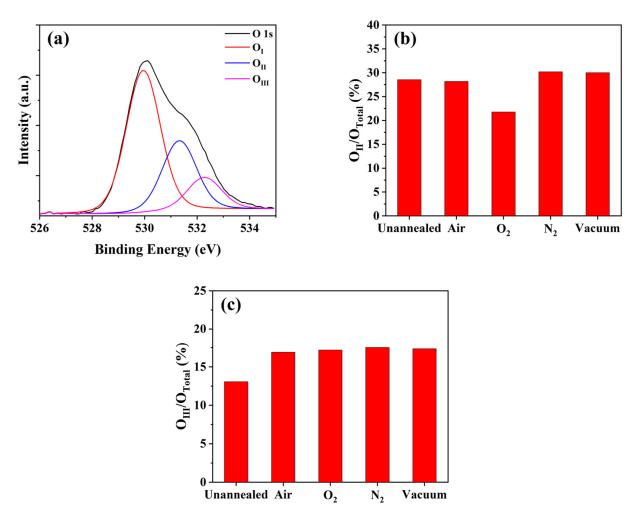

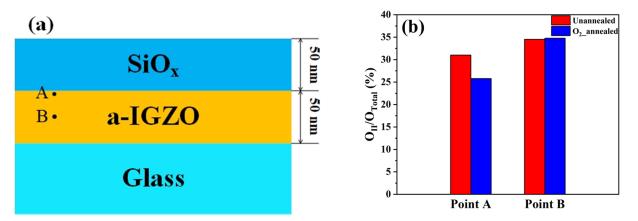

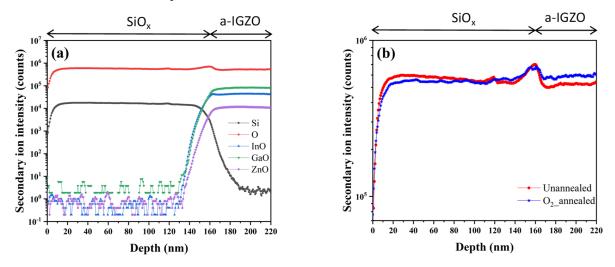

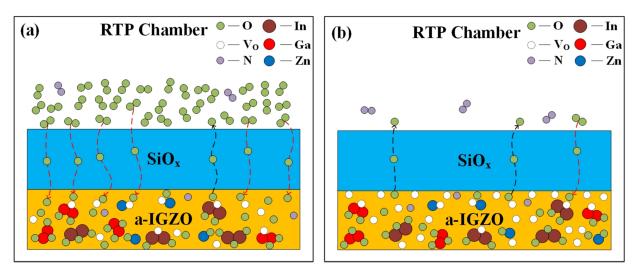

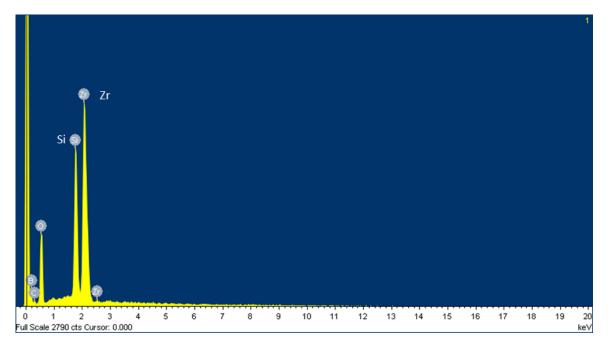

the sub-gap DOS other than  $N_{TA}$  was lower than that of the undoped TFT. Because the sub-band-gap density in a-IGZO film mainly originates from V<sub>0</sub>-related defects, the amount of Vo in annealed a-IGZO thin films with various N-doping ratios was analyzed by X-ray photoelectron spectroscopy (XPS). Figure 3a–c show the O 1 s XPS spectra of the a-IGZO films grown using different N-doped ratios. The binding energies were calibrated by taking the C 1s as reference at 284.6 eV. Gaussian fitting was applied to decompose the combined O 1s peak. The sub-peaks centered at binding energies of 529.7 eV, 530.5 eV, and 531.5 eV were attributed to  $O^{2-}$  ions surrounded by metal atoms (In, Ga and Zn), oxygen vacancies  $(V_o)$ , and OH<sup>-</sup> impurities, respectively [26–28]. The relative level of  $V_o$  in a-IGZO film can be estimated by the proportion of peak area Vo to the whole O 1s (Owhole). It was found that the area proportion of  $V_o/O_{whole}$  was decreased from 35% for N-free a-IGZO film to 25% for a-IGZO film with the 20% N-doped ratio, as shown in Figure 3a,b, indicating that  $V_0$ decreases when the N is incorporated into the a-IGZO film. However, as shown in Figure 3c, it was found that the V<sub>o</sub> increased to 31% for the a-IGZO film deposited with the 40% N-doped ratio, which means that the additional Vo was created when excess N atoms were doped into the a-IGZO film. Furthermore, the N 1s spectra XPS of the annealed a-IGZO film with 20% N-doped ratio was also analyzed, as shown in Figure 3d. The N 1 s spectrum is decomposed into two peaks at 395.7 and 397.3 eV, which are associated with the Ga Auger and N-Ga bonding [29], respectively. Therefore, the XPS results reveal that moderate N doping in a-IGZO film can suppress the generation of V<sub>o</sub>, and excess N incorporation into a-IGZO film leads to an increase in  $V_0$ . Because the  $V_0$  existing in the 40% N-doping ratio a-IGZO film was lower than that of undoped a-IGZO film, the increased  $N_{TA}$  in 40% N-doping ratio a-IGZO TFT should be the result of the generation of N-related defects by excess N-doping [16,30], which agrees well with the increased SS from 0.8 V/dec to 0.9 V/dec compared to undoped a-IGZO TFT. Meanwhile, to quantitatively estimate the N concentration in the a-IGZO active layer, the actual level of N-doping in annealed a-IGZO films is characterized by secondary ion mass spectrometry (SIMS) measurement [31–33]. Figure 4 shows the depth profile of N concentration in the a-IGZO film deposited with the 20% and 40% N-doped ratios. N is clearly detectable, and there is a considerable amount of incorporated nitrogen ( $\sim 10^{20}$  cm<sup>-3</sup>) in the a-IGZO film. It has been reported that the value of the sub-gap density of states (DOSs) near the VBMs is about  $5-9 \times 10^{20}$  cm<sup>-3</sup> in a-IGZO film [5,34]. In this work, it is found that when the concentration of N doping in the channel region of a-IGZO TFT with a 20% N doping ratio is  $\sim 1.0 \times 10^{20}$  cm<sup>-3</sup>, the electrical performance and stability of the device are dramatically improved. But when the concentration of N-doping in the channel region of a-IGZO TFT with a 40% N doping ratio is increased to  $\sim 1.2 \times 10^{20}$  cm<sup>-3</sup>, the electrical performance and stability of a-IGZO TFT are degraded.

**Figure 2.** Simulated transfer characteristics for a-IGZO TFTs with different N-doping conditions: undoped, 20% N-doping ratio, and 40% N-doping ratio.

| <b>Table 1.</b> Densities of key defect model parameters for a-IGZO TFT fitted after different N-doping ratio | <b>Table 1.</b> Densities of ker | v defect model | parameters for a- | -IGZO TFT fitte | ed after o | different N-do | oping ratios. |

|---------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|-------------------|-----------------|------------|----------------|---------------|

|---------------------------------------------------------------------------------------------------------------|----------------------------------|----------------|-------------------|-----------------|------------|----------------|---------------|

| Parameters                                                       | Undoping             | 20%<br>N-Doping<br>Ratio | 40%<br>N-Doping<br>Ratio | Description                            |

|------------------------------------------------------------------|----------------------|--------------------------|--------------------------|----------------------------------------|

| $\frac{D_{itA}}{(eV^{-1} cm^{-2})}$                              | $2.5 \times 10^{13}$ | $8.0 \times 10^{12}$     | $1.5 \times 10^{13}$     | Acceptor-like interface trap densities |

| $(eV^{-1} cm^{-2})$                                              | $3.0\times10^{13}$   | $9.0\times10^{12}$       | $2.0\times10^{13}$       | Donor-like interface trap densities    |

| $({\rm eV}^{-1}{\rm cm}^{-3})$                                   | $8.0 \times 10^{19}$ | $1.0\times10^{19}$       | $1.5\times10^{20}$       | Acceptor-like tail states at $E = Ec$  |

| $(eV^{-1} cm^{-3})$                                              | $1.5\times10^{20}$   | $8.0\times10^{19}$       | $1.3\times10^{20}$       | Donor-like tail states at $E = Ev$     |

| $N_{GD}(V_o	ext{-related}) \ (eV^{-1} 	ext{ cm}^{-3})$           | $8.0 \times 10^{20}$ | $5.0\times10^{20}$       | $6.5\times10^{20}$       | Peak of Vo-related states              |

| $N_{\rm GA}({ m O_i}) \ ({ m eV^{-1}~cm^{-3}})$                  | $2.6 \times 10^{17}$ | $1.4\times10^{17}$       | $2.1\times10^{17}$       | Peak of O <sub>i</sub> states          |

| $N_{GD}(V_o^+/V_o^{2+})$<br>(eV <sup>-1</sup> cm <sup>-3</sup> ) | $8.0\times10^{16}$   | $5.0\times10^{16}$       | $6.5\times10^{16}$       | Peak of $V_0^+/V_0^{2+}$ states        |

**Figure 3.** O 1s XPS spectra of the annealed a-IGZO films grown using N-doping ratio of (a) undoped, (b) 20% and (c) 40%. (d) N 1s XPS spectra of a-IGZO film grown with 20% N-doping ratio.

According to the distribution of the sub-gap DOS fitted in a-IGZO TFTs with various N-doping ratios, a comprehensive quantitative study on the device stability under positive bias stress (PBS) was carried out. During the PBS process, the TFTs were applied at a  $V_{\rm GS}$  of 15 V for the stress duration of 5000 s. Figure 5a–c show the experimental and simulated evolution of transfer characteristics as a function of PBS time for the a-IGZO TFTs with different N-doping ratios. It was found that the shift in threshold voltage ( $\Delta V_{\rm th}$ ) induced by PBS was 2.06 V, 0.8 V, and 1.68 V for undoped a-IGZO TFT, 20% N-doping a-IGZO TFT, and 40% N-doping a-IGZO TFT, respectively. It has been reported that the shift in  $V_{\rm th}$  ( $\Delta V_{\rm th}$ ) of a-IGZO TFTs under PBS basically originates from the interfacial  $V_{\rm o}$ -related defects trapping electrons at the device interfacial region [35,36]. In the simulation results, it was clearly seen that the  $D_{it}(E)$  for the 20% N-doping ratio a-IGZO TFT was lower than of the undoped a-IGZO TFT and 40% N-doping ratio a-IGZO TFT. For example, the  $D_{itA}$  for undoped a-IGZO TFT, 20% N-doped a-IGZO TFT, and 40% N-doped a-IGZO TFT

is  $2.5 \times 10^{13}~eV^{-1}~cm^{-2}$ ,  $8.0 \times 10^{12}~eV^{-1}~cm^{-2}$ , and  $1.5 \times 10^{13}~eV^{-1}~cm^{-2}$ , respectively, suggesting that interfacial  $V_o$ -related defects can be suppressed by moderate N-doping.

**Figure 4.** Depth profile of nitrogen in a-IGZO film deposited under 20% N-doping ratio and 40% N-doping ratio.

**Figure 5.** Simulated transfer characteristics against positive bias stress (PBS) time for the a-IGZO TFTs fabricated with different N-doping ratios: (a) undoped, (b) 20% N-doping ratio, and (c) 40% N-doping ratio.

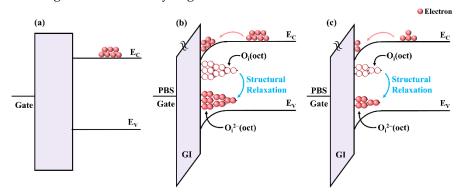

In addition, it has been reported that weak oxygen ions originating from structural disorder in a-IGZO TFTs cause  $\Delta V_{th}$  under PBS [37]. During the PBS process, the weak oxygen ions are ionized to generate oxygen interstitials ( $O_i$ ) because of their low formation energies [4,38,39]. Meanwhile, according to the first-principle studies, the generated  $O_i$  during PBS forms an octahedral configuration [ $O_i$ (oct)] and is electrically active. Correspondingly, the introduced  $O_i$ (oct)-related defect states are distributed above the mid-gap ( $E_i$ ) in the a-IGZO TFTs [40]. When the Fermi level moves up under PBS, the  $O_i$ (oct)-related states are filled by trapping electrons and thus negatively charged to generate  $O_i^{2-}$  oct) [41]. Figure 6a–c show the forming process of  $O_i^{2-}$ (oct)-related charged states in a-IGZO TFTs undergoing PBS. Because of the structural relaxation effect, the  $O_i^{2-}$ (oct)-related charged states are transformed into deep-level negative-U states, which are located below the midgap in the a-IGZO TFTs [37,42]. As a result, although new  $O_i^{2-}$ (oct)-related charged states are generated under the PBS process, the SS of a-IGZO TFTs has no apparent change due to the negative-U property of the  $O_i^{2-}$ (oct) states.

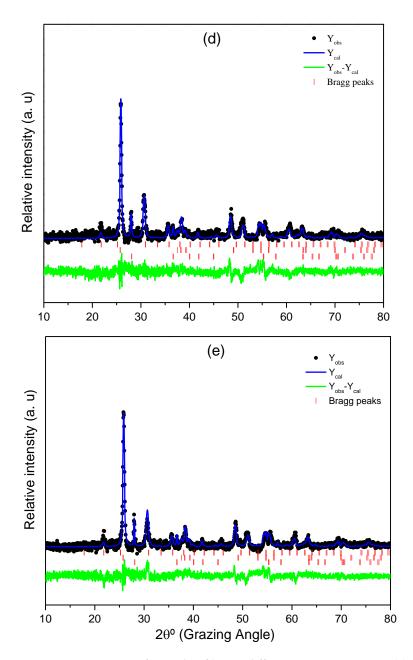

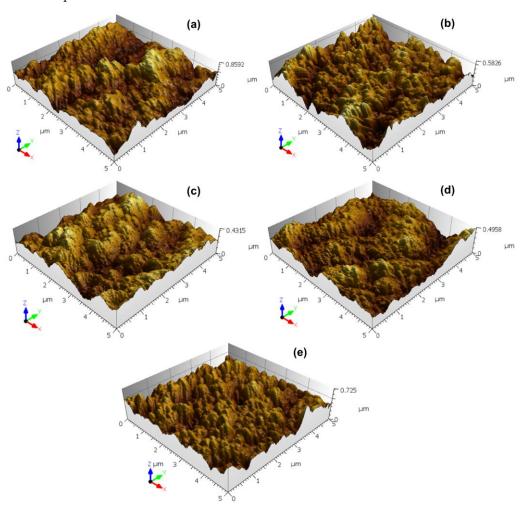

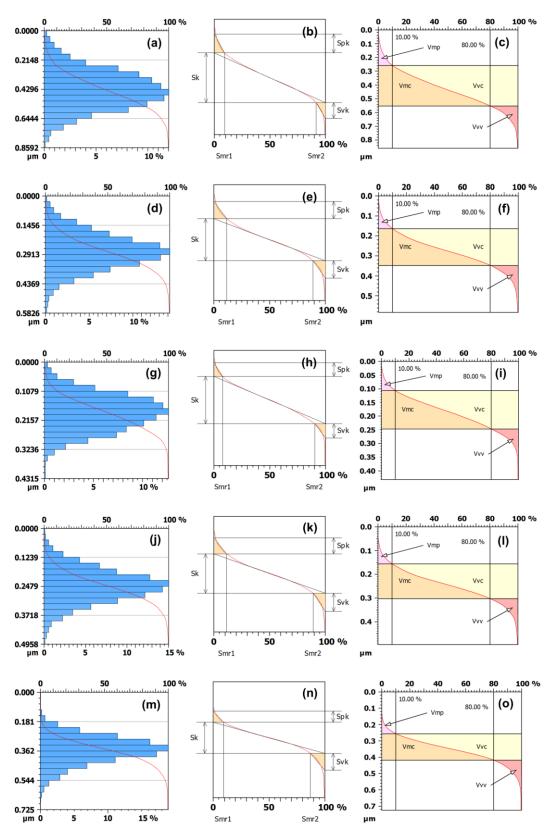

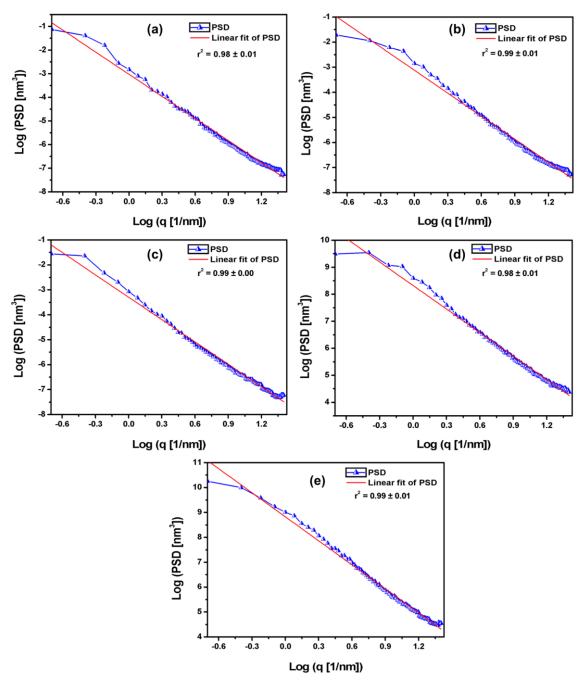

According to the simulation results,  $N_{GA}(O_i)$  exhibited an increasing trend for a-IGZO TFTs with various N-doping ratios under the PBS process, as shown in Table 2. For example, the  $N_{GA}(O_i)$  in the N-free a-IGZO TFT continuously increased from  $2.6 \times 10^{17} \, \mathrm{eV}^{-1} \, \mathrm{cm}^{-3}$  to  $3.6 \times 10^{17} \, \mathrm{eV}^{-1} \, \mathrm{cm}^{-3}$  after 5000 s PBS. This result shows that the  $O_i$ (oct)-related defects