Journal of Low Power Electronics and Applications

**Special Issue Reprint**

# Ultra-Low-Power ICs for the Internet of Things

Edited by Orazio Aiello

www.mdpi.com/journal/jlpea

## **Ultra-Low-Power ICs for the Internet** of Things

## Ultra-Low-Power ICs for the Internet of Things

Editor **Orazio Aiello**

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

*Editor* Orazio Aiello University of Genoa Italy

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Journal of Low Power Electronics and Applications* (ISSN 2079-9268) (available at: https://www.mdpi.com/journal/jlpea/special\_issues/low\_power\_iot).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-7902-3 (Hbk) ISBN 978-3-0365-7903-0 (PDF)

© 2023 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

## Contents

| About the Editor                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Orazio Aiello         Ultra-Low-Power ICs for the Internet of Things         Reprinted from: J. Low Power Electron. Appl. 2023, 13, 38, doi:10.3390/jlpea13020038 1                                                                                                                                                                       |

| Vincenzo Stornelli, Gianluca Barile, Leonardo Pantoli, Massimo Scarsella, Giuseppe Ferri,Francesco Centurelli, Pasquale Tommasino, et al.A New VCII Application: Sinusoidal OscillatorsReprinted from: J. Low Power Electron. Appl. 2021, 11, 30, doi:10.3390/jlpea11030030                                                               |

| Andrea Ballo, Salvatore Pennisi and Giuseppe Scotti0.5 V CMOS Inverter-Based Transconductance Amplifier with Quiescent Current ControlReprinted from: J. Low Power Electron. Appl. 2021, 11, 37, doi:10.3390/jlpea11040037 21                                                                                                             |

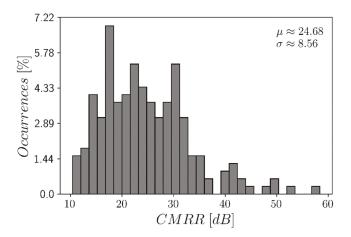

| Rafael Sanchotene Silva, Luis Henrique Rodovalho, Orazio Aiello and<br>Cesar Ramos Rodrigues                                                                                                                                                                                                                                              |

| A 1.9 nW, Sub-1 V, 542 pA/V linear Bulk-Driven OTA with 154 dB CMRR for Bio-Sensing Applications                                                                                                                                                                                                                                          |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2021</b> , <i>11</i> , 40, doi:10.3390/jlpea11040040 <b>31</b>                                                                                                                                                                                                                     |

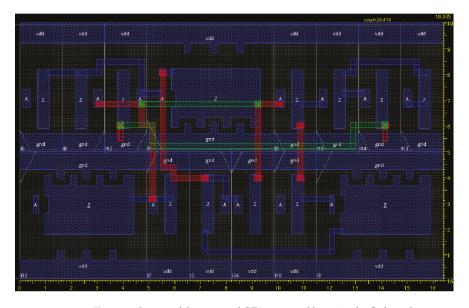

| Gaetano Palumbo and Giuseppe Scotti         A Novel Standard-Cell-Based Implementation of the Digital OTA Suitable for Automatic Place         and Route         Reprinted from: J. Low Power Electron. Appl. 2021, 11, 42, doi:10.3390/jlpea11040042                                                                                     |

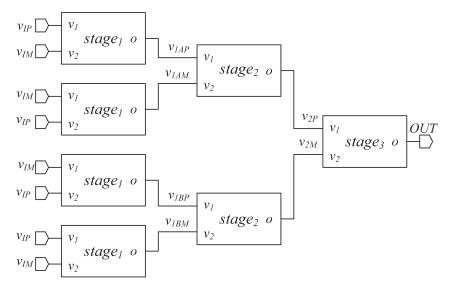

| Francesco Centurelli, Riccardo Della Sala, Pietro Monsurrò, Giuseppe Scotti and                                                                                                                                                                                                                                                           |

| Alessandro Trifiletti         A Tree-Based Architecture for High-Performance Ultra-Low-Voltage Amplifiers         Reprinted from: J. Low Power Electron. Appl. 2022, 12, 12, doi:10.3390/jlpea12010012                                                                                                                                    |

| Andrea Ballo, Salvatore Pennisi, Giuseppe Scotti and Chiara Venezia<br>A 0.5 V Sub-Threshold CMOS Current-Controlled Ring Oscillator for IoT and Implantable<br>Devices                                                                                                                                                                   |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2022</b> , <i>12</i> , <i>16</i> , doi:10.3390/jlpea12010016 <b>79</b>                                                                                                                                                                                                             |

| Francesco Centurelli, Riccardo Della Sala and Giuseppe ScottiA Standard-Cell-Based CMFB for Fully Synthesizable OTAsReprinted from: J. Low Power Electron. Appl. 2022, 12, 27, doi:10.3390/jlpea12020027 97                                                                                                                               |

| Cristina Missel Adornes, Deni Germano Alves Neto, MárcioCherem Schneider and<br>Carlos Galup-Montoro<br>Bridging the Gap between Design and Simulation of Low-Voltage CMOS Circuits                                                                                                                                                       |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2022</b> , <i>12</i> , <i>34</i> , doi:10.3390/jlpea12020034 <b>113</b>                                                                                                                                                                                                            |

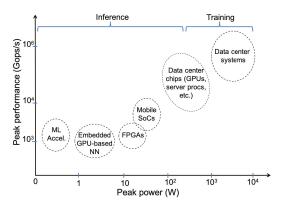

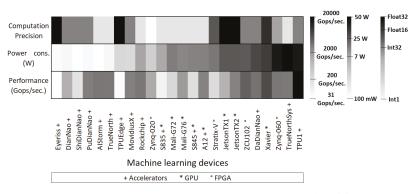

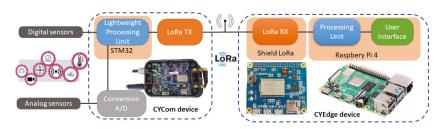

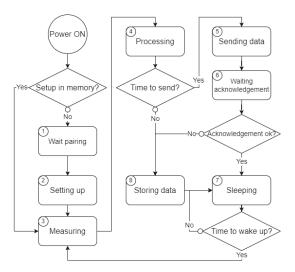

| Lucas Martin Wisniewski, Jean-Michel Bec, Guillaume Boguszewski and<br>Abdoulaye Gamatié<br>Hardware Solutions for Low-Power Smart Edge Computing<br>Reprinted from: J. Low Power Electron. Appl. 2022, 12, 61, doi:10.3390/jlpea12040061 133                                                                                             |

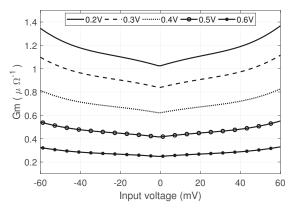

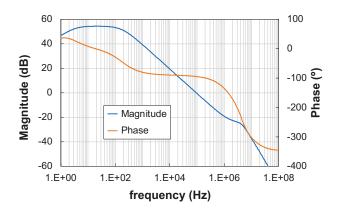

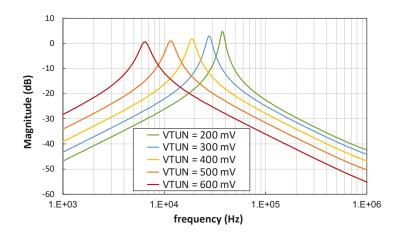

| Juan M. Carrillo and Carlos A. de la Cruz-Blas<br>$0.6-V$ 1.65-µW Second-Order $G_m$ -C Bandpass Filter for Multi-Frequency Bioimpedance<br>Analysis Based on a Bootstrapped Bulk-Driven Voltage Buffer<br>Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2022</b> , <i>12</i> , <i>62</i> , doi:10.3390/jlpea12040062 <b>157</b> |

#### Ana Correia, Vítor Grade Tavares, Pedro Barquinha and João Goes

| All-Standard-Cell-Based Analog-to-Digital Architectures Well-Suited for Internet of Things<br>Applications                    |

|-------------------------------------------------------------------------------------------------------------------------------|

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2022</b> , <i>12</i> , 64, doi:10.3390/jlpea12040064 <b>175</b>        |

| Israel Corbacho, Juan M. Carrillo, José L. Ausín, Miguel Á. Domínguez, Raquel Pérez-Aloe<br>and J. Francisco Duque-Carrillo   |

| A Fully-Differential CMOS Instrumentation Amplifier for Bioimpedance-Based IoT Medical                                        |

| Devices                                                                                                                       |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2023</b> , <i>13</i> , <i>3</i> , doi:10.3390/jlpea13010003 <b>189</b> |

| Arash Abbasi and Frederic Nabki                                                                                               |

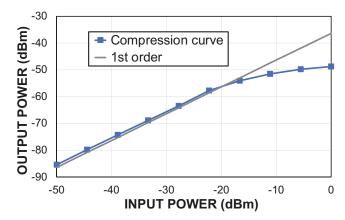

| Wideband Cascaded and Stacked Receiver Front-Ends Employing an Improved Clock-Strategy                                        |

| Technique                                                                                                                     |

| Reprinted from: <i>J. Low Power Electron. Appl.</i> <b>2023</b> , <i>13</i> , 14, doi:10.3390/jlpea13010014 <b>207</b>        |

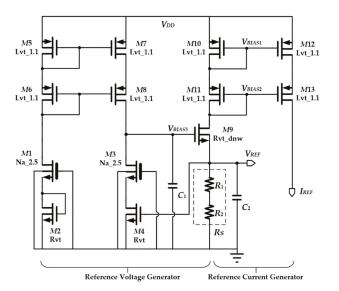

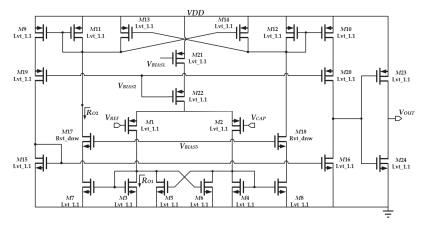

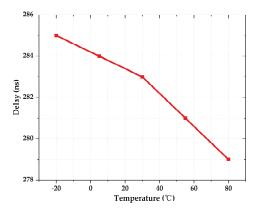

| Yizhuo Liao and Pak Kwong Chan                                                                                                |

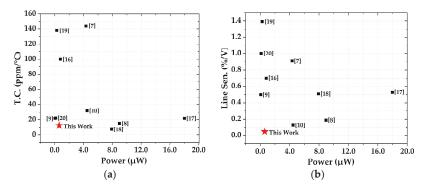

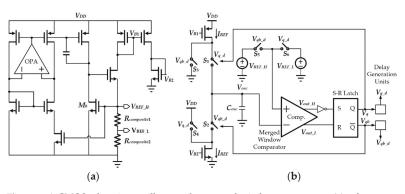

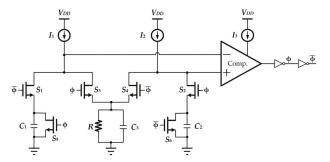

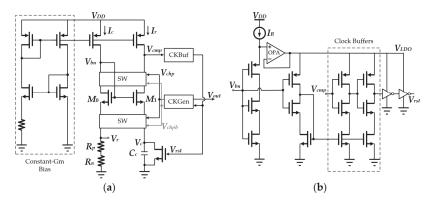

| A 1.1 V 25 ppm/°C Relaxation Oscillator with 0.045%/V Line Sensitivity for Low Power                                          |

| Applications                                                                                                                  |

| Reprinted from: J. Low Power Electron. Appl. 2023, 13, 15, doi:10.3390/jlpea13010015 223                                      |

### About the Editor

#### Orazio Aiello

Orazio Aiello received B.Sc. and M.Sc. degrees (cum laude) from the University of Catania, Italy, in 2005 and 2008, respectively, a M.Sc. degree (cum laude) from the Scuola Superiore di Catania, Italy, in 2009, and a Ph.D. degree from the Politecnico di Torino, Italy, in 2013. He has earned his technical background in worldwide universities R&D institutions, consultant activities, and direct work experience in semiconductor companies. He is currently a tenure-track assistant Professor at the University of Genoa, Italy. His main research interests include energy-efficient analog mixed-signal circuits and sensor interfaces.

#### Editorial Ultra-Low-Power ICs for the Internet of Things

Orazio Aiello

Department of Electrical, Electronics and Telecommunication Engineering and Naval Architecture (DITEN), University of Genoa, 16100 Genova, Italy; orazio.aiello@unige.it

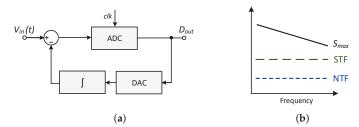

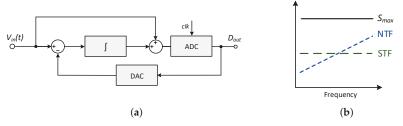

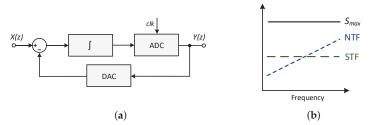

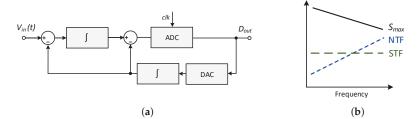

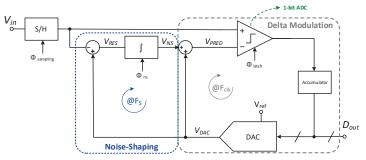

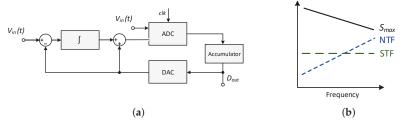

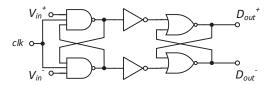

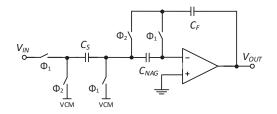

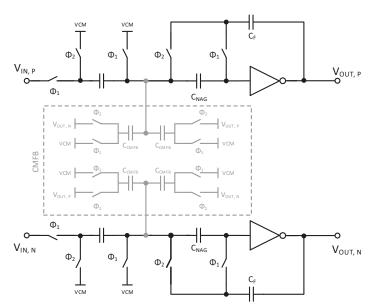

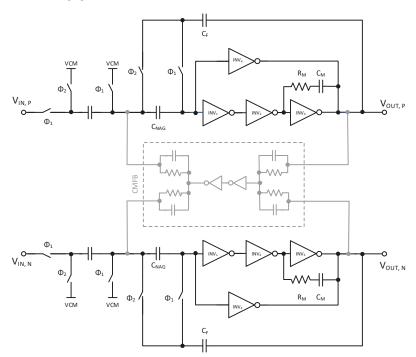

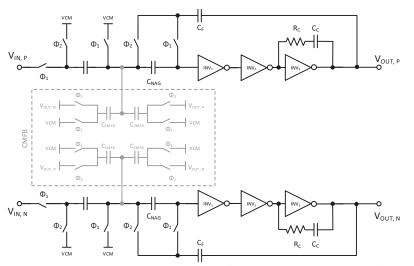

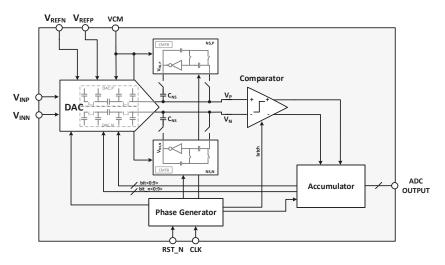

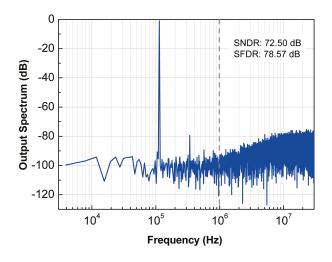

The collection of research works in this Special Issue focuses on Ultra-Low-Power (ULP) Integrated Circuits (ICs) operating under a tight budget of power as a criterion to build electronic devices relying less and less on batteries. These enable the Internet of Things (IoT): a view of a world in which we are surrounded by devices that exchange data to enhance our quality of living. Thus, the goals of novel IC design strategies target both reducing the cost and the power consumption of any device. A method to reduce the cost is to minimize the use of a manual design process and maximize the use of a digital (automated) design flow so that the design is transferable across technological nodes. A digital-in-concept design also allows the scale of the supply voltage and offers a performance-power consumption trade-off [1-4]. In particular, a two-stage inverter-based operational transconductance amplifier (OTA) using rail-to-rail output operating with a supply voltage of 0.5 V is presented in [1]. Then, a novel implementation of a digital-based OTA consisting of only digital gates usually available in the standard cell libraries is the focus of [2]. In [3], a novel fully standard-cell-based common-mode feedback (CMFB) loop to improve the CMRR and to stabilize the DC output voltage of pseudo-differential standard-cell-based amplifiers is proposed. To further explore complexity, dynamic performance, and energy efficiency, a fully synthesizable digital–delta ( $\Delta$ ) modulator ( $\Delta$ M) ADC with noise shaping using passive components (i.e., integrated capacitors and resistors) and standard-cell-based amplifiers is presented in [4].

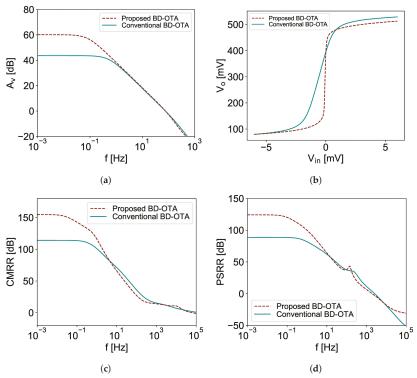

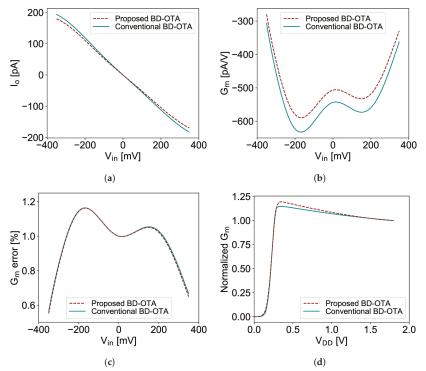

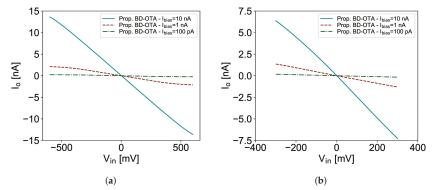

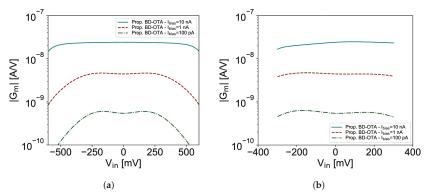

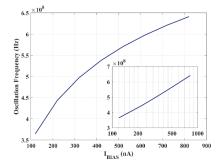

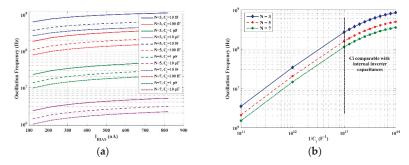

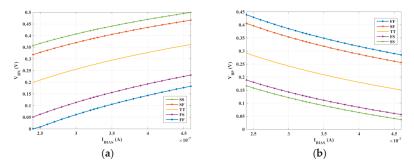

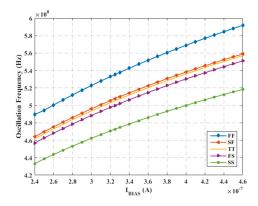

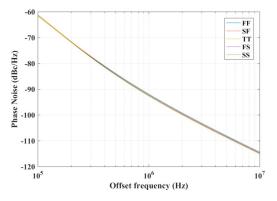

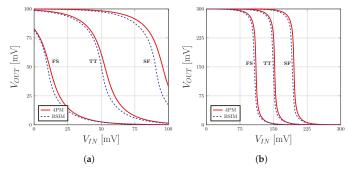

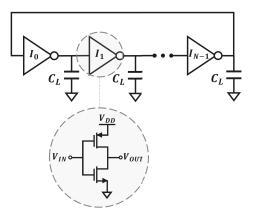

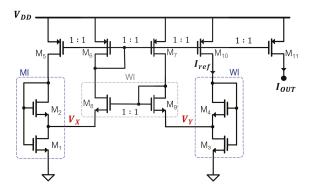

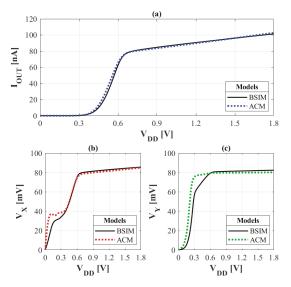

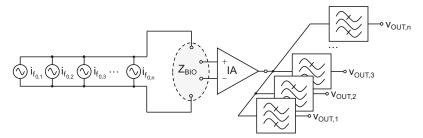

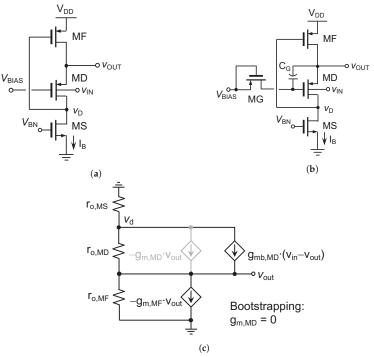

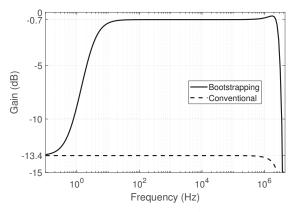

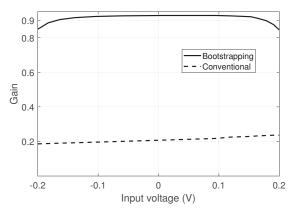

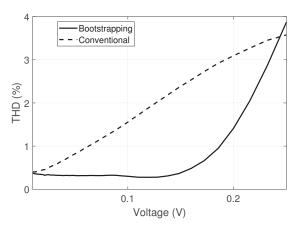

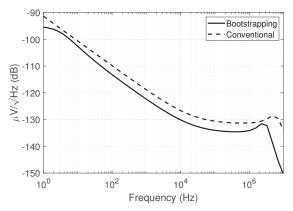

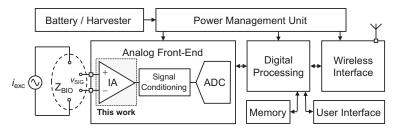

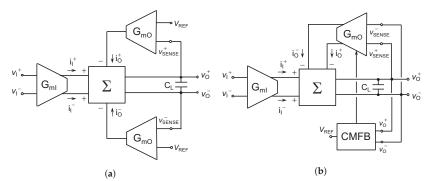

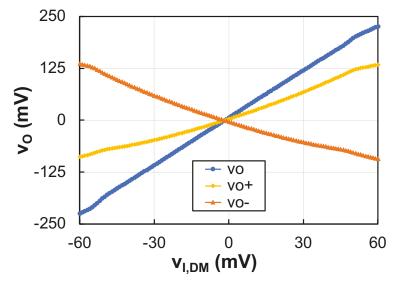

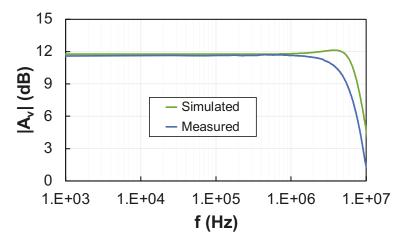

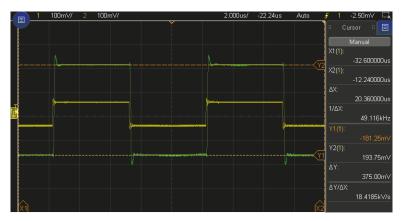

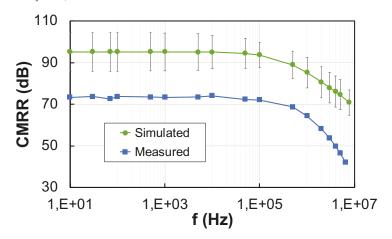

The other research works exploit other methods, focusing on increasing the energy efficiency for a number of building blocks for general-purpose applications (i.e., amplifiers); more specifically, they target biomedical applications or at the system level. ULP/Ultra-Low-Voltage (ULV) ICs exploring bulk-drive solutions and operating with Sub-1V supply voltage down to 0.3 V were considered [5–8]. In [5], the authors proposed a new technique to improve the DC voltage gain, while keeping the high linearity in symmetrical bulk-driven (BD) OTA topology. A novel tree-based architecture that allows the implementation of a ULV OTA exploiting a body-driven input stage to guarantee a rail-to-rail input common mode range is also described in [6]. A bootstrapped BD Voltage Buffer is used to increase the intrinsic voltage gain of the Second-Order Gm-C Bandpass Filter in [7]. Moreover, a current-controlled CMOS ring oscillator topology, which exploits the bulk voltages of the inverter stages as control terminals to tune the oscillation frequency, is proposed and analyzed in [8]. Then, a fully differential (FD) instrumentation amplifier aimed at electrical impedance measurements in an IoT biomedical scenario is presented in [9].

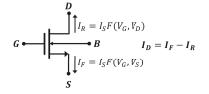

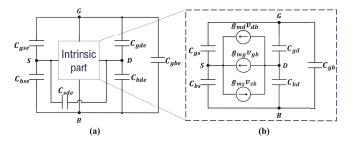

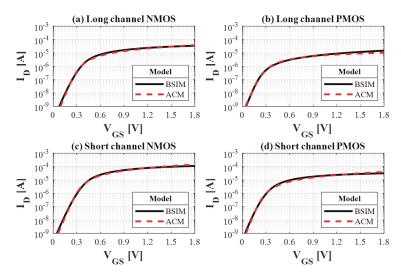

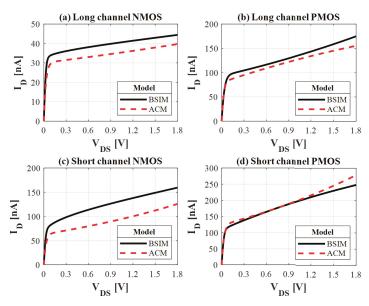

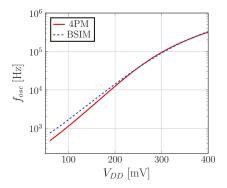

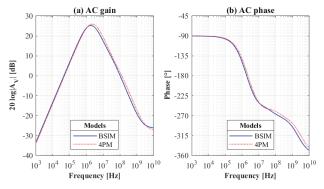

To assist the ULP IC design flow, a compact and simplified approach that contains only four parameters and is based on the Advanced Compact MOSFET (ACM) model was implemented in Verilog-A and compared with the BSIM model in [10].

Sinusoidal oscillators based on second-generation voltage conveyors are investigated in [11], while a relaxation oscillator with valuable line sensitivity for Low Power Applications is shown in [12].

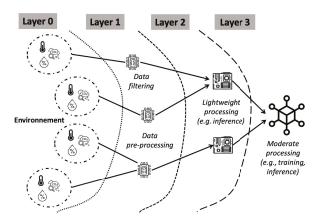

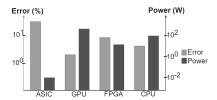

The last two studies in this Special Issue consider the IC as part of a ULP/ULV sensor system that needs to interact with the surrounding environment.

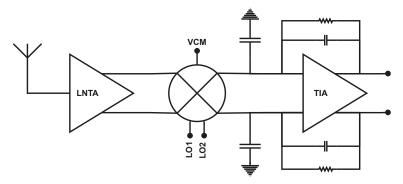

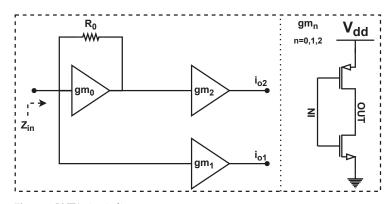

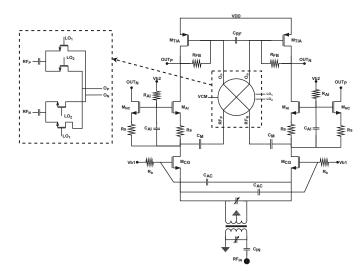

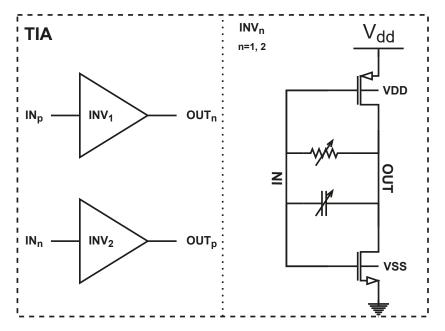

A wideband cascaded receiver including an inverter-based low-noise transconductance amplifier and a stacked receiver using an improved clock strategy with reduced mixer

Citation: Aiello, O. Ultra-Low-Power ICs for the Internet of Things. J. Low Power Electron. Appl. 2023, 13, 38. https://doi.org/10.3390/ jlpea13020038

Received: 23 May 2023 Accepted: 24 May 2023 Published: 26 May 2023

Copyright: © 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). switches is described in [13]. Hardware solutions for Low-Power Smart Edge Computing are presented in [14].

In summary, the published research works cover a wide area of the ULP/ULV IC field, offering the reader many ideas inspired by these innovative design approaches.

Acknowledgments: The Guest Editor of the Special Issue "Ultra-Low-Power ICs for the Internet of Things" thanks the Multidisciplinary Digital Publishing Institute (MDPI) for the invitation to write this Editorial as a presentation of the 14 papers published in this Special Issue which is freely available at https://www.mdpi.com/journal/jlpea/special\_issues/low\_power\_iot. Moreover, based on the success of this Special Issue, a "Volume 2" has been launched at https://www.mdpi.com/journal/jlpea/special\_issues/919Q5756T0.

Conflicts of Interest: The author declares no conflict of interest.

#### References

- Ballo, A.; Pennisi, S.; Scotti, G. 0.5 V CMOS Inverter-Based Transconductance Amplifier with Quiescent Current Control. J. Low Power Electron. Appl. 2021, 11, 37. [CrossRef]

- Palumbo, G.; Scotti, G. A Novel Standard-Cell-Based Implementation of the Digital OTA Suitable for Automatic Place and Route. J. Low Power Electron. Appl. 2021, 11, 42. [CrossRef]

- Centurelli, F.; Della Sala, R.; Scotti, G. A Standard-Cell-Based CMFB for Fully Synthesizable OTAs. J. Low Power Electron. Appl. 2022, 12, 27. [CrossRef]

- Correia, A.; Tavares, V.G.; Barquinha, P.; Goes, J. All-Standard-Cell-Based Analog-to-Digital Architectures Well-Suited for Internet of Things Applications. J. Low Power Electron. Appl. 2022, 12, 64. [CrossRef]

- Sanchotene Silva, R.; Rodovalho, L.H.; Aiello, O.; Ramos Rodrigues, C. A 1.9 nW, Sub-1 V, 542 pA/V Linear Bulk-Driven OTA with 154 dB CMRR for Bio-Sensing Applications. J. Low Power Electron. Appl. 2021, 11, 40. [CrossRef]

- Centurelli, F.; Della Sala, R.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A Tree-Based Architecture for High-Performance Ultra-Low-Voltage Amplifiers. J. Low Power Electron. Appl. 2022, 12, 12. [CrossRef]

- Carrillo, J.M.; de la Cruz-Blas, C.A. 0.6-V 1.65-µW Second-Order Gm-C Bandpass Filter for Multi-Frequency Bioimpedance Analysis Based on a Bootstrapped Bulk-Driven Voltage Buffer. J. Low Power Electron. Appl. 2022, 12, 62. [CrossRef]

- Ballo, A.; Pennisi, S.; Scotti, G.; Venezia, C. A 0.5 V Sub-Threshold CMOS Current-Controlled Ring Oscillator for IoT and Implantable Devices. J. Low Power Electron. Appl. 2022, 12, 16. [CrossRef]

- Corbacho, I.; Carrillo, J.M.; Ausín, J.L.; Domínguez, M.Á.; Pérez-Aloe, R.; Duque-Carrillo, J.F. A Fully-Differential CMOS Instrumentation Amplifier for Bioimpedance-Based IoT Medical Devices. J. Low Power Electron. Appl. 2023, 13, 3. [CrossRef]

- Adornes, C.M.; Alves Neto, D.G.; Schneider, M.C.; Galup-Montoro, C. Bridging the Gap between Design and Simulation of Low-Voltage CMOS Circuits. J. Low Power Electron. Appl. 2022, 12, 34. [CrossRef]

- 11. Stornelli, V.; Barile, G.; Pantoli, L.; Scarsella, M.; Ferri, G.; Centurelli, F.; Tommasino, P.; Trifiletti, A. A New VCII Application: Sinusoidal Oscillators. J. Low Power Electron. Appl. 2021, 11, 30. [CrossRef]

- Liao, Y.; Chan, P.K. A 1.1 V 25 ppm/°C Relaxation Oscillator with 0.045%/V Line Sensitivity for Low Power Applications. J. Low Power Electron. Appl. 2023, 13, 15. [CrossRef]

- Abbasi, A.; Nabki, F. Wideband Cascaded and Stacked Receiver Front-Ends Employing an Improved Clock-Strategy Technique. J. Low Power Electron. Appl. 2023, 13, 14. [CrossRef]

- 14. Martin Wisniewski, L.; Bec, J.-M.; Boguszewski, G.; Gamatié, A. Hardware Solutions for Low-Power Smart Edge Computing. J. Low Power Electron. Appl. 2022, 12, 61. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

#### Article A New VCII Application: Sinusoidal Oscillators

Vincenzo Stornelli <sup>1</sup>, Gianluca Barile <sup>1</sup>, Leonardo Pantoli <sup>1</sup>, Massimo Scarsella <sup>1</sup>, Giuseppe Ferri <sup>1,\*</sup>, Francesco Centurelli <sup>2</sup>, Pasquale Tommasino <sup>2</sup> and Alessandro Trifiletti <sup>2</sup>

- <sup>1</sup> Department of Industrial and Information Engineering and Economics, University of L'Aquila, 67100 L'Aquila, Italy; vincenzo.stornelli@univaq.it (V.S.); gianluca.barile@univaq.it (G.B.); leonardo.pantoli@univaq.it (L.P.); massimo.scarsella@student.univaq.it (M.S.)

- <sup>2</sup> Department of Information Engineering, Electronics and Telecommunications, Sapienza University of Rome, 00185 Rome, Italy; francesco.centurelli@uniroma1.it (F.C.); pasquale.tommasino@uniroma1.it (P.T.); alessandro.trifiletti@uniroma1.it (A.T.)

- Correspondence: giuseppe.ferri@univaq.it

Abstract: The aim of this paper is to prove that, through a canonic approach, sinusoidal oscillators based on second-generation voltage conveyor (VCII) can be implemented. The investigation demonstrates the feasibility of the design results in a pair of new canonic oscillators based on negative type VCII (VCII<sup>-</sup>). Interestingly, the same analysis shows that no canonic oscillator configuration can be achieved using positive type VCII (VCII<sup>+</sup>), since a single VCII<sup>+</sup> does not present the correct port conditions to implement such a device. From this analysis, it comes about that, for 5-node networks, the two presented oscillator configurations are the only possible ones and make use of two resistors, two capacitors and a single VCII<sup>-</sup>. Notably, the produced sinusoidal output signal is easily available through the low output impedance Z port of VCII, removing the need for additional voltage buffer for practical use, which is one of the main limitations of the current mode (CM) approach. The presented theory is substantiated by both LTSpice simulations and measurement results using the commercially available AD844 from Analog Devices, the latter being in a close agreement with the theory. Moreover, low values of THD are given for a wide frequency range.

Keywords: VCII; RC oscillator; sinusoidal oscillator; current mode; voltage conveyor application

#### 1. Introduction

There has always been an interest in designing sinusoidal oscillators due to several applications in different areas such as communication, instrumentation, biomedical, etc. [1–3]. Compared to LC and RLC sinusoidal oscillators, RC-active type oscillators are advantageous from the integration point of view. In the early implementations of RC-active sinusoidal oscillators, operational amplifiers (Op-Amps) were used as active elements [4–6]. A systematic approach was introduced in [5] to design Op-Amp-based oscillators with a single active element and the minimum number of passive elements. The design method of [5] resulted in Op-Amp-based oscillator configurations composed of one active device, two capacitors and four resistors.

However, the limited frequency performance and slew rate of Op-Amps as well as their high power consumption imposed a restriction in the application of Op-Ampbased sinusoidal oscillators. A literature survey shows that, after revealing the potential capabilities of current-mode (CM) signal processing, efforts have been made to design RC-active sinusoidal oscillators using various CM active building blocks (ABBs) [7–34]. Undoubtedly, second-generation current conveyor (CCII) as the main ABB of CM signal processing is the most widely used one for this purpose. Different approaches were employed to realize CCII-based oscillators. For example, in [8], the Op-Amps were replaced with composite current conveyors, resulting in CM oscillators. Unfortunately, this approach did not reach a simple realization because each amplifier could only be implemented with at least two CCIIs and two resistors. The extension of the approach presented in [5] was

Citation: Stornelli, V.; Barile, G.; Pantoli, L.; Scarsella, M.; Ferri, G.; Centurelli, F.; Tommasino, P.; Trifiletti, A. A New VCII Application: Sinusoidal Oscillators. *J. Low Power Electron. Appl.* **2021**, *11*, 30. https:// doi.org/10.3390/jlpea11030030

Academic Editor: Orazio Aiello

Received: 15 June 2021 Accepted: 6 July 2021 Published: 8 July 2021

Publisher's Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). employed in [9] to synthesize CCII-based oscillators. Although the resulting sinusoidal oscillators enjoyed a canonic structure with the minimum possible number of elements, they were still not readily cascadable, i.e., they required additional voltage buffers to be actually usable in a real-world application. Most of the other CM oscillator realizations reported in [10–34] using different ABBs instead of CCIIs also suffered from a large number of active and/or passive elements.

Recently, the dual circuit of CCII, called second-generation voltage conveyor (VCII), has attracted the attention of researchers [35–44]. In particular, the recent study reported in [35,36] showed that this device helps to benefit from CM signal processing features and overcome the limitations in CCII-based circuits. Particularly, unlike CCII, there is a low-impedance voltage output port in VCII which allows it to be easily cascaded with other high-impedance processing blocks, without the need for extra voltage buffers in voltage output applications. Compared to CCII, VCII has proven superior performance in many applications [37]; up to now, this device has not been employed in the realization of sinusoidal oscillators.

However, the VCII, combining the advantages of CM processing with a voltage-mode interfacing, could provide sinusoidal oscillators operating up to higher frequency than Op-Amp-based ones. Moreover, breaking the gain-bandwidth tradeoff, it could ease decoupling oscillation frequency and oscillation condition even at the higher end of the spectrum. Among the possible implementations of VCII-based sinusoidal oscillators, those requiring the minimum number of (active and) passive components, so-called canonic, are of particular interest to minimize silicon area and power consumption. The aim of this work is only to present possible VCII-based canonic sinusoidal oscillator realizations, replicating the general approach presented in [5,9] which, as previously anticipated, has been used to synthesize Op-Amp-based and CCII-based sinusoidal oscillators. We will show that it is possible to implement sinusoidal oscillators with a minimum number of elements using a single negative type VCII (VCII<sup>-</sup>), two resistors and two capacitors, so demonstrating a new practical application of the VCII. The notable advantage of the proposed VCII<sup>-</sup>-based oscillator is that it is easily cascadable from port Z of VCII<sup>-</sup>, alleviating the need for any extra voltage buffer. Moreover, THD values are low also for higher frequency oscillators. However, the results of this study show that the applied approach does not reach any canonic configuration using positive type VCII (VCII+). The effect of non-idealities in the VCII has been considered, and the proposed approach has been tested by both simulations and measurement results.

The organization of this paper is the following: in Section 2, an introduction on the VCII as active building block as well as the basics of the general configuration of the VCII-based oscillator is introduced. Section 3 proposes, in detail, the study on the possible realizations of VCII-based oscillators, and the effects of non-idealities in VCII are considered in Section 4. Simulations and measurement results are given in Section 5. Finally, Section 6 concludes the paper.

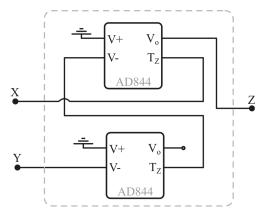

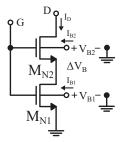

#### 2. General Configuration of the VCII-Based Oscillator

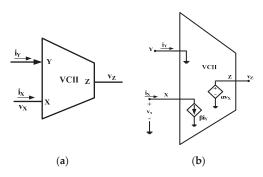

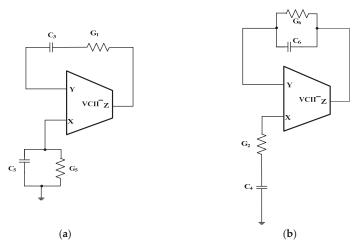

The symbolic representation and internal structure of VCII are shown in Figure 1. In this block, *Y* is a low-impedance (ideally zero) current input terminal. The current entering into *Y* node is transferred to *X* terminal which is a high-impedance (ideally infinity) current output port. The voltage produced at *X* terminal is transferred to *Z* terminal which is a low-impedance (ideally zero) voltage output terminal. The relationship between port currents and voltages are given by:  $v_Z = \alpha v_X$ ,  $i_X = \beta i_Y$  and  $v_Y = 0$ . In the ideal case we have  $\alpha = 1$  and  $\beta = \pm 1$ . If  $\beta = 1$  we are considering a VCII<sup>+</sup>, whereas if  $\beta = -1$  we have a VCII<sup>-</sup>.

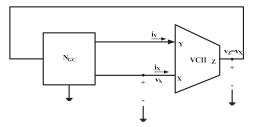

Using the approach presented in [5,9], the general configuration of an RC-active oscillator based on a single VCII is shown in Figure 2, where  $N_{GC}$  represents 4-terminal network consisting of only capacitors and conductances.

Figure 1. VCII: (a) symbol; (b) internal structure.

Figure 2. General configuration of RC-VCII oscillator.

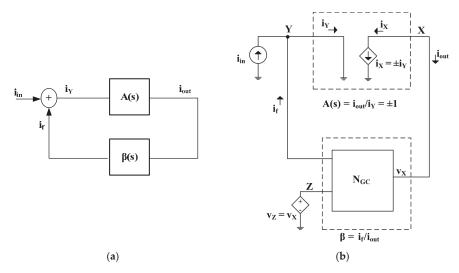

The characteristic equation (CE) of the whole system can be calculated replacing, in the circuit of Figure 2, the equivalent model of a VCII of Figure 1b and considering a fictitious input at the *Y* node (of course, no input signal will be present in an actual oscillator circuit), as shown in Figure 3a at the building block level and Figure 3b in more detail.

Figure 3. Positive feedback system: (a) general schematic; (b) positive feedback in the VCII-based oscillator.

The configurations in Figures 2 and 3 can hence be seen as a positive feedback system for which the current transfer function (TF) is given by:

$$T_I(s) = \frac{i_{out}(s)}{i_{in}(s)} = \frac{A(s)}{1 - A(s)\beta(s)}.$$

(1)

Since  $A(s) = \pm 1$  and  $\beta(s) = i_f(s)/i_{out}(s)$ , (1) becomes:

$$T_{I}(s) = \frac{\pm 1}{1 \mp i_{f}(s)/i_{out}(s)}.$$

(2)

However, since from Figure 3b  $i_{out} = -i_X$  and in an oscillator circuit there is no input  $(i_{in} = 0)$ , we have  $i_f = i_Y$  and the TF is given by:

$$T_I(s) = \frac{\pm 1}{1 \mp i_Y(s)/i_{out}(s)} = \frac{\pm i_X(s)}{i_X(s) \pm i_Y(s)}.$$

(3)

From (3), we can derive the condition of existence (CE) as:

$$i_X(s) \pm i_Y(s) = 0. \tag{4}$$

By assuming  $v_Z = v_X$ ,  $v_Y = 0$ , the transconductance functions of the passive network in Figure 2 can be expressed by a rational expression as:

$$\frac{i_X(s)}{v_Z(s)} = \frac{N_X(s)}{D(s)} \tag{5}$$

$$\frac{i_{Y}(s)}{v_{Z}(s)} = \frac{N_{Y}(s)}{D(s)}$$

(6)

where  $N_X(s)$  and  $N_Y(s)$  are the numerators at *X* and *Z* nodes, respectively, while D(s) is a common denominator. Using (5) and (6) in (4), the CE becomes:

$$N_X(s) \pm N_Y(s) = 0 \tag{7}$$

In (7), the plus and minus signs are for VCII<sup>-</sup> and VCII<sup>+</sup> respectively. To ensure a pure sinusoidal oscillation, the CE in (7) should be a second-order polynomial with purely imaginary roots. This requires the network N<sub>GC</sub> to include at least two capacitors. It has to be noted that, in Figure 2, by using a VCII<sup>+</sup> rather than a VCII<sup>-</sup>, at least three capacitors are required to provide a phase shift to generate a positive feedback loop. Therefore, no canonic oscillator is possible using VCII<sup>+</sup>, and for the following, we will consider the VCII in Figure 2 as a VCII<sup>-</sup>. By then assuming a network with only two capacitors, Equation (7) will be in the form:

$$as^2 + bs + c = 0. (8)$$

In order to start the oscillation, the following commonly known criteria must be satisfied:

b

$$= 0$$

(9)

$$\frac{c}{a} > 0 \tag{10}$$

with  $c \neq 0$ ,  $a \neq 0$ , so that, according to the Barkhausen criterion, purely imaginary poles for the closed-loop transfer function are obtained. The oscillation frequency is:

$$\omega_o = \sqrt{\frac{c}{a}} \,. \tag{11}$$

#### 3. Oscillator Circuits

In this section we analyze the possible VCII<sup>-</sup>-based oscillators based on the scheme of Figure 2. The passive N<sub>GC</sub> is assumed as a general *n*-node network consisting of *b* possible branches between two nodes. Each node is a junction where two or more branches are connected, and each branch is an admittance connected between two nodes represented as:

$$Y_i = sC_i + G_i. \tag{12}$$

In the following, we analyze the CE to see if oscillation is possible for the particular case study of a five-node network. From this analysis we see that for a four-node network it is not possible to obtain a second-order polynomial for (7), whereas for a six-node network (or more) only non-canonic oscillators using more than the minimum number of passive components are possible.

#### N<sub>GC</sub> as a Five-Node Network

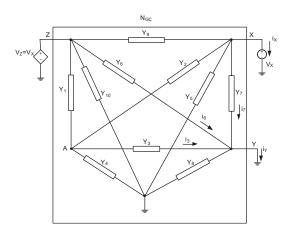

In Figure 4 we assume  $N_{GC}$  as a five-node network. We start analyzing this network by performing KCL at node Y as reported in the following:

$$i_Y = i_3 + i_6 + i_7 = i_3 + Y_6 V_Z + Y_7 V_Z.$$

<sup>(13)</sup>

Since no current is flowing into  $Y_8$  and  $Y_9$ , these admittances can be assumed as open circuit ( $Y_8 = Y_9 = 0$ ). Routine analysis of Figure 4 results in  $i_3$  as:

$$i_3 = \frac{Y_3(Y_1 + Y_2)}{Y_1 + Y_2 + Y_3 + Y_4} V_Z.$$

(14)

Using (13)–(14), we have:

$$\frac{i_Y}{V_Z} = \frac{Y_3(Y_1 + Y_2)}{Y_1 + Y_2 + Y_3 + Y_4} + Y_6 + Y_7.$$

(15)

Similar analysis for  $i_x$  results:

$\frac{i_X}{V_Z} = -\frac{Y_2(Y_3 + Y_4)}{Y_1 + Y_2 + Y_3 + Y_4} - Y_5 - Y_7$ (16)

Figure 4. The N<sub>GC</sub> as a five-node network.

Using (15) and (16) in (7), the CE of the five-node network is found as:

$$-Y_2Y_4 + Y_3Y_1 + (Y_6 - Y_5)(Y_1 + Y_2 + Y_3 + Y_4) = 0.$$

(17)

It can be noticed that CE does not depend on  $Y_7, \ldots, Y_{10}$  which means that these branches can be assumed to be open circuit. For the other branches we can make different choices. If two branches have non-zero admittances, the following CEs are possible:

$$Y_1, Y_3 \neq 0 \to CE : Y_1Y_3 = 0$$

(18a)

$$Y_1, Y_5 \neq 0 \to CE : Y_1 Y_5 = 0$$

(18b)

$$Y_1, Y_6 \neq 0 \to CE : Y_1 Y_6 = 0$$

(18c)

$$Y_2, Y_4 \neq 0 \to CE : Y_2 Y_4 = 0$$

(18d)

$$Y_2, Y_5 \neq 0 \to CE : Y_2 Y_5 = 0$$

(18e)

$$Y_2, Y_6 \neq 0 \to CE : Y_2 Y_6 = 0$$

(18f)

$$Y_3, Y_5 \neq 0 \to CE : Y_3 Y_5 = 0$$

(18g)

$$Y_3, Y_6 \neq 0 \to CE : Y_3 Y_6 = 0$$

(18h)

$$Y_4, Y_5 \neq 0 \to CE : Y_4 Y_5 = 0$$

(18i)

$$Y_4, Y_6 \neq 0 \to CE : Y_4 Y_6 = 0$$

(18j)

In the general case, (18) can be expressed as

$$CE: Y_a Y_b = 0 \tag{19}$$

By assuming  $Y_a = sC_a + G_a$  and  $Y_b = sC_b + G_b$ , (19) can be written as:

$$s^{2}C_{a}C_{b} + s[C_{a}G_{b} + C_{b}G_{a}] + G_{a}G_{b} = 0$$

<sup>(20)</sup>

From (20) it is not possible to have imaginary roots. Therefore, in case of two non-zero branches, no oscillation is possible.

Finally, we investigate the possibility of achieving oscillations from (17) in the case that three branches of  $N_{GC}$  present non-zero admittance.

For  $(Y_1 = Y_5 = Y_6 = 0)$  or  $(Y_3 = Y_5 = Y_6 = 0)$ , we have  $Y_2Y_4 = 0$ , while for  $(Y_2 = Y_5 = Y_6 = 0)$  or  $(Y_4 = Y_5 = Y_6 = 0)$ , we have  $Y_1Y_3 = 0$ . In both these cases, the CE has the general form of (19).

For  $(Y_1 = Y_2 = Y_5 = 0)$ ,  $(Y_1 = Y_2 = Y_6 = 0)$ ,  $(Y_1 = Y_4 = Y_5 = 0)$ ,  $(Y_1 = Y_4 = Y_6 = 0)$ ,  $(Y_2 = Y_3 = Y_5 = 0)$ ,  $(Y_2 = Y_3 = Y_6 = 0)$ ,  $(Y_3 = Y_4 = Y_5 = 0)$ ,  $(Y_3 = Y_4 = Y_6 = 0)$  the CE has the following form:

$$Y_c(Y_a + Y_b) = 0.$$

(21)

For  $(Y_1 = Y_3 = Y_6 = 0)$  and  $(Y_2 = Y_4 = Y_5 = 0)$ , the CE is obtained as:

$$Y_a Y_b + Y_c (Y_a + Y_b) = 0. (22)$$

The CEs of (21) and (22) do not result in pure imaginary roots; therefore, these cases cannot give oscillator topologies.

Considering instead the cases  $(Y_1 = Y_2 = Y_3 = 0)$ ,  $(Y_1 = Y_2 = Y_4 = 0)$ ,  $(Y_1 = Y_3 = Y_4 = 0)$ and  $(Y_2 = Y_3 = Y_4 = 0)$ , the CE has the following general form:

$$Y_c(Y_a - Y_b) = 0. (23)$$

It is easy to verify that the CE in (23) cannot be associated with an oscillator topology if only two capacitors are used (we need three of them at least).

Finally, for  $(Y_1 = Y_3 = Y_5 = 0)$  and  $(Y_2 = Y_4 = Y_6 = 0)$ , the CEs will be given by (24a) and (24b), respectively:

$$Y_2Y_4 - Y_6(Y_2 + Y_4) = 0 (24a)$$

$$Y_1Y_3 - Y_5(Y_1 + Y_3) = 0 (24b)$$

which are equations with the general form:

$$Y_a Y_b - Y_c (Y_a + Y_b) = 0. (25)$$

In (25), oscillation condition is related to the choice of  $Y_c$  and  $Y_a$  or  $Y_b$  as a capacitance. In order to design an oscillator with the minimum number of components, we now have to verify the choice of the components in (25). It can be demonstrated that it is possible to have a minimum of two capacitors and at least two resistors in order to have a constant term in the constituting equation. In fact, with this choice we obtain a complete polynomial. In this case, having only three branches of the type sC + G with  $C \ge 0$ ,  $G \ge 0$ , it is a matter of choosing an admittance between  $Y_a$ ,  $Y_b$ ,  $Y_c$  of the type sC + G; the two remaining admittances will be a capacitance sC, and a conductance *G*. Inserting all possible combinations of options into (25), two sets of CEs which show imaginary roots are obtained.

For  $Y_c = sC_c + G_c$ ;  $Y_a = sC_a$ ;  $Y_b = G_b$ , the CE becomes

$$-s^{2}C_{a}C_{c} + s[C_{a}G_{b} - C_{a}G_{c} - C_{c}G_{b}] - G_{b}G_{c} = 0.$$

(26)

For  $Y_c = sC_c + G_c$ ;  $Y_b = sC_b$ ;  $Y_a = G_a$ , the CE becomes

$$-s^{2}C_{b}C_{c} + s[C_{b}G_{a} - C_{c}G_{a} - C_{b}G_{c}] - G_{a}G_{c} = 0.$$

(27)

From (26) and (27), the oscillation condition ( $C_o$ ) and oscillation frequency ( $\omega_0$ ) for the two cases are obtained respectively as:

$$C_o: \frac{G_c}{G_b} + \frac{C_c}{C_a} = 1, \ \omega_0 = \sqrt{\frac{G_b G_c}{C_a C_c}}$$

(28a)

$$C_o: \frac{G_c}{G_a} + \frac{C_c}{C_b} = 1, \ \omega_0 = \sqrt{\frac{G_a G_c}{C_b C_c}}$$

(28b)

Thus, the minimum number of elements necessary to obtain an oscillator based on the scheme of Figure 2 is four, being two of these capacitors and two resistors. Considering the two cases ( $Y_1 = Y_3 = Y_5 = 0$ ) and ( $Y_2 = Y_4 = Y_6 = 0$ ) and the possible choices for  $Y_a$  and  $Y_b$ , we obtain a total of four canonic oscillators, corresponding to the following CEs:

$$-s^{2}C_{1}C_{5} + s[C_{1}G_{3} - C_{1}G_{5} - C_{5}G_{3}] - G_{3}G_{5} = 0$$

<sup>(29)</sup>

$$-s^{2}C_{3}C_{5} + s[C_{3}G_{1} - C_{3}G_{5} - C_{5}G_{1}] - G_{1}G_{5} = 0$$

(30)

$$s^{2}C_{2}C_{6} + s[C_{6}G_{4} + C_{2}G_{6} - C_{2}G_{4}] + G_{4}G_{6} = 0$$

(31)

$$s^{2}C_{4}C_{6} + s[C_{6}G_{2} + C_{4}G_{6} - C_{4}G_{2}] + G_{2}G_{6} = 0$$

(32)

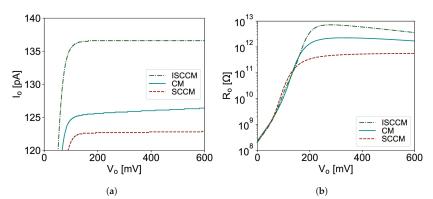

However, this number is reduced again to two if we consider that from each of the cases  $(Y_1 = Y_3 = Y_5 = 0)$  and  $(Y_2 = Y_4 = Y_6 = 0)$  we obtain two equal oscillators if we exchange the order of the elements which are connected in series. These two configurations are shown in Figure 5, and the corresponding transfer functions, oscillation frequencies  $\omega_0$  and oscillation conditions are reported in Table 1. The oscillation frequencies and oscillation conditions in (28) show a strong interdependence since they are functions of the same parameters. Since the oscillation condition requires that the sum of the ratios of the capacitances and of the conductances is constant and equal to 1, a possible strategy for frequency tuning requires varying both resistors or both capacitors, maintaining their ratio

constant. For example, a ratio of 2 between  $C_a$  and  $C_c$  can be obtained by using two parallel capacitors equal to  $C_a$  to obtain  $C_c$ ; all three capacitors can be varied together; thus their ratio remains constant unless there are mismatches and the effect of parasitics.

**Figure 5.** VCII-based oscillators obtained in the case NGC is a five-node network. (a)Series-parallel impedances configuration; (b) parallel-series impedances configuration.

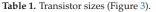

Table 1. Main equations of the canonic VCII-based oscillators.

| Figure 5a                                                                                                                                                                                                       | Figure 5b                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $T_{I}(s) = -\frac{s^{2}C_{5}C_{3}+s[C_{3}G_{1}+C_{3}C_{5}]+G_{5}G_{1}}{s^{2}C_{5}C_{3}+G_{5}G_{1}}$ $\omega_{0} = \sqrt{\frac{C_{5}C_{3}}{C_{5}C_{3}}}$ $C_{o}: \frac{C_{3}}{G_{1}} + \frac{C_{3}}{C_{3}} = 1$ | $T_{I}(s) = \frac{sC_{2}G_{2}}{s^{2}C_{4}C_{6}+C_{2}G_{6}}$ $\omega_{0} = \sqrt{\frac{C_{2}G_{6}}{C_{4}C_{6}}}$ $C_{o} : \frac{G_{6}}{G_{2}} + \frac{C_{6}}{C_{4}} = 1$ |

#### 4. Analysis of Parasitic Effects: A Case Study

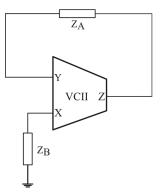

The only two possible canonic topologies for the VCII-based oscillator are synthesized in Figure 6, where  $Z_A$  and  $Z_B$  are a series-connected RC network and a parallel-connected RC network; we define  $t_A = R_A C_A$  and  $t_B = R_B C_B$  as the time constants associated with these networks. The two oscillator topologies shown in Figure 6 correspond to the cases:

Type I:

$$Z_A = \frac{R_5}{1 + sR_5C_5}$$

,  $Z_B = R_1 + \frac{1}{sC_3}$  (33a)

Type II :

$$Z_A = R_2 + \frac{1}{sC_4}$$

,  $Z_B = \frac{R_6}{1 + sR_6C_6}$ . (33b)

where  $R_i = 1/G_i$ . From Figure 6, the oscillation condition can be obtained as:

$$\alpha \ |\beta| \frac{Z_A}{Z_B} = 1 \tag{34}$$

where  $\beta$  and  $\alpha$  are the VCII current and voltage gains (ideally both equal to 1), and the oscillation frequency is given by:

$$\omega_0 = \frac{1}{\sqrt{\tau_A \tau_B}}.$$

(35)

The oscillation condition and the oscillation frequency are affected by the non-idealities of the VCII, i.e., finite port impedances, gain errors (a < 1, |b| < 1) and poles of the voltage and current buffers. In order to analyze the effects of these non-idealities on the oscillator

behavior, a model of a real VCII has been developed and implemented (see Figure 7), able to take into account the non-idealities.

Figure 6. General topology of the canonic VCII-based oscillators.

Figure 7. Model for the Type I canonic oscillator with non-ideal VCII.

In the general case, we can model the VCII with the first-order transfer functions

$$\alpha(s) = \alpha_0 / (1 + s\tau_z) \tag{36}$$

$$\beta(s) = -\beta_0 / (1 + s\tau_x) \tag{37}$$

and complex port impedances

$$Y_x(s) = G_x + sC_x \tag{38}$$

$$Z_y(s) = R_y + sL_y \tag{39}$$

$$Z_z(s) = R_z + sL_z. ag{40}$$

In order to better understand the effects of non-idealities and to compare the performance of the two topologies in Figure 5, different cases have been considered under the hypothesis that the ideal design has been carried out starting from the oscillation condition (34). When the non-idealities of the VCII are taken into account, Equation (34) becomes

$$\alpha(s)|\beta(s)|\frac{1}{Z_B + Z_y + Z_z}\frac{1}{1/Z_A + Y_x} = 1.$$

(41)

By a simple inspection of the impedances  $Z_A$  and  $Z_B$  given by (33), and of the port impedances (38)–(40), it is evident that the Type I canonic oscillator should be less affected by non-idealities. In fact, in this case  $Y_x$  can be absorbed in  $Z_A$  ( $G_x$  and  $C_x$  are summed to  $1/R_5$  and  $C_5$ , respectively), and  $Z_y$  and  $Z_z$  in  $Z_B$ : a parallel RC network is used in parallel to a port impedance modeled as an RC parallel network, and a series impedance is connected in series to port impedances modeled as RL series networks. In contrast, for the Type II canonic oscillator, a series network is connected in parallel to the parallel RC port impedance, and a parallel RC network is connected in series to LR series port impedances, thus non-ideal port impedances alter  $Z_A$  and  $Z_B$  more significantly. The Type I canonic VCII-based oscillator seems therefore more suited to a practical realization, and it has been selected for further analysis.

#### 4.1. Resistive Port Impedances

If only the resistive parasitics  $G_x$ ,  $R_y$  and  $R_z$  in (39)–(41) are considered, the oscillation condition for the Type I canonic oscillator becomes:

$$\frac{\alpha |\beta| s(R_5||R_x)C_3}{[1+s(R_5||R_x)C_5][1+s(R_1+R_y+R_z)C_3]} = 1.$$

(42)

It is evident from (42) that the effect of the port impedances is limited, since they are simply summed to the ones from the NGC network (that have to be chosen as much larger than the corresponding parasitics to make them negligible). The oscillation frequency in Table 1 is modified as follows:

$$\omega_0' = \sqrt{\frac{G_5'}{C_5 C_3 R_1'}} = \omega_0 \cdot \sqrt{\frac{1 + G_x / G_5}{1 + G_1 (R_y + R_z)}}$$

(43)

where  $R_1' = R_1 + R_y + R_z$  and  $G_5' = 1/R_5' = G_5 + G_x$ , and the oscillation condition becomes

$$\frac{\alpha |\beta|}{\frac{R_1}{R_5} \left(1 + \frac{R_5}{R_x}\right) \left(1 + \frac{R_y + R_z}{R_1}\right) + \frac{C_5}{C_3}} = 1.$$

(44)

If the parasitic capacitance  $C_x$  at the X terminal is also considered, Equations (43) and (44) have to be slightly modified by considering  $G_5' = C_5 + C_x$  instead of  $C_5$ . Inductances  $L_y$  and  $L_z$  can be neglected in several applications and have not been considered in the following. However, for the sake of completeness, we report below the expression for the oscillation frequency when inductive parasitics are also considered:

$$\omega_0' = \omega_0 \cdot \sqrt{\frac{1 + G_x/G_5}{(L_y + L_z)(1 + G_x/G_5)\frac{G_5G_1}{C_5} + (1 + C_x/C_5)[1 + G_1(R_y + R_z)]}}$$

(45)

#### 4.2. Single-Pole Transfer Functions

If the non-ideal transfer functions in (36) and (37) are also considered in addition to the terminal resistive parasitics in (38)–(40), the denominator of the oscillation condition in (34) becomes of fourth degree:

$$\frac{\alpha |\beta| sG_5'R_5'}{as^4 + bs^3 + cs^2 + ds + e} = 1$$

(46)

Prime variables are considered for  $R_5'$ ,  $G_5'$  and  $R_1'$  to account for parasitic resistances  $R_y$  and  $R_z$  and admittance  $Y_x$ , as in the previous subsection, and we have

$$a = R_5' C_5' R_1' C_3 \tau_x \tau_z \tag{47a}$$

$$b = R_5' C_5' R_1' C_3 \cdot (\tau_x + \tau_z) + \tau_x \tau_z \cdot (R_5' C_5' + R_1' C_3)$$

(47b)

$$c = R_5' C_5' R_1' C_3 + \tau_x \tau_z + (R_5' C_5' + R_1' C_3) \cdot (\tau_x + \tau_z)$$

(47c)

$$d = R_5' C_5' + R_1' C_3 + \tau_x + \tau_z \tag{47d}$$

$$e = 1$$

(47e)

A real value is obtained for the left-hand side, under the hypothesis of a purely imaginary denominator. By equating to zero the real part of the denominator at  $\omega = \omega_0$ , we get:

$$\omega_0'^2 = \frac{c}{2a} \left( 1 - \sqrt{1 - \frac{4a}{c^2}} \right) \cong \frac{c}{2a} \left( \frac{1}{2} \frac{4a}{c^2} \right) = \frac{1}{c}$$

(48)

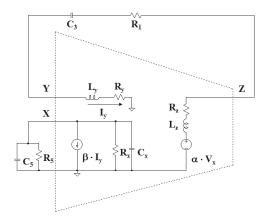

where *c* is given by (47*c*). The approximation  $\frac{4a}{c^2} << 1$  is justified under the hypothesis that the parasitic time constants  $\tau_x$  and  $\tau_z$  are significantly lower than the time constants  $\tau_A = R_5'C_5'$  and  $\tau_B = R_1'C_3$ . Finally, the oscillation frequency  $\omega_0'$  can be expressed in terms of the ideal value  $\omega_0$ , by using the expression of coefficient *c*:

$$\omega_0' \cong \frac{1}{\sqrt{c}} = \omega_0 \frac{1}{\sqrt{1 + \frac{\tau_x \tau_z + (\tau_A + \tau_B)(\tau_x + \tau_z)}{\tau_A \tau_B}}}$$

(49)

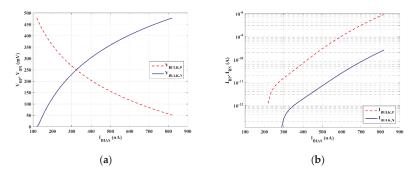

Under the simplifying assumptions  $\tau_x = \tau_y = \tau_{par}$  and  $\tau_A = \tau_B = \tau$ , the relative error on the oscillation frequency  $(1 - \omega_o'/\omega_o)$  can be readily expressed as a function of the ratio  $\tau_{par}/\tau$ , thus providing a design guideline for the bandwidth of the VCII transfer functions. The graph in Figure 8 shows that errors lower than 10% can be obtained if the time constant ratio is lower than 0.06.

**Figure 8.** Relative error on the oscillation frequency vs. the time constant ratio  $\tau_{par}/\tau$ .

#### 5. Experimental Results

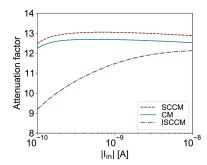

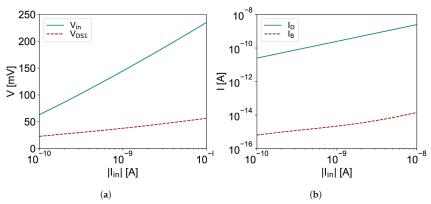

The performance of the Type I canonic oscillator of Figure 5a has been verified by both LTSpice simulations and experimental results. In particular, the approximated expression for  $\omega_0$  in (49) has been checked for different values of  $\tau$  and  $\tau_x = \tau_z$ , and errors lower than 1% have been found.

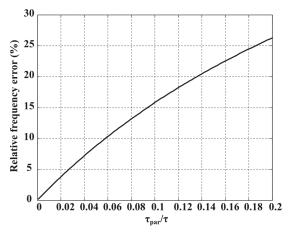

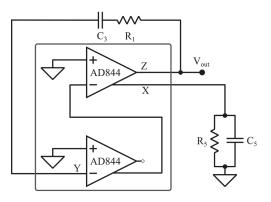

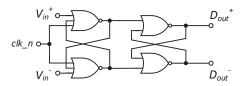

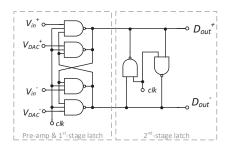

Then, we have used the commercially available AD844 to configure a VCII<sup>–</sup> as shown in Figure 9. A single VCII is realizable using two AD844 ICs, whose Spice model can be found in [45]. The situation is quite different in the case of an integrated design, where a single VCII block can be exploited to design the oscillator, as shown in the previous sections.

The circuit was supplied with a dual  $\pm 5$  V voltage, achieving a total power consumption of 14 mA.

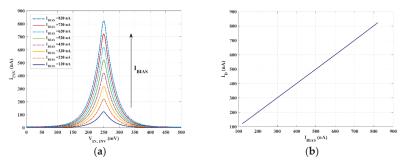

Firstly, simulation of the topology in Figure 5a has been carried out to evaluate performance in terms of robustness to parasitics, and to estimate the achievable THD. In particular, the circuit has been designed with  $C_3 = 2C_5 = 2 \text{ nF}$  and  $R_5 = 2R_1 = 15 \text{ k}\Omega$ , and an oscillation frequency  $f_0 = 10.6 \text{ kHz}$  was expected.

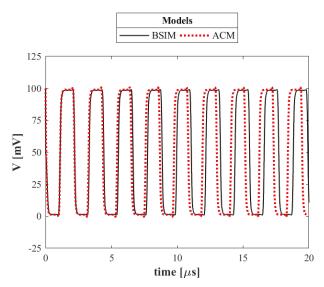

However, AD844 parasitics can slightly change the oscillation frequency and/or cause failing of oscillation condition: in this case, starting from the nominal design, the resistance  $R_1$  can be changed (to 7.3 k $\Omega$  in the present case, see the schematic in Figure 10) to allow fulfillment of oscillation condition in (41): the obtained oscillation frequency is  $f_0 = 10.8$  kHz, as shown in Figure 11.

A model for the VCII composed of AD844 components, shown in Figure 9, has been extracted from Spice simulations according to the equations presented in Section 4. At terminal *X*, we have found  $C_x = 5.5$  pF in parallel with a resistor  $R_x = 3$  M $\Omega$ . Purely resistive input impedances have been extracted at node *Y* ( $R_y = 50$   $\Omega$ ) and *Z* ( $R_z = 15$   $\Omega$ ). Finally, a dominant pole has been found for both the transfer function  $\alpha(s)$  at f = 49 MHz (corresponding to  $\tau_x = 3.25$  ns), and for  $\beta(s)$  at f = 764 MHz ( $\tau_z = 208$  ps).

Figure 9. Realization of a VCII<sup>-</sup> using the AD844.

Figure 10. VCII oscillator based on the AD844.

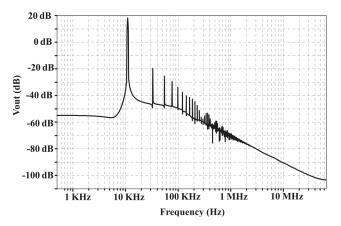

The element values used for the different design case studies, the simulated THD and the oscillation frequency evaluated with both the LTSpice AD844 non-linear model and with the VCII linear model, including parasitics, are summarized in Table 2. The linear model is accurate enough to be used for circuit design, and excellent simulated performance has been achieved in terms of THD with the proposed VCII topology.

Figure 11. Simulated output spectrum of the oscillator shown in Figure 10.

Table 2. Simulation results at different frequencies.

| $C_3 = 2C_5$ (nF) | R <sub>5</sub><br>(kΩ) | R <sub>1</sub><br>(kΩ) | f <sub>0</sub> (Spice)<br>(Hz) | f <sub>0</sub> (Model)<br>(Hz) | f <sub>0</sub> Error<br>(%) | THD<br>(%) |

|-------------------|------------------------|------------------------|--------------------------------|--------------------------------|-----------------------------|------------|

| 2000              | 15                     | 7.3                    | 10.8                           | 10.74                          | 0.6                         | 0.7        |

| 200               | 15                     | 7.35                   | 107.3                          | 107.0                          | 0.3                         | 0.4        |

| 20                | 15                     | 7.35                   | 1.073 K                        | 1.070 K                        | 0.3                         | 0.4        |

| 2                 | 15                     | 7.3                    | 10.80 K                        | 10.70 K                        | 0.9                         | 0.5        |

| 0.2               | 15                     | 6.9                    | 108.1 K                        | 107.2 K                        | 0.9                         | 0.7        |

| 0.2               | 1.5                    | 0.65                   | 1.080 M                        | 1.040 M                        | 3.7                         | 1.7        |

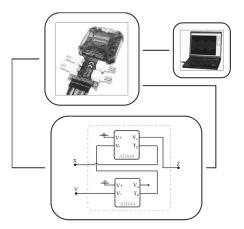

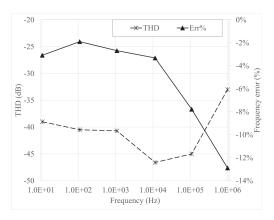

Finally, experimental verification of performance has been carried out, exploiting the test bench shown in Figure 12: for data acquisition, the Digilent Analog Discovery  $2^{TM}$  board was used [46]. The design of Figure 5a was implemented as the reference topology for the oscillator. Measurements were carried out in the range  $(10-10^6)$  Hz and are reported in Table 3. In agreement with simulation results, the oscillator shows a very low THD value even at 1 MHz (considering 10 harmonics). The average relative frequency error between measured and ideal values is -5.2% and is comparable with tolerances of the passive components.

Figure 12. Test bench for the experimental verification of the VCII oscillator based on the AD844.

| R1<br>(kΩ) | R5<br>(kΩ) | C3<br>(F) | C5<br>(F) | Ideal<br>Frequency (Hz) | Measured<br>Frequency (Hz) | Error<br>(%) | THD<br>(%) |

|------------|------------|-----------|-----------|-------------------------|----------------------------|--------------|------------|

| 15         | 6.8        | 2 μ       | 1μ        | 11.1                    | 10.8                       | -3           | 1.12       |

| 15         | 6.8        | 200 n     | 100 n     | 111                     | 109                        | -1.9         | 0.94       |

| 15         | 6.8        | 20 n      | 10 n      | 1.11 k                  | 1.08 k                     | -2.7         | 0.92       |

| 15         | 6          | 2 n       | 1 n       | 11.9 k                  | 11.5 k                     | -3.3         | 0.47       |

| 15         | 6          | 200 p     | 100 p     | 119 k                   | 109 k                      | -7.8         | 0.56       |

| 15         | 0.64       | 200 p     | 100 p     | 1.15 M                  | 1.0 M                      | -12.9        | 2.24       |

Table 3. Measured results.

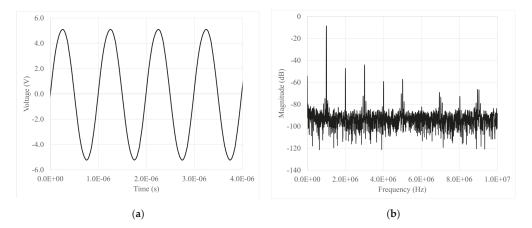

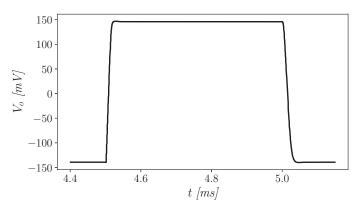

An example of the output signal, both in the time and frequency domains, is reported in Figure 13a,b for a frequency of 1 MHz.

Figure 13. Output waveform of the canonic VCII-based oscillator of Figure 5a. (a) Time domain, (b) frequency domain for an output frequency of 1 MHz.

Figure 14 shows the THD and frequency error trends vs. frequency.

Figure 14. THD and frequency error vs. frequency.

#### 6. Conclusions

By means of a systematic analysis, the possibility of realizing VCII-based oscillators is studied and demonstrated. The investigation results in a pair of new canonic oscillators

based on VCII<sup>-</sup>. However, it is shown that, using the systematic approach, no oscillator configuration is possible using VCII+. The two found oscillator configurations are the only possible ones which use only two resistors, two capacitors and a single VCII<sup>-</sup>. Compared to Op-Amp-based oscillators, designed using the same systematic approach which employs two capacitors and four resistors, the proposed VCII-based oscillator is preferred in terms of low number of capacitors and resistances. Another interesting feature of the found VCII-based oscillator is that the produced sinusoidal output signal is easily available through the low output impedance Z port, while the CCII-based oscillators designed using the same systematic approach requires an additional voltage buffer for practical use. Simulations and experimental results using AD844 as VCII are reported to validate the theory.

A comparison with oscillator topologies based on different ABBs, with particular attention to canonic topologies, is reported in Table 4. The table reports the type of active building block (ABB) the oscillator is based on, the number of active and passive components, specifying how many of them are grounded, the availability of a quadrature output and the independence of oscillation condition from oscillation frequency that allows tuning the oscillator acting on a single component. It has to be noted that the independence from the oscillation condition on oscillation frequency often requires additional passive (and sometimes also active) components, thus resulting in non-canonic topologies. Notable exceptions are the oscillators of [21,26] that use complex ABBs with gain, whose value contributes to satisfying the oscillation condition.

| Ref.      | АВВ Туре | ABB<br>Number | C<br>(Grounded) | R<br>(Grounded) | Output<br>Phases | Indep.<br>w <sub>o</sub> /C <sub>o</sub> |

|-----------|----------|---------------|-----------------|-----------------|------------------|------------------------------------------|

| [5]       | Op-Amp   | 1             | 2 (2)           | 4 (2)           | 1                | NO                                       |

| [7]       | OTA      | 3             | 2 (2)           | -               | 2                | YES                                      |

| [9]       | CCII     | 1             | 2 (2)           | 2 (1)           | 1                | NO                                       |

| [9]       | CCII     | 1             | 2(1)            | 3 (3)           | 1                | YES                                      |

| [12]      | FTFN     | 1             | 2(1)            | 5(1)            | 1                | YES                                      |

| [13]      | CCII     | 2             | 2 (2)           | 2 (1)           | 1                | YES                                      |

| [16]      | CDTA     | 2             | 2(1)            | _               | 2                | NO                                       |

| [19]      | OTRA     | 1             | 2 (0)           | 3 (1)           | 1                | YES                                      |

| [21]      | CCCCTA   | 1             | 2 (2)           | 1 (1)           | 1                | YES                                      |

| [23]      | CCIII    | 2             | 2 (2)           | 3 (3)           | 1                | YES                                      |

| [25]      | UVC      | 1             | 2(1)            | 3 (1)           | 1                | YES                                      |

| [26]      | VDTA     | 1             | 2 (2)           | -               | 2                | YES                                      |

| [29]      | CFOA     | 1             | 3 (2)           | 4 (2)           | 1                | YES                                      |

| [47]      | CFOA     | 1             | 2 (2)           | 2 (1)           | 1                | NO                                       |

| [47]      | CFOA     | 1             | 2(1)            | 3 (1)           | 1                | YES                                      |

| [48]      | OTRA     | 1             | 2 (0)           | 2 (0)           | 1                | NO                                       |

| [48]      | OTRA     | 1             | 2 (0)           | 3 (1)           | 1                | YES                                      |

| [49]      | CFOA     | 1             | 3 (2)           | 3 (3)           | 1                | YES                                      |

| [50]      | CDBA     | 2             | 2 (2)           | 3 (0)           | 2                | YES                                      |

| [51]      | OTRA     | 1             | 3 (1)           | 3 (0)           | 1                | YES                                      |

| This Work | VCII     | 1             | 2(1)            | 2 (1)           | 1                | NO                                       |

Table 4. Comparative table of sinusoidal oscillator topologies.

Op-Amp: operational amplifier; OTA: operational transconductance amplifier; CCII: second generation current conveyor; FTFN: four terminal floating nullor; CDTA: current differencing transconductance amplifier; OTRA: operational transresistance amplifier; CCCCTA: current controlled current conveyor transconductance amplifier; CCIII: third generation current conveyor; UVC: universal voltage conveyor; VDTA: voltage dependent transconductance amplifier; CCIII: second generation amplifier; CCCCA: current of the conveyor; CDTA: current differencing buffered amplifier; VCII: second generation voltage conveyor.

Author Contributions: Conceptualization, M.S. and G.B.; methodology, G.B. and F.C.; software, G.B.; validation, G.F., P.T., V.S. and L.P.; formal analysis, M.S. and F.C.; investigation, P.T. and V.S.; resources, V.S. and G.F.; data curation, V.S. and L.P.; writing—original draft preparation, L.P. and G.B.; writing—review and editing, V.S., G.B., L.P., M.S., G.F., F.C. and A.T.; visualization, F.C. and L.P.; supervision, L.P., G.F., V.S. and P.T.; project administration, G.F., V.S. and A.T.; funding acquisition, V.S. All authors have read and agreed to the published version of the manuscript.

Funding: The work did not receive any external funding.

**Data Availability Statement:** No new data were created or analyzed in this study. Data sharing is not applicable to this article.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Jaikla, W.; Adhan, S.; Suwanjan, P.; Kumngern, M. Current/voltage controlled quadrature sinusoidal oscillators for phase sensitive detection using commercially available IC. Sensors 2020, 20, 1319. [CrossRef] [PubMed]

- Mohsen, M.; Said, L.; Elwakil, A.; Madian, A.; Radwan, A. Extracting optimized bio-impedance model parameters using different topologies of oscillators. *IEEE Sensors J.* 2020, 20, 9947–9954. [CrossRef]

- Li, G.; Cui, J.; Yang, H. A new detecting method for underwater acoustic weak signal based on differential double coupling oscillator. IEEE Access 2021, 9, 18842–18854. [CrossRef]

- Senani, R. New canonic sinusoidal oscillator with independent frequency control through a single grounded resistor. *Proc. IEEE* 1979, 67, 691–692. [CrossRef]

- Bhattacharyya, B.; Tavakoli Darkani, M. A unified approach to the realization of canonic RC-active, single as well as variable, frequency oscillators using operational amplifiers. J. Frankl. Inst. 1984, 317, 413–439. [CrossRef]

- Senani, R.; Bhaskar, D.R.; Gupta, M.; Singh, A.K. Canonic OTA-C sinusoidal oscillators: Generation of new grounded-capacitor versions. Am.J. Electr. Electron. Eng. 2015, 3, 137–146.

- Gupta, S.; Senani, R. State variable synthesis of single-resistance-controlled grounded capacitor oscillators using only two CFOAs: Additional new realisations. *IEE Proc. Circuits Devices Syst.* 1998, 145, 135–138. [CrossRef]

- 8. Soliman, A.M. Current-mode oscillators using single output current conveyors. Microelectron. J. 1998, 29, 907–912. [CrossRef]

- Celma, S.; Martinez, P.A.; Carlosena, A. Approach to the synthesis of canonic RC-active oscillators using CCll. *IEE Proc. Circuits Devices Syst.* 1994, 141, 493–497. [CrossRef]

- Khan, A.A.; Bimal, S.; Dey, K.K.; Roy, S.S. Novel RC sinusoidal oscillator using second-generation current conveyor. *IEEE Trans. Instrum. Meas.* 2005, 54, 2402–2406. [CrossRef]

- 11. Bajer, J.; Lahiri, A.; Biolek, D. Current-mode CCII+ based oscillator circuits using a conventional and a nodified Wien-bridge with all capacitors grounded. *Radio Eng.* 2011, 20, 245–251.

- Çam, U.G.; Toker, A.; Çicekoglu, O.G.; Kuntman, H. Current-mode high output impedance sinusoidal oscillator configuration employing single FTFN. Analog Integr. Circuits Signal Process. 2000, 24, 231–238. [CrossRef]

- Lahiri, A. New canonic active RC sinusoidal oscillator circuits using second-generation current conveyors with application as a wide frequency digitally controlled sinusoidal generator. Act. Passiv. Electron. Compon. 2011, 2011, 274394. [CrossRef]

- Horng, J.-W. Current-mode third-order quadrature oscillator using CDTAs. Act. Passiv. Electron. Compon. 2009, 2009, 789171. [CrossRef]

- Uttaphut, P.; Mekhum, W.; Jaikla, W. Current-mode multiphase sinusoidal oscillator using CCCCTAs and grounded elements. In Proceedings of the NEWCAS 11 IEEE 9th Int. New Circuits and Systems Conference, Bordeaux, France, 26–29 June 2011; pp. 345–349.

- Jin, J.; Wang, C. Current-mode universal filter and quadrature oscillator using CDTAs. Turk. J. Electr. Eng. Comput. Sci. 2014, 22, 276–286. [CrossRef]

- Agrawal, D.; Maheshwari, S. An active-C current-mode universal first order filter and oscillator. J. Circuits Systems Comput. 2019, 28, 1950219. [CrossRef]

- 18. Soliman, A.M. Current-mode oscillators using inverting CCII. J. Act. Passive Electron. Devices 2011, 6, 305–320.

- Cam, U. A novel single-resistance-controlled sinusoidal oscillator employing single operational transresistance amplifier. Analog Integr. Circ. Sig. Proc. 2002, 32, 183–186. [CrossRef]

- Gupta, S.S.; Sharma, R.K.; Bhaskar, D.R.; Senani, R. Sinusoidal oscillators with explicit current output employing current-feedback op-amps. Int. J. Circuit Theory Appl. 2010, 38, 131–147. [CrossRef]

- 21. Li, Y. Derivation for current-mode Wien oscillators using CCCCTAs. Analog Integr. Circ. Sig. Proc. 2015, 84, 479–490. [CrossRef]

- Abduelma'atti, M.T.; Alsuhaibani, E.S. New current-feedback operational-amplifier based sinusoidal oscillators with explicit current output. *Analog Integr. Circ. Sig. Proc.* 2015, 85, 513–523. [CrossRef]

- Sharma, R.K.; Arora, T.S.; Senani, R. On the realization of canonic single-resistance-controlled oscillators using third generation current conveyors. *IET Circuits Devices Syst.* 2017, 11, 10–20. [CrossRef]

- Chen, H.-P.; Hwang, Y.-S.; Ku, Y.-T. Voltage-mode and current-mode resistorless third-order quadrature oscillator. *Appl. Sci.* 2017, 7, 179. [CrossRef]

- Pushkar, K.L. Single-resistance controlled sinusoidal oscillator employing single universal voltage conveyor. SCIRP Circuits Syst. 2018, 9, 1–7. [CrossRef]

- Banerjee, K.; Singh, D.; Paul, S.K. Single VDTA based resistorless quadrature oscillator. Analog Integr. Circ. Sig. Proc. 2019, 100, 495–501. [CrossRef]

- Komanapalli, G.; Pandey, R.; Pandey, N. New sinusoidal oscillator configurations using operational transresistance amplifier. Int. J. Circuit Theory Appl. 2019, 47, 666–685. [CrossRef]

- Yuce, F.; Yuce, E. Supplementary CCII based second-order universal filter and quadrature oscillators. AEU Int. J. Electron. Commun. 2020, 118, 153138. [CrossRef]

- Srivastava, D.K.; Singh, V.K.; Senani, R. A class of single-CFOA-based sinusoidal oscillators. Am.J. Electr. Electron. Eng. 2020, 8, 1–10.

- Kumari, S.; Gupta, M. A new CMOS design of high transconductance current follower transconductance amplifier and its applications. *Analog Integr. Circ. Sig. Process.* 2018, 95, 325–349. [CrossRef]

- Pushkar, K.L.; Bhaskar, D.R. Voltage-mode third-order quadrature sinusoidal oscillator using VDIBAs. Analog Integr. Circ. Sig. Process. 2019, 98, 201–207. [CrossRef]

- Bhagat, R.; Bhaskar, D.R.; Kumar, P. Quadrature sinusoidal oscillators using CDBAs: New realizations. *Circuits Systems Sig.* Process. 2021, 40, 2634–2658. [CrossRef]

- Gupta, S.; Arora, T.S. Design and experimentation of VDTA based oscillators using commercially available integrated circuits. Analog Integr. Circ. Sig. Process. 2021, 106, 713–728. [CrossRef]

- Roy, S.; Pal, R.R. Electronically tunable third-order dual-mode quadrature sinusoidal oscillators employing VDCCs and all grounded components. *Integr. VLSI J.* 2021, 76, 99–112. [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. An overview on the second generation voltage conveyor: Features, design and applications. *IEEE Trans. Circuits Syst. Part II Express Briefs* 2019, 66, 547–551. [CrossRef]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. A new low-voltage low-power dual-mode VCII-based SIMO universal filter. *Electronics* 2019, 8, 765. [CrossRef]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. Traditional Op-Amp and new VCII: A comparison on analog circuits applications. AEU Int. J. Electron. Commun. 2019, 110, 152845. [CrossRef]

- Pantoli, L.; Barile, G.; Leoni, A.; Muttillo, M.; Stornelli, V. A novel electronic interface for micromachined Si-based photomultipliers. *Micromachines* 2018, 9, 507. [CrossRef] [PubMed]

- Barile, G.; Ferri, G.; Safari, L.; Stornelli, V. A new high drive class-AB FVF-based second generation voltage conveyor. *IEEE Trans. Circuits Syst. Part II Express Briefs* 2020, 67, 405–409. [CrossRef]

- Centurelli, F.; Monsurrò, P.; Tommasino, P.; Trifiletti, A. On the use of voltage conveyors for the synthesis of biquad filters and arbitrary networks. In Proceedings of the ECCTD 17 23rd Eur. Conf. Circuit Theory and Design, Catania, Italy, 4–6 September 2017.

- Yesil, A.; Minaei, S. New simple transistor realizations of second-generation voltage conveyor. Int. J. Circuit Theory Appl. 2020, 48, 2023–2038. [CrossRef]

- Al-Shahrani, S.M.; Al-Absi, M.A. Efficient inverse filter based on second-generation voltage conveyor (VCII). Arab J. Sci. Eng. 2021. [CrossRef]

- Al-Absi, M.A. Realization of inverse filters using second generation voltage conveyor (VCII). Analog Integr. Circ. Sig. Process. 2021. [CrossRef]

- Kumngern, M.; Torteanchai, U.; Khateb, F. CMOS class AB second generation voltage conveyor. In Proceedings of the 2019 IEEE International Circuits and Systems Symposium (ICSyS), Kuantan, Malaysia, 18–19 September 2019.

- Analog Devices. AD844 Datasheet and Product Info | Analog Devices. Analog.com. 2020. Available online: https://www.analog. com/en/products/ad844.html (accessed on 6 June 2021).

- Analog Discovery 2 [Digilent Documentation]. Available online: https://reference.digilentinc.com/reference/instrumentation/ analog-discovery-2/start (accessed on 6 June 2021).

- Soliman, A.M. Current feedback operational amplifier based oscillators. *Analog Integr. Circ. Sig. Process.* 2000, 23, 45–55. [CrossRef]

- Chien, N.-C. New realizations of single OTRA-based sinusoidal oscillators. Act. Passiv. Electron. Compon. 2014, 2014, 938987. [CrossRef]

- Srivastava, D.K.; Singh, V.K.; Senani, R. Novel single-CFOA-based sinusoidal oscillator capable of absorbing all parasitic impedances. Am.J. Electr. Electron. Eng. 2015, 3, 71–74.

- 50. Arora, T.S.; Gupta, S. A new voltage mode quadrature oscillator using grounded capacitors: An application of CDBA. *Eng. Sci. Technol.* **2018**, *21*, 43–49. [CrossRef]

- Komanapalli, G.; Pandey, N.; Pandey, R. New realization of third order sinusoidal oscillator using single OTRA. AEU Int. J. Electron. Commun. 2020, 93, 182–190. [CrossRef]

#### Article 0.5 V CMOS Inverter-Based Transconductance Amplifier with Quiescent Current Control

Andrea Ballo<sup>1</sup>, Salvatore Pennisi<sup>1,\*</sup> and Giuseppe Scotti<sup>2</sup>

- <sup>1</sup> DIEEI (Dipartimento di Ingegneria Elettrica Elettronica e Informatica), University of Catania, 95125 Catania, Italy; andrea.ballo@unict.it

- <sup>2</sup> DIET (Dipartimento di Ingegneria dell'Informazione Elettronica e Telecomunicazioni), Sapienza University of Rome, 00184 Rome, Italy; giuseppe.scotti@uniroma1.it

- \* Correspondence: salvatore.pennisi@unict.it; Tel.: +39-0957382318

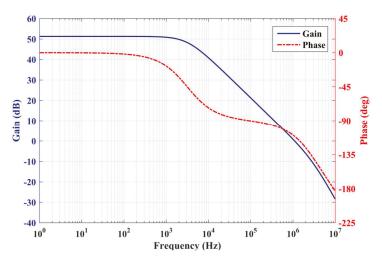

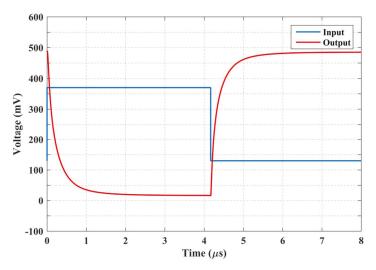

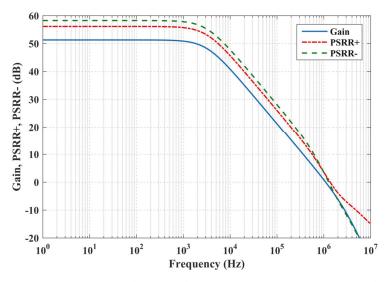

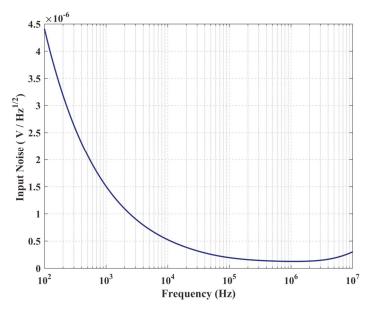

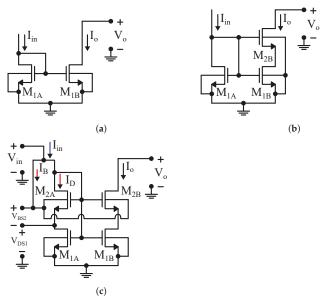

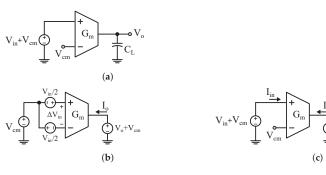

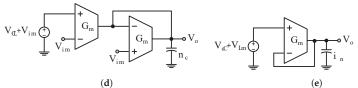

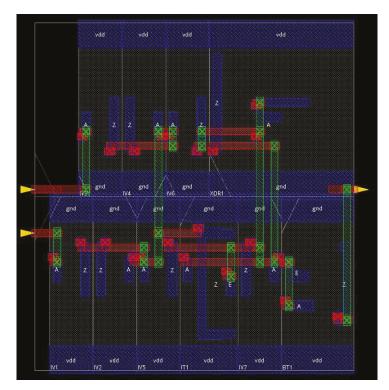

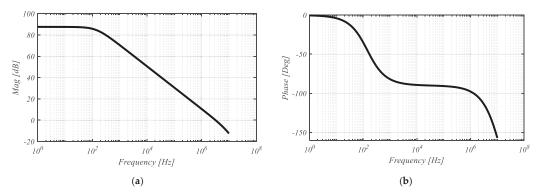

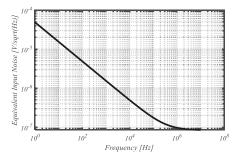

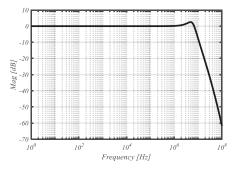

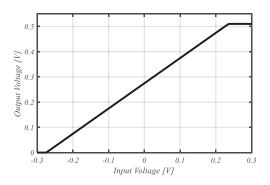

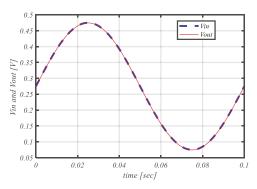

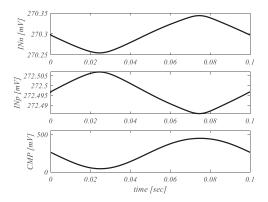

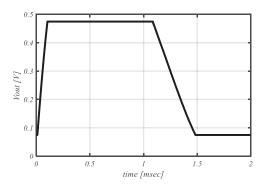

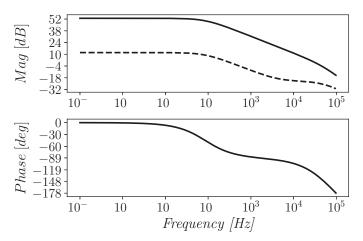

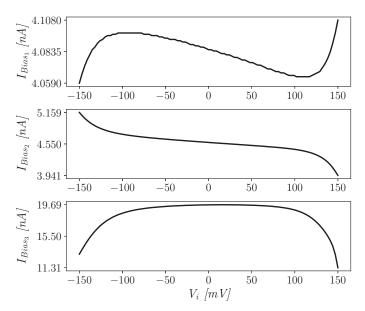

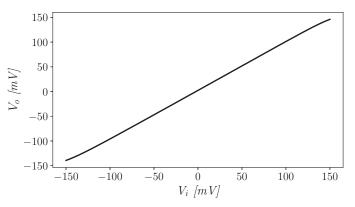

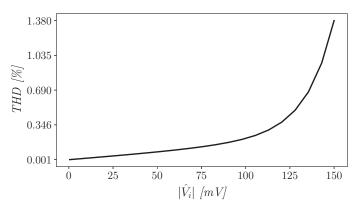

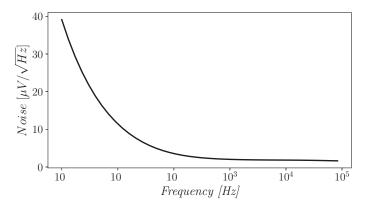

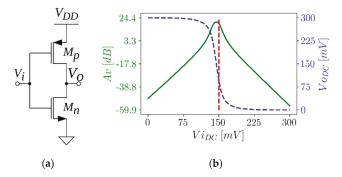

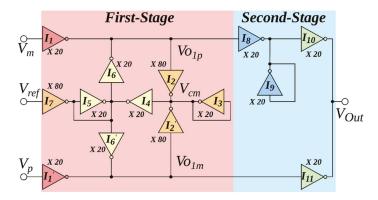

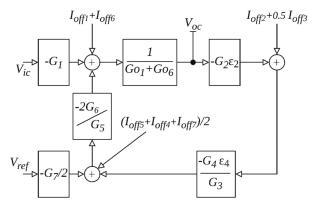

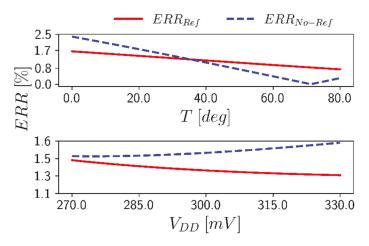

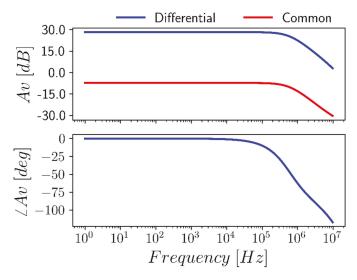

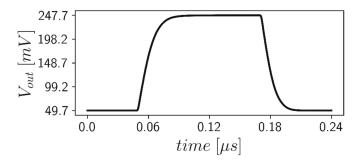

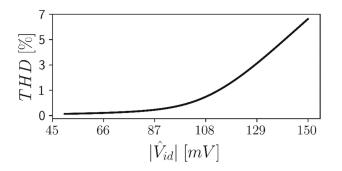

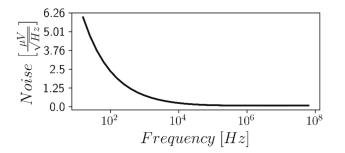

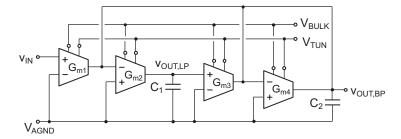

Abstract: A two-stage CMOS transconductance amplifier based on the inverter topology, suitable for very low supply voltages and exhibiting rail-to-rail output capability is presented. The solution consists of the cascade of a noninverting and an inverting stage, both characterized by having only two complementary transistors between the supply rails. The amplifier provides class-AB operation with quiescent current control obtained through an auxiliary loop that utilizes the MOSFETs body terminals. Simulation results, referring to a commercial 28 nm bulk technology, show that the quiescent current of the amplifier can be controlled quite effectively, even adopting a supply voltage as low as 0.5 V. The designed solution consumes around 500 nA of quiescent current in typical conditions and provides a DC gain of around 51 dB, with a unity gain frequency of 1 MHz and phase margin of 70 degrees, for a parallel load of 1 pF and 1.5 MΩ. Settling time at 1% is 6.6  $\mu$ s, and white noise is 125 nV/ $\sqrt{Hz}$ .

Keywords: feedback amplifier; analog; CMOS; bulk; class AB; low voltage

#### 1. Introduction

It is known that CMOS technology scaling, together with supply voltage reduction, is principally aimed at improving the performance of digital circuits and that, in this framework, the design of analog and mixed-signal blocks becomes increasingly demanding. It is indeed very difficult to obtain high linearity and high precision under near- and sub-threshold supply.

For this reason, operational transconductance amplifiers (OTAs) remain indispensable blocks for the implementation of high-accuracy closed-loop analog circuits, and several techniques have been proposed for the implementation of (ultra) low-voltage solutions. These include subthreshold-operated MOS transistors [1,2], bulk (body) driven [3,4], floating gate and quasi-floating gate MOS transistors [5,6], threshold lowering [7,8], level shifting [9], complementary pairs with body-driven gain boosting, and non-tailed pairs [10]. Additional approaches have also been proposed to replace OTAs, though not for general purpose usage, including dynamic amplifiers [11], ring amplifiers [12], and zero-crossing based circuits [13]. In addition, one interesting trend is the use of inverter-based topologies [14–28]. (A good review of the principal techniques for low-voltage OTAs can be found in the last reference.) At the basis of this approach is the single inverter (CMOS NOT gate), which is topologically simple, as it requires only two transistors between the supply rails, it provides a quite good voltage gain (though multi-stage topologies are usually required for 40 dB or more), and it exhibits class-AB and full swing operation. Therefore, it is rather effective under low supply voltages. However, the main drawback of the inverter-based solutions is related to the difficult control of the quiescent current feature that is especially required in low-power applications with a restricted current budget.

Citation: Ballo, A.; Pennisi, S.; Scotti, G. 0.5 V CMOS Inverter-Based Transconductance Amplifier with Quiescent Current Control. J. Low Power Electron. Appl. 2021, 11, 37. https://doi.org/10.3390/ jlpea11040037

Academic Editor: Orazio Aiello

Received: 26 August 2021 Accepted: 27 September 2021 Published: 28 September 2021

Publisher's Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

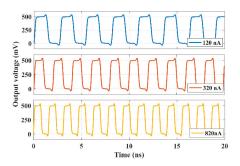

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). In this paper, a body-biasing technique, originally developed in [29] and utilized in [30], is applied to set the quiescent current of the generic inverter stage. Starting from this generic stage, a gate-driven, two-stage, inverter-based transconductance amplifier, suitable for switched-capacitor applications, is designed. Simulations results are also provided taking into account process and temperature variations. The proposed amplifier is designed in a 28-nm bulk process and is powered by a 0.5 V supply voltage. Typical quiescent current is 488 nA and, with a 1-pF//1.5-M $\Omega$  load, it provides 51-dB DC gain with a unity gain frequency of 1 MHz and phase margin of 70 degrees. Settling time at 1% is 6.6  $\mu$ s and white noise is 125 nV/ $\sqrt{Hz}$ .

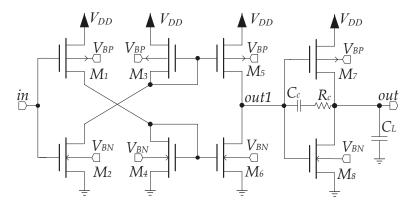

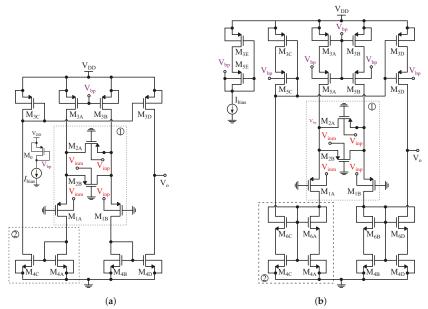

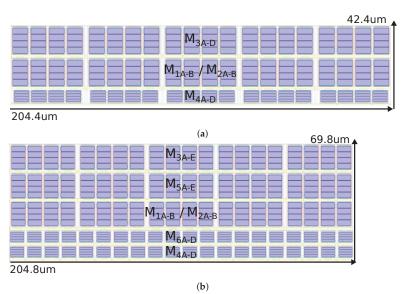

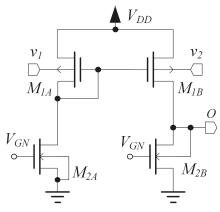

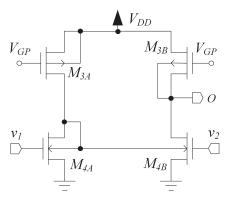

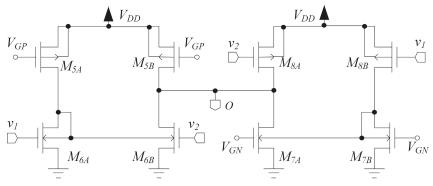

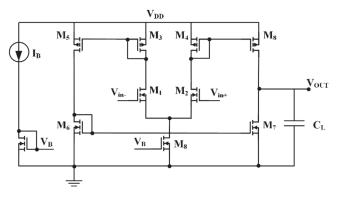

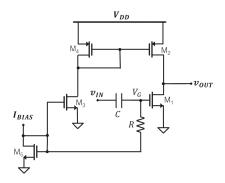

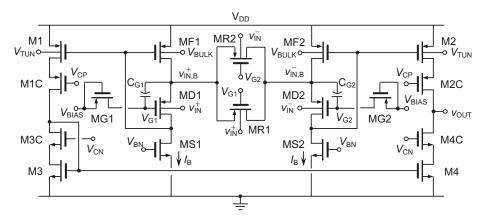

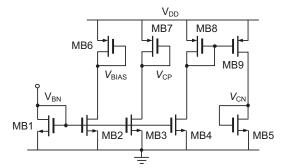

#### 2. The Proposed Solution

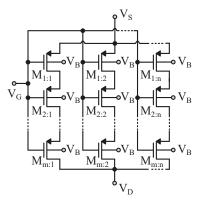

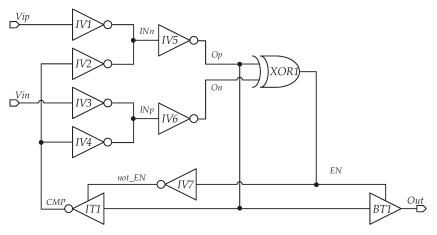

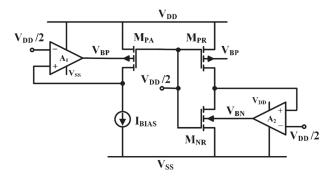

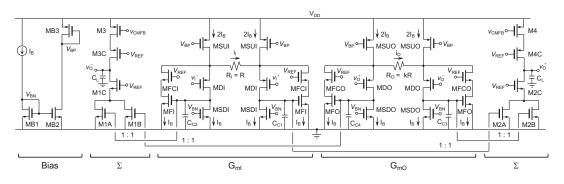

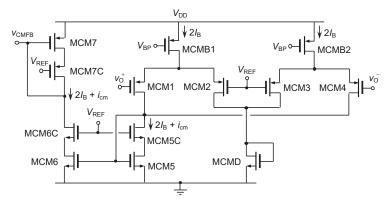

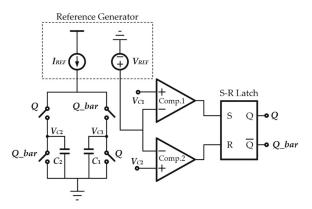

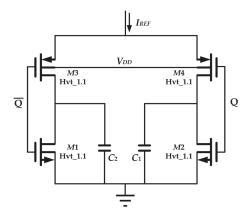

Figure 1 shows the circuit schematic of the proposed amplifier. It consists of a first noninverting stage, made up of transistors  $M_1$ - $M_6$ , and a second inverting stage, made up of transistors  $M_7$ - $M_8$ . As it is seen, the second stage is a straight CMOS NOT gate while the first one is based also onto the NOT topology, but rearranged to invert the gain trough two complementary p-channel and n-channel current mirrors  $M_3$ ,  $M_5$  and  $M_4$ ,  $M_6$ . In quiescent conditions, the input terminal is set to  $V_{DD}/2$  and thanks to the overall negative feedback (not shown) also the output and intermediate node, *out1*, are all biased at  $V_{DD}/2$ .

Figure 1. Simplified schematic of the proposed solution.

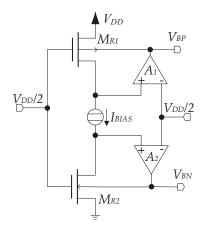

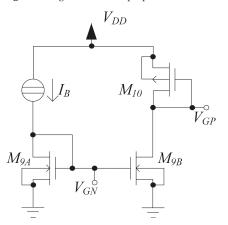

As far as the quiescent current control of the two stages is concerned, it is implemented through the bulk terminals via voltage  $V_{BP}$ , for p-channel transistors, and  $V_{BN}$ , for the n-channel ones. These voltages are generated by exploiting a technique proposed in [29] and utilized also in [10,30]. The basic working principle can be inferred with the aid of Figure 2, showing the simplified schematic of the amplifier's biasing section.

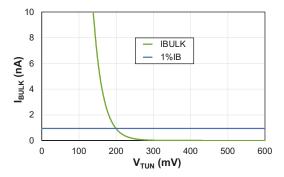

$M_{R1}$  and  $M_{R2}$  are two reference transistors both with their  $|V_{GS}|$  equal to  $V_{DD}/2$ . Their quiescent drain current is equal to  $I_{BIAS}$  thanks to the local feedback loop operated by the auxiliary amplifiers  $A_1$  and  $A_2$ , which generate the required bulk voltages,  $V_{BP}$  and  $V_{BN}$ , under the following summarized constraints:

- (a) assigned aspect ratios  $(W/L)_{R1}$  and  $(W/L)_{R2}$ ;

- (b)  $I_{D1,2} = kI_{BIAS}$ , where k is the ratio of the transistors aspect ratio as in (1);

- (c)  $V_{SGR1} = V_{GSR2} = V_{DD}/2;$

- (d)  $V_{SDR1} = V_{DSR2} = V_{DD}/2$ , assuming ideal input virtual short in A<sub>1</sub> and A<sub>2</sub>.

Figure 2. Simplified schematic of the biasing section generating  $V_{BN}$  and  $V_{BP}$  for the main amplifier in Figure 1.

Of course, aspect ratios of  $M_{R1}$  and  $M_{R2}$  must be set so that the required bulk voltages are within  $V_{DD}$  and ground. Moreover, the auxiliary amplifiers  $A_1$  and  $A_2$  should provide a maximum (rail-to-rail) output voltage range, whereas input common mode range is not a concern as input voltage is kept constant to  $V_{DD}/2$ . Therefore, simple two-stage OTAs biased in subthreshold can be profitably used. An example of implementation of this type of amplifier is found in [10], albeit operating with MOSFETs in saturation.

Consider now transistor  $M_1$  of the main amplifier in Figure 1 and remember that in quiescent conditions *Vin* is equal to  $V_{DD}/2$ . As a consequence,  $M_{R1}$  and  $M_1$  have respectively the same source, gate, and bulk voltage and hence the drain current of  $M_1$  is related to that of  $M_{R1}$  in a mirror-like condition

$$I_{D1} = \frac{(W/L)_1}{(W/L)_{R1}} I_{BIAS}$$

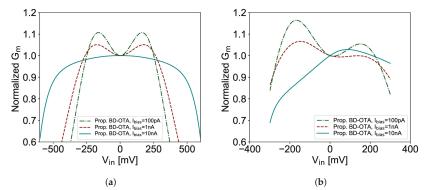

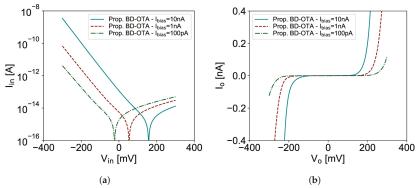

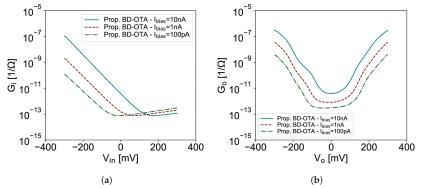

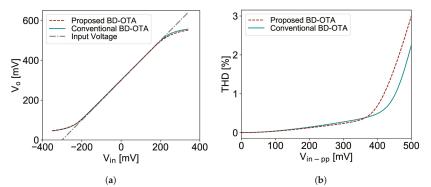

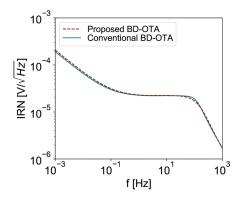

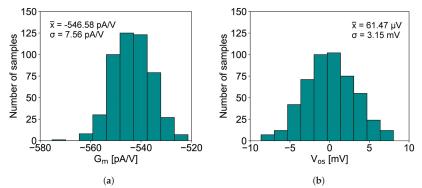

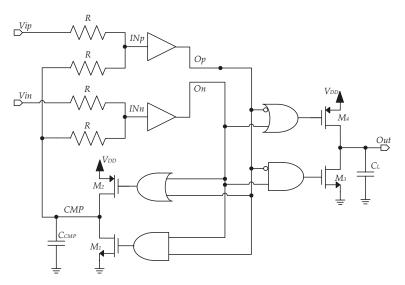

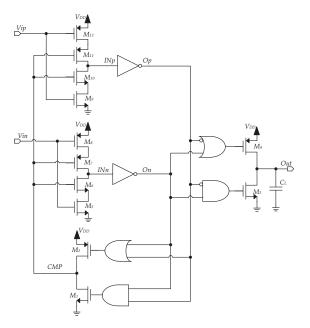

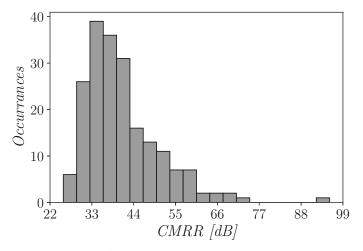

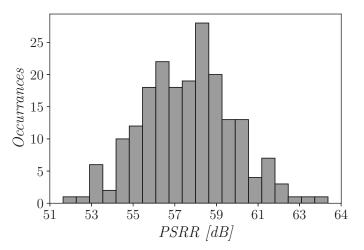

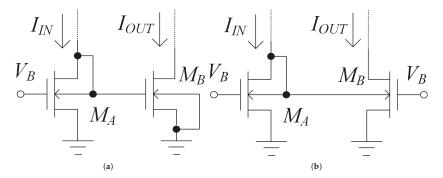

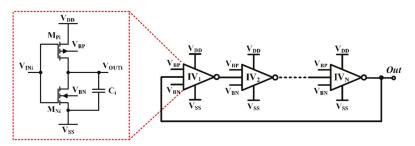

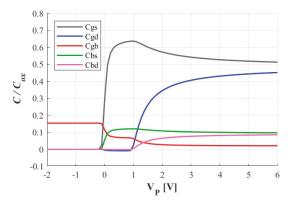

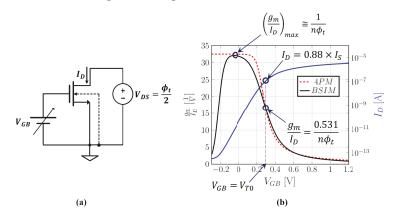

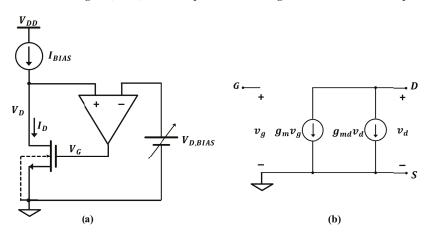

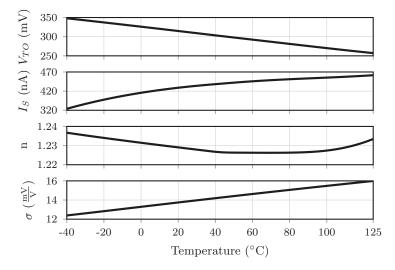

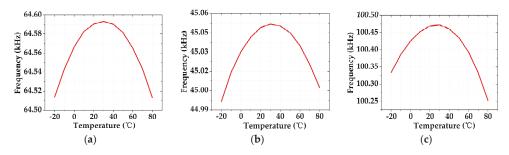

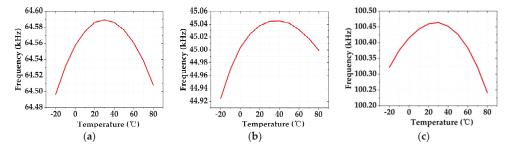

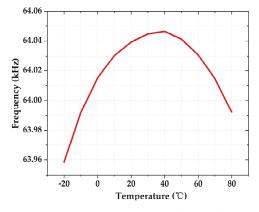

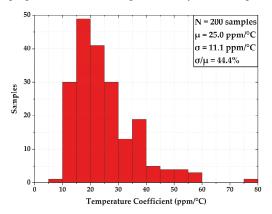

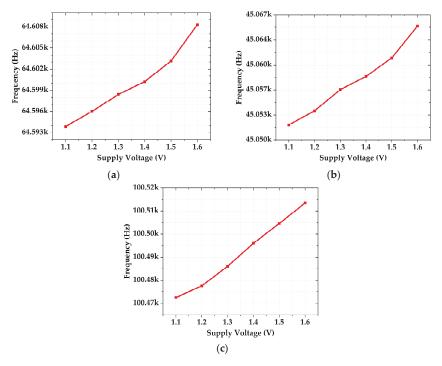

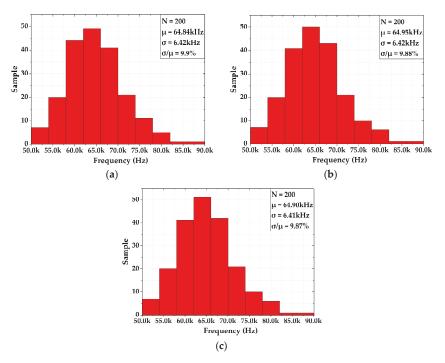

(1)