Special Issue Reprint

# High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives

Edited by Massimiliano Luna

www.mdpi.com/journal/energies

# High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives

# High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives

**Editor**

Massimiliano Luna

MDPI • Basel • Beijing • Wuhan • Barcelona • Belgrade • Manchester • Tokyo • Cluj • Tianjin

Editor

Massimiliano Luna

CNR-INM

Palermo, Italy

Editorial Office MDPI St. Alban-Anlage 66 4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Energies* (ISSN 1996-1073) (available at: https://www.mdpi.com/journal/energies/special\_issues/high-efficiency\_and\_high-performance\_power\_electronics\_for\_power\_grids\_and\_electrical\_drives).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

LastName, A.A.; LastName, B.B.; LastName, C.C. Article Title. *Journal Name* Year, *Volume Number*, Page Range.

ISBN 978-3-0365-8080-7 (Hbk) ISBN 978-3-0365-8081-4 (PDF)

© 2023 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license, which allows users to download, copy and build upon published articles, as long as the author and publisher are properly credited, which ensures maximum dissemination and a wider impact of our publications.

The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons license CC BY-NC-ND.

# Contents

| About the Editor                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preface to "High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives"                                                                                                                                                                                                                                      |

| Massimiliano Luna                                                                                                                                                                                                                                                                                                                              |

| High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives Reprinted from: <i>Energies</i> <b>2022</b> , <i>15</i> , 5844, doi:10.3390/en15165844                                                                                                                                                            |

| Shuren Wang, Fahad Saeed Alsokhiry and Grain Philip Adam Impact of Submodule Faults on the Performance of Modular Multilevel Converters Reprinted from: Energies 2020, 13, 4089, doi:10.3390/10.3390/en13164089                                                                                                                                |

| Sachin Kumar, Kumari Sarita, Akanksha Singh S Vardhan, Rajvikram Madurai Elavarasan,<br>R. K. Saket, and Narottam Das                                                                                                                                                                                                                          |

| Reliability Assessment of Wind-Solar PV Integrated Distribution System Using Electrical Loss Minimization Technique                                                                                                                                                                                                                            |

| Reprinted from: Energies 2020, 13, 5631, doi:10.3390/10.3390/en13215631                                                                                                                                                                                                                                                                        |

| Marco di Benedetto, Alessandro Lidozzi, Luca Solero, Fabio Crescimbini and Petar J. Grbović<br>High-Performance 3-Phase 5-Level E-Type Multilevel–Multicell Converters for Microgrids<br>Reprinted from: <i>Energies</i> <b>2021</b> , <i>14</i> , 843, doi:10.3390/en14040843                                                                 |

| Marco di Benedetto, Luca Bigarelli, Alessandro Lidozzi and Luca Solero  Efficiency Comparison of 2-Level SiC Inverter and Soft Switching-Snubber SiC Inverter for Electric Motor Drives  Reprinted from: Energies 2021, 14, 1690, doi:10.3390/en14061690                                                                                       |

| Salvatore Foti, Antonio Testa, Salvatore De Caro, Luigi Danilo Tornello, Giacomo Scelba                                                                                                                                                                                                                                                        |

| And Mario Cacciato  Multi-Level Multi-Input Converter for Hybrid Renewable Energy Generators  Reprinted from: Energies 2021, 14, 1764, doi:10.3390/en14061764                                                                                                                                                                                  |

| Luigi Danilo Tornello, Salvatore Foti, Mario Cacciato, Antonio Testa, Giacomo Scelba, Salvatore De Caro, Giuseppe Scarcella, et al.  Performance Improvement of Grid-Connected Induction Motors through an Auxiliary Winding Set  Reprinted from: Energies 2021, 14, 2178, doi:10.3390/en14082178                                              |

|                                                                                                                                                                                                                                                                                                                                                |

| Massimiliano Luna, Antonino Sferlazza, Angelo Accetta, Maria Carmela Di Piazza, Giuseppe La Tona and Marcello Pucci  Modeling and Performance Assessment of the Split-Pi Used as a Storage Converter in All the Possible DC Microgrid Scenarios. Part I: Theoretical Analysis  Reprinted from: Energies 2021, 14, 4902, doi:10.3390/en14164902 |

| Massimiliano Luna, Antonino Sferlazza, Angelo Accetta, Maria Carmela Di Piazza,<br>Giuseppe La Tona and Marcello Pucci                                                                                                                                                                                                                         |

| Modeling and Performance Assessment of the Split-Pi Used as a Storage Converter in All the Possible DC Microgrid Scenarios. Part II: Simulation and Experimental Results Reprinted from: <i>Energies</i> <b>2021</b> , <i>14</i> , 5616, doi:10.3390/en14185616                                                                                |

| Nikolay Madzharov and Nikolay Hinov                                                                                                                                                                                                                                                                                                            |

| High-Performance Power Converter for Charging Electric Vehicles  Reprinted from: Energies 2021, 14, 8569, doi:10.3390/en14248569                                                                                                                                                                                                               |

| Ismail Aouichak, Sébastien Jacques, Sébastien Bissey, Cédric Reymond, Téo Besson          |

|-------------------------------------------------------------------------------------------|

| and Jean-Charles Le Bunetel                                                               |

| A Bidirectional Grid-Connected DC-AC Converter for Autonomous and Intelligent Electricity |

| Storage in the Residential Sector                                                         |

| Reprinted from: Energies <b>2022</b> , 15, 1194, doi:10.3390/en15031194                   |

|                                                                                           |

### **About the Editor**

### Massimiliano Luna

Massimiliano Luna, Ph.D., is a permanent research scientist at the National Research Council of Italy (CNR). He obtained his Ph.D. in Energy Science (2009) and his M.Sc. degree in Electrical Engineering (2003) from the University of Palermo, Italy. His research has been mostly focused on Power Electronics and electrical drives, static and dynamic modeling of renewable sources, FPGAand DSP-based signal processing, and control and management of smart microgrids. He participated in ten research projects and is currently leading the following research projects for CNR: "Mission Innovation - MISSION (Smart, multi-vector and integrated microgrids to accelerate the energy transition) - LA1.7" and "NAUSICA (Efficient ships using innovative and low carbon technological solutions) - OR3". Furthermore, he holds two patents and has been the supervisor of the related technology transfer project. In 2021, he was visiting researcher at Universidad Politécnica de Madrid (UPM) - Centro de Electrónica Industrial (CEI) as a winner of the Short-Term Mobility competition held by CNR. Dr. Luna co-authored more than 60 scientific papers in international journals and conferences, a book chapter, and two software applications. One of his co-authored papers won the Third Prize Paper Award 2020, recognized by the IEEE IAS Industrial Drives Committee; another was shortlisted for the Best Paper Award at the 2017 IEEE International Symposium on Industrial Electronics. In addition, Dr. Luna serves as a reviewer for several journals and conferences and is a member of two Technical Committees of the IEEE and IMACS societies. Finally, he was called as an expert peer reviewer for the evaluation of research project funding on behalf of the Italian Ministry of University and Research.

# Preface to "High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives"

Power electronics have enabled the transition from rotating to static power conversion and radically transformed the way we condition electrical energy in stationary and non-stationary applications. As a result, power electronic converters are pervasive in today's society. They are available in many variants, each with pros and cons, and their rated power keeps increasing significantly. Many successful applications have already been deployed. However, the urge for a sustainable future requires further performance increase in terms of efficiency, power density, power quality, cost, robustness to faults, as well as stable operation and high dynamic performance in several operating conditions. These results can be obtained by leveraging different approaches such as advanced converter topologies, innovative control techniques, and wide bandgap power devices.

Based on the above premises, this Special Issue collects papers addressing techniques to improve the efficiency and performance of the application of power electronics in power grids and electrical drives. Such papers can be grouped into three categories:

- (a) Power converters used to interface Renewable Energy Sources (RESs) and Energy Storage Systems (ESSs) with microgrids or to recharge ESSs in electric vehicles.

- (b) Performance increase in variable speed electrical drives and direct online induction motors.

- (c) Application of electrical loss minimization techniques to microgrids based on RESs.

The articles published in this Special Issue contribute to expanding the scientific knowledge in the field of power electronics and offer valuable insights into the recent developments for researchers, scholars, and practitioners working in such a field.

The Guest Editor is grateful to the MDPI publisher for the invitation to hold such a position for this Special Issue of *Energies*. He would also like to thank all the authors and reviewers for their commitment that led to the success of this Special Issue. Furthermore, he is very grateful to the editorial staff of Energies, especially to Ms. Vickie Zhang for her valuable cooperation and support.

Massimiliano Luna

Editor

Editoria

## High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives

Massimiliano Luna

Istituto di Ingegneria del Mare (INM), Consiglio Nazionale delle Ricerche (CNR), Via Ugo La Malfa 153, 90146 Palermo, Italy; massimiliano.luna@cnr.it

### 1. Introduction

Since the invention of the light bulb by T. A. Edison, the use of electricity has kept growing during the recent century. In fact, electrical energy is the most versatile among the various forms of energy. It can be easily generated, transmitted across long distances, distributed as AC or DC, and converted into other forms with high efficiency to be used on demand or stored for later use. In particular, power electronics is the enabling technology that allowed for the transition from rotating to static power conversion, thus radically transforming how we condition electrical energy in stationary and non-stationary applications. Currently, power electronic converters are available in many variants, each with pros and cons. They generally exhibit good efficiency, dynamic performance, and reliability, especially when they supply passive loads. The most recent power electronic converters are very sophisticated and cover different application domains: from grid-connected inverters for renewable energy sources (RESs) to optimal power flow controllers for microgrids under the supervision of an energy management system (EMS); from high-dynamics variable speed electrical drives (VSDs) for industrial applications to smart and efficient drives for e-mobility; and from wireless charging of electric vehicles to bidirectional converters for the integration of energy storage systems (ESSs) into AC or DC microgrids.

Although such applications have been successfully deployed, the urge for a sustainable future requires further performance increase in terms of efficiency, power density, power quality, cost, robustness to faults, as well as stable operation and high dynamic performance in several operating conditions. These results can be obtained by leveraging different approaches. For example, wide bandgap power devices such as silicon carbide (SiC) or gallium nitride (GaN) allow for faster dynamics, reduced power loss, and increased power density. In addition, advanced converter topologies such as multilevel/multiphase converters or partial power converters can also offer several benefits. The first can improve power quality and can reach higher power levels through modular design; the others allow for processing only a fraction of load power, thus achieving increased power density and, again, higher power levels.

Moreover, it is also possible to take advantage of innovative control techniques. For example, electrical loss minimization (ELM) techniques can reduce losses for a given load power, whereas maximum torque per ampere (MTPA) techniques for electrical drives can reduce the current needed to obtain a given load torque level. As a result, both techniques lead to increased efficiency; in addition, MTPA improves the dynamic performance.

Based on these premises, this Special Issue was launched to gather technical and scientific contributions on various techniques aimed at improving the efficiency and performance in power electronics applications for power grids and electrical drives. The Guest Editor of this Special Issue was pleased to observe a positive response from the scientific community, which contributed ten high-quality articles. Such a response confirms the importance of the subject and the need for investigating new solutions in this field. The articles published in this Special Issue contribute to expanding the scientific knowledge in the field of power electronics and will be briefly reviewed in the following section.

Citation: Luna, M. High-Efficiency and High-Performance Power Electronics for Power Grids and Electrical Drives. Energies 2022, 15, 5844. https://doi.org/10.3390/ en15165844

Received: 1 August 2022 Accepted: 10 August 2022 Published: 11 August 2022

Publisher's Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

### 2. Overview of the Contributions in This Special Issue

This Special Issue includes ten contributions on various techniques aimed at improving the efficiency and performance in power electronics applications for power grids and electrical drives [1–10]. Such articles were authored by international research teams from several countries and covered different topics. For the reader's convenience, they were grouped into three categories:

- (a) Power converters used to interface RESs and ESSs with microgrids [1,3,5,7,8,10] or to recharge ESSs in electric vehicles [9];

- (b) Performance increase in VSDs and direct online induction motors [4,6];

- (c) Application of electrical loss minimization techniques to microgrids based on RESs [2]. In the following, after a short description of each contribution, some perspectives for future developments are briefly given.

As for category (a), the first three contributions deal with multilevel converters. The study presented in [1] by Wang et al. is focused on modular multilevel converters (MMC). Although such converters are well-suited for high-power and medium-voltage applications, they exhibit a quite complex topology based on several submodules (SMs). Therefore, their performance can be affected by SM failures, leading to unequal power distribution and undesirable internal dynamics. Wang et al. [1] studied the impact of SM failures on the MMC internal dynamics performance and proposed two implementations of auxiliary controllers that can regulate such dynamics. The performance of the presented techniques was assessed using time-domain simulations and through experiments. In general, the authors found that appropriate control countermeasures can minimize the adverse impact of SM failures in terms of control range, power quality on the AC and DC sides, and distribution of voltage stress across the SM capacitors and semiconductor switches. Furthermore, they presented the trade-offs of the two proposed control methods. The first control scheme is better than the second from the AC side viewpoint but pollutes the DC current with a fundamental frequency ripple. In contrast, the second scheme is better than the other from the DC side viewpoint; nevertheless, it increases the risk of DC injection into the AC grid and reduces the AC control range. Future development could be devoted to devising control strategies that can improve the performance on both the DC and AC sides without trade-offs.

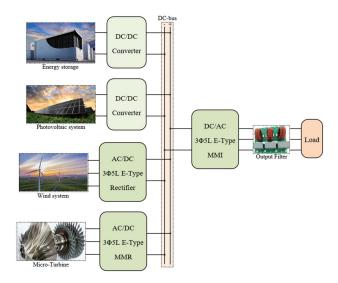

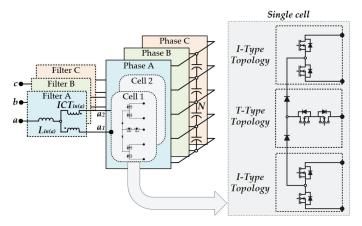

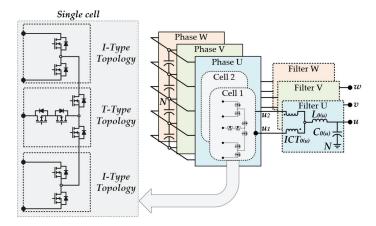

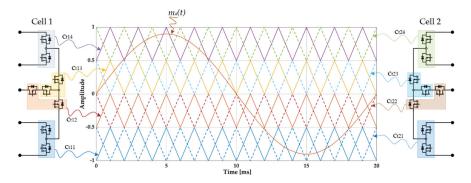

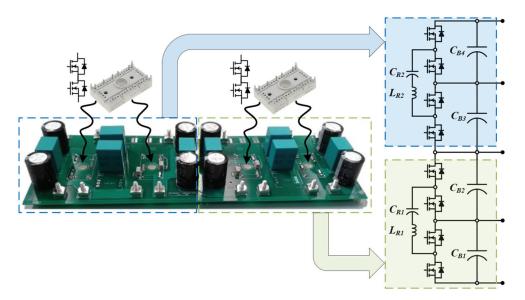

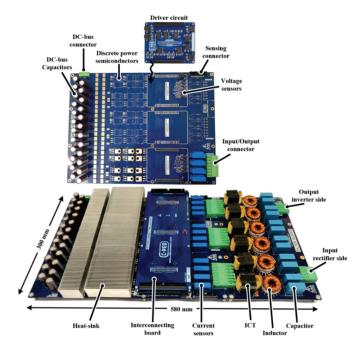

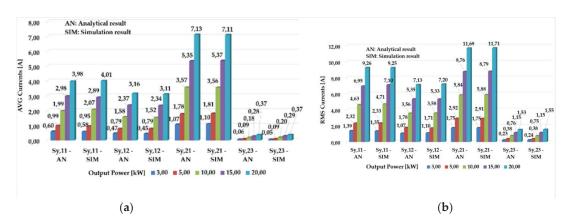

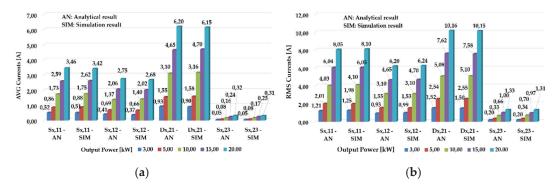

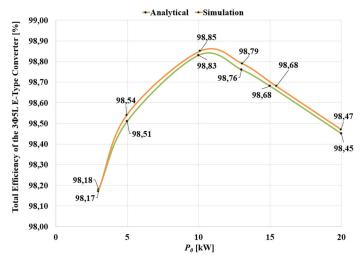

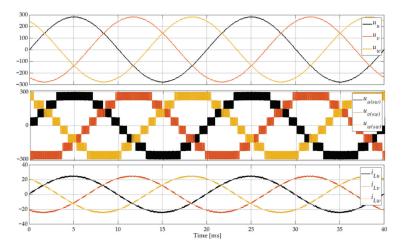

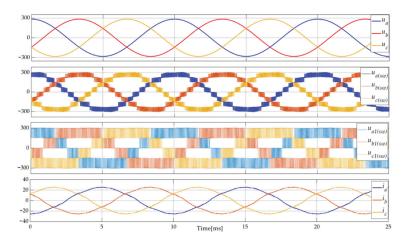

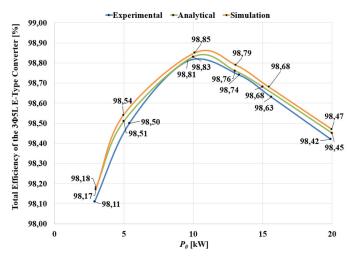

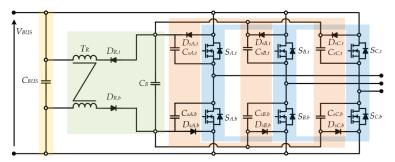

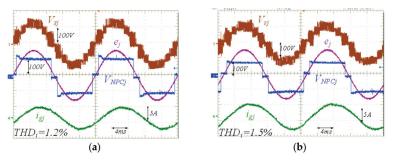

In [3], Di Benedetto et al. designed two multilevel converters that exhibited high efficiency and power density, as required for microgrid applications, as well as good performance in terms of quality of voltage and current waveforms using only silicon power semiconductors. In particular, the paper focused on a three-phase five-level E-type multilevel-multicell rectifier (3Ф5L E-Type MMR) and a three-phase five-level E-type multilevel-multicell inverter (3Ф5L E-Type MMI). The E-type topology was chosen because it allows for implementing an interleaved configuration using an intercell transformer, thus reducing the volume of the output filter. First, the proposed hardware design and control strategy were validated by simulations. Then, a prototypal 3Φ5L E-Type MMR plus 3Ф5L E-Type MMI was built using silicon MOSFETs or IGBTs switching at 20 kHz, and its performance was assessed experimentally. The results obtained showed excellent performance. The THDv and THDi were 0.88% and 1.95%, respectively. Furthermore, the converter exhibited a peak efficiency of nearly 99% using only silicon power semiconductors, a power density of 8.4 kW/dm<sup>3</sup>, and specific power of 3.24 kW/kg. In comparison, a similar SiC-based converter proposed by another author exhibited the following figures of merit: 99.2%, 1.4 kW/dm<sup>3</sup>, and 2.5 kW/kg; furthermore, another SiC-based converter proposed in the technical literature exhibited 99.26% efficiency and a power density of 4 kW/dm<sup>3</sup>. This comparison shows that remarkable results can be obtained using an appropriate topology, even without using wide-bandgap devices. On the one hand, this concept could also be applied to other converter topologies. On the other hand, the performance of the converter proposed in [3] could have been even higher if SiC devices had been used.

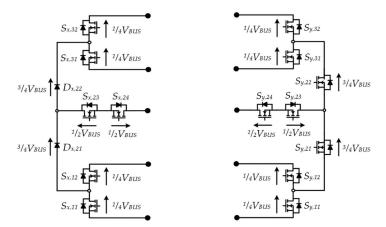

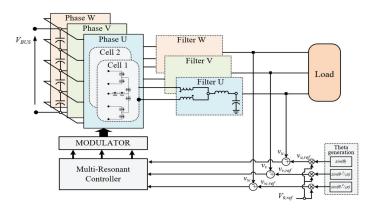

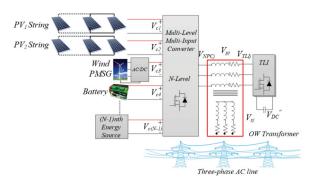

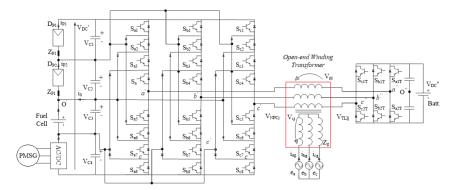

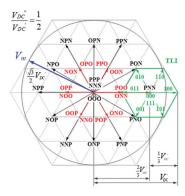

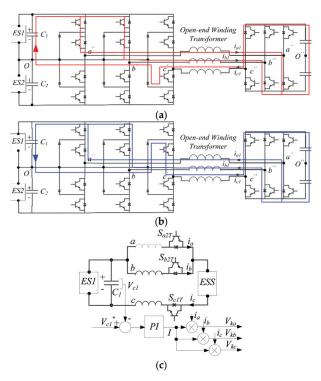

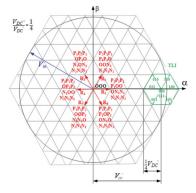

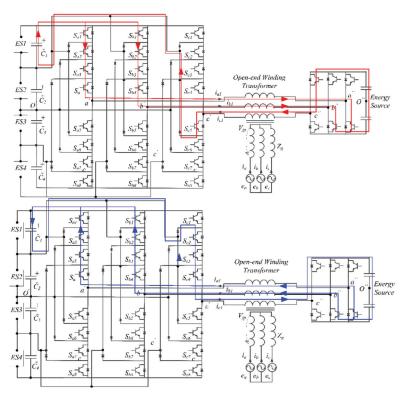

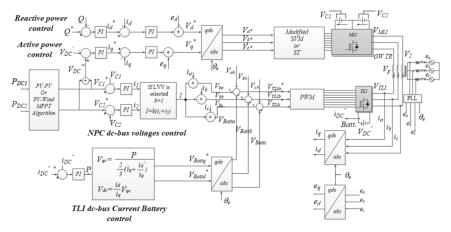

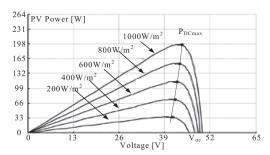

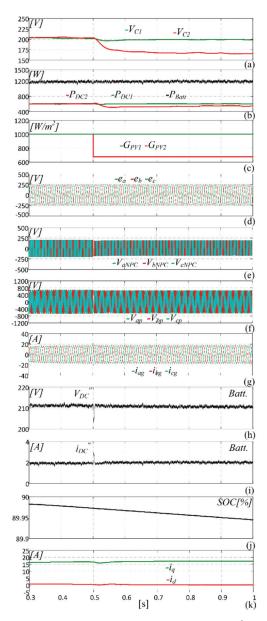

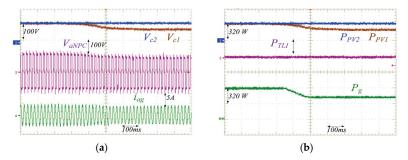

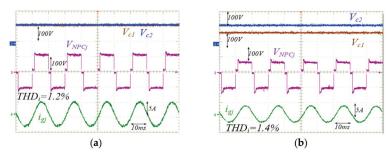

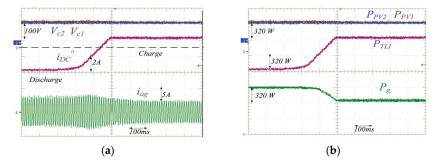

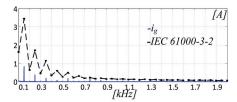

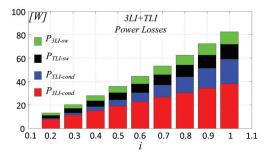

Another contribution about multilevel converters was given by Foti et al. [5]. The authors presented a multi-input N-level power converter topology for grid-connected

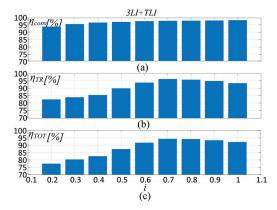

applications, which can perform independent management of N-1 power sources and an ESS without requiring additional DC-DC power converters. The proposed topology encompasses a three-phase neutral point clamped multilevel inverter (MLI), a three-phase transformer in an open-end winding configuration, and a conventional two-level inverter (TLI). The MLI can interface several DC sources such as photovoltaic (PV) modules and wind energy conversion systems with rectified output, providing active power to the grid. It operates at a low switching frequency (<1 kHz), thus featuring low switching power losses. The TLI is operated at a higher switching frequency but with a lower DC bus voltage, and its DC port can be connected to a bulk capacitor or an ESS. The TLI works as an active filter to compensate for the low-order harmonics generated by the MLI and for imbalances among the source voltages, provided that they do not exceed the DC bus voltage. The proposed topology reduces the complexity and cost of a multi-input power converter. Moreover, it exhibits reduced losses and lower switch count with the same power quality level. Both features contribute to increasing the efficiency and the power density of the converter. The validity of such a concept was confirmed first theoretically and then by simulations and experimental tests. Even when the N-1 input voltages were imbalanced, the THD was as low as 1.5%. Furthermore, the peak efficiency of the converter reached a maximum value of 95%. In future work, it could be interesting to apply the proposed concept to other application domains, such as electric vehicles and the aerospace industry.

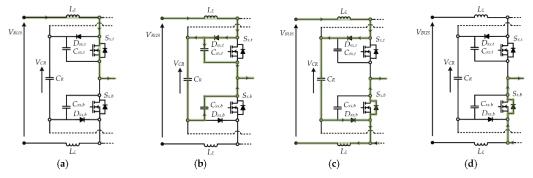

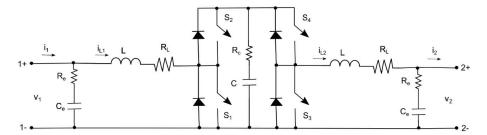

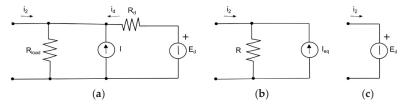

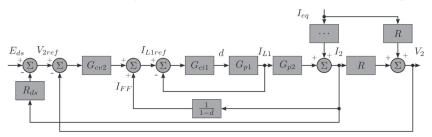

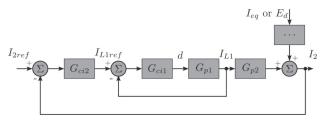

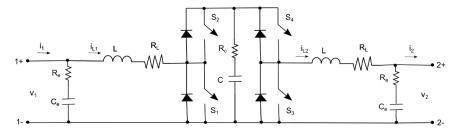

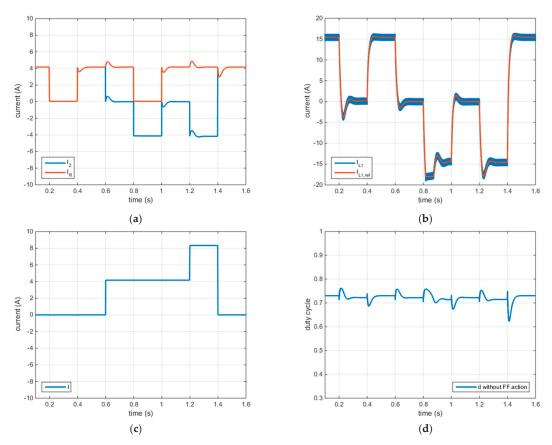

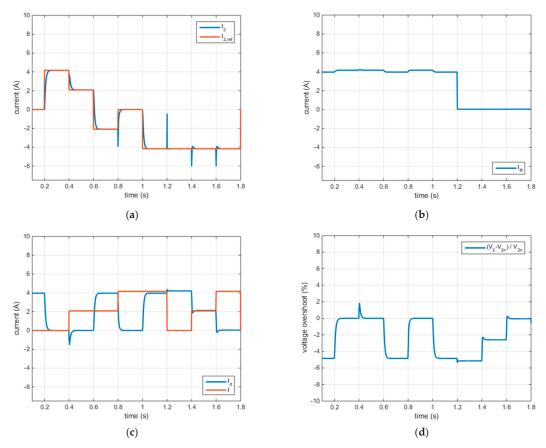

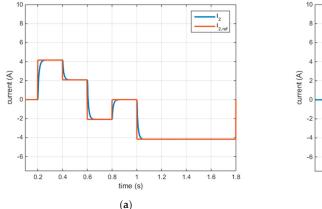

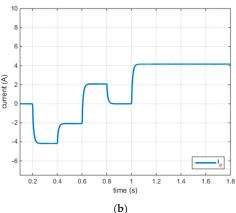

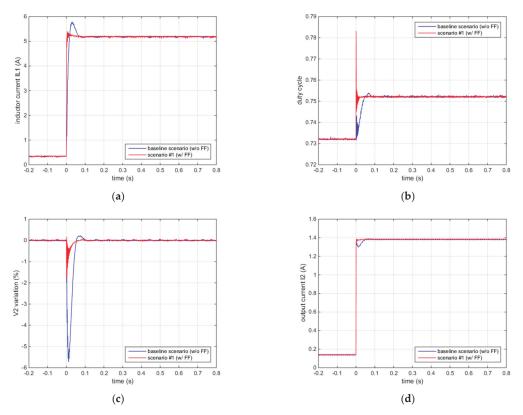

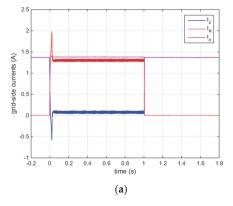

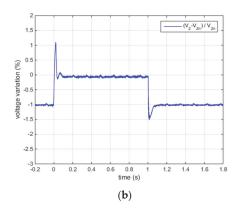

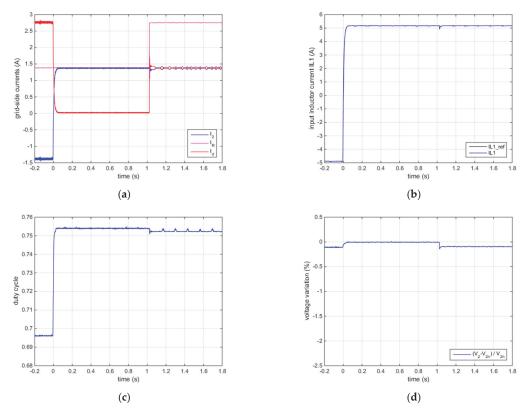

Other contributions that fall into category (a) are [7,8] by Luna et al. These papers were focused on the use of bidirectional DC-DC converters to integrate an ESS into a DC microgrid, ensuring stable operation and good dynamic performance. The authors showed that this integration deserves careful design because the ESS converter is required to work in different scenarios depending on the microgrid configuration. They chose the Split-Pi converter as a case study because it presents several merits at the only cost of non-isolated operation; however, the proposed approach has general validity. In [7], the authors analyzed the five possible operating scenarios, showing how to model the equivalent load of the ESS converter, and devised the state-space model of the ESS converter supplying such a load. Each scenario requires a different control scheme with reference to the number of control loops and the controller design procedure to obtain high performance. Proportional-integral-derivative (PID) controllers were employed, and the related design criteria were given. Then, in [8], the authors validated the theoretical analysis presented in [7] by performing several simulations and experimental tests. Future development of this work could be devoted to designing unconventional control systems for ESS converters suitable for operating in more than one microgrid scenario or, possibly, in all the scenarios.

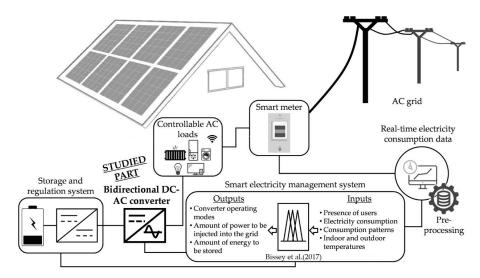

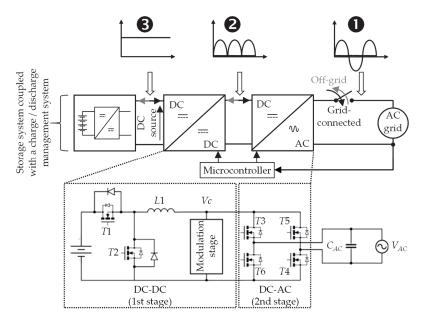

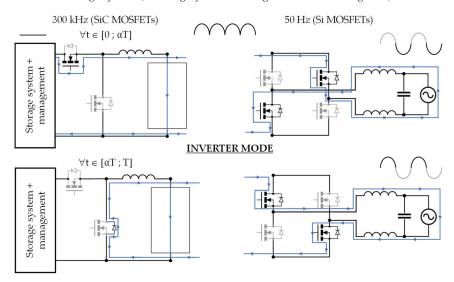

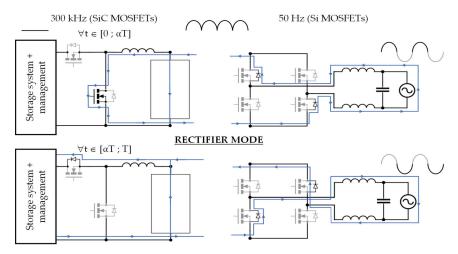

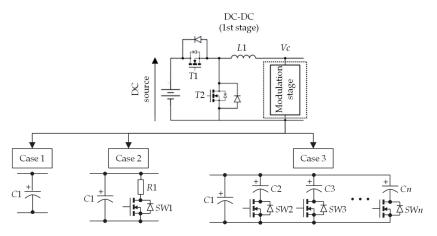

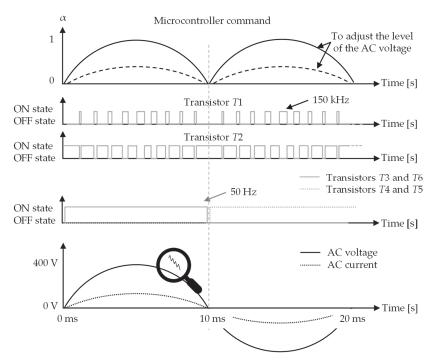

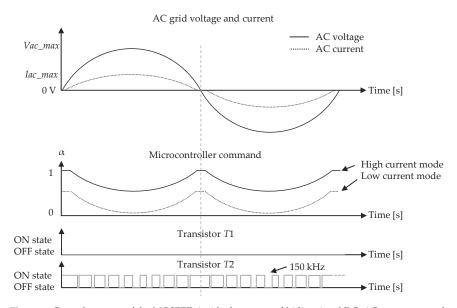

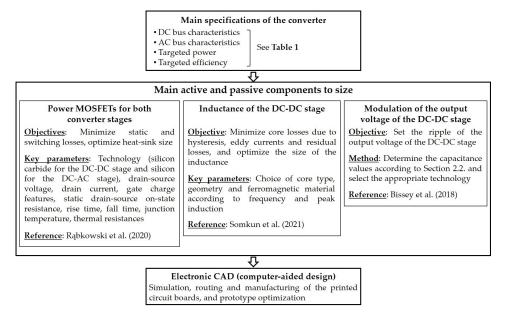

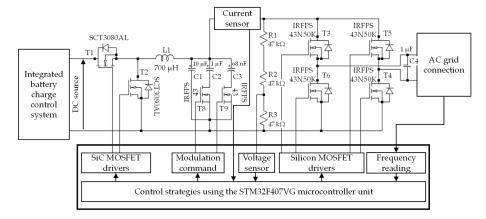

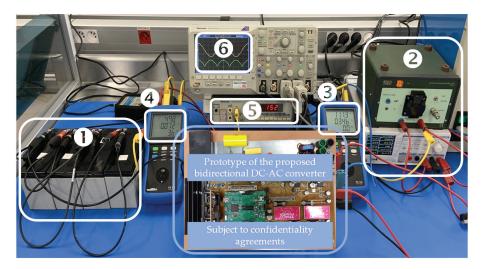

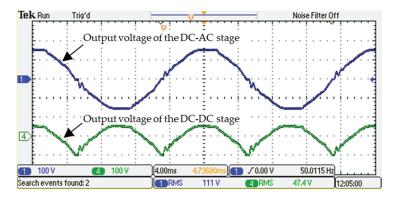

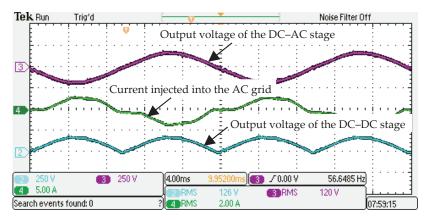

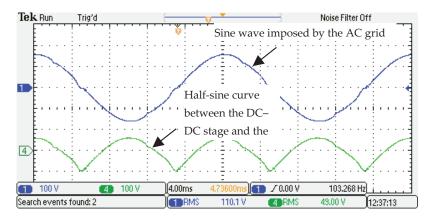

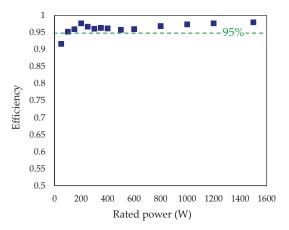

The main objective of the work by Aouichak et al. was to present and experimentally validate a bidirectional DC-AC converter for ESSs, connected to the AC grid and operated under the supervision of a smart home electricity management system (HEMS) to reduce the cost of electricity [10]. The proposed converter can operate in both grid-connected and off-grid modes. It is based on two cascaded bidirectional stages and can generate a full sinusoidal wave from a sinusoidal half wave thanks to the high performance of wide bandgap devices. First, a modified half-bridge DC-DC stage regulates the DC voltage and establishes the positive half of the AC waveform; such a stage is based on two SiC power MOSFETs controlled at a high frequency (150 kHz). Then, an H-bridge DC-AC stage periodically reverses such a waveform; this stage is composed of four MOSFETs on a silicon substrate, controlled at line frequency (50 Hz). The converter was validated experimentally in inverter mode and in rectifier mode with power factor correction (PFC). The use of SiC switches combined with appropriate control strategies allowed for an increase in the compactness of the converter while ensuring good performance, especially in terms of efficiency, which exceeded 95% over the entire power range from 100 W to 1.5 kW. The main advantages of the proposed converter are twofold: (1) it is based on a reasonably complex topology and, thus, can be recommended as an alternative solution for HEMS applications; (2) in stand-alone operations, it does not require a bulky output filter, so it is more compact than a traditional H-bridge inverter. Future development could be focused on analyzing the electromagnetic compatibility aspects related to the high switching frequency to ensure a safe connection to the AC grid.

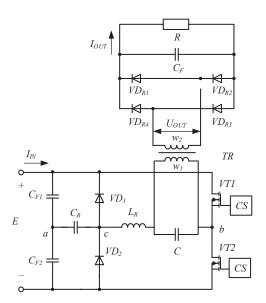

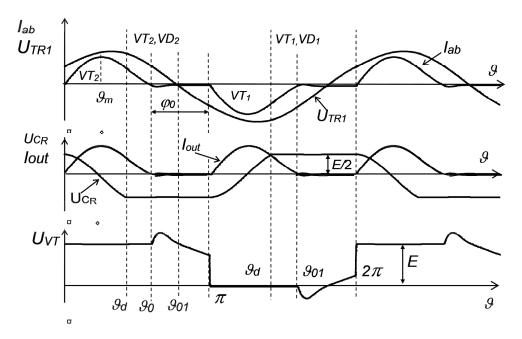

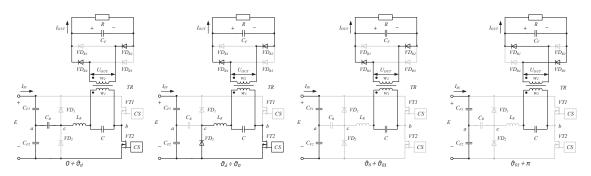

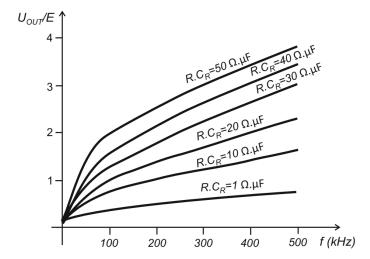

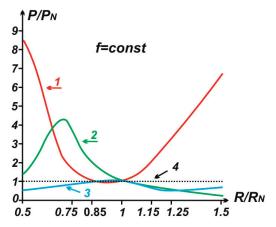

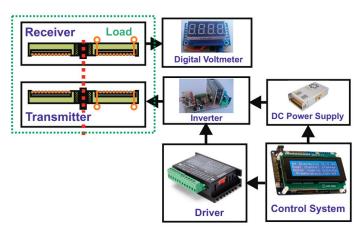

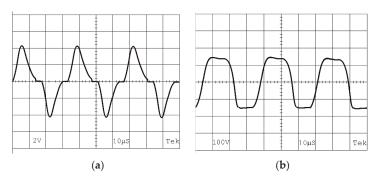

The last contribution falling into category (a) is the one by Madzharov et al. and discusses the application of the energy dosing technique to improve the performance of a charging station for electric vehicles based on a resonant DC-DC converter [9]. The proposed converter comprises a half-bridge resonant inverter with energy dosing (RI with ED) without reverse diodes, a high-frequency matching transformer, and an output rectifier with a capacitive filter. The switching devices operate with zero current switching (ZCS) and zero voltage switching (ZVS). The main advantage of the energy dosing schemes is that the power does not depend on the load resistance value but is a function of the operating frequency, the resonant capacitance, and the supply voltage. Therefore, the power transferred to the vehicle can be kept constant despite variations in the magnetic coupling coefficient during stops and driving. The characteristics of the RI with ED were compared with two other competing schemes often used in charging stations as high-frequency sources. The proposed converter presents a higher intrinsic regulation capability because the frequency variation required to maintain the nominal power against load variation is lower. A further extension of this work could include optimizing the component size to achieve different goals, such as minimum losses, maximum efficiency, and minimum weight and volume.

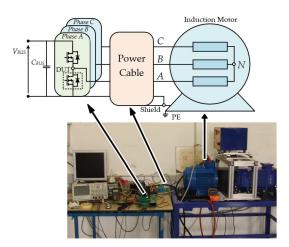

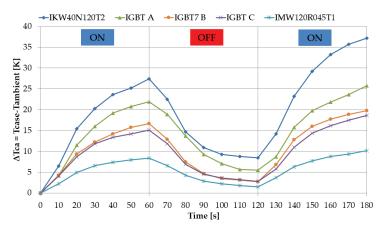

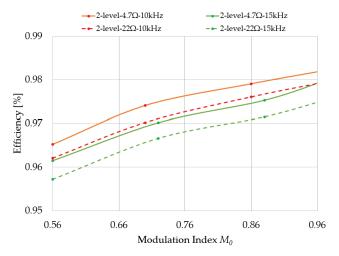

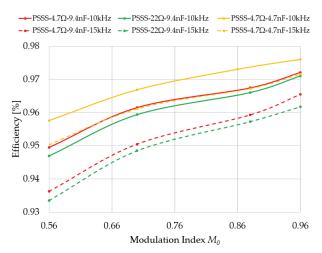

The two contributions that fall into category (b) focused on performance increases in VSDs and direct online induction motors (DOL-IMs). In [4], Di Benedetto et al. focused on implementing a high-performance power conversion system to reduce overvoltage in VSDs supplied by SiC-based inverters using long power cables. In particular, a three-phase two-level inverter with snubber circuits based on capacitors and diodes was investigated, designed, and tested to mitigate the overvoltage without sacrificing the conversion efficiency. Furthermore, an additional circuit was used to recover the energy from the snubbers avoiding increased losses. The proposed analysis was validated through experimental tests performed on a prototypal converter. The experimental results showed that, in the absence of the snubbers, the voltage at the motor terminals could reach twice the DC bus voltage when the cable length was equal to 15 m or 30 m: using a 400 V DC bus, the peak voltage at the motor side was 845 V, and the dV/dt was 9.95 V/ns. Instead, the proposed converter reduced the dV/dt to 1.47 V/ns and limited the overvoltage to 562 V. The power density was much higher than that for classical solutions such as the three-phase two-level inverter complemented by a bulky passive filter. The only drawback was a slight reduction in the conversion efficiency (0.976% against 0.982%). The proposed technique is promising, but further work should be devoted to finding a good compromise between the efficiency, dV/dt, and overvoltage of the entire electrical drive system.

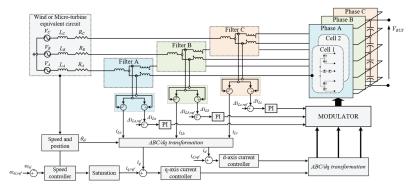

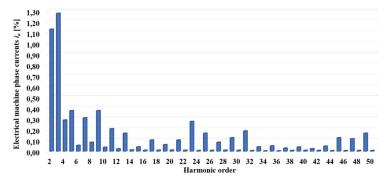

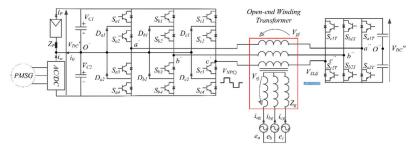

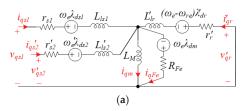

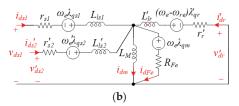

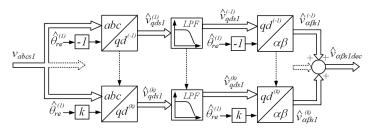

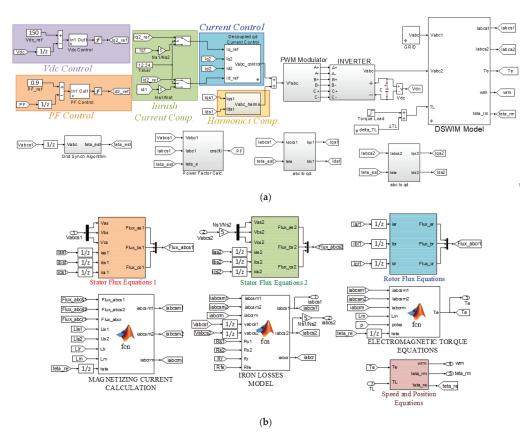

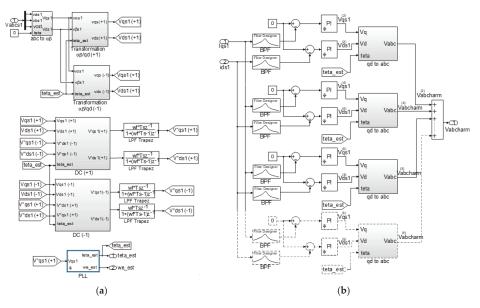

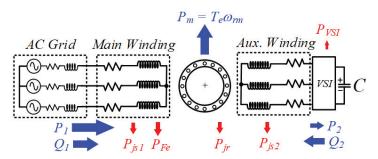

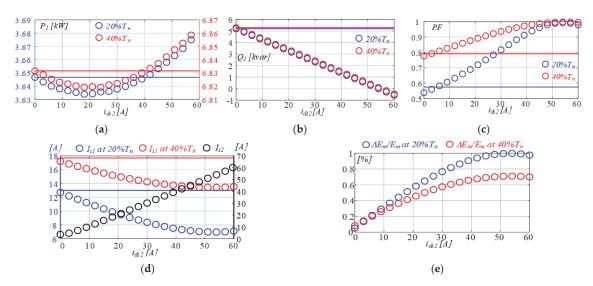

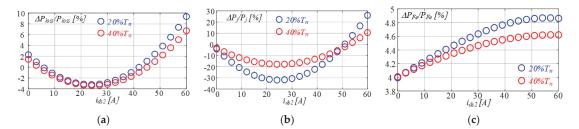

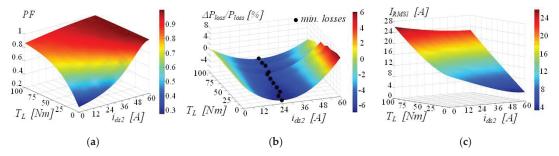

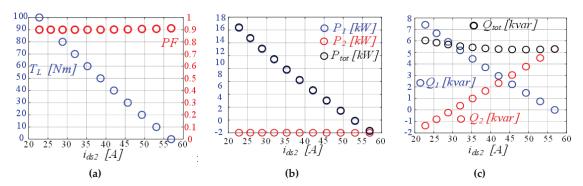

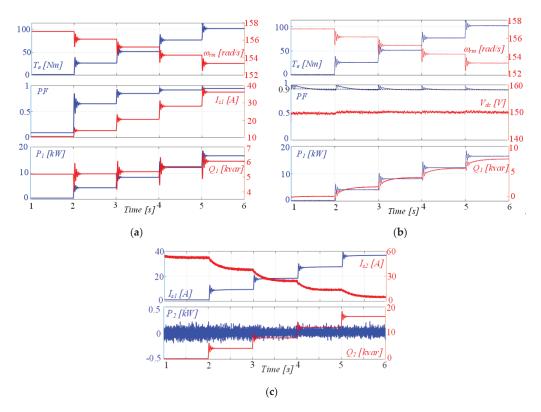

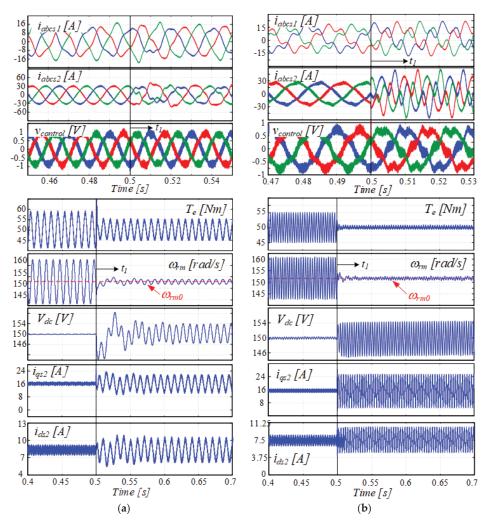

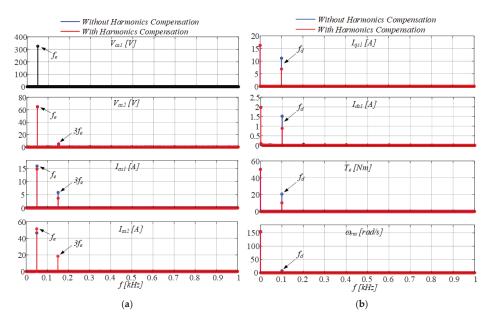

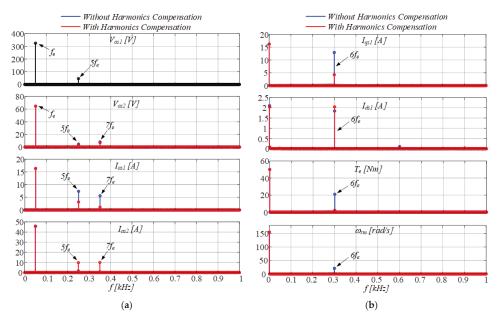

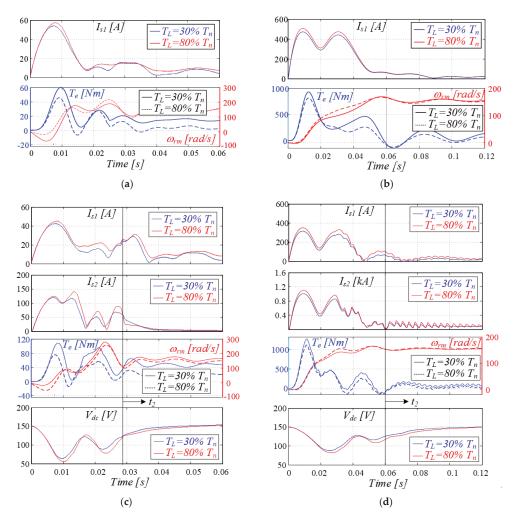

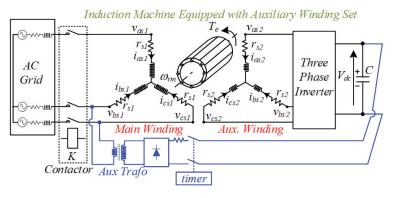

In [6], Tornello et al. presented a technique to improve the performance of induction motors by exploiting an auxiliary winding set supplied by a partial power inverter. In fact, three-phase DOL-IMs are the most dominant solution in the industrial sector, providing a variety of constant speed and variable load applications where dynamic requirements are not critical. However, they exhibit a low power factor at partial loads, which is mitigated by adding suitable capacitors; moreover, a significant in-rush current is generated at startup, leading to voltage dips, speed losses, torque pulsations, and possible activation of protection devices. In such applications, the additional cost implied by a VSD with a full-size inverter is not justified. However, the authors of [6] showed that it is possible to compromise cost and performance by using an auxiliary winding and a partial power inverter. The auxiliary winding features fewer turns than the main one and thus has lower voltage and power ratings. If suitably controlled by an inverter sized for a fraction of the motor's rated power and supplied through a floating capacitor, it allows for the following advantages to be obtained: (1) the machine power factor and, thus the efficiency, can be increased; (2) torque oscillations produced by the mechanical load or by distorted grid voltages can be mitigated; and (3) grid current peaks at motor start-up can be mitigated as well. The proposed technique was assessed by simulating a machine with a turn ratio of five. The results obtained showed that the power handled by the auxiliary winding and the inverter in the worst-case scenario was roughly one-fifth of the machine's rated power. Given that the inrush current mitigation depends on the capacitance of the floating capacitor, future extensions of this study could be focused on finding alternative approaches, such as performing the start-up at a higher DC-bus voltage to increase the energy stored in the floating capacitor.

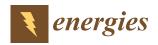

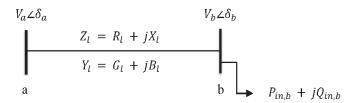

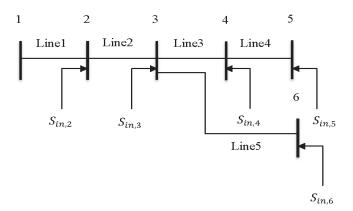

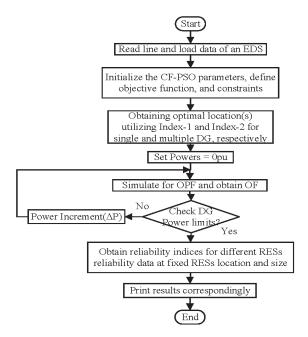

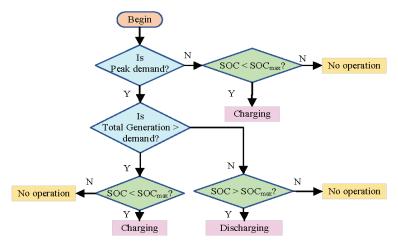

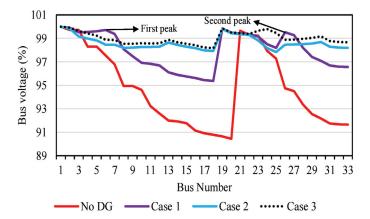

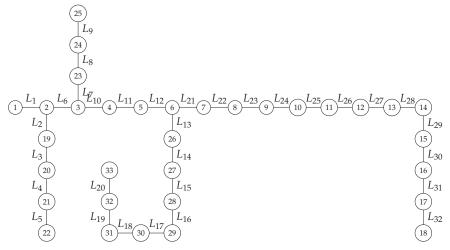

Lastly, regarding category (c), Kumar et al. applied an ELM technique to a microgrid with power converters interfacing RESs such as solar photovoltaics (SPV) and wind turbine generators (WTG), as well as battery storage systems (BSSs) [2]. The authors' goal was to minimize the detrimental effect of active and reactive power losses in the microgrid to exploit the full potential of green energy generation and use. First, the optimal locations for accommodating the distributed generators (DGs) were obtained by considering two specific indices. Then, an optimization problem was formulated to perform the optimal sizing of the DGs for achieving the ELM. The problem was solved using a constriction factor-based particle swarm optimization (CF-PSO) technique, which has overtaken many algorithms, including the genetic algorithms (GA). Finally, a reliability analysis (RA) of the microgrid was performed by evaluating five indices and using the optimal location and sizing of the RESs and BSSs. The outcomes of the study showed an enhancement in the electrical loss minimization and an improvement in the bus voltage profile compared with a system without DGs. In addition, the RA was repeated considering the uncertainties in the reliability data of the SPV and WTG interfaced by power converters, including the failure rate and the time to repair. It was shown that the microgrid's reliability significantly improved by considering the reliability data of the optimally integrated DGs. Some perspectives for future developments include the extension of the analysis to include aspects such as CO<sub>2</sub> emissions, economics, system protection and reconfiguration, and system security.

### 3. Conclusions

This Special Issue is composed of ten papers that presented various techniques aimed at improving the efficiency and performance of power electronics applications in power grids and electrical drives. The contributions provided offer valuable insights into the recent developments in such a field. The Guest Editor briefly summarized each contribution and highlighted some perspectives for future developments. It is hoped that the proposed techniques will soon be implemented in the energy industry and further improved.

Funding: This research received no external funding.

**Acknowledgments:** The Guest Editor is grateful to the MDPI Publisher for the invitation to hold such a position for this Special Issue of *Energies*. He also thanks all of the authors and reviewers for their commitment, which led to the success of this Special Issue. Furthermore, he is very grateful to the editorial staff of *Energies* for the valuable cooperation and support.

Conflicts of Interest: The author declares no conflict of interest.

### References

- Wang, S.; Alsokhiry, F.; Adam, G. Impact of Submodule Faults on the Performance of Modular Multilevel Converters. Energies 2020, 13, 4089. [CrossRef]

- Kumar, S.; Sarita, K.; Vardhan, A.; Elavarasan, R.; Saket, R.; Das, N. Reliability Assessment of Wind-Solar PV Integrated Distribution System Using Electrical Loss Minimization Technique. *Energies* 2020, 13, 5631. [CrossRef]

- Di Benedetto, M.; Lidozzi, A.; Solero, L.; Crescimbini, F.; Grbović, P. High-Performance 3-Phase 5-Level E-Type Multilevel– Multicell Converters for Microgrids. Energies 2021, 14, 843. [CrossRef]

- Di Benedetto, M.; Bigarelli, L.; Lidozzi, A.; Solero, L. Efficiency Comparison of 2-Level SiC Inverter and Soft Switching-Snubber SiC Inverter for Electric Motor Drives. Energies 2021, 14, 1690. [CrossRef]

- 5. Foti, S.; Testa, A.; De Caro, S.; Tornello, L.; Scelba, G.; Cacciato, M. Multi-Level Multi-Input Converter for Hybrid Renewable Energy Generators. *Energies* **2021**, *14*, 1764. [CrossRef]

- 6. Tornello, L.; Foti, S.; Cacciato, M.; Testa, A.; Scelba, G.; De Caro, S.; Scarcella, G.; Rizzo, S. Performance Improvement of Grid-Connected Induction Motors through an Auxiliary Winding Set. *Energies* **2021**, *14*, 2178. [CrossRef]

- 7. Luna, M.; Sferlazza, A.; Accetta, A.; Di Piazza, M.; La Tona, G.; Pucci, M. Modeling and Performance Assessment of the Split-Pi Used as a Storage Converter in All the Possible DC Microgrid Scenarios. Part I: Theoretical Analysis. *Energies* **2021**, *14*, 4902. [CrossRef]

- 8. Luna, M.; Sferlazza, A.; Accetta, A.; Di Piazza, M.; La Tona, G.; Pucci, M. Modeling and Performance Assessment of the Split-Pi Used as a Storage Converter in All the Possible DC Microgrid Scenarios. Part II: Simulation and Experimental Results. *Energies* **2021**, *14*, 5616. [CrossRef]

- 9. Madzharov, N.; Hinov, N. High-Performance Power Converter for Charging Electric Vehicles. Energies 2021, 14, 8569. [CrossRef]

- Aouichak, I.; Jacques, S.; Bissey, S.; Reymond, C.; Besson, T.; Le Bunetel, J. A Bidirectional Grid-Connected DC-AC Converter for Autonomous and Intelligent Electricity Storage in the Residential Sector. *Energies* 2022, 15, 1194. [CrossRef]

Article

# Impact of Submodule Faults on the Performance of Modular Multilevel Converters

Shuren Wang 1, Fahad Saeed Alsokhiry 2 and Grain Philip Adam 1,\*

- Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow G1 1RD, UK; shuren.wang@strath.ac.uk

- Renewable Energy Research Group and Department of Electrical and Computer Engineering, Faculty of Engineering, King Abdulaziz University, Jeddah 21589, Saudi Arabia; falsokhiry@kau.edu.sa

- \* Correspondence: grain.adam@strath.ac.uk

Received: 21 May 2020; Accepted: 24 July 2020; Published: 6 August 2020

Abstract: Modular multilevel converter (MMC) is well suited for high-power and medium-voltage applications. However, its performance is adversely affected by asymmetry that might be introduced by the failure of a limited number of submodules (SMs) or even by severe deviations in the values of SM capacitors and arm inductors, particularly when the number of SMs per arm is relatively low. Although a safe-failed operation is easily achieved through the incorporation of redundant SMs, the SMs' faults make MMC arms present unequal impedances, which leads to undesirable internal dynamics because of unequal power distribution between the arms. The severity of these undesirable dynamics varies with the implementation of auxiliary controllers that regulate the MMC internal dynamics. This paper studied the impact of SMs failure on the MMC internal dynamics performance, considering two implementations of internal dynamics control, including a direct control method for suppressing the fundamental component that may arise in the dc-link current. Performances of the presented and widely-appreciated conventional methods for regulating MMC internal dynamics were assessed under normal and SM fault conditions, using detailed time-domain simulations and considering both active and reactive power applications. The effectiveness of control methods is also verified by the experiment. Related trade-offs of the control methods are presented, whereas it is found that the adverse impact of SMs failure on MMC ac and dc side performances could be minimized with appropriate control countermeasures.

**Keywords:** ac/dc converter for medium and high-voltage applications; modular multilevel converter; submodule fault; fault-tolerant control and operation

### 1. Introduction

To date, modular multilevel converter (MMC) is a preferred technology for high-power medium/high-voltage distribution and transmission applications due to ease of scalability, modularity, reduced power losses, and high-quality ac and dc side waveforms [1]. However, the use of submodules (SMs) with floating distributed capacitors in MMC results in complex internal dynamics, which necessitates the adoption of a complex multi-layer control system compared to that of conventional voltage source converters.

Typically, the common-mode current of balanced MMC consists of dc and harmonic components, and its dc component acts as a link between the dc power and the power flowing through SMs, which constitute the MMC arms. The harmonic components of the common-mode current circulate between the arms, which are widely referred to as circulating currents representing undesirable parasitic components that add losses and increase SM capacitor voltage ripples [1]. In contrast, the differential-mode currents of an internally balanced MMC are the fundamental output currents that flow in the ac side and responsible for power transfer between the MMC arm and ac-side output

circuit. Normally, the SM capacitor voltages affect the synthesis of ac and dc side voltages of the MMC, i.e., the differential- and common-mode voltages, respectively. To reduce such couplings, several control methods exist in the open literature for suppression of the circulating current and regulation of the capacitor voltages independent of dc-link voltage [2].

SM, arm, and phase-leg voltages/energies represent three important elements or layers that must be controlled to minimize MMC internal dynamic interactions during normal and abnormal conditions. To manage the voltage differences between SMs within each arm, SM voltage balancing algorithms based on either centralized sorting or distributed control are employed [3,4]. Generally, MMCs with de-coupled internal-external dynamics respond faster to active power and dc voltage set-points; exhibit reduced output voltage distortion during major transients and overall impacts of cross-modulation on ac and dc side waveforms [5,6]. Wide-ranging research efforts have been invested into high-level controllers (capacitor voltage/energy sum controllers in arm and phase-leg levels) [7,8], in which predominantly ideal (identical) passive components are usually assumed. Although a large number of SMs may reduce the adverse effects of capacitance tolerances, passive component tolerances remain a prevalence issue, particularly, for MMCs, with a relatively low number of SMs per arm as anticipated in medium-voltage (MV) applications. Therefore, it is imperative to account for uncertainties due to passive component tolerances during MMC design and maintenance stages [9–12]. In this line, the adverse effects of asymmetrical cell capacitances on the ac output voltage of MMC that employs three-level flying capacitor SMs have been identified when the energy-based balancing approach was used in the high-level controllers that regulate the MMC internal dynamics [10]. The work in [11] has revealed the inducement of fundamental frequency ripple in the dc-link current of the MMC with asymmetrical arm inductances and proposed a voltage-based active control method to suppress the induced fundamental frequency ripple from the dc-link current.

On the other hand, a fault that happened in MMC SMs may cause operational issues ranging from distortion of ac and dc side voltages and currents to total disruption of power transfer. Methods for SMs fault detection and identification are proposed in [13–15], while increased MMC resiliency to SM faults through the concept of redundant SMs are discussed in [16] and [17]. With regard to the SM fault tolerance capability of the MMC, several SM-fault control methods have been discussed [18–21]. Two approaches are proposed, and the respective features are presented in [18]. The fundamental common-mode current ripple during SM faulty has been claimed in [19], and a dq-frame-based control method is proposed. However, this method depends on phase lock-loop for the ripple. Further research in [20,21] has proposed proportional resonant (PR) based control methods to suppress the fundamental ripple, but the control effects on the overall operation are not analyzed. Besides, in most previous works, the predominant assumption is that the number of faulty SMs is less than the number of redundant SMs or within a hot redundancy configuration, while the extreme condition, in which the number of faulty SMs is larger than the redundant SMs, is seldom discussed. In these cases, SM capacitor voltages would be increased, within a safe margin, for continuous operation.

Based on the preliminary findings in [22], this paper considered the adverse effects of MMC asymmetry caused by SM fault on both dc and ac sides when mainstream balancing control methods are employed. The differential-mode voltage balancing control method reduces the fundamental component in the common-mode and dc-link currents of the MMC with significant passive component tolerances. However, its effectiveness is limited since it is not direct control but via minor ripple injection, and its control objective is to nullify the differential-mode capacitor voltage sums. Considering the random nature of the passive component tolerance distribution within one phase-leg of an MMC-based power conversion system, the proportional-resonant (PR)-based controller that operates at the fundamental frequency was studied to suppress any fundamental circulating component that may arise in the three-phase common-mode currents. Comparatively, control effects on both ac and dc side performances were investigated in this paper. This paper is organized as follows. Section 2 provides a brief review of MMC operation fundamentals, and Section 3 discusses the issues that arise due to component tolerance and SM fault. Section 4 introduces the internal control methods

against internal imbalance. Section 5 verifies the effectiveness and assesses the performances of control methods. Finally, Section 6 summarizes this paper.

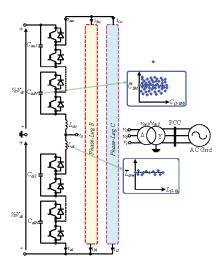

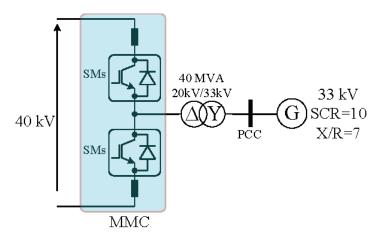

### 2. MMC Basic Operation

Figure 1 shows a three-phase half-bridge MMC, with  $V_{dc}$  and  $I_{dc}$  representing dc bus voltage and current, respectively. Each phase-leg consists of upper and lower arms, and each arm comprises a reactor with nominal inductance  $\overline{L_{ARM}}$  and N series-connected SMs. Each SM consists of a capacitor with nominal capacitance  $\overline{C_{SM}}$  and an IGBT-based half-bridge circuit. The term circulating current represents the ac component of the common-mode current,  $i_{cm}$ . The  $i_{cm}$  is mainly caused by cross-modulation of the upper and lower arms or, simply, the interaction of the arm voltages, currents, and switching functions. Strategies of the inner-arm SM voltage balancing and the second-order circulating current suppression have been widely discussed [2–5]. Figure 1 also shows a generic MMC connected into the ac grid through an interfacing transformer.

Figure 1. Modular multilevel converter (MMC) topology configuration.

Under the ideal condition, each MMC arm has an equivalent capacitance  $C_{ARM}$ , which can be calculated as:

$$C_{ARM} = \frac{\overline{C_{SM}}}{N} \tag{1}$$

As the arm equivalent capacitance is alternatively charging and discharging, the MMC internal power can be dynamically balanced as it transfers power between ac and dc sides.

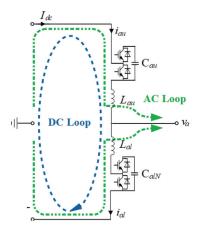

Figure 2 visualizes the MMC power paths, which can be divided into ac and dc loops. The dc loop depicted in Figure 2 represents the conduction path through dc output to MMC phase-leg, in which the common-mode current of each phase follows, which consists of ac and dc components ( $i_{cm} = I_d + i_h$ , where  $I_d$  and  $i_h$  are dc and harmonic components of  $i_{cm}$ ). In a three-phase MMC, the dc components of the common-mode currents of the phase legs add to the dc-link currents that flow in the positive and negative dc poles at the upper/positive and lower/negative dc nodes. In this way, the MMCs exchange power with the dc side. The ac components of the common-mode currents of the MMC phase legs are predominantly second-order harmonics and add to zero at upper and lower dc-link nodes; they represent parasitic currents, which increase the MMC SM capacitance requirement for a given voltage ripple and semiconductor losses. In contrast, the depicted ac loop represents the conduction path through which each MMC phase-leg exchanges active power with ac side and

fundamental frequency ac current flows. The output phase current represents the differential-mode current; for example, for a phase A,  $i_a = i_{au} - i_{al}$ , where  $i_a$ ,  $i_{au}$ , and  $i_{al}$  are output and upper and lower arm currents. In a balanced three-phase MMC, the fundamental frequency components of the currents add to zero at positive and negative dc nodes; while in an internally unbalanced MMC with asymmetrical ac and dc loops in the phase-legs, the asymmetries introduce zero and negative sequence fundamental frequency components in the common-mode currents of the phase-legs, which may leak into dc side and appear as fundamental frequency ripples in the dc current.

Figure 2. Diagram of MMC internal dynamics (phase A).

### 3. Internally Unbalanced MMC

The manufacturing process introduces significant inaccuracies and deviations in the values of passive components from the nominal. Therefore, instead of ideal and identical parameters, the practical MMC passive parameters can be assumed as a random distribution shown in Figure 1, with the inherent tolerances included. Commonly, circuit parameter tolerances are neglected to facilitate modeling, analysis, and controller design of complex energy conversion systems, such as the MMC. Nonetheless, it is essential to take countermeasures to neutralize any potential adverse implications of circuit parameter tolerances on MMC performance [10], for the following reasons:

- Because of a large number of passive components, parameter uncertainties due to manufacturing tolerances are inevitable and vary with several factors, including lifetimes.

- 2. Although the SM capacitor voltage balancing controller or algorithm distributes the total dc voltage across each arm equally amongst the SM capacitors, the switching devices of each SM only withstand an SM capacitor voltage. However, asymmetry due to parameter tolerances or SM faults may cause unequal power contribution and voltage distribution between the MMC arms. Thus, the current and voltage stresses in the switching devices and heat distribution may differ between arms.

- 3. Besides, capacitance and inductance differences between arms may actuate unbalanced fundamental frequency common-mode currents, which tend to leak into the dc side and appear as an undesirable current ripple in the dc current [23]. This is mainly because of the inherent power balancing mechanism of the MMC operation: in order to keep ac-dc power balance, different capacitor charge/discharge rate is induced, leading to fundamental frequency current difference between upper and lower arms.

The imbalance between upper and lower arms of one phase-leg, created by SM faults on the MMC internal dynamics, can be explained with the aid of the ac and dc loop described earlier. It is

well-established from the literature that the incorporation of redundant SMs can protect active and passive components of SMs from damage due to excessive over-voltage. However, with the hot redundancy approach, which is extensively studied, the post-fault voltage stresses on the MMC switching device and SM capacitor may differ from the pre-fault condition [18]. When an SM fails, it will be bypassed, and MMC continues to operate as normal, following a brief period of transients. For the simplicity of the analysis, this paper assumed that all the N SMs in the MMC arms are in use, and  $N_F$  SMs become faulty. Therefore, the equivalent arm capacitance is:

$$C'_{ARM} = \frac{\overline{C_{SM}}}{N - N_F} \tag{2}$$

Hence, 10% of the total number of SMs in a particular arm have failed and bypassed, leading to an 11% increase in the arm equivalent capacitance; hence, this scenario resembles an extreme case of passive component tolerances. Therefore, the consequences of SM faults are similar to that caused by passive components' tolerances, in which SM fault appears as a vertical asymmetry between the upper and lower arms of the same phase-leg and horizontal asymmetries relative to the healthy phase-legs. The work in [23] has demonstrated that the horizontal asymmetries between the phase-legs have negligible effects on dc-loop dynamics during steady-state, even though the phase-legs equivalent capacitances store different energies. In contrast, the vertical asymmetry has several operational implications, specifically, contamination of common-mode current by circulating current at the fundamental frequency, which increases semiconductor losses and contributes to the inducement of fundamental frequency ripple on the dc side, and reduced exploitable modulation index range, which generates the differential-mode voltage in the ac output. Throughout this paper, the sum and difference of arm capacitor voltage sums are referred to as the common- and differential-mode capacitor voltage sums of each phase-leg, respectively. For example, the common- and differential-mode capacitor voltage sums for phase-leg A are  $\sum_k^N V_{c,au} + \sum_k^N V_{c,al}$  and  $\sum_k^N V_{c,al} - \sum_k^N V_{c,al}$ , respectively, where  $\sum_k^N V_{c,au}$  and  $\sum_k^N V_{c,al}$  are phase-leg A upper and lower arm capacitor voltage sums.

### 4. MMC Internal Dynamics Controllers

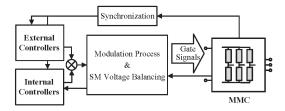

Figure 3 shows a generic depiction of the MMC control structure, which consists of internal dynamic and external system-level controllers, and modulator that generates the gating signals for the SMs. The internal dynamic controllers of the MMC operate at three levels, namely, SM, arm, and phase-leg. These controllers ensure adequate distribution of voltage stresses across the followings: SMs semiconductor switches and capacitors; upper and lower arms, to avoid narrowing of modulation index control range; phase-legs, to enable SM capacitor voltage regulation independent of the dc-link voltage and to prevent the development of ac and dc circuit currents between the phase-legs. In other words, the latter reduces interactions between MMC internal and external dynamics. The ac output (external) controllers include the following: positive and negative sequence separation stage; outer system-level controllers that regulate active power or dc voltage and reactive powers or ac voltage; inner positive and negative currents controllers that generate the principle modulation functions for the arms.

Figure 3. Diagram of MMC control structure.

Although theoretically, each MMC arm exchanges zero average power during one period, tolerances of the passive components lead to different levels of background energy stored in the SM capacitors, and presentation of different impedances by the MMC arms. Thus, the instantaneous power of the passive components deviates from their nominal values at the fundamental frequency. As voltage (or energy) of each arm is usually controlled by corresponding inter-arm balancing controllers, (also known as differential-mode capacitor voltage sum controller or vertical controllers), the power imbalance due to asymmetries of conduction paths will be compensated largely by injection fundamental frequency circulating currents into the common-mode loops. The asymmetries of energy levels and conduction path impendence lead to unequal contributions from the vertical balancing controllers of three phase-legs; hence, unequal fundamental currents in the common-mode loops. Recall that the vertical balancing controllers prioritize nullification of vertical voltage/energy asymmetry between the upper and lower arms over unintended consequences of injection odd-order harmonics into the common-mode currents [23]. Without a dedicated controller, a vertical asymmetry of any kind results in unbalanced fundamental common-mode currents in three phase-legs and thereby the development of fundamental frequency oscillations in the dc-link and increased semiconductor losses.

Two internal controllers to be assessed are:

### 4.1. Scheme-A

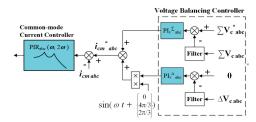

Conventionally, the common- and differential-mode capacitor voltage sums are controlled equally across all three-phase legs using the internal dynamic controllers shown in Figure 4. The regulation of average SM capacitor voltage (common-mode capacitor voltage sum) is achieved through the manipulation of common-mode current in conjunction with the common-mode capacitor voltage/energy sum controller (where  $\sum_{j=1}^{N} V_{cj}$  and  $\sum_{j=1}^{N} E_{cj}$  represent the common-mode capacitor voltage and energy sums per phase-leg, respectively). To eliminate the steady-state dc mean value error and suppress the  $2\omega$  circulating current, a PIR (proportional integral and resonant) controller with a resonant frequency at  $2\omega$  is adopted. This controller decouples SM capacitor voltage from the input dc-link voltage, hence the synthesis of the ac voltage from the dc-link voltage. A differential-mode capacitor voltage (or energy) sum control regulates arm active power using fundamental common-mode current injection, with another resonant frequency  $\omega$  component. Since the performances of energy-based internal dynamic control methods deteriorate as the stored energies in the arms vary rapidly with SM capacitance tolerances [22], the voltage-based balancing method shown in Figure 4 was adopted in this paper. From this point, it is referred to as control scheme A. From the ac side point of view, this method is able to maximize the use of full modulation index control range for the synthesis of the arm and ac output voltages, as determined by the minimum arm capacitor voltage sum. However, the by-product of this method is slightly higher fundamental current ripples in the dc loops and in the dc-link current.

Figure 4. Diagram of the common- and differential-mode capacitor voltage sum controller (Scheme-A) [23].

### 4.2. Scheme-B

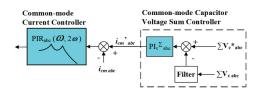

Since SM faults in one or multiple arms of the MMC lead to vertical and horizontal capacitance asymmetries, with the former cases, fundamental frequency ripples to appear in the common-mode currents, and a direct fundamental current ripple suppressing method (referred to as Scheme-B)

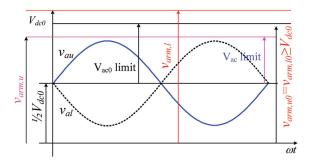

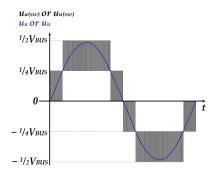

displayed in Figure 5 is proposed. Instead of targeting differential-mode capacitor voltage sums, the Scheme-B suppresses the fundamental frequency ripple in the common-mode current directly. This method uses an additional fundamental frequency PR controller to cancel the fundamental components in common-mode currents, thereby suppressing the dc-link current ripple, which is predominantly of fundamental frequency in the internally asymmetric MMC. However, the potential disadvantage of the proposed direct suppression of fundamental circulating current method is that the modulation-index control range might be reduced. In this method, the MMC arm with a smaller capacitor voltage sum would limit the ac voltage synthesis. Therefore, a dedicated design margin is needed to enable full exploitation of the modulation index control range in practical MMC under all operating conditions. Figure 6 illustrates potential impact of unequal or imbalance upper and lower capacitor voltage sums in the same phase-leg on modulation index control range (synthesis of the maximum arm or output ac voltage), assuming the SM capacitor of voltage sum of each arm is regulated at least at  $V_{dc0}$ , where  $V_{dc0}$  represents the nominal dc-link voltage. Notice that under the ideal case of internally balanced MMC, when the upper and lower arm voltages are limited by the nominal input dc-link voltage  $V_{dc0}$ , the maximum peak output phase ac voltage is  $\frac{1}{2}V_{dc0}$  for sinusoidal references and can rise to 0.577  $V_{dc0}$  ( $V_{dc0}/\sqrt{3}$ ) with 3rd harmonic injection. Notice that when upper and lower arms of a phase-leg suffer from unequal SM capacitor voltage sums, the arm with the least capacitor voltage sum defines the maximum safe limits for the synthesis of the output ac voltage. Should the arm with the largest capacitor voltage sum successfully synthesizes the requested voltage set by its modulation function, and the arm with the least capacitor voltage sum fails to synthesize the target voltage, the common-mode voltage that the phase-leg presents at the dc side may contain fundamental component besides the dc voltage. These may further exacerbate fundamental frequency ripples in the dc current. Besides, the imbalance in the SMs capacitor voltage sums, particularly, between the upper and lower arms, may appear as an imbalance in the differential-mode voltages of the phase-legs, which resemble three-phase output voltages. In Figure 6,  $v_{arm,u0}$  and  $v_{arm,l0}$  denote the upper and lower arm voltages in the ideal case, corresponding to balanced upper and lower SMs capacitor voltage sums;  $v_{arm,u}$  and  $v_{arm,l}$  stand for the upper and lower arm voltages under unequal upper and lower SMs capacitor voltage sums, in which the upper arm has the least SMs capacitor voltage sum and limits the maximum attainable ac voltage.

Figure 5. Diagram of internal control structure against inter-arm parametric imbalance (Scheme-B) [23].

Figure 6. Arbitrary arm voltage of the MMC that suffers from unequal capacitor voltage sums in the upper and lower arms of the same phase-leg.

In summary, since trade-offs exist, it is important to conclusively establish and quantitatively evaluate the performance of the above methods, under SM faults or tolerances conditions. The two trade-off cases are:

- 1. Prioritization of balanced capacitor voltage sums of the arms over the suppression of fundamental frequency current into the dc loops of three phase-legs;

- Prioritization of suppressing fundamental frequency currents in the dc loop over active balancing of the capacitor voltage sums of the upper and lower arms.

### 5. Simulations

This section presents detailed MATLAB-based simulations that assess the MMC performance during SM faults for two different implementations of internal dynamic controllers described earlier, i.e., control schemes A and B, considering two distinct operating points. The simulated MMC models include the following external controllers: active and reactive powers; positive and negative sequence currents. Two control methods for internal dynamics considered in this section are:

- Scheme-A consists of common- and differential-mode capacitor voltage sum balancing controllers, which include a circulating current suppression controller.

- Scheme-B consists of common-mode capacitor voltage sum control in conjunction with the proposed direct fundamental circulating current suppression. Circulating current suppression controller is also included.

Sorting-based SM level voltage balancing method is adopted, and modulators based on level-shifted pulse width modulation and phase disposition carriers are used to generate the gating signals for the SMs.

### 5.1. Impact of SM Faults on MMC Operation for Different Control Schemes

This subsection presents time-domain simulations that illustrate the behaviors of the 20-cell MMC in Figure 7 under SM faults. The parameters of the simulated MMC are listed in Table 1. In this study, two faulted SMs represented 10% of the total SMs per arm, and the SM fault was applied at the upper arm of phase-leg A at 0.4 s, and the two faulty SMs were bypassed.

Figure 7. Simplified single line diagram of the 40 kV, 40 MVA, and 20-cell MMC connected to ac grid.

Table 1. Simulation Parameters.

| System Parameters              | 3                 | Value                          |

|--------------------------------|-------------------|--------------------------------|

| DC voltage                     | $V_{dc}$          | 40 kV                          |

| Rated power                    | S                 | 40 MVA                         |

| AC grid line to line voltage   | $v_{ac2}$         | 33 kV                          |

| AC grid frequency              | F                 | 50 Hz                          |

| Transformer ratio              | $v_{ac1}/v_{ac2}$ | 20 kV/33 kV                    |

| Transformer leakage-inductance | $L_T$             | 0.2 pu                         |

| Numbers of SMs per arm         | N                 | 20                             |

| Expected arm inductance value  | L                 | 0.18 pu                        |

| Expected SM capacitance value  | С                 | 6.7 mF                         |

| DC cable length                | $D_{cable}$       | 10 km                          |

| DC cable resistance per km     | $R_{cable}$       | $10 \text{ m}\Omega/\text{km}$ |

| DC cable inductance per km     | $L_{cable}$       | 1.4 mH/km                      |

| DC cable capacitance per km    | $C_{cable}$       | 0.1 μF/km                      |

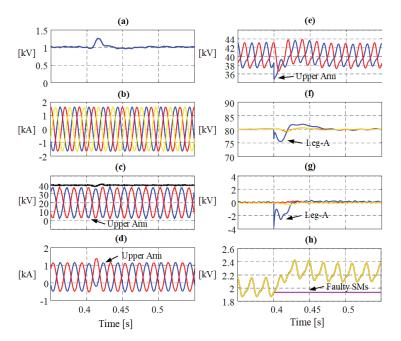

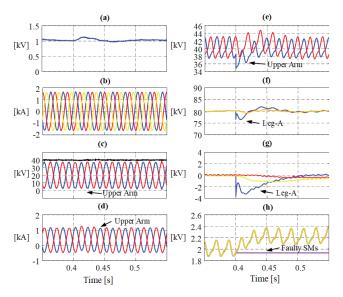

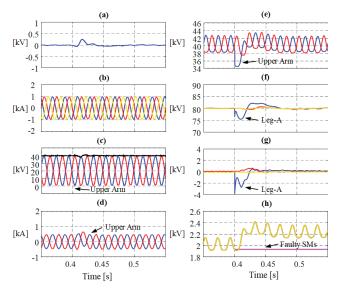

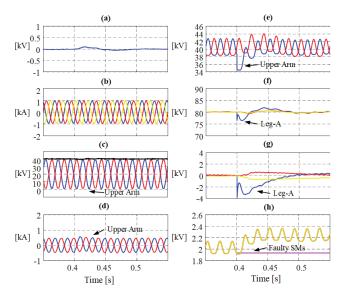

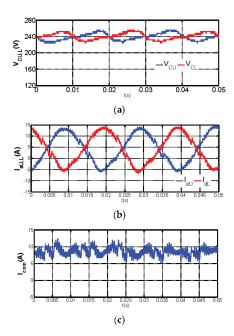

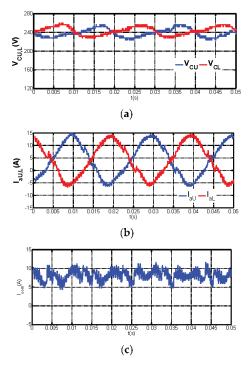

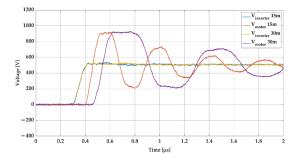

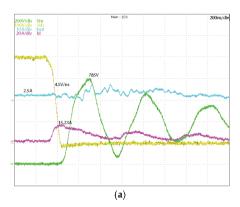

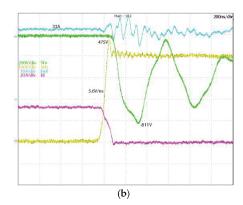

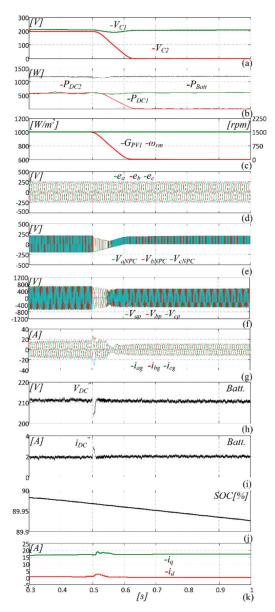

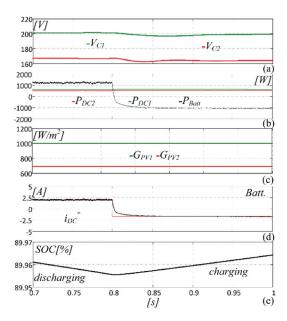

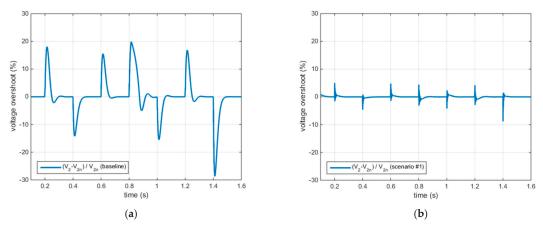

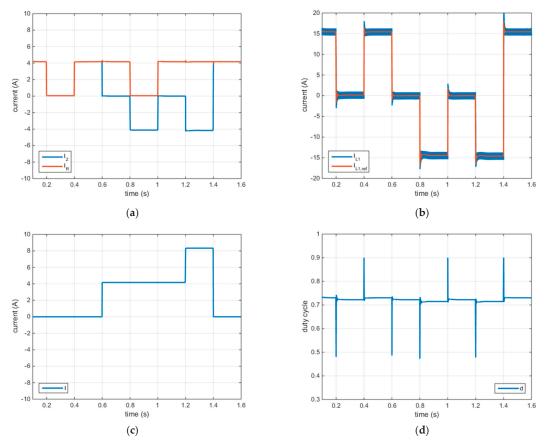

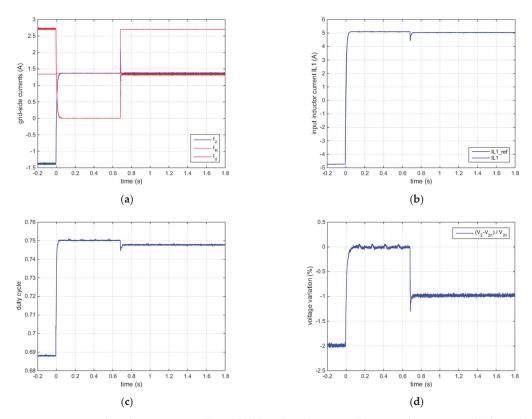

Figures 8 and 9 show simulation waveforms for the control schemes A and B, respectively. These results are obtained when the MMC injects a 1.0 pu (40 MW) active power into the ac grid and regulates reactive power at zero. In contrast, Figures 10 and 11 display simulation waveforms when the MMC injects 0.6 pu (24 MVAr) capacitive reactive power and zero active power into the ac grid, with control schemes A and B, respectively. The 0.6 pu (24 MVAr) represents the maximum capacitive reactive power, which the simulated MMC can inject into the ac grid.

**Figure 8.** Simulation waveforms of the MMC under submodule (SM) fault and control scheme-A operates in active power mode: (a) dc current, (b) ac current, (c) leg A upper and lower arm voltages superimposed on its common-mode voltage, (d) leg A upper and lower arm currents, (e) leg A upper and lower capacitor voltage sums, (f) common-mode capacitor voltage sums of three phase-legs, (g) differential-mode capacitor voltage sums of three phase-legs, and (h) leg A upper arm SM voltages.

**Figure 9.** Simulation waveforms of the MMC under SM fault and control scheme-B operates in active power mode: (a) dc current, (b) ac current, (c) leg A upper and lower arm voltages superimposed on its common-mode voltage, (d) leg A upper and lower arm currents, (e) leg A upper and lower capacitor voltage sums, (f) common-mode capacitor voltage sums of three phase-legs, (g) differential-mode capacitor voltage sums of three phase-legs, and (h) leg A upper arm SM voltages.

**Figure 10.** Simulation waveforms of the MMC under SM fault and control scheme-A operates in reactive power mode: (a) dc current, (b) ac current, (c) leg A upper and lower arm voltages superimposed on its common-mode voltage, (d) leg A upper and lower arm currents, (e) leg A upper and lower capacitor voltage sums, (f) common-mode capacitor voltage sums of three phase-legs, (g) differential-mode capacitor voltage sums of three phase-legs, and (h) leg A upper arm SM voltages.

**Figure 11.** Simulation waveforms of the MMC under SM fault and control scheme-B operates in reactive power mode: (a) dc current, (b) ac current, (c) leg A upper and lower arm voltages superimposed on its common-mode voltage, (d) leg A upper and lower arm currents, (e) leg A upper and lower capacitor voltage sums, (f) common-mode capacitor voltage sums of three phase-legs, (g) differential-mode capacitor voltage sums of three phase-legs, and (h) leg A upper arm SM voltages.

The observations drawn from results of Scheme-A presented in Figure 8 can be summarized as follows:

- 1. When the SM fault occurs in the upper arm of leg-A at 0.4 s, the upper arm capacitor voltage sum decreases briefly and quickly recovers by sinking extra dc current, largely, due to the actions of differential-mode capacitor voltage sum or arm voltage balancing controllers of Scheme-A. During the transient period, the upper and lower arm voltages of the faulty phase exhibit brief disturbances, while the three-phase ac output currents remain unaffected, see Figure 8a–e.

- 2. Following the SM fault, the common-mode capacitor voltage sums of three legs return to their pre-fault set-points, with the deviations emerged in both common- and differential-mode capacitor voltage sums of the three phase-legs (including the faulty phase-leg A) at 0.4 s that are quickly eliminated, see Figure 8f,g. These results demonstrate the importance of inter-arm vertical controllers implemented in Scheme-A.

- 3. The plots in Figure 8h show that the healthy SM capacitor voltages of the faulty arm (upper arm of phase-leg A) increase due to a reduced number of active SMs that could contribute to the target capacitor voltage sums enforced by collective actions of common- and differential-mode controllers of Scheme-A. After bypass of the faulty SMs, their capacitor voltages do not exhibit any fluctuations associated with fundamental and remnant of 2nd harmonic currents as anticipated.

Simulation waveforms of the 20-cell MMC in Figure 7, with the Scheme-B, are presented in Figure 9. The observations drawn from the results in Figure 9 are as follows:

1. MMC with the use of Scheme-B exhibits slightly different behavior from that with the control scheme A. The dc-link current displayed in Figure 9a exhibits smaller increase, and SM capacitor voltage sum of the faulty leg (an upper arm of phase-leg A) exhibits slightly small under-shoot and over-shoot compared to those with Scheme-A. The smaller increase in the dc current with control scheme B can be attributed to the absence of vertical controllers, which actively inject

- additional active powers and fundamental currents into the common-mode loops in order to enforce equalization of the arm capacitor voltage sums.

- 2. The Scheme-B makes the MMC less sensitive to SM faults and remains capable of synthesizing the output ac voltages that the ac grid imposes at its ac terminals, with three-phase ac output currents remain unaffected, see Figure 9a,e.

- 3. The common-mode capacitor voltage sums of the three phase-legs remain tightly controlled and less affected throughout as the control scheme B only enforces equal dc voltages across the MMC phase-legs, with the SM level capacitor voltage controller ensuring the imposed dc voltage across the phase-legs being equally distributed across the SM capacitors. These are achieved without paying any attention to the symmetry of upper and lower arm capacitor voltage sums, see Figure 9f,g.

- 4. The healthy SMs have slightly lower capacitor voltages with Scheme-B than that of Scheme-A due to lower dc voltage across the faulty arm in post-fault condition, as demonstrated by the clear drift the differential-mode voltage displayed in Figure 9g. As in the previous case, the capacitor voltages of the faulty SMs become flat under the post-fault condition.

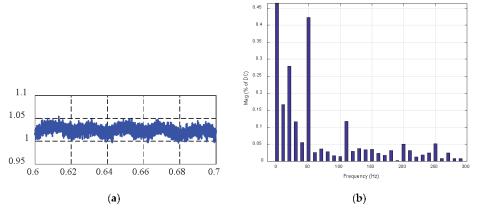

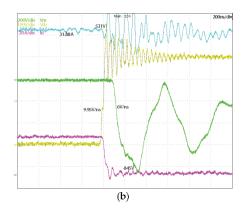

In addition, the results of fast Fourier transform (FFT) analysis presented in the appendix for the MMC in Appendix A, when it is controlled using the control schemes A and B, respectively, show that the amplitudes of the fundamental frequency component in dc-link current are 11.3 A and 4.1 A, respectively. These results confirm the effectiveness of the Scheme-B in dealing with fundamental frequency ripples in the dc loop (common-mode and dc-link currents) compared to that of the Scheme-A.

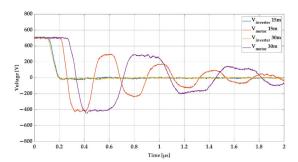

The observations, drawn from Figures 10 and 11 when control schemes A and B are used to control the 20-cell MMC in Figure 7, are as follows:

Figures 10a and 11a show that the MMC dc current for the two control schemes is zero, as anticipated during pure reactive power exchange. In line with previous cases, these results show that the dc current of Scheme-A exhibits a brief period of larger temporary over-current due to actions of arm balancing controllers, which force the dc voltages across all arms to be equal.

Figures 10b–d and 11b–d display the three-phase output currents and phase-leg A upper and lower arm voltages superimposed on the common-mode capacitor voltage sum of phase A. Notice that reactive power output reaches the limit as the arm voltage synthesized nearly touches the limits in both cases.

Although the common-mode capacitor voltage sums of the schemes A and B exhibit similar behaviors, the capacitor voltage sums of the upper and lower arms of the faulty phase-leg exhibit slightly different behaviors, see Figure 10e,f and Figure 11e,f. Besides, the differential-mode capacitor voltage sums in Figures 10g and 11g present different convergence patterns, as Scheme-A controls the differential-mode capacitor voltage sum actively.

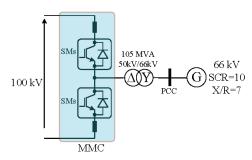

### 5.2. Parametric Studies of Asymmetric MMC Operation

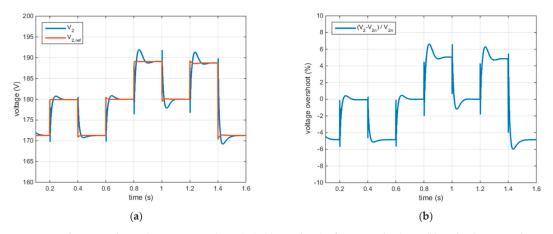

To further generalize the findings of the above detailed quantitative studies on asymmetries introduced by the MMC SM faults, additional parametric studies are conducted on a 50-cell MMC using control schemes A and B. The test system parameters are listed in Table 2. To reproduce more representative MMC asymmetries that may arise from SM faults or severe deviations in the values of passive parameters from their nominal values, the SM capacitance ( $C_u$  and  $C_l$ ) and arm inductance ( $L_u$  and  $L_l$ ) of the upper and lower arms are varied within  $\pm 10\%$  of their nominal values,  $C_0$  and  $L_0$  (i.e.,  $0.9C_0 \le C_{u,\,l} \le 1.1C_0$  and  $0.9L_0 \le L_{u,\,l} \le 1.1L_0$ ). In the parametric studies, the 50-cell MMC in Figure 12 injects 100 MW into the ac grid at a unity power factor.

| System parameters              | Value             |             |

|--------------------------------|-------------------|-------------|

| DC voltage                     | $V_{dc}$          | 100 kV      |

| Rated power                    | s                 | 100 MVA     |

| AC grid line to line voltage   | $v_{ac2}$         | 66 kV       |

| AC grid frequency              | F                 | 50 Hz       |

| Transformer ratio              | $v_{ac1}/v_{ac2}$ | 50 kV/66 kV |

| Transformer leakage-inductance | $L_T$             | 0.2 pu      |

| Numbers of SMs per arm         | N                 | 50          |

| Expected arm inductance value  | L                 | 0.18 pu     |

| Expected SM capacitance value  | C                 | 6.7 mF      |

Table 2. Simulation Parameters.

**Figure 12.** Test system employed in parametric studies with a 50-cell MMC, in which 5 faulty SMs represent 10% of the total number of SMs per arm.

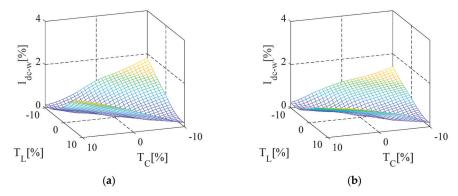

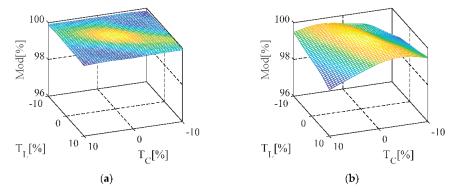

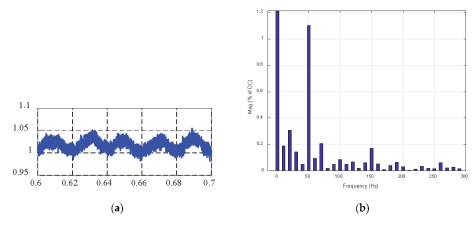

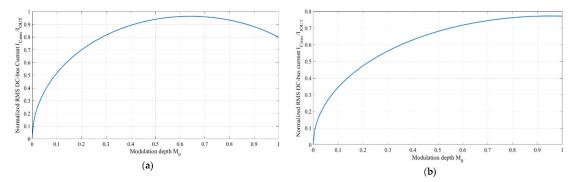

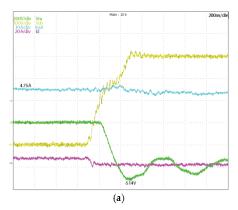

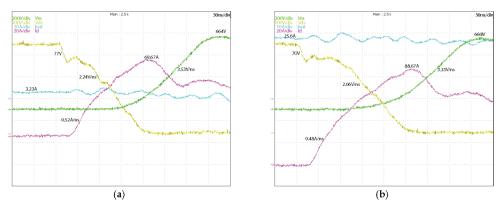

Figures 13 and 14 present side-by-side comparisons of the normalized fundamental frequency ripple in the dc current by its average and maximum achievable modulation range versus average asymmetries in the SM capacitances and inductances between the upper and lower arms of the same phase-leg, for control schemes A and B. The observations drawn from these parametric studies are:

- 1. Figure 13a,b show that the highest fundamental frequency ripple in the dc current is observed when the upper and lower arms of the same phase-leg simultaneously present a higher mismatch in both SM capacitance and arm inductance, i.e., at extrema of  $(T_C \text{ and } T_L) = (-10\% \text{ and } -10\%)$  and (+10% and +10%). In contrast, the lowest fundamental current ripples are observed when  $T_C \text{ and } T_L \text{ are (0 and 0), (+10\% \text{ and } -10\%), and (-10\% \text{ and } +10\%), entailing the polarities of SM capacitance, and arm inductance tolerances affect the magnitude of the fundamental current ripple on dc-side current. Notice that these observations are applied to both control schemes.$

- 2. Quantitatively, comparative parametric studies shown in Figure 13a,b confirm that the Scheme-B, which prioritizes suppression of fundamental frequency ripple in the common-mode currents, exhibits a lower residual ripple in the dc current compared to Scheme-A that prioritizes strict management of voltage stress within the converter over dc side waveform quality.

- 3. Figure 14a,b display the variations of maximum attainable modulation index in faulty leg-A, with control schemes A and B. The active arm balancing control of scheme A helps to preserve the maximum achievable modulation index range during severe SM capacitance and arm inductance asymmetries. In contrast, with Scheme-B, the MMC modulation index range experiences small reduction as the levels of passive parameter mismatch increase. The worst-case reduction observed in the modulation index range is about 1.5%, which corresponds to a small reduction in MMC ac voltage synthesis and reactive power generation capabilities.

- 4. The Scheme-A ensures a dc offset free in ac output voltage independent of the severity of MMC internal asymmetries at the expense of compromised dc current quality. While Scheme-B increases the risk of dc injection into the ac grid, particularly, when the arms with minimum capacitor

voltage sums are no longer sufficient to synthesize the required ac voltage to exchange the desired active and reactive powers. These observations are in line with the discussions above.

**Figure 13.** Variation of fundamental frequency dc-link current ripple magnitude (pu) with SM capacitance tolerances  $T_C$  and arm inductor tolerances  $T_L$ : (a) Scheme-A and (b) Scheme-B.

**Figure 14.** Variation of fundamental frequency dc-link current ripple magnitude (pu) with SM capacitance tolerances  $T_C$  and arm inductor tolerances  $T_L$ : (a) Scheme-A, and (b) Scheme-B.

It is worth emphasizing that the 20-cell MMC in previous studies is a good representation of the scenario with low SMs numbers per arm. In such a scenario, the loss of 10% of total SMs per arm in absolute term, namely, two SMs, is of practical significance, particularly from the following point of views: (1) Increased duties on remaining and healthy SMs (frequency of insertion and bypass of SM capacitors). (2) Increased sampling errors in the synthesis of the dc, arm, and output ac voltages. (3) Average switching frequency per device. (4) Increased likelihood of occurrence in a practical system. On the other hand, the 50-cell MMC is a relatively good representation for upper MV applications, in which the likelihood of loss of 10% of the total number of SMs per arm is much lower but remains possible with less impact on the quality of the ac and dc side waveforms and duties on SM capacitors.

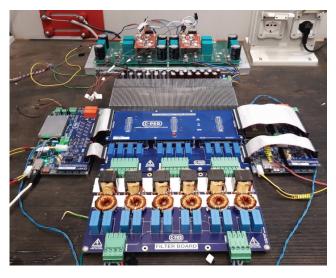

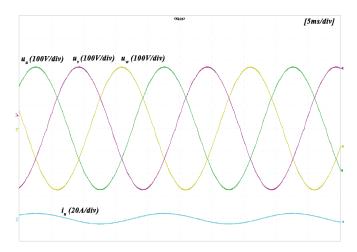

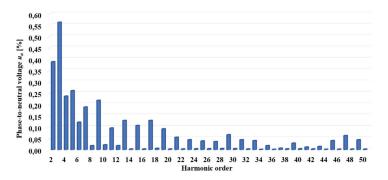

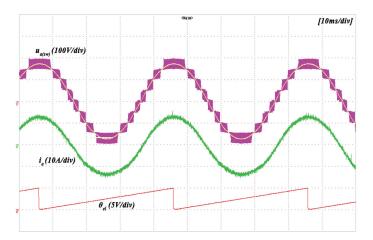

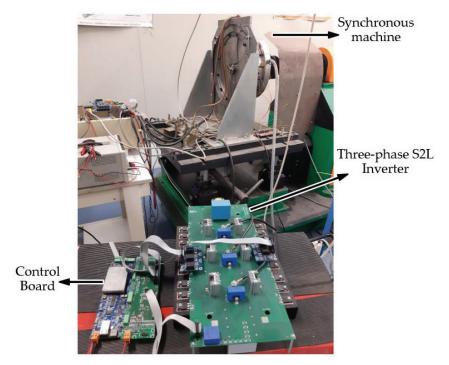

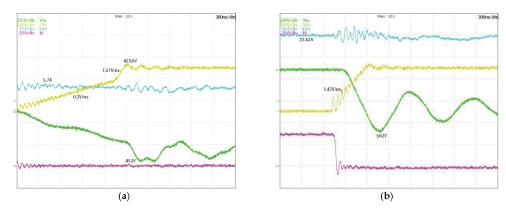

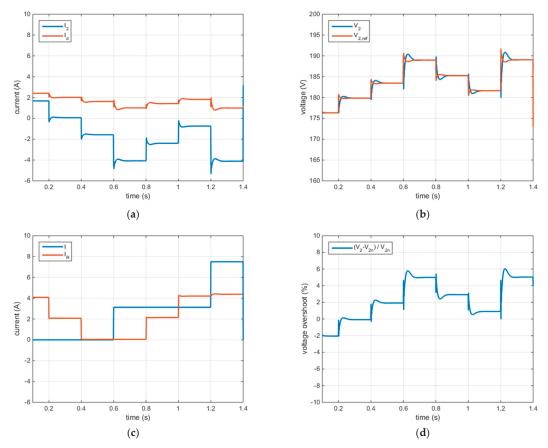

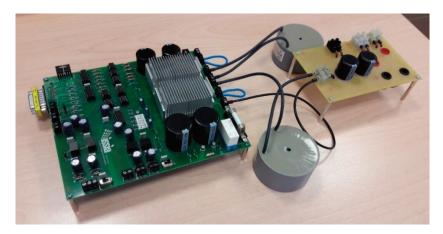

### 6. Experimental Verifications

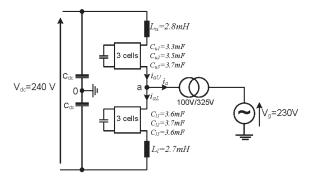

Since SM faults make the MMCs present unequal equivalent capacitances per arm and per phase-leg bases, this section emulates the steady-state impacts of SM faults through the deliberate use of unequal cell capacitances and arm inductances on experimental test rig of a single-phase grid-connected MMC with three cells per arm, see Figure 15. The MMC test rig is equipped with the following controllers: 1) active and reactive power controller, which sets P = 2kW and Q = 0, 2) inner current controller, circulating current suppression controller, 3) horizontal/common-mode capacitor

voltage sum, 4) level-shifted pulse width modulation with 1 kHz carrier frequency and sorting-based capacitor voltage balancing.

Figure 15. Experimental test of a 3-cell HB-MMC.