Special Issue Reprint

# Radiation Effects of Advanced Electronic Devices and Circuits

Edited by Yaqing Chi, Li Cai and Chang Cai

mdpi.com/journal/electronics

## **Radiation Effects of Advanced Electronic Devices and Circuits**

## **Radiation Effects of Advanced Electronic Devices and Circuits**

Editors

Yaqing Chi Li Cai Chang Cai

Editors

Yaqing Chi

College of Computer

National University of Defense Technology

Changsha China Li Cai

Institute of Modern Physics Chinese Academy of Sciences

Lanzhou

China

Chang Cai

State Key Laboratory of ASIC

and System Fudan University

Shanghai China

Editorial Office

MDPI

St. Alban-Anlage 66

4052 Basel, Switzerland

This is a reprint of articles from the Special Issue published online in the open access journal *Electronics* (ISSN 2079-9292) (available at: https://www.mdpi.com/journal/electronics/special\_issues/K198F4P50R).

For citation purposes, cite each article independently as indicated on the article page online and as indicated below:

Lastname, A.A.; Lastname, B.B. Article Title. Journal Name Year, Volume Number, Page Range.

ISBN 978-3-7258-1481-7 (Hbk) ISBN 978-3-7258-1482-4 (PDF) doi.org/10.3390/books978-3-7258-1482-4

Cover image courtesy of Yaqing Chi

© 2024 by the authors. Articles in this book are Open Access and distributed under the Creative Commons Attribution (CC BY) license. The book as a whole is distributed by MDPI under the terms and conditions of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) license.

## Contents

| About the Editors vii                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Yaqing Chi, Chang Cai and Li Cai Radiation Effects of Advanced Electronic Devices and Circuits Reprinted from: Electronics 2024, 13, 1073, doi:10.3390/electronics13061073                                                                                                                      |

| Mingzhu Xun, Yudong Li, Jie Feng, Chengfa He, Mingyu Liu and Qi Guo  Effect of Proton Irradiation on Complementary Metal Oxide Semiconductor (CMOS)  Single-Photon Avalanche Diodes                                                                                                             |

| Reprinted from: <i>Electronics</i> <b>2024</b> , <i>13</i> , 224, doi:10.3390/electronics13010224                                                                                                                                                                                               |

| Hualiang Zhou, Hao Yu, Zhiyang Zou, Zhantao Su, Qianyun Zhao, Weitao Yang and Chaohui<br>He                                                                                                                                                                                                     |

| Evaluation of Single Event Upset on a Relay Protection Device  Reprinted from: <i>Electronics</i> <b>2024</b> , <i>13</i> , 64, doi:10.3390/electronics13010064                                                                                                                                 |

| Ruiqiang Song, Jinjin Shao, Yaqing Chi, Bin Liang, Jianjun Chen and Zhenyu Wu Machine Learning-Based Soft-Error-Rate Evaluation for Large-Scale Integrated Circuits Reprinted from: Electronics 2023, 12, 4978, doi:10.3390/electronics12244978                                                 |

| Yutang Xiang, Xiaowen Liang, Jie Feng, Haonan Feng, Dan Zhang, Ying Wei, et al. Refined Analysis of Leakage Current in SiC Power Metal Oxide Semiconductor Field Effect Transistors after Heavy Ion Irradiation Reprinted from: Electronics 2023, 12, 4349, doi:10.3390/electronics12204349     |

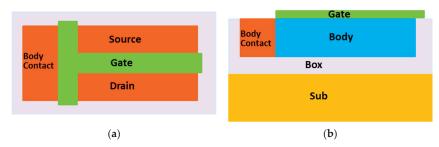

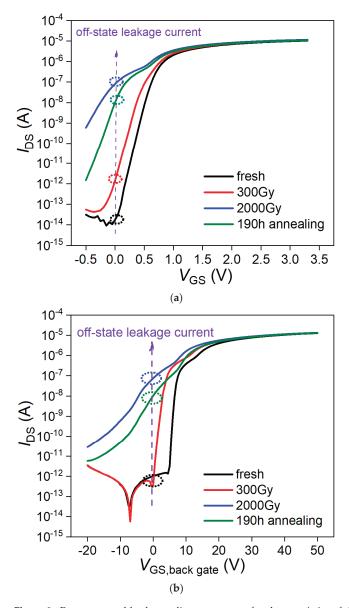

| Lan Lin, Zhongchao Cong and Chunlei Jia Recovery Effect of Hot-Carrier Stress on $\gamma$ -ray-Irradiated 0.13 $\mu$ m Partially Depleted SOI n-MOSFETs                                                                                                                                         |

| Reprinted from: <i>Electronics</i> <b>2023</b> , <i>12</i> , 4233, doi:10.3390/electronics12204233 60                                                                                                                                                                                           |

| Mingyu Liu, Chengfa He, Jie Feng, Mingzhu Xun, Jing Sun, Yudong Li and Qi Guo Analysis of Difference in Areal Density Aluminum Equivalent Method in Ionizing Total Dose Shielding Analysis of Semiconductor Devices Reprinted from: Electronics 2023, 12, 4181, doi:10.3390/electronics12194181 |

| Reprinted from: Electronics 2023, 12, 4101, doi:10.3390/ electronics12194101                                                                                                                                                                                                                    |

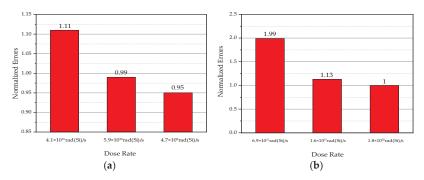

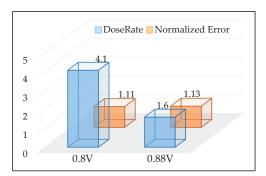

| Tongde Li, Jingshuang Yuan, Yang Bai, Chunqing Yu, Chunliang Gou, Lei Shu, et al. Research on High-Dose-Rate Transient Ionizing Radiation Effect in Nano-Scale FDSOI Flip-Flops                                                                                                                 |

| Reprinted from: <i>Electronics</i> <b>2023</b> , 12, 3149, doi:10.3390/electronics12143149                                                                                                                                                                                                      |

| Xiaowen Liang, Haonan Feng, Yutang Xiang, Jing Sun, Ying Wei, Dan Zhang, et al.  Oxide Electric Field-Induced Degradation of SiC MOSFET for Heavy-Ion Irradiation  Reprinted from: Electronics 2023, 12, 2886, doi:10.3390/electronics12132886                                                  |

| Zhikang Yang, Lin Wen, Yudong Li, Jie Feng, Dong Zhou, Bingkai Liu, et al.<br>Heavy Ion Single Event Effects in CMOS Image Sensors: SET and SEU                                                                                                                                                 |

| Reprinted from: <i>Electronics</i> <b>2023</b> , <i>12</i> , 2833, doi:10.3390/electronics12132833                                                                                                                                                                                              |

| Jie Feng, Hai-Chuan Wang, Yu-Dong Li, Lin Wen and Qi Guo                                                                                                                                                                                                                                        |

| Mechanism of Total Ionizing Dose Effects of CMOS Image Sensors on Camera Resolution                                                                                                                                                                                                             |

| Reprinted from: <i>Electronics</i> <b>2023</b> , 12, 2667, doi:10.3390/electronics12122667                                                                                                                                                                                                      |

| Haonan Feng, Xiaowen Liang, Xiaojuan Pu, Yutang Xiang, Teng Zhang, Ying Wei, et al. Total Ionizing Dose Effects of $^{60}$ Co $\gamma$ -Ray Radiation on Split-Gate SiC MOSFETs                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reprinted from: Electronics 2023, 12, 2398, doi:10.3390/ electronics12112398 129                                                                                                                                                                                                                         |

| Weitao Yang, Yonghong Li, Yang Li, Zhiliang Hu, Jiale Cai, Chaohui He, et al.  Neutron Irradiation Testing and Monte Carlo Simulation of a Xilinx Zynq-7000 System on Chip  Reprinted from: Electronics 2023, 12, 2057, doi:10.3390/electronics12092057                                                  |

| Yihao Cui, Jie Feng, Yudong Li, Lin Wen and Qi Guo<br>Proton Radiation Effects of CMOS Image Sensors on Different Star Map Recognition Algorithms<br>for Star Sensors                                                                                                                                    |

| Reprinted from: <i>Electronics</i> <b>2023</b> , <i>12</i> , 1629, doi:10.3390/electronics12071629                                                                                                                                                                                                       |

| Xiao Li, Jiangwei Cui, Qiwen Zheng, Pengwei Li, Xu Cui, Yudong Li and Qi Guo Study of the Within-Batch TID Response Variability on Silicon-Based VDMOS Devices Reprinted from: Electronics 2023, 12, 1403, doi:10.3390/electronics12061403                                                               |

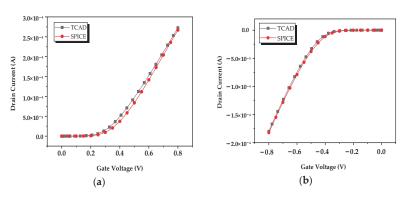

| Zheng Zhang, Gang Guo, Futang Li, Haohan Sun, Qiming Chen, Shuyong Zhao, et al.  Effects of Different Factors on Single Event Effects Introduced by Heavy Ions in SiGe Heterojunction Bipolar Transistor: A TCAD Simulation  Reprinted from: Electronics 2023, 12, 1008, doi:10.3390/electronics12041008 |

| Hongyu Ding, Jiangwei Cui, Qiwen Zheng, Haitao Xu, Ningfei Gao, Mingzhu Xun, et al.  Effect of Trapped Charge Induced by Total Ionizing Dose Radiation on the Top-Gate Carbon Nanotube Field Effect Transistors  Reprinted from: Electronics 2023, 12, 1000, doi:10.3390/electronics12041000             |

|                                                                                                                                                                                                                                                                                                          |

| Xiaoyu Pan, Hongxia Guo, Chao Lu, Hong Zhang and Yinong Liu The Inflection Point of Single Event Transient in SiGe HBT at a Cryogenic Temperature Reprinted from: Electronics 2023, 12, 648, doi:10.3390/electronics12030648                                                                             |

| <b>Jindou Xin, Xiang Zhu, Yingqi Ma and Jianwei Han</b><br>Study of Single Event Latch-Up Hardness for CMOS Devices with a Resistor in Front of DC-DC<br>Converter                                                                                                                                       |

| Reprinted from: <i>Electronics</i> <b>2023</b> , <i>12</i> , 550, doi:10.3390/electronics12030550                                                                                                                                                                                                        |

| Peixiong Zhao, Bo Li, Hainan Liu, Jinhu Yang, Yang Jiao, Qiyu Chen, et al. The Effects of Total Ionizing Dose on the SEU Cross-Section of SOI SRAMs Reprinted from: Electronics 2022, 11, 3188, doi:10.3390/electronics11193188                                                                          |

#### **About the Editors**

#### Yaqing Chi

Yaqing Chi, Ph.D., Associate Researcher, Master's Supervisor in the School of Computer, National University of Defense Technology, director of the Hunan Aerospace Society, and member of the "High Performance Microprocessor Technology" Innovation Team of the Ministry of Education of China. He received the Ph.D. degree in 2009 from the National University of Defense Technology and has worked there since. He leads a team testing radiation effects for advanced integrated circuits, and has conquered many key technologies such as single-event effect characterization and measurement for nano-integrated circuits, radiation-resistance testing, and evaluations of complex microprocessors and so on. He participated in the development and evaluation of many aerospace microprocessors, which have been widely applied in aerospace projects such as satellites, rockets, spacecrafts, space stations, and deep space explorations. His research interest includes the radiation effects in integrated circuits, radiation-hardening techniques for microprocessors based on advanced semiconductor processes, high-speed radiation-tolerant SerDes, and FPGAs. He has won an award of national scientific and technological progress and four awards of the provincial and ministerial levels, obtained more than 20 national invention patent authorizations, and published more than 40 papers in important journals and conferences in the field of integrated circuit radiation effects.

#### Li Cai

Li Cai, Ph.D., Researcher, was selected for the CAS Talent Program Youth Project, Doctor's Supervisor in the Institute of Modern Physics, Chinese Academy of Sciences. After graduating with a Master's degree in 2009, she worked in the Chinese Academy of Atomic Energy (CIAE), and obtained her doctoral degree from the CIAE in 2017. She began to work in the Institute of Modern Physics in 2020. The main research field is the radiation effect of semiconductor devices, especially the experimental technology based on accelerators. Dr. Cai is skillful in broadbeam and microbeam irradiation experiments, has established a sample temperature measurement and control system based on the SEE test terminal, and has evaluated the impact of temperature on SEE in SRAMs and inverter chains. During the work, she has collaborated with several universities and institutes to study the radiation effects on SRAMs, DSPs, FinFET inverter chains, CMOS image sensor, MRAM, etc. She has won the second prize for National Defense Science and Technology Progress and first prize for the China National Nuclear corporation Science and Technology Award, and she has published more than 20 papers as the first or corresponding author in important journals and conferences in the field of radiation effects on semiconductor devices. As the project leader, she has led multiple scientific research projects, such as the National Natural Science Foundation of China, national defense pre-research, talent project, etc.

#### Chang Cai

Chang Cai received his Ph.D. degree from the Institute of Modern Physics, Chinese Academy of Sciences, in 2021. After graduation, he joined Fudan University as a researcher, where he has continued to make significant contributions to the field of radiation effects in integrated circuits. Dr. Cai's research focuses on a wide range of topics within this field, including the radiation mechanisms for bulk, FDSOI, and FinFET devices. He investigates the single-event effects in advanced novel electronic devices, which are critical for understanding and mitigating radiation-induced failures. His work also includes the design of fault-tolerant field-programmable gate arrays (FPGA) and systems on chip (SoC), where he develops strategies to enhance radiation hardness through both layout and logical design. In addition to his theoretical and design work, Dr. Cai is actively involved in practical experiments. He conducts radiation experiments in extreme conditions to test and validate the robustness of various electronic devices. His expertise includes single-event effect characterization and evaluation techniques for VLSI, which are essential for ensuring the reliability of complex integrated circuits in radiation environments. Dr. Cai has published more than 30 peer-reviewed papers as the first or corresponding author in recent five years. His research has been widely recognized and presented at numerous international conferences, including prestigious symposiums such as the IEEE IRPS.

Editorial

#### Radiation Effects of Advanced Electronic Devices and Circuits

Yaqing Chi 1,2, Chang Cai 3,\* and Li Cai 4

- College of Computer, National University of Defense Technology, Changsha 410073, China; yqchi@nudt.edu.cn

- <sup>2</sup> Key Laboratory of Advanced Microprocessor Chips and Systems, National University of Defense Technology, Changsha 410073, China

- State Key Laboratory of ASIC and System, Fudan University, Shanghai 201203, China

- Institute of Modern Physics, Chinese Academy of Sciences, Lanzhou 730000, China; caili@impcas.ac.cn

- \* Correspondence: caichang@fudan.edu.cn

#### 1. Introduction

Research on the effects of radiation on advanced electronic devices and integrated circuits has experienced rapid growth over the last few years, resulting in many approaches being developed for the modeling of radiation's effects and the design of advanced radiation-hardened electronic devices and integrated circuits [1–10]. With the progressive scaling of integrated circuit technologies and the growing complexity of electronic devices, their susceptibility to radiation's effects has presented many exciting challenges that are expected to propel research in the coming decade [11–14]. Additionally, regarding single-event effects (SEEs), continued scaling has drastically introduced new challenges, resulting in multiplecell upsets, multipulse propagations, and other complex effects [15–22]. These issues necessitate the development of new solutions to assess and mitigate radiation sensitivity in advanced devices and integrated circuits.

The first edition of "Radiation Effects of Advanced Electronic Devices and Circuits" features nineteen high-quality submissions that showcase emerging applications and address recent breakthroughs. One key focus is the exploration of materials and device architectures designed to enhance radiation tolerance. This Special Issue also studies the development of advanced simulation tools and modeling techniques for accurately predicting the behavior of electronic devices exposed to radiation. These efforts encompass the refinement of existing simulation methodologies and the development of new computational approaches to better capture the complex interactions between radiation particles and basic materials. Additionally, this Special Issue addresses the growing importance of testing and validation methodologies for assessing the radiation hardness of integrated circuits and electronic systems. Researchers are exploring innovative testing protocols to ensure the reliability and robustness of electronic components in radiation environments, highlighting recent advancements in the field of radiation-tolerant electronics for space applications. Overall, this Special Issue serves as a comprehensive platform for researchers to showcase their latest findings and advancements in the effects of radiation on advanced electronic devices and circuits. By addressing a wide array of topics spanning from fundamental mechanisms to practical applications, this first Special Issue aims to foster collaboration and innovation within the radiation effects community and to contribute to the ongoing advancement of radiation-hardened electronics technology.

Radiation Effects of Advanced Electronic Devices and Circuits. Electronics 2024, 13, 1073. https:// doi.org/10.3390/electronics13061073

Citation: Chi, Y.; Cai, C.; Cai, L.

Received: 27 February 2024 Accepted: 8 March 2024 Published: 14 March 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 2. Highlighting Key Contributions

The nineteen articles in this Special Issue focus on not only systematic evaluation methods such as technology computer-aided design (TCAD), geometry and tracking (GEANT4), and novel numerical computation techniques but also the basic mechanisms and hardening results regarding the radiation performance of key components or devices such as sensors,

FinFET, silicon-on-insulator (SOI), system-on-chip (SoC), direct current (DC)–DC converters, SiC, heterojunction bipolar transistors (HBTs), and carbon nanotubes (Contribution 1–19).

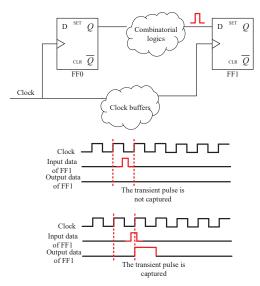

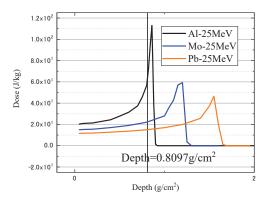

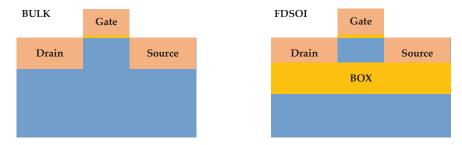

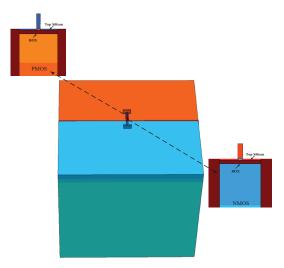

With the development of integrated circuit technology, radiation's effects such as total ionizing dose (TID) effects, the high-dose-rate transient ionizing radiation response, and the single-event upset (SEU) of electron devices under advanced SOI CMOS processes have attracted considerable attention. Three articles provide recent and relevant research on the effects of radiation on SOI technology. The detailed TID effects and SEU features for SOI static random-access memories (SRAMs) with different layout structures were explored by Zhao, P. et al. (Contribution 1). The experimental results indicate that the SEU crosssections are not only influenced by TID irradiation but also closely related to the layout structure of the memory cells. Li, T. et al. (Contribution 13) conducted an experimental and simulation study on the high-dose-rate transient ionizing radiation response and factors influencing fully depleted SOI (FDSOI) D flip-flop (DFF) circuits. The results demonstrate that the number of errors in DFFs nonlinearly increases with increasing dose rate, and the increasing supply voltage leads to an increase in data errors due to increased charge collection efficiency. Lin, L. et al. (Contribution 15) investigated the effect of hot-carrier injection (HCI) on γ-ray-irradiated partially depleted (PD) SOI n-MOSFETs with a T-shaped gate structure. The results indicate that the HCI has a recovery effect on the long-term reliability of n-MOSFETs when applied to a space environment.

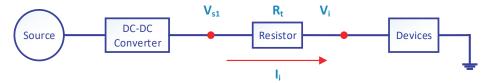

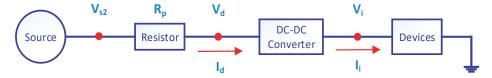

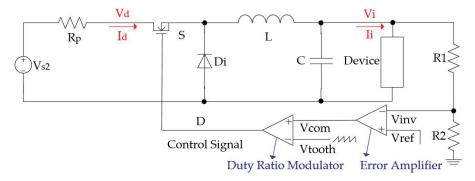

Bulk silicon complementary metal oxide semiconductor (CMOS) devices encounter distinct single event latch-up (SEL) problems in aerospace. The traditional method fails to release devices from the latch-up state due to the narrow resistance range. Therefore, Xin, J. et al. (Contribution 2) developed an improved design for the resistor in front of the DC–DC buck converter, which increases the resistance range according to the input characteristics of the DC–DC buck converter. The method enhances the latch-up hardness performance by expanding the resistance range in comparison with that of the conventional design.

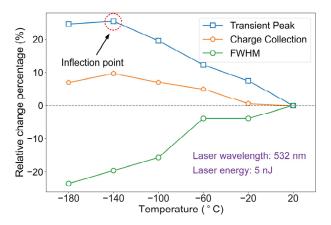

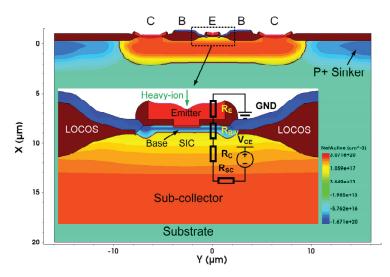

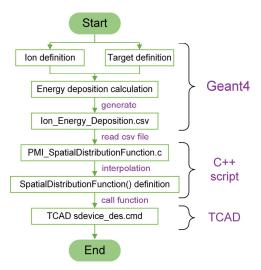

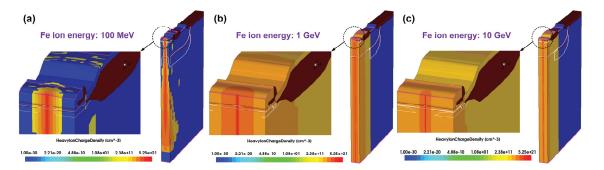

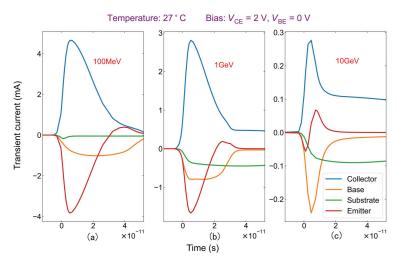

Some studies focused on the basic radiation effects of transistors or diodes have been published in our Special Issue. Pan, X. et al. (Contribution 3) investigated the inflection point of a single-event transient in a SiGe HBT. The collector's transient inflection point is jointly determined by the transient current of the emitter, substrate, and base, and the characteristics of the transient peaks widely vary among electrodes. Additionally, the contributors proposed a method to introduce the initial ionized EHPs' distribution of the Geant4 simulation to a TCAD simulation, thereby increasing the simulation accuracy and efficiency of the heavy-ion-induced SEE. To understand the microphysical mechanism of SEEs in SiGe HBTs, the effects of the heavy-ion striking location, incident angle, LET value, projected range, ambient temperature, and bias state were investigated by Zhang, Z. et al. (Contribution 5). The results indicate that the current transient peak value increases with the LET and the projected range of the heavy ions and decreases with the ambient temperature. The SEEs of SiGe HBTs are influenced not only by heavy-ion irradiation parameters such as the incident angle, LET value, and projected range but also by the striking location, ambient temperature, and bias state. In addition, the effects of proton irradiation on CMOS singlephoton avalanche diodes with and without shallow trench isolation were examined by Xun, M. et al. (Contribution 19). The I–V characteristics, dark count rate, and photon detection probability of the diodes were measured under proton irradiation, contributing to meeting the dramatically increasing demands for satellite-to-ground quantum communication and space environment detection. Furthermore, semiconductor devices have entered the post-Moore era, where new materials and new technology have emerged. The excellent performance and radiation-hardness potential of carbon nanotube field-effect transistors (CNTFETs) have widely attracted attention. Ding, H. et al. (Contribution 4) investigated the TID effect of top-gate structure CNTFETs and the influence of the substrate on topgate during irradiation. Studies regarding the influence mechanism of trapped charge introduced by TID irradiation on the characteristics of the top-gate CNTFETs are urgently needed for the design of CNT-based devices.

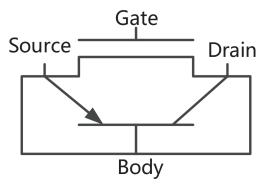

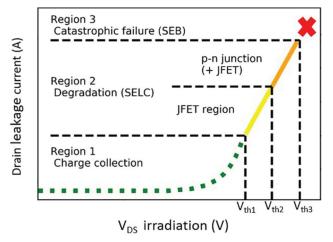

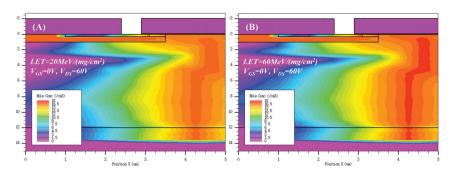

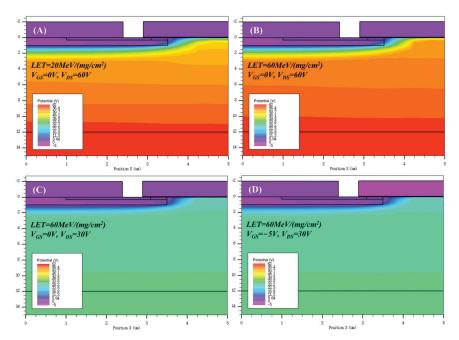

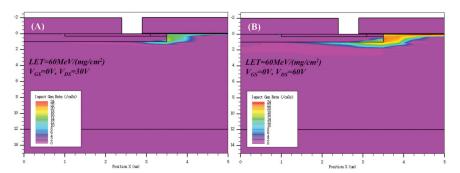

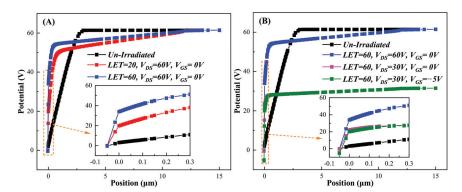

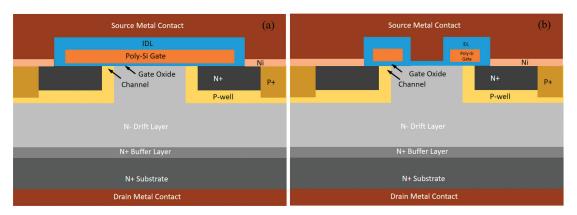

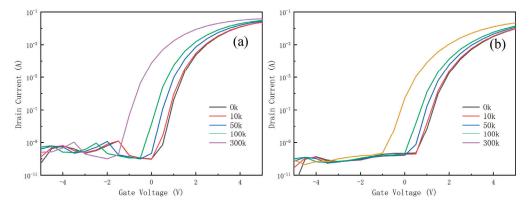

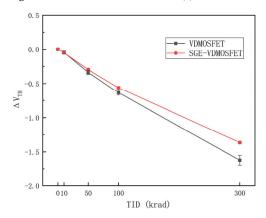

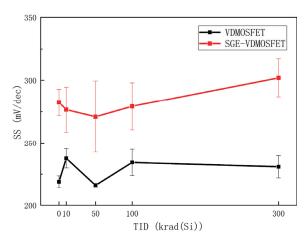

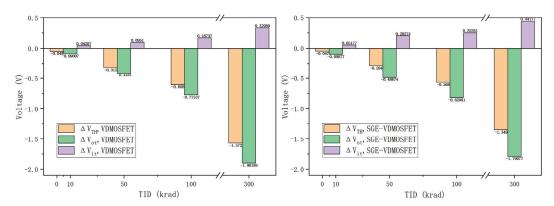

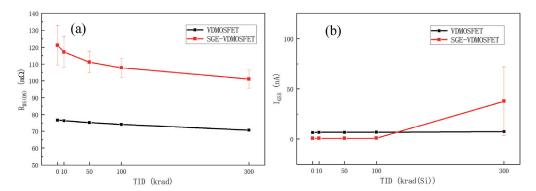

SiC power devices require resistance to both SEEs and TIDs in a space radiation environment, and several articles in our Special Issue present detailed results on simulation or irradiation experiments. Li, X. et al. (Contribution 6) investigated the impact mechanism and regularity of using the split-gate-enhanced process to determine the radiation resistance and long-term reliability of SiC vertically diffused MOS (VDMOS). The split-gate-enhanced VDMOSFET process can effectively enhance the radiation resistance of SiC VDMOS but impacts on the gate oxide reliability of SiC VDMOSs. Feng, H. et al. (Contribution 9) investigated the impact mechanism and regularity of using the SGE process to determine reliability of SiC VDMOS under radiation conditions. The use of the new process leads to more defects in the oxide layer, reducing the long-term reliability of the device, but its stability recovers after accelerated high-temperature annealing. Liang, X. et al. (Contribution 12) experimentally studied heavy-ion irradiation with different particle LETs, gate biases, and drain biases. The experimental results, along with those of TCAD simulations, suggest that the latent damage induced by irradiation in gate oxide is closely related to the peak electric field in the gate oxide at the time of particle incidence. The peak electric field, determined via the potential difference between the two sides of the gate oxide, is affected by the particle LETs, gate biases, and drain biases together. The leakage current is the most critical parameter for characterizing heavy-ion radiation damage in SiC MOSFETs. Moreover, an accurate and refined analysis of the source and generation process of leakage current is the key to revealing the failure mechanism. Xiang, Y. et al. (Contribution 16) finely tested the online and postirradiation leakage changes in and leakage pathways of SiC MOSFETs caused by heavy-ion irradiation, reverse-analyzed the damaged location of the device, and discussed the mechanism of leakage generation. The experimental results further confirm that an increase in the leakage current of a device during heavy-ion irradiation is positively correlated with the applied voltage of the drain, but the leakage path is indirect from the drain to the source. This study provides a theoretical basis for the radiation resistance reinforcement of SiC power devices.

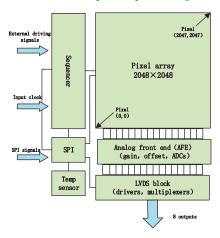

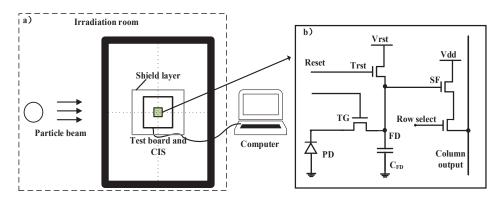

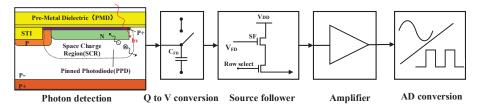

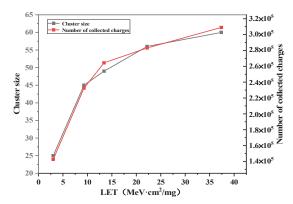

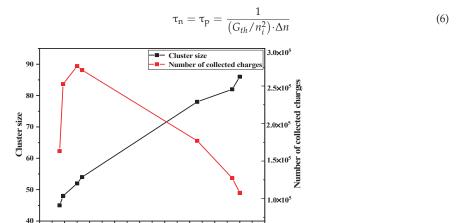

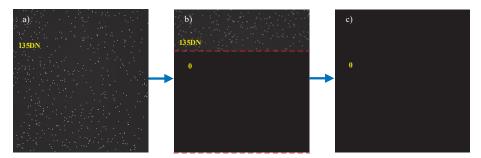

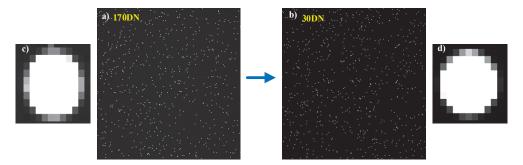

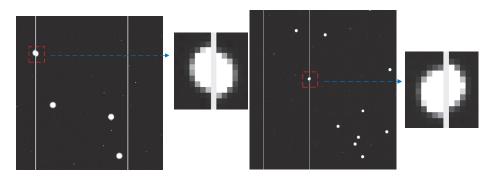

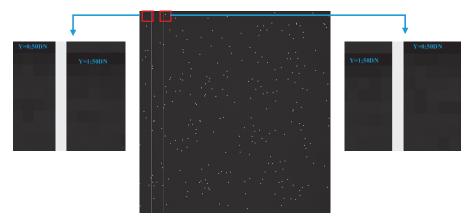

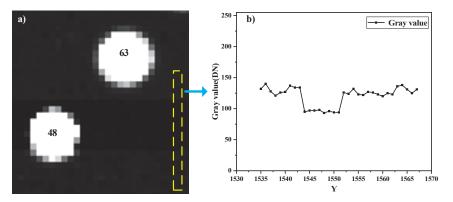

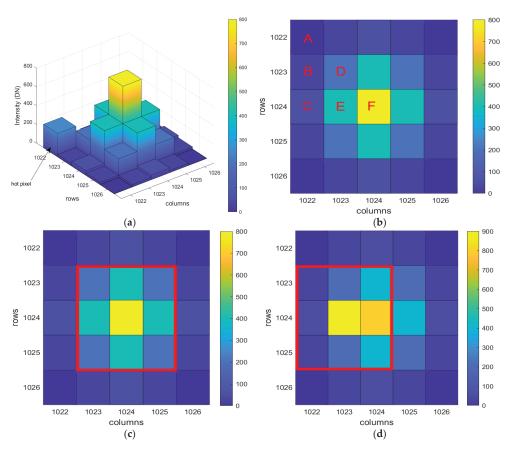

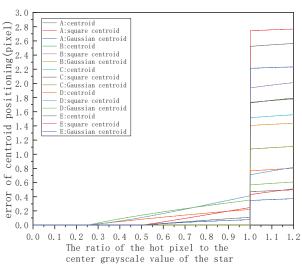

Star sensors are widely used on satellites owing to their precise pointing accuracy. However, space radiation environments ill cause cumulative effects and single-event transients (SETs) in the imaging systems of star sensors, which can affect their star map recognition success rate. In this Special Issue, three articles illustrate the radiation effects on sensors. Cui, Y. et al. (Contribution 7) individually analyzed the influence of the decrease in the number of stars to be identified caused by proton irradiation, hot pixels, and SET spots on the success rate of different star map recognition algorithms. The findings of this study provide theoretical and technical bases for the improvement in star map recognition algorithms for long-term on-orbit star sensors. In addition, Feng, J. et al. (Contribution 10) conducted gamma-ray TID radiation experiments on CMOS image sensors and camera systems, and they thoroughly analyzed the impact mechanisms of dark current, full well capacity, and quantum efficiency of CMOS image sensors on camera resolution. Yang, Z. et al. (Contribution 11) investigated the relationship between the variation in SET bright spots under different conditions by conducting heavy-ion irradiation of image sensors. The authors propose identifying and classifying SEUs using the characteristics of set bright spo.t They established a fast identification method to analyze SEU patterns and sensitive areas based on transient bright spot size, background gray value, and other parameters. These studies provide theoretical bases for the evaluation of the radiation resistance of sensors in radiation environments and the development of radiation-resistant cameras.

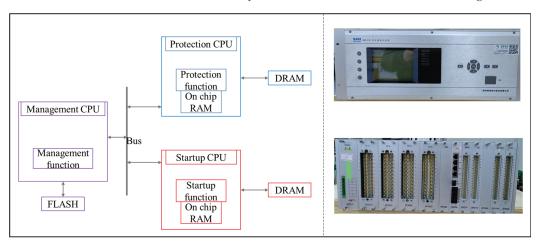

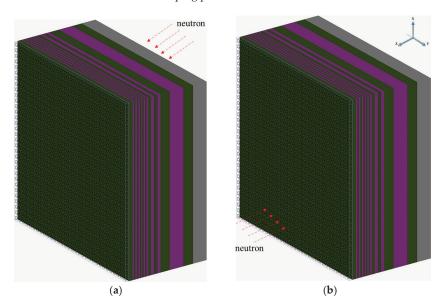

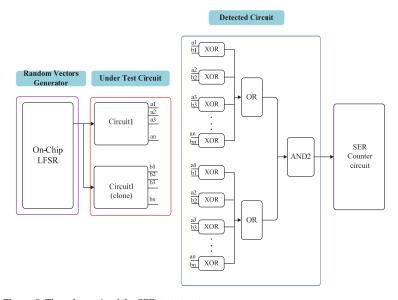

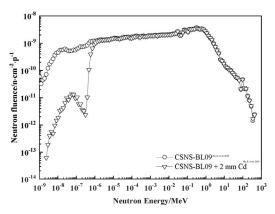

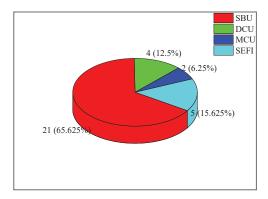

The reliability of nanoscale electronic systems is crucial in various applications. Current research has confirmed that atmospheric neutrons can induce single-event effects in advanced relay protection devices as well. Yang, W. et al. (Contribution 8) investigated a Xilinx Zynq-7000 SoC manufactured with 28 nm CMOS technology using two rounds of spallation neutron irradiation. They conducted spallation neutron irradiation and analyzed the results in combination with those of Monte Carlo simulation to explore the impact of atmospheric neutrons on the SEEs of the target system-on-chip. Zhou, H. et al. (Contribution 18) preliminary assessed the SEEs on relay protection devices using neutron-based analysis

and provide valuable insights for evaluating the reliability of advanced technology relay protection devices.

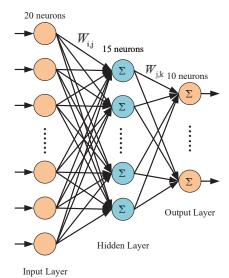

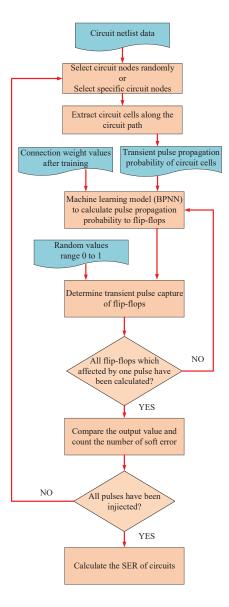

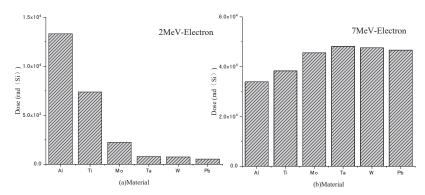

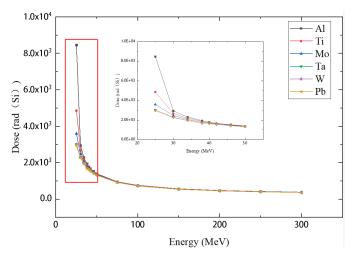

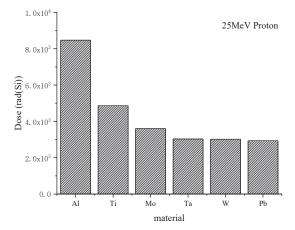

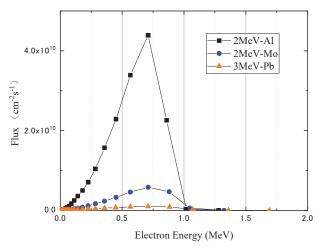

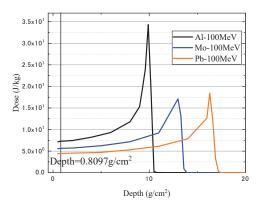

Several novel evaluation methods for radiation effects have been developed. Based on the illustrations of Liu, M. et al. (Contribution 14), depending on the particle energy, the areal density aluminum equivalent method may over- or underestimate the absorbed dose in a shielded silicon detector, especially for the ionization total-dose shielding effect of low-energy electrons. For integrated circuits used in space applications, the soft errors caused by transient pulses must first be evaluated, and the conventional evaluation approaches are limited to the circuit scale. Additionally, Song, R. et al. (Contribution 17) developed an approach for evaluating the soft error rate using machine learning technology. A back propagation neural network is implemented in the proposed approach. The proposed approach helps with determining the probability of transient pulse propagation. Compared with the conventional soft-error-rate evaluation results, the proposed approach strong correlations in both trend and magnitude.

#### 3. The Future

The space radiation environment strongly impacts electronic devices, thereby seriously affecting the service life of spacecraft on-orbit electronic equipment. Consequently, the need is critical to thoroughly investigate the basis of radiation effects and develop innovative strategies to enhance the radiation resistance of electronic devices. The diverse array of articles featured in this Special Issue underscore the breadth of research in the field of the effects of radiation on advanced electronic devices and circuits. These articles span from cutting-edge advancements in nuclear and solid-state physics to sophisticated device and circuit-level modeling techniques as well as innovative hardening design methodologies. Moreover, these researchers have explored the application of progressive algorithms and deep learning methodologies to optimize system performance across various radiation environments. Together, these articles represent a collective leap forward in the pursuit of understanding radiation's effects and devising efficient methods for assessing the reliability and responses of novel electronic devices under radiation conditions.

In addition to the aforementioned areas of focus, the second edition of "Radiation Effects of Advanced Electronic Devices and Circuits" will delve deeper into several key aspects of radiation effects on electronic systems. This includes exploring the impact of radiation on emerging technologies such as quantum computing, neuromorphic computing, photonic devices, etc. The second edition will feature research on the development of radiation-hardened sensors and actuators, as well as advances in fault-tolerant computing architectures designed to mitigate the effects of radiation-induced errors. Moreover, given the push toward miniaturization and the complexity of electronic systems, the second edition will highlight research on radiation's effects at the nanoscale level. This will encompass investigations into the susceptibility of advanced electronic devices, such as carbon nanotubes, graphene-based transistors, and nanostructured materials, to radiation-induced degradation and failure mechanisms. Furthermore, the second edition will address the growing importance of system-level approaches to radiation hardening, including the integration of redundant components, fault-tolerant algorithms, and adaptive error correction techniques. Additionally, the next Special Issue will include articles exploring the role of machine learning and artificial intelligence in enhancing the resilience of electronic systems to radiation's effects, particularly in autonomous spacecraft, low-orbit commercial satellites, and space station systems. Overall, the second edition aims to provide a comprehensive overview of the latest advancements in radiation effects research and their implications for the design and operation of advanced electronic devices and circuits in space applications. These insights are expected to drive innovation and development in the field, paving the way for the creation of more robust and reliable electronic systems for future space missions.

**Author Contributions:** Y.C., C.C. and L.C. worked together in the whole editorial process of the Special Issue, "Radiation Effects of Advanced Electronic Devices and Circuits". Y.C., C.C. and L.C. worked closely together in the overall editorial activities towards the completion of the Special

Issue. Y.C. and C.C. drafted this manuscript. Y.C., C.C. and L.C. reviewed, edited, and finalized the manuscript. All authors have read and agreed to the published version of the manuscript.

**Funding:** This study was jointly supported by National Natural Science Foundation of China (grant No. 62174180 and No. 12205052), CAS Talent Program Youth Project (grant No. E129193YR0), and the fund of Innovation Center for Radiation Application (grant No. KFZC2022020301).

Conflicts of Interest: The authors declares no conflicts of interest.

#### List of Contributions

- Zhao, P.; Liu, B.; Liu, H.; Yang, J.; Jiao, Y.; Chen, Q.; Sun, Y.; Liu, J. The Effects of Total Ionizing Dose on the SEU Cross-Section of SOI SRAMs. *Electronics* 2022, 11, 3188.

- Xin, J.; Zhu, X.; Ma, Y.; Han, J. Study of Single Event Latch-Up Hardness for CMOS Devices with a Resistor in Front of DC-DC Converter. *Electronics* 2023, 12, 550.

- 3. Pan, X.; Guo, H.; Lu, C.; Zhang, H.; Liu, Y. The Inflection Point of Single Event Transient in SiGe HBT at a Cryogenic Temperature. *Electronics* **2023**, *12*, 648.

- 4. Ding, H.; Cui, J.; Zheng, Q.; Xu, H.; Gao, N.; Xun, M.; Yu, G.; He, C.; Li, Y.; Guo, Q. Effect of Trapped Charge Induced by Total Ionizing Dose Radiation on the Top-Gate Carbon Nanotube Field Effect Transistors. *Electronics* **2023**, *12*, 1000.

- Zhang, Z.; Guo, G.; Li, F.; Sun, H.; Chen, Q.; Zhao, S.; Liu, J.; Ouyang, X. Effects of Different Factors on Single Event Effects Introduced by Heavy Ions in SiGe Heterojunction Bipolar Transistor: A TCAD Simulation. *Electronics* 2023, 12, 1008.

- 6. Li, X.; Cui, J.; Zheng, Q.; Li, P.; Cui, X.; Li, Y.; Guo, Q. Study of the Within-Batch TID Response Variability on Silicon-Based VDMOS Devices. *Electronics* **2023**, *12*, 1403.

- 7. Cui, Y.; Feng, J.; Li, Y.; Wen, L.; Guo, Q. Proton Radiation Effects of CMOS Image Sensors on Different Star Map Recognition Algorithms for Star Sensors. *Electronics* **2023**, *12*, 1629.

- 8. Yang, W.; Li, Y.; Li, Y.; Hu, Z.; Cai, J.; He, C.; Wang, B.; Wu, L. Neutron Irradiation Testing and Monte Carlo Simulation of a Xilinx Zynq-7000 System on Chip. *Electronics* **2023**, *12*, 2057.

- Feng, H.; Liang, X.; Pu, X.; Xiang, Y.; Zhang, T.; Wei, Y.; Feng, J.; Sun, J.; Zhang, D.; Li, Y.; et al. Total Ionizing Dose Effects of 60Co -Ray Radiation on Split-Gate SiC MOSFETs. Electronics 2023, 12, 2398.

- Feng, J.; Wang, H.; Li, Y.; Wen, L.; Guo, Q. Mechanism of Total Ionizing Dose Effects of CMOS Image Sensors on Camera Resolution. *Electronics* 2023, 12, 2667.

- 11. Yang, Z.; Wen, L.; Li, Y.; Feng, J.; Zhou, D.; Liu, B.; Zhao, Z.; Guo, Q. Heavy Ion Single Event Effects in CMOS Image Sensors: SET and SEU. *Electronics* **2023**, *12*, 2833.

- Liang, X.; Feng, H.; Xiang, Y.; Sun, J.; Wei, Y.; Zhang, D.; Li, Y.; Feng, J.; Yu, X.; Guo, Q. Oxide Electric Field-Induced Degradation of SiC MOSFET for Heavy-Ion Irradiation. Electronics 2023, 12, 2886.

- 13. Li, T.; Yuan, J.; Bai, Y.; Yu, C.; Gou, C.; Shu, L.; Wang, L.; Zhao, Y. Research on High-Dose-Rate Transient Ionizing Radiation Effect in Nano-Scale FDSOI Flip-Flops. *Electronics* **2023**, *12*, 3149.

- Liu, M.; He, C.; Feng, J.; Xun, M.; Sun, J.; Li, Y.; Guo, Q. Analysis of Difference in Areal Density Aluminum Equivalent Method in Ionizing Total Dose Shielding Analysis of Semiconductor Devices. *Electronics* 2023, 12, 4181.

- 15. Lin, L.; Cong, Z.; Jia, C. Recovery Effect of Hot-Carrier Stress on -ray-Irradiated 0.13 um Partially Depleted SOI n-MOSFETs. *Electronics* **2023**, *12*, 4233.

- Xiang, Y.; Liang, X.; Feng, J.; Feng, H.; Zhang, D.; Wei, Y.; Yu, X.; Guo, Q. Refined Analysis of Leakage Current in SiC Power Metal Oxide Semiconductor Field Effect Transistors after Heavy Ion Irradiation. *Electronics* 2023, 12, 4349.

- Song, R.; Shao, J.; Chi, Y.; Liang, B.; Chen, J.; Wu, Z. Machine Learning-Based Soft-Error-Rate Evaluation for Large-Scale Integrated Circuits. *Electronics* 2023, 12, 4978.

- 18. Zhou, H.; Yu, H.; Zou, Z.; Su, Z.; Zhao, Q.; Yang, W.; He, C. Evaluation of Single Event Upset on a Relay Protection Device. *Electronics* **2024**, *13*, 64.

19. Xun, M.; Li, Y.; Feng, J.; He, C.; Liu, M.; Guo, Q. Effect of Proton Irradiation on Complementary Metal Oxide Semiconductor (CMOS) Single-Photon Avalanche Diodes. *Electronics* **2024**, *13*, 224.

#### References

- 1. Allison, J.; Amako, K.; Apostolakis, J.; Araujo, H.A.A.H.; Dubois, P.A.; Asai, M.A.A.M.; Barrand, G.; Capra, R.; Chauvie, S.; Chytracek, R.; et al. Geant4 developments and applications. *IEEE Trans. Nucl. Sci.* 2006, 53, 270–278. [CrossRef]

- 2. Weller, R.A.; Mendenhall, M.H.; Reed, R.A.; Schrimpf, R.D.; Warren, K.M.; Sierawski, B.D.; Massengill, L.W. Monte Carlo simulation of single event effects. *IEEE Trans. Nucl. Sci.* 2010, 57, 1726–1746. [CrossRef]

- 3. Reed, R.A.; Weller, R.A.; Mendenhall, M.H.; Fleetwood, D.M.; Warren, K.M.; Sierawski, B.D.; King, M.P.; Schrimpf, R.D.; Auden, E.C. Physical processes and applications of the Monte Carlo radiative energy deposition (MRED) code. *IEEE Trans. Nucl. Sci.* 2015, 62, 1441–1461. [CrossRef]

- Munteanu, D.; Autran, J.L. Modeling and simulation of singleevent effects in digital devices and ICs. IEEE Trans. Nucl. Sci. 2008, 55, 1854–1878. [CrossRef]

- Artola, L.; Gaillardin, M.; Hubert, G.; Raine, M.; Paillet, P. Modeling single event transients in advanced devices and ICs. IEEE Trans. Nucl. Sci. 2015, 62, 1528–1539. [CrossRef]

- 6. Hughes, H.L.; Benedetto, J.M. Radiation effects and hardening of MOS technology: Devices and circuits. *IEEE Trans. Nucl. Sci.* **2003**, *50*, 500–521. [CrossRef]

- 7. Lacoe, R.C. Improving integrated circuit performance through the application of hardness-by-design methodology. *IEEE Trans. Nucl. Sci.* **2008**, *55*, 1903–1925. [CrossRef]

- Lacoe, R.C.; Osborn, J.V.; Koga, R.; Brown, S.; Mayer, D. Application of hardness-by-design methodology to radiation-tolerant ASIC technologies. *IEEE Trans. Nucl. Sci.* 2000, 47, 2334–2341. [CrossRef]

Leray, J.L.; Dupont-Nivet, E.; Pere, J.F.; Coïc, Y.M.; Raffaelli, M.; Auberton-Hervé, A.J.; Bruel, M.; Giffard, B.; Margail, J. CMOS/SOI

- 9. Leray, J.L.; Dupont-Nivet, E.; Pere, J.F.; Coic, Y.M.; Kaffaelli, M.; Auberton-Herve, A.J.; Bruel, M.; Giffard, B.; Margail, J. CMOS/SOI hardening at 100 Mrad(SiO<sub>2</sub>). *IEEE Trans. Nucl. Sci.* **1990**, *37*, 2013–2019. [CrossRef]

- 10. Wang, H.; Dai, X.; Ibrahim, Y.M.Y.; Sun, H.; Nofal, I.; Cai, L.; Guo, G.; Shen, Z.; Chen, L. A Layout-Based Rad-Hard DICE Flip-Flop Design. J. Electron. Test. 2019, 35, 111–117. [CrossRef]

- 11. Fleetwood, D.M. Radiation effects in a post-Moore world. IEEE Trans. Nucl. Sci. 2021, 68, 509–545. [CrossRef]

- 12. Gaspard, N.J.; Jagannathan, S.; Diggins, Z.J.; King, M.P.; Wen, S.-J.; Wong, R.; Loveless, T.D.; Lilja, K.; Bounasser, M.; Reece, T.; et al. Technology Scaling Comparison of Flip-Flop Heavy-Ion Single-Event Upset Cross Sections. *IEEE Trans. Nucl. Sci.* 2013, 60, 4368–4373. [CrossRef]

- 13. Fleetwood, Z.E.; Lourenco, N.E.; Ildefonso, A.; Warner, J.H.; Wachter, M.T.; Hales, J.M.; Tzintzarov, G.N.; Roche, N.J.-H.; Khachatrian, A.; Buchner, S.P.; et al. Using TCAD modeling to compare heavy-ion and laser induced single event transients in SiGe HBTs. *IEEE Trans. Nucl. Sci.* 2017, 64, 398–405. [CrossRef]

- 14. Chatterjee, I.; Narasimham, B.; Mahatme, N.N.; Bhuva, B.L.; Reed, R.A.; Schrimpf, R.D.; Wang, J.K.; Vedula, N.; Bartz, B.; Monzel, C. Impact of technology scaling on SRAM soft error rates. *IEEE Trans. Nucl. Sci.* 2014, 61, 3512–3518. [CrossRef]

- 15. Sheshadri, V.B.; Bhuva, B.L.; Reed, R.A.; Weller, R.A.; Mendenhall, M.H.; Schrimpf, R.D.; Warren, K.M.; Sierawski, B.D.; Wen, S.-J.; Wong, R. Effects of multi-node charge collection in flip-flop designs at advanced technology nodes. In Proceedings of the 2010 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 2–6 May 2010; pp. 1026–1030.

- 16. Vogl, T.; Sripathy, K.; Sharma, A.; Reddy, P.; Sullivan, J.; Machacek, J.R.; Zhang, L.; Karouta, F.; Buchler, B.C.; Doherty, M.W.; et al. Radiation tolerance of two-dimensional material-based devices for space applications. *Nature* 2019, 10, 1202. [CrossRef] [PubMed]

- 17. Wang, P.; Kalita, H.; Krishnaprasad, A.; Dev, D.; O'Hara, A.; Jiang, R.; Zhang, E.; Fleetwood, D.M.; Schrimpf, R.D.; Pantelides, S.T.; et al. Total-ionizing-dose response of MoS<sub>2</sub> transistors with ZrO<sub>2</sub> and h-BN gate dielectrics. *IEEE Trans. Nucl. Sci.* 2019, 66, 1584–1591. [CrossRef]

- 18. Gao, S.; Li, X.; Zhao, S.; He, Z.; Ye, B.; Cai, L.; Sun, Y.; Xiao, G.; Cai, C.; Liu, J. Heavy Ion Induced MCUs in 28 nm SRAM-based FPGAs: Upset Proportions, Classifications, and Pattern Shapes. *Nucl. Sci. Tech.* 2022, 33, 10. [CrossRef]

- 19. Chi, Y.; Huang, P.; Sun, Q.; Liang, B.; Zhao, Z. Characterization of Single-Event Upsets Induced by High-LET Heavy Ions in 16-nm Bulk FinFET SRAMs. *IEEE Trans. Nucl. Sci.* **2022**, *69*, 1176–1181.

- 20. Chi, Y.; Wu, Z.; Huang, P.; Sun, Q.; Liang, B.; Zhao, Z. Characterization of single-event transients induced by high LET heavy ions in 16 nm bulk FinFET inverter chains. *Microelectron. Reliab.* **2022**, *130*, 114490. [CrossRef]

- 21. Dodds, N.A.; Martinez, M.J.; Dodd, P.E.; Shaneyfelt, M.R.; Sexton, F.W.; Black, J.D.; Lee, D.S.; Swanson, S.E.; Bhuva, B.L.; Warren, K.M.; et al. The contribution of low-energy protons to the total on-orbit SEU rate. *IEEE Trans. Nucl. Sci.* 2015, 62, 2440–2451. [CrossRef]

- 22. Sierawski, B.D.; Mendenhall, M.H.; Reed, R.A.; Clemens, M.A.; Weller, R.A.; Schrimpf, R.D.; Blackmore, E.W.; Trinczek, M.; Hitti, B.; Pellish, J.A.; et al. Muon-induced single event upsets in deep-submicron technology. *IEEE Trans. Nucl. Sci.* 2010, 57, 3273–3278. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

MDPI

Article

## Effect of Proton Irradiation on Complementary Metal Oxide Semiconductor (CMOS) Single-Photon Avalanche Diodes

Mingzhu Xun 1,2,3, Yudong Li 1,2,\*, Jie Feng 1,2, Chengfa He 1,2, Mingyu Liu 1,2,3 and Qi Guo 1,2

- 1 Xinjiang Technical Institute of Physics and Chemistry, Chinese Academy of Sciences, Urumqi 830011, China; xunmz@ms.xjb.ac.cn (M.X.); fengjie@ms.xjb.ac.cn (J.F.); hecf@ms.xjb.ac.cn (C.H.); liumingyu21@mails.ucas.ac.cn (M.L.); guoqi@ms.xjb.ac.cn (Q.G.)

- <sup>2</sup> Xinjiang Key Laboratory of Electronic Information Material and Device, Urumqi 830011, China

- University of Chinese Academy of Sciences, Beijing 100049, China

- \* Correspondence: lydong@ms.xjb.ac.cn

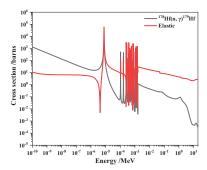

Abstract: The effects of proton irradiation on CMOS Single-Photon Avalanche Diodes (SPADs) are investigated in this article. The I–V characteristics, dark count rate (DCR), and photon detection probability (PDP) of the CMOS SPADs were measured under 30 MeV and 52 MeV proton irradiations. Two types of SPAD, with and without shallow trench isolation (STI), were designed. According to the experimental results, the leakage current, breakdown voltage, and PDP did not change after irradiation at a DDD of  $2.82 \times 10^8$  MeV/g, but the DCR increased significantly at five different higher voltages. The DCR increased by 506 cps at an excess voltage of 2 V and 10,846 cps at 10 V after 30 MeV proton irradiation. A  $\gamma$  irradiation was conducted with a TID of 10 krad (Si). The DCR after the  $\gamma$  irradiation increased from 256 cps to 336 cps at an excess voltage of 10 V. The comparison of the DCR after proton and  $\gamma$ -ray irradiation with two structures of SPAD indicates that the major increase in the DCR was due to the depletion region defects caused by proton displacement damage rather than the Si-SiO<sub>2</sub> interface trap generated by ionization.

Keywords: CMOS SPAD; proton radiation; DCR; displacement damage

Citation: Xun, M.; Li, Y.; Feng, J.; He, C.; Liu, M.; Guo, Q. Effect of Proton Irradiation on Complementary Metal Oxide Semiconductor (CMOS)

Single-Photon Avalanche Diodes.

Electronics 2024, 13, 224. https://doi.org/10.3390/electronics13010224

Academic Editor: Domenico Caputo

Received: 25 November 2023 Revised: 29 December 2023 Accepted: 2 January 2024 Published: 4 January 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

A Single-Photon Avalanche Diode (SPAD) is a photodiode that operates in Geiger mode with a reverse bias voltage higher than its avalanche breakdown voltage, and it utilizes an avalanche process to achieve single-photon detection capability. When photons are absorbed in the multiplication region of SPADs, a self-sustaining avalanche may be generated, and the current increases rapidly in the realm of picoseconds. By measuring the detectable current during the avalanche process, the arrival time of photons can be recorded [1]. An external quenching circuit is used to restore a SPAD to its initial state while waiting for the next photon to enter the multiplication region. By repeating the process above, single-photon detection and counting can be achieved. It can be seen that there is a dead time after the avalanche process, which may limit the maximum counting rate of the detected photons.

Due to their performance of high sensitivity, high detection efficiency, reliability, and low jitter noise, SPADs are widely used in some applications that require a low dark count rate (DCR), a low breakdown voltage, a low leakage current, a high gain, and high photon detection efficiency. SPADs are used in various fields, such as light detection and ranging (LiDAR), Non-Line of Sight (NLOS) imaging, fluorescence spectroscopy analysis, astronomic observations, optical communication, and quantum key distribution in weak light detection. When non-visible light must be used, especially in the near-infrared spectrum, high efficiency is very important [2].

At present, many research institutions and companies are developing SPADs with high efficiency, low noise, and high gain for different application scenarios, such as visible and infrared light. In 2019, NASA reported an avalanche photodiode (APD) focal plane array assembled with linear-mode photon-counting capability for space lidar applications. The APD array uses a high-density, vertically integrated photodiode frame structure, and a preamplifier in the ROIC is directly integrated under the APD array to reduce the transmission capacitance. A microlens array is used to improve the fill factor. Its spectral response ranges from 0.9- to 4.3-µm wavelengths, its photon detection efficiency is as high as 70%, and it has a dark count rate of <250 kHz at 110 K [3]. In 2022, silicon photomultipliers (SiPMs), which are SPAD arrays based on a standard 55 nm Bipolar-CMOS-DMOS (BCD) technology, were developed by the Ecole Polytechnique Federale de Lausanne (EPFL). SiPMs are integrated into a coaxial light detection and ranging (LiDAR) system with a time-correlated single-photon counting (TCSPC) module system. Each SPAD cell is passively quenched by a monolithically integrated 3.3 V-thick oxide transistor. The measured gain is  $3.4 \times 10^5$  at a 5 V excess bias voltage. The single-photon timing resolution (SPTR) is 185 ps, and the multiple-photon timing resolution (MPTR) is 120 ps at a 3.3 V excess bias voltage. Under the condition of a 25 m distance, the accuracies of SPTR and MPTR are 2 cm and 2 mm [4]. In 2022, a best-performing CMOS SPAD with a peak photon detection probability (PDP) of 55% at 480 nm, spanning from the near ultraviolet (NUV) to near infrared (NIR) spectrum, and a normalized dark count rate (DCR) of 0.2 cps/µm<sup>2</sup> at an excess bias of 6 V was proposed. Its after-pulsing probability is about 0.1% at a dead time of ~3 ns, and its single-photon time resolution (SPTR) is 12.1 ps (FWHM) at a 6 V excess bias voltage with a diameter of 25 μm. SPADs operate over a wide range of temperatures, from -65 °C to 40 °C, reaching a normalized DCR of 1.6 mcps/ $\mu m^2$  at a 6 V excess bias voltage and -65 °C [5]. Some big companies, such as STMicroelectronics, Sony, and HAMAMATSU, have also developed a series of SPADs for different applications.

In the field of radiation detection, SPAD arrays combined with different types of scintillators, which can absorb energy from radiation, are mainly used in high-sensitivity gamma-ray detectors and medical PET imaging [6–9]. Scintillator detectors are used for real-time radiation dose rate detection above the environmental background. PET imaging uses radioactive isotope tracing methods to display its location and concentration. By detecting the gamma photons generated by an isotope, the emission position of the photons can be reconstructed, and changes in metabolic processes and other physiological activities can be visualized. In addition, a single SPAD can be used to detect low-energy electrons and X-rays. A SPAD collects electrons generated by incident electrons and X-rays in the multiplication region instead of the photons emitted by scintillators. This makes detection faster and more accurate.

With the dramatic increase in interest in satellite-to-ground quantum communication and space environment detection, SPADs, with the advantages of high efficiency, low power consumption, easy integration, and anti-magnetic field performance, are more and more widely used in space and high-energy radiation detection [10–13]. But they are inevitably exposed to radiation environments, which can affect the performance of SPADs. Most satellite-to-ground quantum communication satellites are in near-earth orbit at an orbital altitude of 500 km, and the space radiation environment includes electrons and protons in the Van Allen radiation belt and high-energy protons in the South Atlantic Anomaly (SAA) region [14–17]. The space radiation environment during deep space exploration is dominated by high-energy galactic cosmic rays, including most of the particles in the periodic table from Z = 1 to Z = 92, with energies ranging from 1 MeV/n to 1 TeV/n. SiPMs were used in space-borne scintillation detectors for many space missions. For example, they have been used for the gain control system on board the Hard X-ray Modulation Telescope (HXMT), a Chinese X-ray space observatory launched in June 2017 [18]. The experiment GMOD assembled an SiPMs array with a CeBr3 scintillator and an Application-Specific Integrated Circuit (ASIC) to detect cosmic gamma-ray phenomena such as Gamma-Ray Bursts (GRBs) in space carried by the Educational Irish Research Satellite 1 (EIRSAT-1). This is a 2U cube satellite deployed from the International Space Station, and it remained in orbit at an altitude of 405 km and a tilt of 51.6 degrees for a year, which is a safe space

environment to avoid serious damage to SiPMs. SiPMs are also used in the Large Hadron Collider CMS, LHCb, and the proposed International Linear Collider (ILC) at the European Organization for Nuclear Research (CERN), which reaches  $10^{14}$  p/cm<sup>2</sup> [19,20].

In radiation environments, protons, electrons,  $\gamma$  rays, and heavy ions can cause certain parameters, such as the breakdown voltage, leakage current, DCR, gain, and photon detection efficiency, to deteriorate at different levels through the displacement damage dose (DDD) effect and the Total Ionizing Dose (TID) effect [21,22]. This is due to the point defects in silicon and the interface defects at the Si-SiO<sub>2</sub> interface near STI. These defects include the vacancy  $(V_{Si})$ , the substitutional phosphorus  $(P_{Si})$ , the interstitial oxygen (Oi), the double vacancy  $(V_{Si}V_{Si})$ , the A-center  $(V_{Si}O_i)$ , and the E-center  $(P_{Si}V_{Si})$ . They are electrically active and act as efficient generation–recombination centers which cause leakage currents and DCR increases [23–27].

To study the SPAD radiation effect of protons, a SPAD of 180 nm standard CMOS technology with a P-I-N structure and radiation tolerance design is used in this experiment. The sensitivity of ionization radiation damage and displacement radiation damage for SPADs is investigated using  $\gamma$  rays and protons beams. Two types of SPADs, with and without Shallow Trench Isolation (STI), are also designed and compared to study the influence of the Si-SiO<sub>2</sub> interface defects near the STI after radiation. The dark current, breakdown voltage, DCR, and photon detection probability (PDP) of the SPADs before and after irradiation are measured, and the radiation damage mechanism of the CMOS SPAD is analyzed.

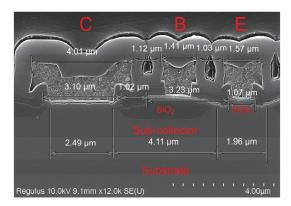

#### 2. Experimental Design

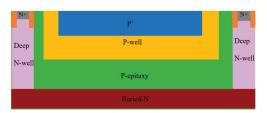

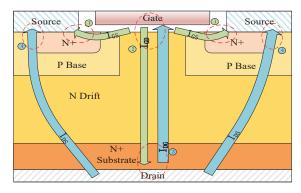

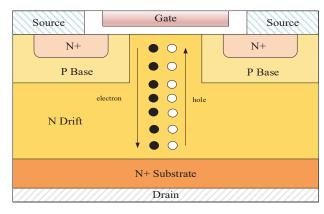

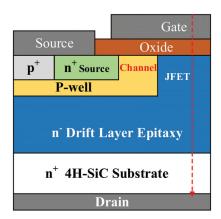

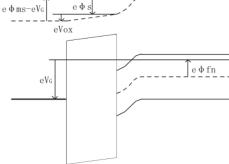

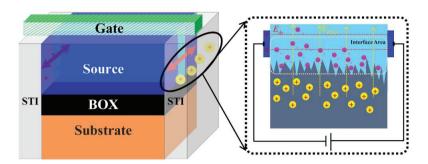

The CMOS SPAD, as shown in Figure 1, is based on the P-I-N structure, with a P-well epitaxial layer and n-type buried channel, and designed by the 180 nm CMOS process. Figure 2 is the cross-section of the SPAD [28,29]. In this design, the n-type buried channel ensures isolation from the substrate, while the deep n-well structure provides contact from N+ to the n-type buried channel. The lateral diffusion and light doping of the P epitaxial layer can avoid premature breakdown at the edge of the junction depletion region. The p+/DNW junction, enabling wider depletion, along with novel guard ring designs, facilitate device operation at up to 10 V of excess bias. The DCR is mainly caused by the tunneling noise at an excess bias of 10 V, but in this design, a P-I-N structure with standard CMOS technology is used to reduce the tunneling noise, resulting in better noise performance. The CMOS SPAD had a photon detection probability (PDP) greater than 40% from 440 to 620 nm, and the dark count rate (DCR) was 12.85 cps/ $\mu$ m<sup>2</sup>. In addition, due to the use of n-type buried channels, the peak electric field of the detector is concentrated between the n-type buried channels and the P epitaxial layer.

Figure 1. SPAD for 180 nm CMOS technology.

Figure 2. Cross-section of the P-I-N-structure SPAD.

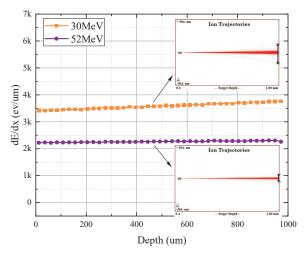

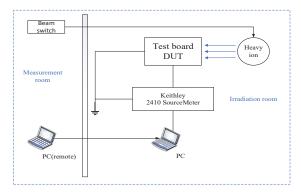

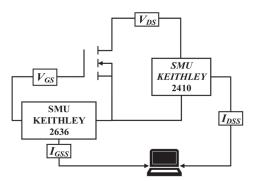

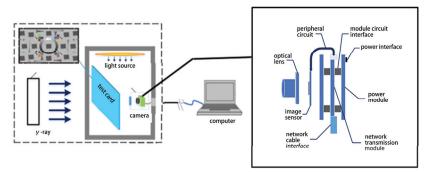

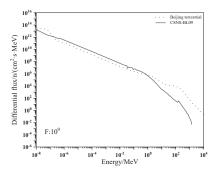

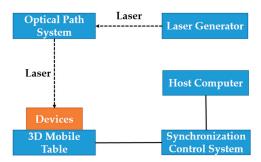

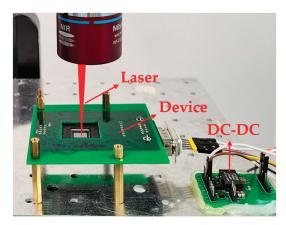

Proton irradiation experiments at two different energies of 30 MeV and 52 MeV were conducted on the Cyclotron Proton Accelerator in the air, and a laser pointing system was used to align it with the beamline center. The proton beam region is 5 cm  $\times$  5 cm, and the uncertainty of the beam intensity had a variation of  $\pm 5\%$ . The proton line energy transport (LET), Nonionizing Energy Loss (NIEL), Total Ionizing Dose (TID), and displacement damage dose (DDD) are shown in Table 1. The LET data come from the NIST stopping power and range tables for the protons program PSTAR, and the NIEL data come from Ref. [30]. The DDD of the SPAD in LEO orbit with an altitude of 400 km and an inclination of  $51.6^{\circ}$  was 19.6 TeV/g with a 2 mm shielding thickness of aluminum [31]. As a contrast, we chose a proton fluence of  $5 \times 10^{10}$  p/cm<sup>2</sup> at energies of 30 MeV and 52 MeV. All the SPAD pins were shorted and connected to ground during the irradiation, and I-V characteristics and PDP measurements were performed before and after irradiation. The parameter testing system for a SPAD includes a Keysight semiconductor parameter analyzer and a DCR and PDP measurement system. The DCR and PDP measurement system consists of a light source, a filter, a spectrograph, an integrating sphere, a sample chamber, and a light source calibration and computer control system, as shown in Figure 3. The halogen lamps can provide a stable light source with a wavelength range of 350 nm-1100 nm. Monochromatic light with specific frequencies can be generated after light passes through the filters and spectrometers. The integrating sphere can reduce small errors caused by an uneven distribution of incident light sources on the detector or beam offset during measurement, thus improving the accuracy of a measurement. The output trigger pulse count of the device is read by an oscilloscope, and then the data are statistically analyzed to obtain the DCR and PDP. A passive quenching circuit with a 50 k $\Omega$  resistor was used to measure the DCR, and the DCR is defined as the average counts of pulses per second (cps) in a 1 min measurement in darkness.

**Figure 3.** The CMOS SPAD parameter testing system with **(a)** oscilloscope for DCR and PDP measurement and **(b)** semiconductor parameter analyzer for I–V characteristics measurement.

Table 1. LET, NIEL, TID, and DDD of 30 MeV and 52 MeV protons.

| Proton Energy | LET                        | NIEL                       | Fluence               | TID    | DDD                |

|---------------|----------------------------|----------------------------|-----------------------|--------|--------------------|

| (MeV)         | (MeV/(g/cm <sup>2</sup> )) | (MeV/(g/cm <sup>2</sup> )) | (p/cm <sup>2</sup> )  | (krad) | (MeV/g)            |

| 30            | $1.47 \times 10$           | $5.63 \times 10^{-3}$      | $5.00 \times 10^{10}$ | 11.8   | $2.82 \times 10^8$ |

| 52            | $9.58 \times 10$           | $3.37 \times 10^{-3}$      | $5.00 \times 10^{10}$ | 7.66   | $1.69 \times 10^8$ |

#### 3. Results

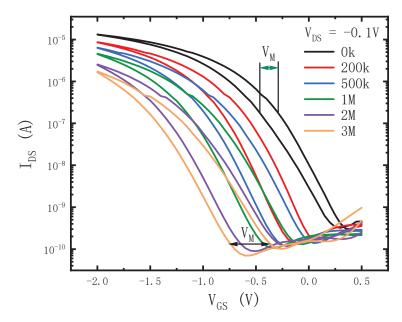

#### 3.1. I-V Characteristics

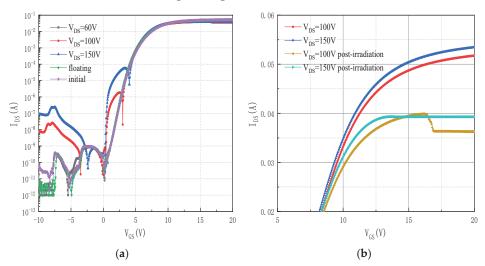

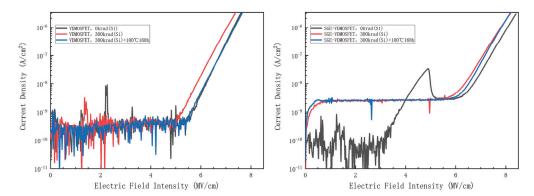

Figure 4 shows the I–V characteristics of the CMOS SPAD. The leakage current of the SPAD after 30 MeV proton irradiation did not increase significantly before reaching the avalanche breakdown voltage. When a bias voltage of 26 V was applied, the reverse current increased from 5.47 mA to 5.71 mA. Table 2 shows a comparison of the SPAD breakdown voltages. The breakdown voltage increased by only 20 mV after 30 MeV proton irradiation, while it remained unchanged after 52 MeV proton irradiation. This indicates that proton displacement damage can lead to a slight increase in the breakdown voltage, but not significantly. This is similar to the results of SPAD  $\gamma$  experiments based on the same P-I-N structure in Ref. [28], indicating that the leakage current and breakdown voltage (V<sub>B</sub>) are almost insensitive to ionization damage and displacement damage.

Figure 4. I–V characteristics for CMOS SPAD.

Table 2. Comparison of the SPAD breakdown voltage.

| Proton Energy<br>(MeV) | V <sub>B</sub> (Fresh)<br>(V) | $V_{B}$ (5 $	imes$ 10 $^{10}$ p/cm $^{2}$ ) (V) |

|------------------------|-------------------------------|-------------------------------------------------|

| 30                     | 24.23                         | 24.25                                           |

| 52                     | 24.18                         | 24.18                                           |

#### 3.2. DCR

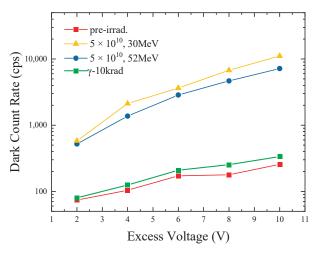

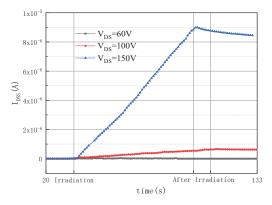

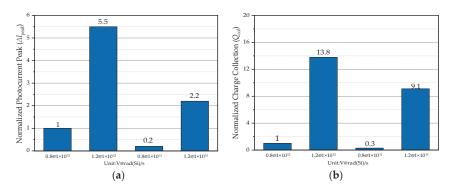

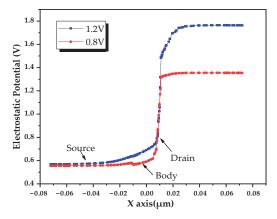

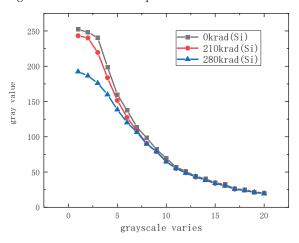

Figure 5 shows the DCR data under different excess voltages before and after irradiation with a passive quenching circuit at 23 °C. It can be seen that before irradiation, the DCR increases with the increase in excess voltage from 74cps@2V to 256cps @10V. But after proton irradiation, the increase in the DCR is very significant. The DCR increases from 74cps@2V before irradiation to 520cps@2V after 52 MeV proton irradiation. This is consistent with the trend of DCR change with excess voltage before irradiation. However,

due to the increase in displacement damage defects in the junction depletion region caused by proton irradiation, the trend of DCR increase with higher excess voltage is significantly enhanced. The DCR increased form 580cps@2V to 11102cps@10V after 30 MeV proton irradiation. Under the same proton fluence of  $5\times10^{10}~\rm p/cm^2$ , the change caused by 30 MeV proton irradiation is greater than that caused by 52 MeV proton irradiation. This is due to the NIEL of low-energy protons being higher than that of high-energy protons, resulting in a DDD of  $2.82\times10^8~\rm MeV/g$  for the 30 MeV protons, which is higher than the DDD of  $1.69\times10^8~\rm MeV/g$  for the 52 MeV protons. So, the displacement damage defects generated by the 30 MeV protons in the junction depletion region resulted in a larger DCR at the same excess voltage.

**Figure 5.** DCR of different excess voltages after proton and  $\gamma$  irradiation.

The TID and DDD caused by proton irradiation resulted in Si-SiO<sub>2</sub> interface defects and junction depletion region defects. In order to confirm the main reason for the increase in the DCR,  $\gamma$  irradiation was conducted with a TID of 10 krad(Si), while the TID of the 52 MeV proton was only 7.66 krad(Si). The DCR after  $\gamma$  irradiation increased from 256 cps to 336 cps at an excess voltage of 10 V. However, after proton irradiation, the DCR increased to 7160 cps, which is approximately 20 times greater than that of  $\gamma$  irradiation, indicating that the increase in the DCR is mainly caused by the displacement damage of proton irradiation, and the TID effect is not obvious.

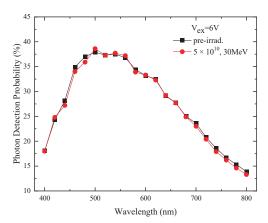

#### 3.3. PDP

The PDP is defined as the ratio of the SPAD-detected photons to the incident photons and reflects the generation of photo-generated carriers. It reflects the photosensitivity of the SPAD. The PDP depends on two main parameters: the absorption probability and the triggering efficiency. The absorption probability is the probability of photons being absorbed in the depletion region, and it depends on the reflectivity, the depth of the junction, and the thickness of the depletion region, while the triggering efficiency is the probability of photo-generated electron–hole pairs triggering a self-sustaining avalanche process, which depends on the electric field [1]. Figure 6 shows a comparison of the PDP curve at an excess voltage of 6 V before and after 30 MeV proton irradiation. It can be seen that there is no significant change in the PDP in the wavelength range of 400 nm–800 nm. The maximum PDP of the SPAD is 37.9% and 38.6% at a wavelength of 500 nm. This indicates that the depletion region defects caused by a proton displacement irradiation damage dose of  $2.82 \times 10^8 \, \text{MeV/g}$  have no effect on the absorption of incident photons and the generation of photo-generated carriers, so the PDP does not change. Ref. [28] reports that the PDP

also has no changes after  $\gamma$  irradiation, which also means that the PDP is not an important radiation-sensitive parameter to consider in radiation environments [32].

Figure 6. PDP value of 30 MeV protons.

#### 4. Discussion

From the previous results, it can be concluded that the SPAD leakage current, breakdown voltage, and PDP are not sensitive to proton displacement damage, but the DCR is very sensitive. The DCR reflects the inherent noise inside a single-photon detector. The sources of noise in silicon devices include thermal noise, tunneling-assisted noise, and trap-assisted noise. Among them, thermal noise and tunneling-assisted noise are related to the operating temperature, doping concentration, and excess voltage of the device. Trapassisted noise is related to defects introduced during the CMOS manufacturing process, and trap defects introduced during irradiation also produce trap-assisted noise [33-37]. The thermal generation and band-to-band tunneling effects of free carriers within the depletion region collectively contribute to the DCR, which is largely dependent on temperature. When the temperature increases by 10 °C near the room temperature of 23 °C, the DCR usually increases by more than double [38,39]. At this temperature, thermal generation is the main noise source. The thermal generation of free carriers is closely related to the presence of impurities and crystal defects, which introduce local energy levels near the middle of the band gap. According to the Shockley-Read-Hall theory, electron-hole pairs are generated sequentially through generation-recombination (G-R) centers. The proton irradiation of silicon-based devices can also form deep-energy-level defects near the center of the energy band in the depletion region, which can trap or emit electrons and become the trap center. These irradiated deep-energy-level defects contribute to the increase in the dark count rate. Besides the thermal effect, another major contributor to the DCR are Poole-Frenkel effects and rap-assisted tunneling, but the DCR does not significantly increase with temperature but instead increases with excess bias, which usually happens in high-doping junctions. The effects of displacement damage on semiconductor materials and devices can be understood in terms of the energy levels introduced in the bandgap. Those radiation-induced levels result in the following effects: the recombination lifetime and diffusion length are reduced; the generation lifetime decreases; majority-carrier and minority-carrier trapping increase; the majority-carrier concentration changes; the thermal generation of electron-hole pairs is enhanced in the presence of a sufficiently high electric field; tunneling at junctions is enabled; and radiation-induced defects reduce the carrier mobility and can exhibit metastable configurations [40,41].

To analyze the displacement damage of protons in the SPAD, we used The Stopping and Range of Ions in Matter Software (SRIM) to simulate the proton transportation process, which is a program written by J.F. Ziegler, M.D. Ziegler, and J.P. Biersack to simulate the

interaction process of ion beams with solids, and the Monte Carlo method was used to calculate details such as vacancies, energy deposition, and particle positions during the collision process [42].

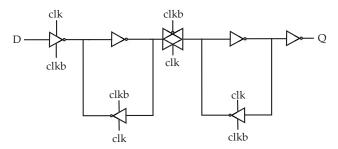

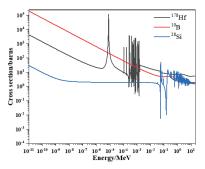

The simulation results of the proton trajectory, stopping power, and energy deposition per unit distance in the photo collector region are shown in Figure 7. At the SPAD surface, the stopping power of silicon for the 30 MeV protons is higher than that for the 52 MeV protons, indicating that the damage caused by the 30 MeV protons on silicon is more severe under the fluence of  $5 \times 10^{10}$  p/cm². As the incident depth increases, the deposited energy of the 30 MeV protons in silicon increases significantly, which is manifested as an enhancement of proton scattering in the same number of particle trajectories, resulting in a larger projected area of the incident direction. The calculated number of vacancies in silicon is shown in Table 3. Comparing the difference between the vacancy numbers and the  $\Delta$ DCR under different excess voltages, it is found that the number of vacancies is 24 for each 30 MeV proton and 13.7 for each 52 MeV proton, and the ratio is 1.75. However, the ratio of DCR increase at the five excess voltages varies from 0.93 to 1.59, which is a little lower than the ratio of vacancy. This may be because not all trap vacancies contribute to the generation of carriers, which will cause the DCR in the depletion region to increase; some vacancies are used for the carrier's recombination. The DCR increase is defined as

$$\Delta DCR = DCR$$

after irradiation – DCR before irradiation (1)

**Table 3.** The ratio of vacancies and  $\Delta$ DCR at different excess voltages.

| Proton<br>Energy<br>(MeV) | Total<br>Vacancies<br>(/ion) | ΔDCR@2V<br>(cps) | ΔDCR@4V<br>(cps) | ΔDCR@6V<br>(cps) | ΔDCR@8V<br>(cps) | ΔDCR@10V<br>(cps) |

|---------------------------|------------------------------|------------------|------------------|------------------|------------------|-------------------|

| 30                        | 24                           | 506              | 2020             | 3468             | 6584             | 10,846            |

| 52                        | 13.7                         | 446              | 1268             | 2686             | 4488             | 6904              |

| ratio                     | 1.75                         | 1.13             | 1.59             | 1.29             | 1.47             | 1.57              |

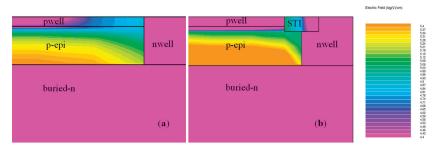

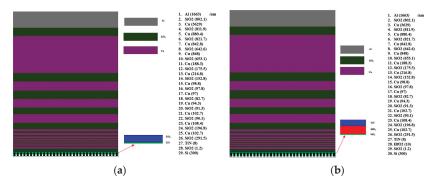

In order to analyze the influence of  $Si-SiO_2$  interface defects on the STI structure, two types of SPAD units, with and without an STI structure, were designed on the same chip. The simulation results of the SPAD design and the electric field distribution with and without an STI structure are shown in Figure 8. Between the p-well and deep n-well, we designed an STI structure using silicon dioxide as an insulating layer. It can be seen that the electric field distribution near the STI structure changes significantly. After ionizing radiation, interface charges accumulate at the Si-SiO<sub>2</sub> interface near the STI structure.

After proton irradiation with the same fluence, the DCR was measured under different excess voltages. The results are shown in Figure 9. The comparison of the results with and without an STI structure before irradiation shows that the presence of the STI structure increases the DCR from 256 cps to 362 cps under a 10 V bias. The interface defects in the STI structure before irradiation increase the DCR by 41.4%. Ref. [28] has proven that the increase in the DCR caused by ionizing irradiation is mainly due to the induced Si-SiO<sub>2</sub> interface traps near the STI structure. The DCR of the SPAD with and without an STI structure significantly increased after irradiation. At 10 V, the DCR increased by 30 times. However, when the excess voltage was 0–8 V, the DCR of the SPAD without an STI structure was higher than that of the SPAD with an STI structure. When the excess voltage was greater than 8 V, the DCR of the SPAD without the STI structure was lower. A possible reason for this is that the Si-SiO<sub>2</sub> interface defect charges near the STI structure will be released from the interface and drift into the depletion region when the electric field exceeds a certain value, and then an avalanche process is formed, resulting in an increase in the DCR.

Figure 7. Stopping power and trajectory of protons in silicon.

Figure 8. SPAD and electric field distribution without STI structure (a) and with STI structure (b).

Figure 9. Comparison of DCR irradiation with and without STI structure.

#### 5. Conclusions

Proton irradiations on the CMOS SPAD of 30 MeV and 52 MeV are studied in this article. The leakage current, breakdown voltage, and PDP before and after proton irradiations were measured and compared with  $\gamma$  rays. SPAD units with and without an STI structure were designed and simulated, and we summarize our results as follows:

- 1. After the 30 MeV proton radiation, the reverse current increased from 5.47 mA to 5.71 mA at a bias voltage of 26 V. The breakdown voltage increased by only 20 mV after the 30 MeV proton irradiation, while it remained unchanged after the 52 MeV proton irradiation. The reported results of the SPAD  $\gamma$  experiments based on the same P-I-N structure in Ref. [17] indicate that the breakdown voltage (V<sub>B</sub>) is almost insensitive to ionization damage and displacement damage.

- 2. Before irradiation, the DCR increased with an increase in the excess voltage from 74cps@2V to 256cps@10V, but the DCR increased rapidly to 520cps@2V and 7160cps@10V after the 52 MeV proton irradiation. For the 30 MeV proton irradiation, the DCR increased form 580cps@2V to 11102cps@10V. The displacement damage defects generated by the 30 MeV protons with a DDD of  $2.82 \times 10^8$  MeV/g resulted in a larger DCR increase than a DDD of  $1.69 \times 10^8$  MeV/g for the 52 MeV protons at the same excess voltage. The trend of the DCR increasing with a higher excess voltage is significantly enhanced due to the displacement damage defects in the junction depletion region. A comparison of  $\gamma$  irradiation with a TID of 10 krad (Si) and the 52 MeV protons with a TID of 7.66 krad (Si) shows that the increase in the DCR is mainly caused by the displacement damage of proton irradiation instead of the TID effect.

- 3. The SPAD units with and without an STI structure also show that the main reason for the DCR increase is the depletion region defects caused by proton displacement damage rather than the Si-SiO<sub>2</sub> interface trap generated by ionization.

- 4. The comparison of the leakage current, breakdown voltage, and PDP shows that the design of the SPAD based on the standard CMOS process exhibits good radiation hardening, but the process of the depletion region should be improved to reduce the DCR after irradiation.

**Author Contributions:** Conceptualization, M.X. and Y.L.; methodology, M.X. and Y.L.; software, M.X.; validation, M.X. and Y.L.; formal analysis, Y.L.; investigation, Y.L.; resources, M.L. and C.H.; data curation, J.F.; writing—original draft preparation, M.X.; writing—review and editing, M.X. and Y.L.; visualization, M.X.; supervision, Y.L.; project administration, Q.G.; funding acquisition, Y.L. and Q.G. All authors have read and agreed to the published version of the manuscript.

Funding: This research was funded by the West Light Talent Training Plan of the Chinese Academy of Sciences under grant No. 2021-XBQNXZ-020, the Tianshan Innovation Team Program of Xinjiang Uygur Autonomous Region No. 2022D14003, the Fund of Robot Technology Used for Special Environment Key Laboratory of Sichuan Province No. 21kftk03, and the "Light of West China" Program of the Chinese Academy of Sciences under grant No. 2020-XBQNXZ-004.

Data Availability Statement: Data are contained within the article.

Conflicts of Interest: The authors declare no conflicts of interest.

#### References

- Cusini, I.; Berretta, D.; Conca, E.; Incoronato, A.; Madonini, F.; Maurina, A.A.; Nonne, C.; Riccardo, S.; Villa, F. Historical Perspectives, State of art and Research Trends of Single Photon Avalanche Diodes and Their Applications (Part 1: Single Pixels). Front. Phys. 2022, 10, 607. [CrossRef]

- Cusini, I.; Berretta, D.; Conca, E.; Incoronato, A.; Madonini, F.; Maurina, A.A.; Nonne, C.; Riccardo, S.; Villa, F. Historical Perspectives, State of Art and Research Trends of SPAD Arrays and Their Applications (Part II: SPAD Arrays). Front. Phys. 2022, 10, 906671. [CrossRef]

- Sun, X.; Abshire, J.B.; Krainak, M.A.; Lu, W.; Beck, J.D.; Sullivan, W.W.; Mitra, P.; Rawlings, D.M.; Fields, R.A.; Hinkley, D.A.; et al. HgCdTe avalanche photodiode array detectors with single photon sensitivity and integrated detector cooler assemblies for space lidar applications. Opt. Eng. 2019, 58, 067103. [CrossRef]

- 4. Zhao, J.X.; Milanese, T.; Gramuglia, F.; Keshavarzian, P.; Tan, S.S.; Tng, M.; Lim, L.; Dhulla, V.; Quek, E.; Lee, M.J.; et al. On Analog Silicon Photomultipliers in Standard 55-nm BCD Technology for LiDAR Applications. *IEEE J. Sel. Top. Quantum Electron.* 2022, 28, 10. [CrossRef]

- Gramuglia, F.; Wu, M.L.; Bruschini, C.; Lee, M.J.; Charbon, E. A Low-Noise CMOS SPAD Pixel with 12.1 Ps SPTR and 3 Ns Dead Time. IEEE J. Sel. Top. Quantum Electron. 2022, 28, 9. [CrossRef]

- 6. Therrien, A.C.; Bérubé, B.L.; Thibaudeau, C.; Charlebois, S.; Lecomte, R.; Fontaine, R.; Pratte, J.F. Modeling of Single Photon Avalanche Diode Array Detectors for PET Applications. In Proceedings of the IEEE Nuclear Science Symposium/Medical Imaging Conference (NSS/MIC)/18th International Workshop on Room-Temperature Semiconductor X-Ray and Gamma-Ray Detectors, Valencia, Spain, 23–29 October 2011.

- 7. Tétrault, M.A.; Lamy, É.; Boisvert, A.; Fontaine, R.; Pratte, J.F. Low Dead Time Digital SPAD Readout Architecture for Realtime Small Animal PET. In Proceedings of the 60th IEEE Nuclear Science Symposium (NSS)/Medical Imaging Conference (MIC)/20th International Workshop on Room-Temperature Semiconductor X-ray and Gamma-ray Detectors, Seoul, Republic of Korea, 27 October–2 November 2013.

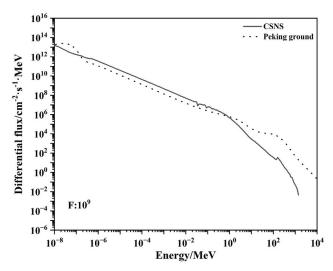

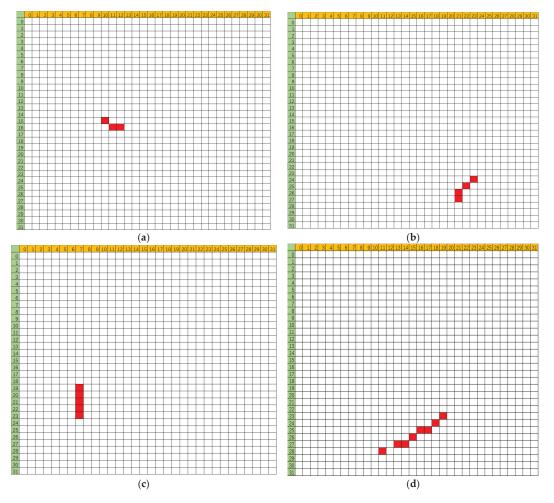

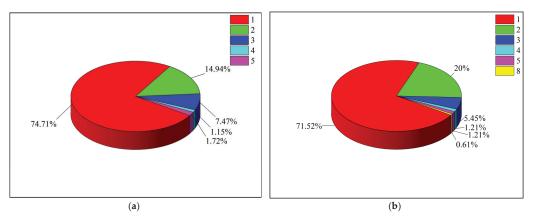

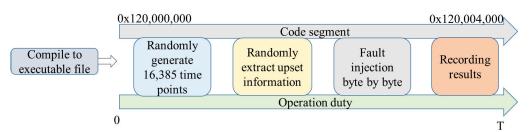

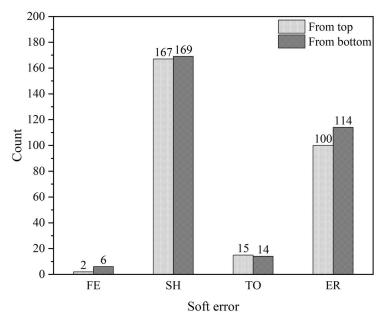

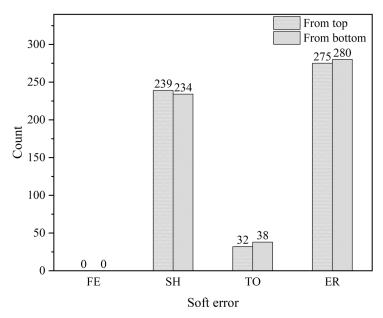

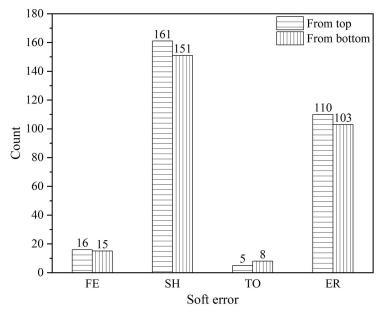

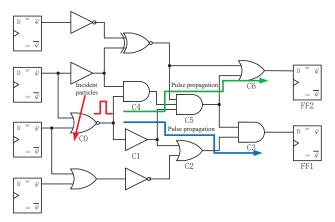

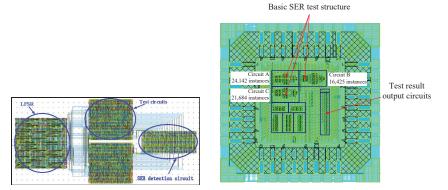

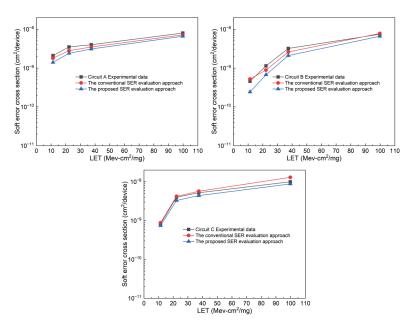

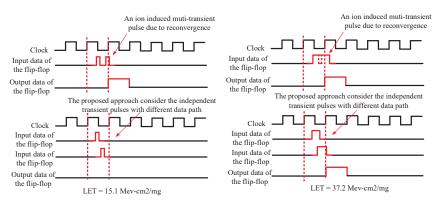

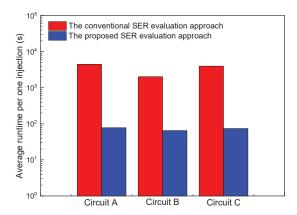

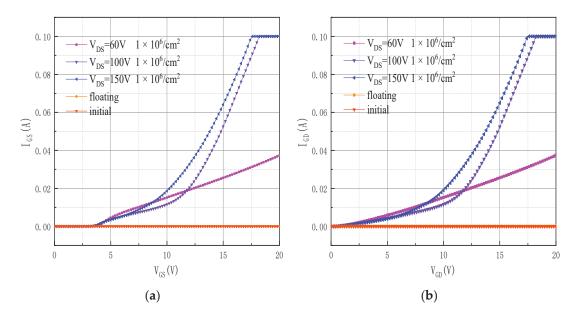

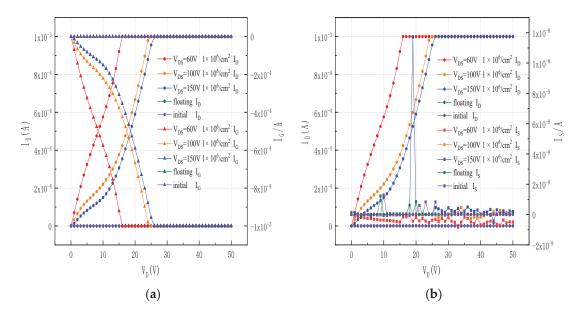

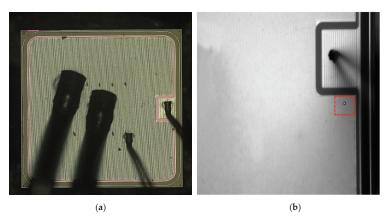

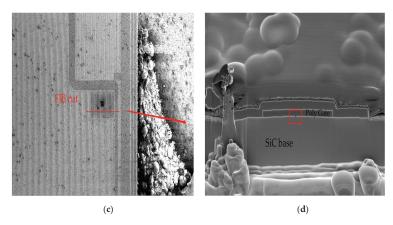

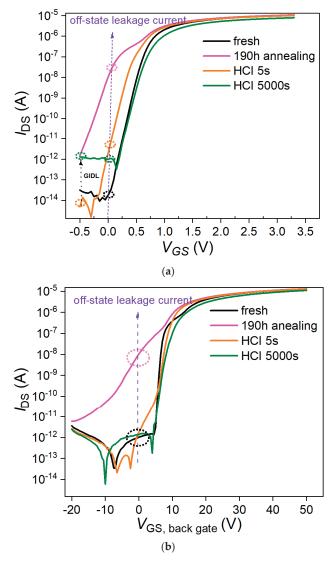

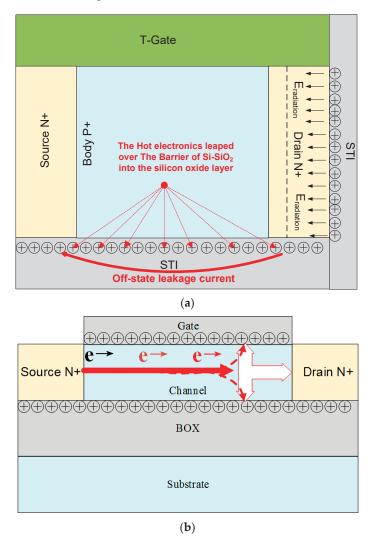

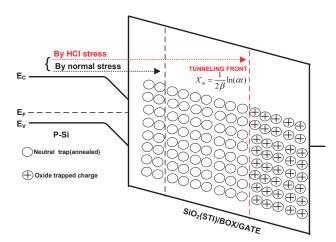

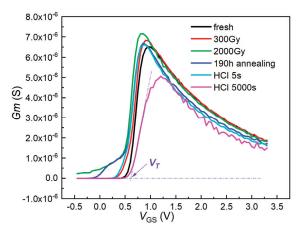

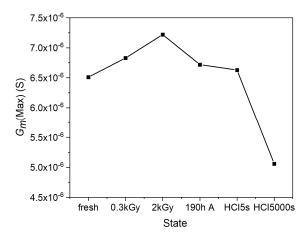

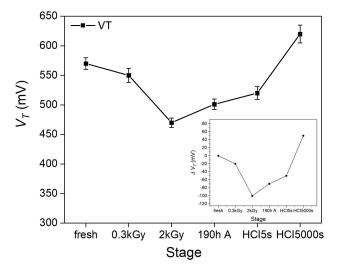

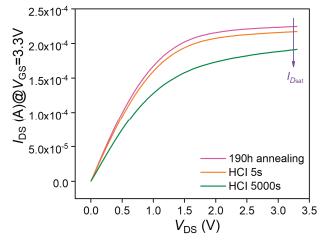

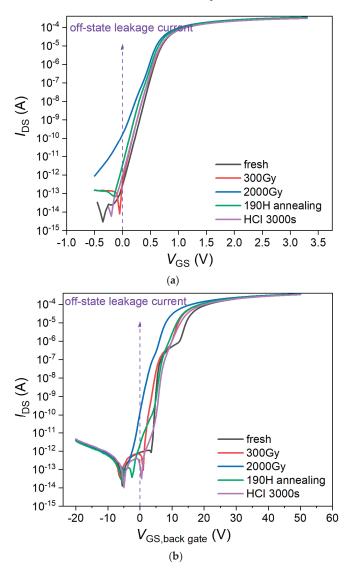

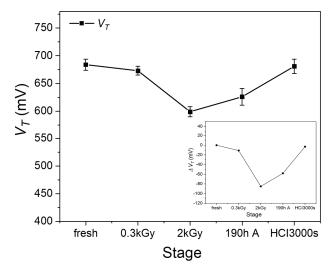

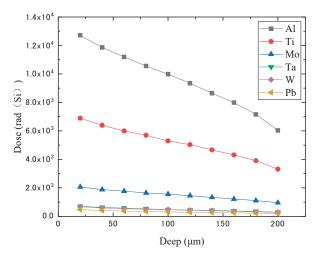

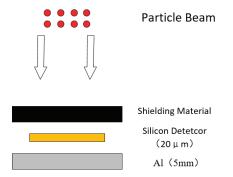

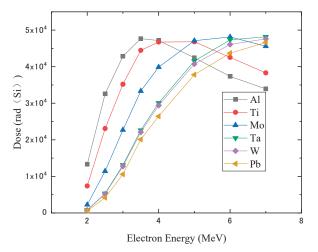

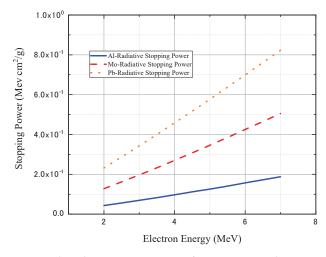

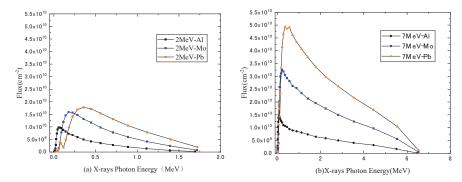

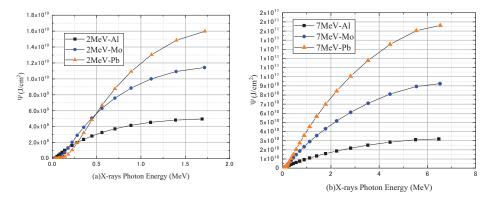

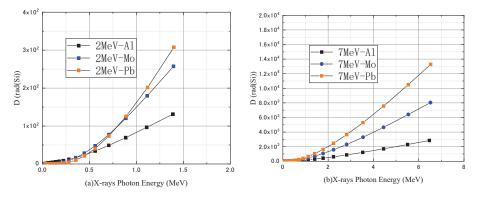

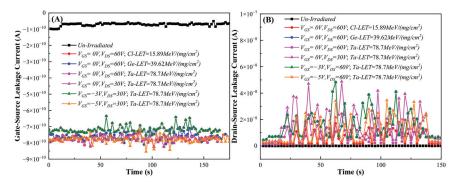

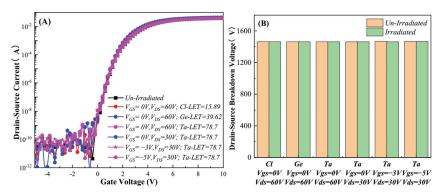

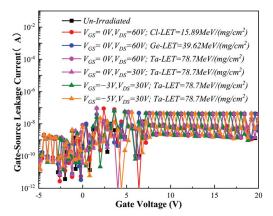

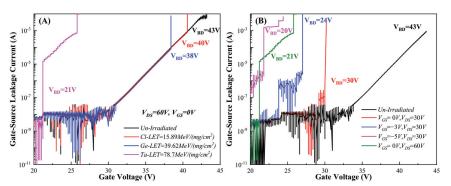

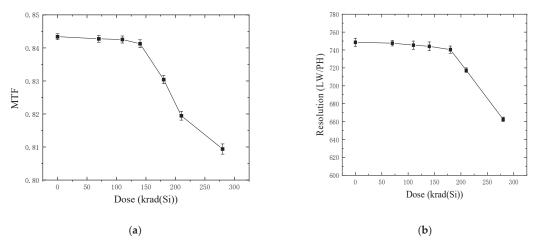

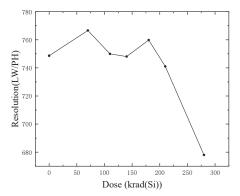

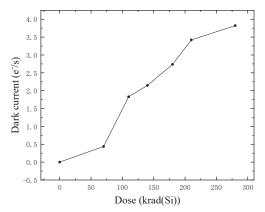

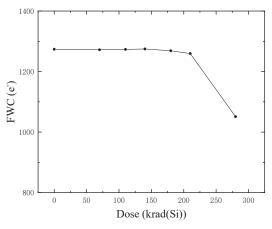

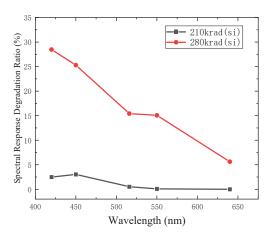

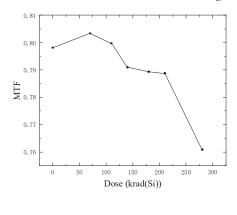

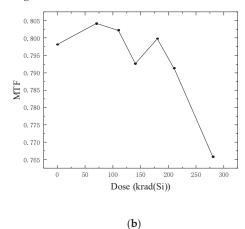

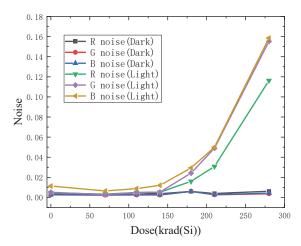

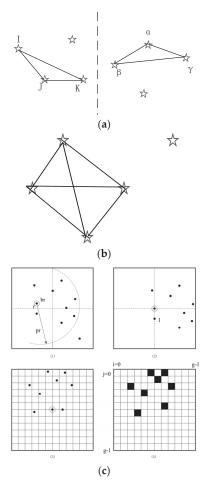

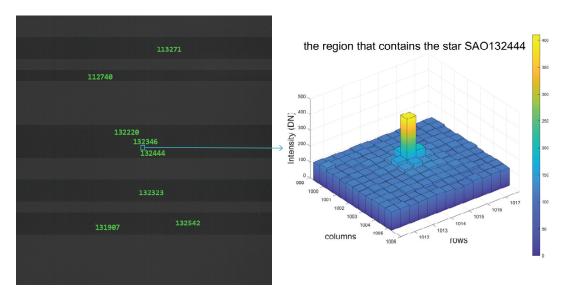

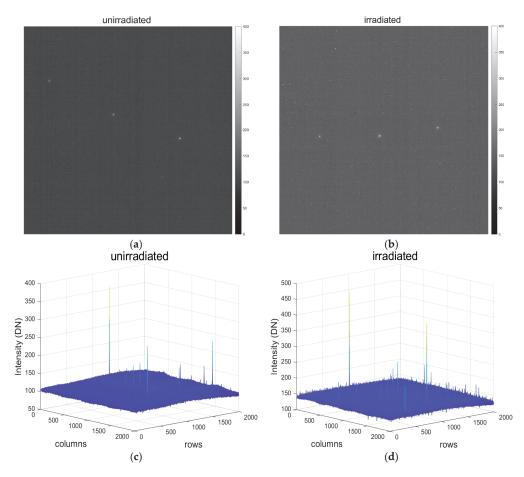

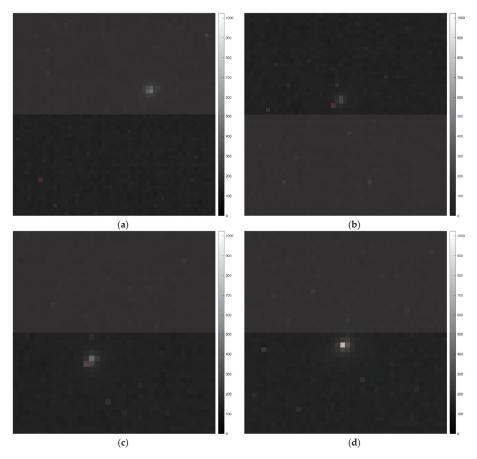

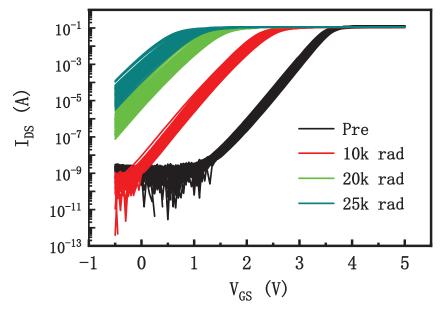

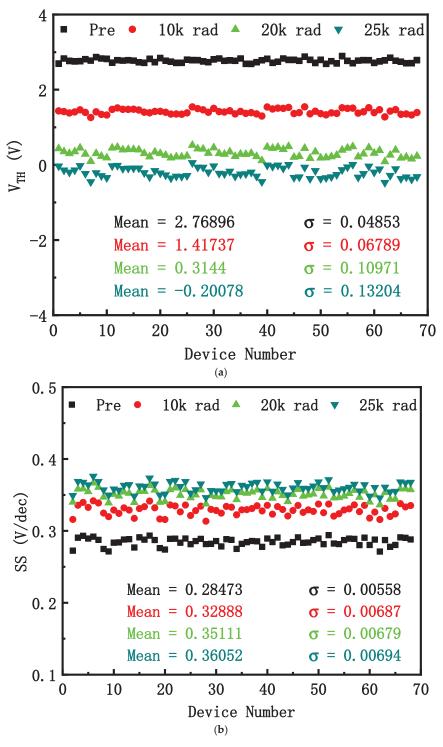

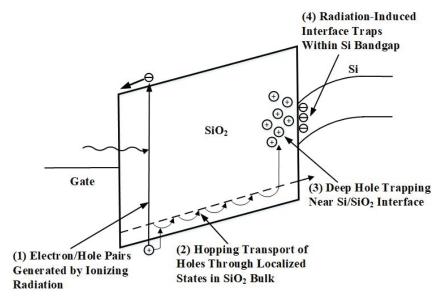

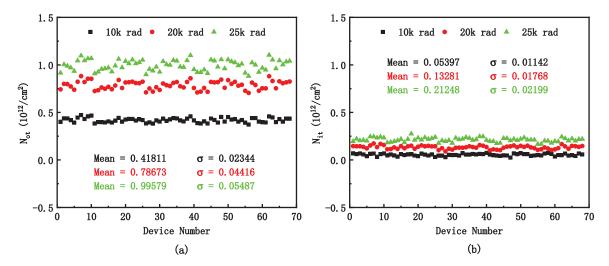

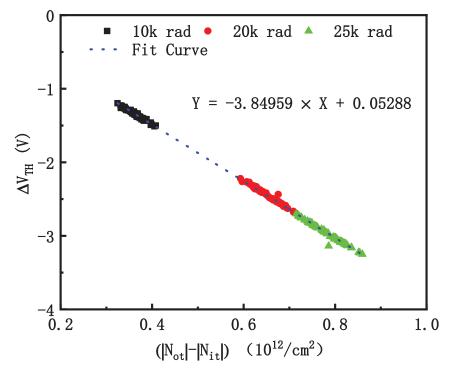

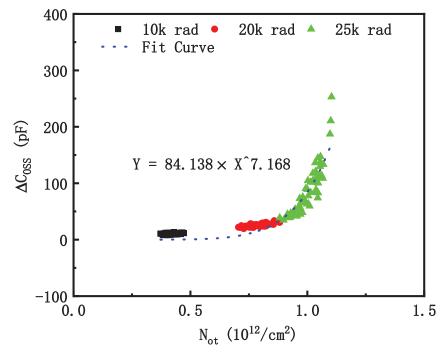

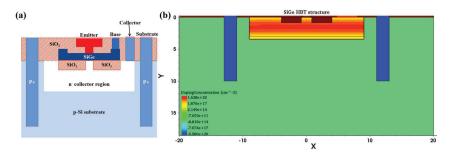

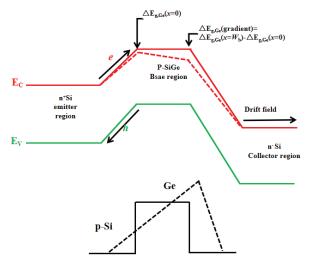

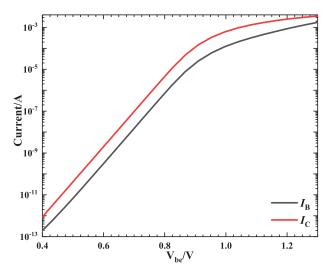

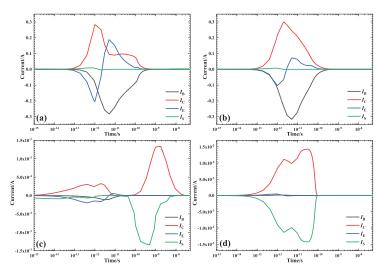

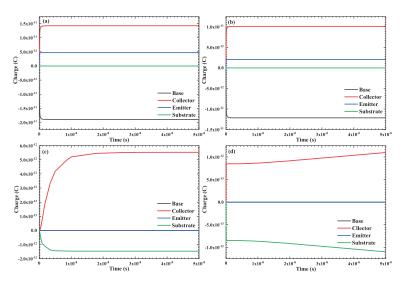

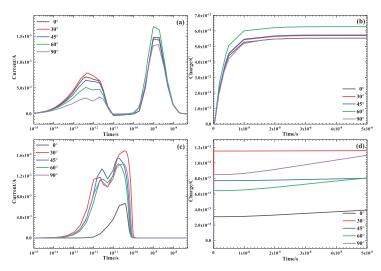

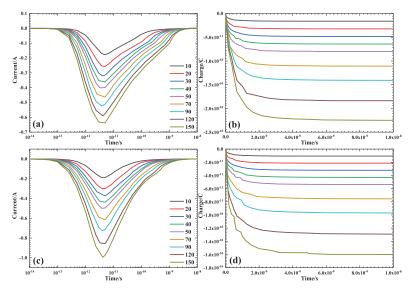

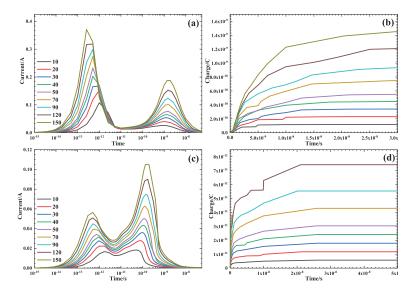

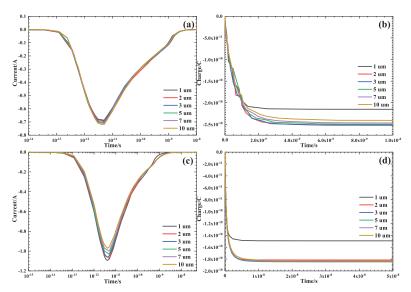

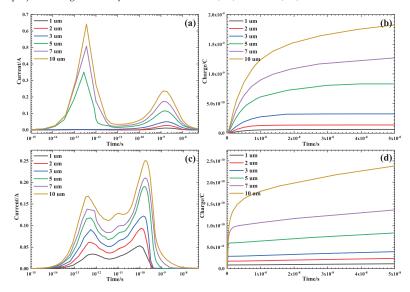

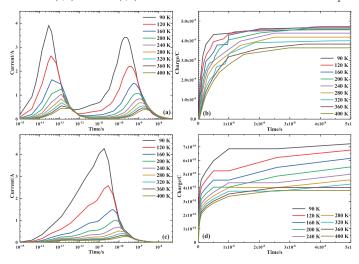

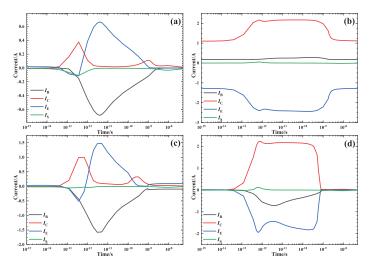

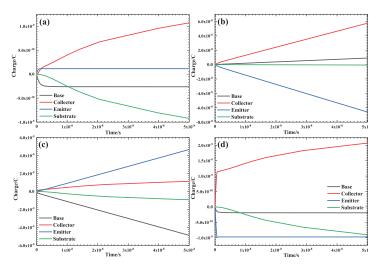

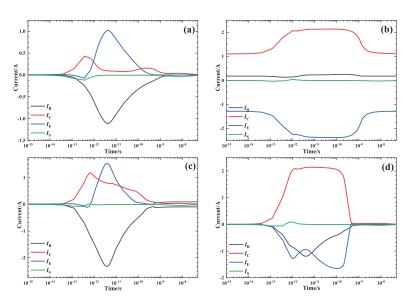

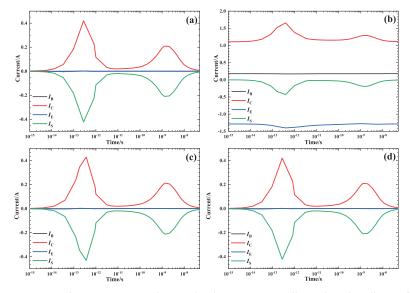

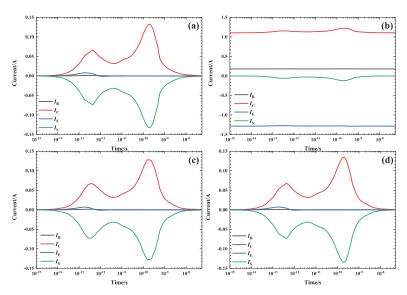

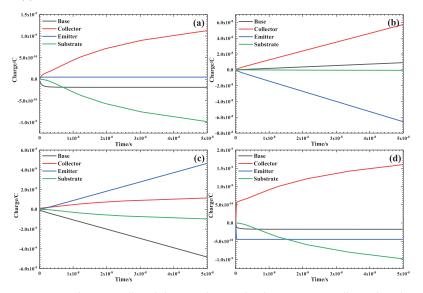

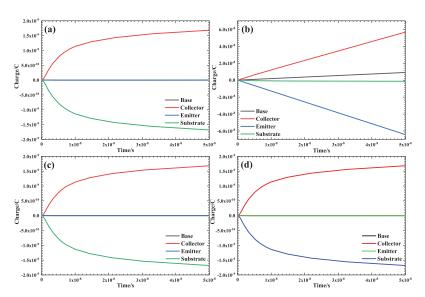

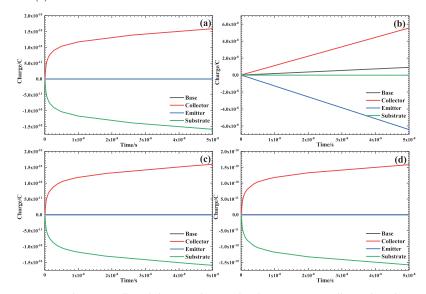

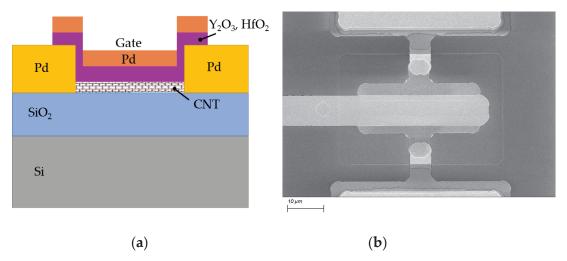

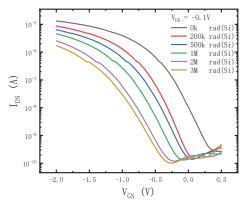

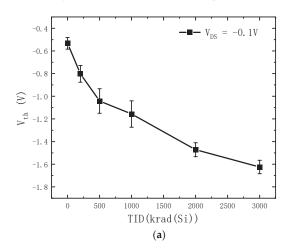

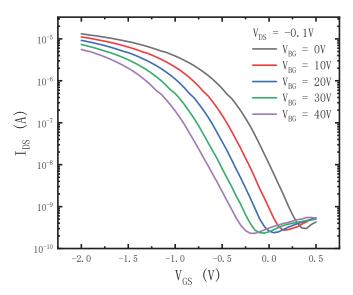

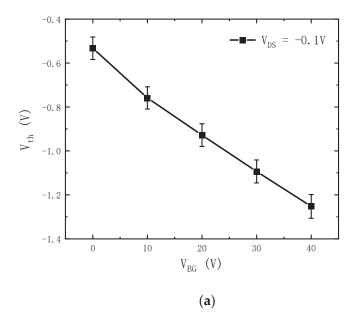

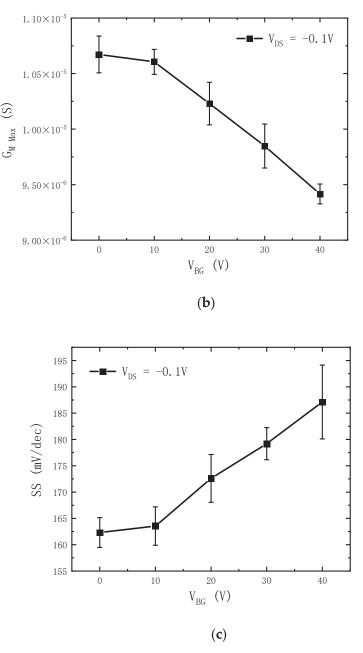

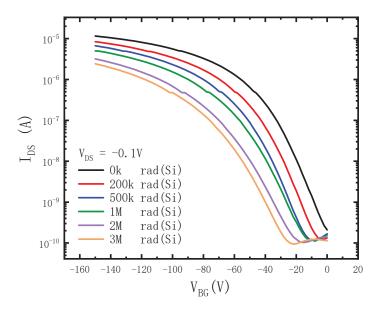

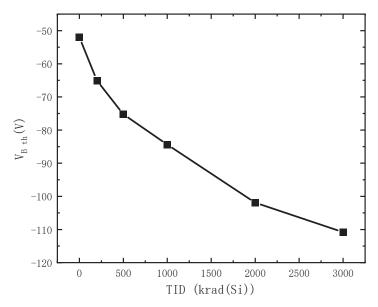

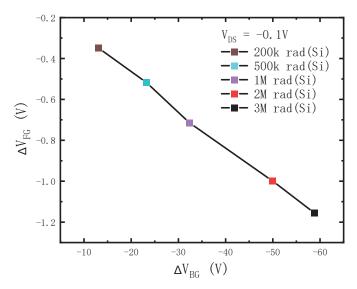

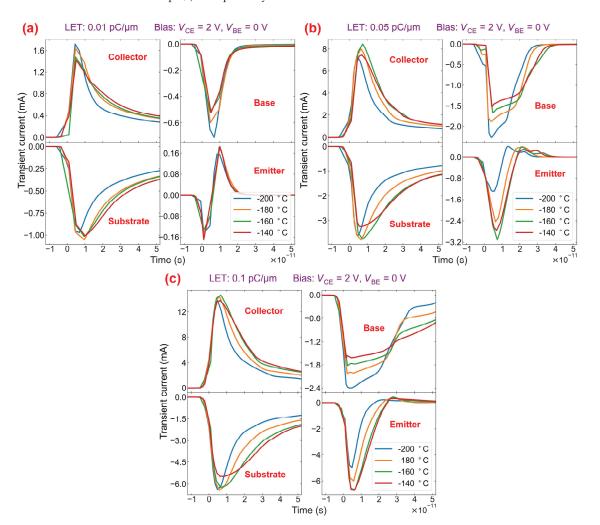

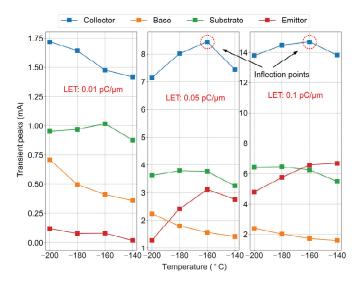

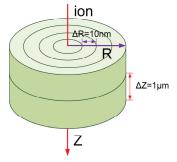

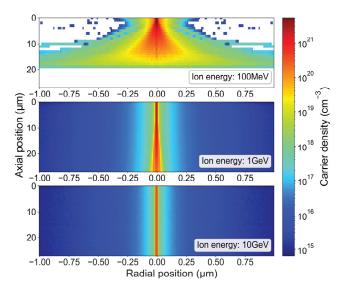

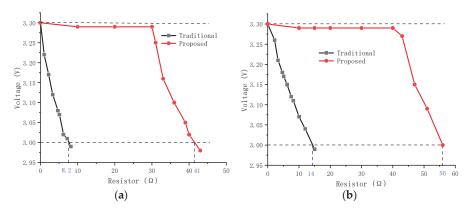

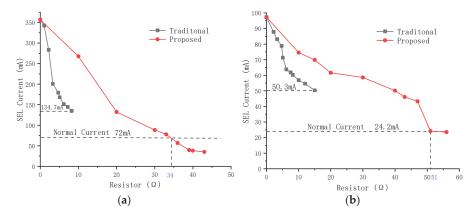

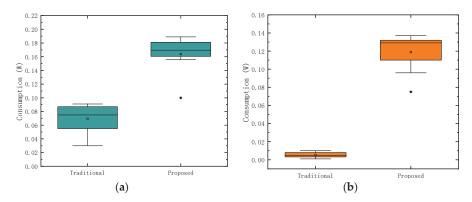

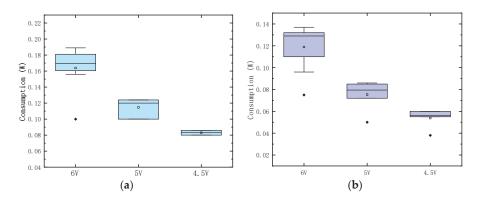

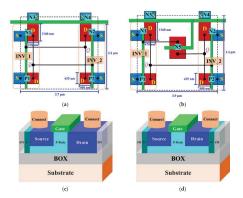

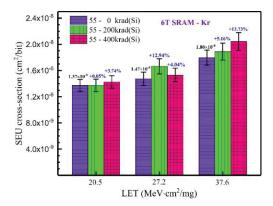

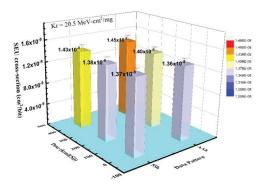

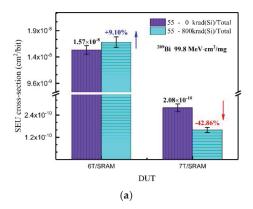

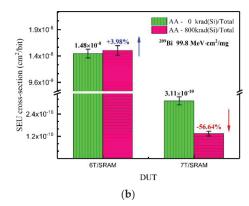

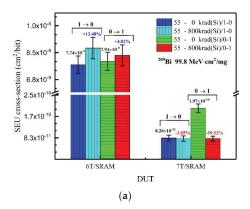

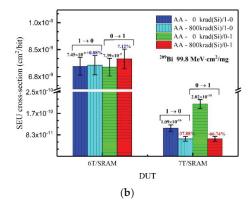

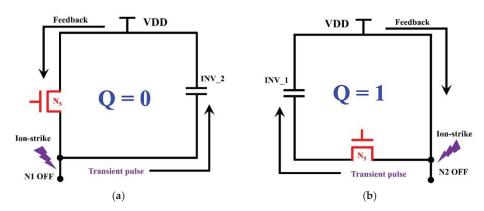

- Braga, L.H.C.; Perenzoni, M.; Stoppa, D. Effects of DCR, PDE and Saturation on the Energy Resolution of Digital SiPMs for PET. In Proceedings of the 60th IEEE Nuclear Science Symposium (NSS)/Medical Imaging Conference (MIC)/20th International Workshop on Room-Temperature Semiconductor X-ray and Gamma-ray Detectors, Seoul, Republic of Korea, 27 October–2 November 2013