# Article Development of a Digitally Controlled Inductive Power Transfer System with Post-Regulation for Variable Load Demand

Kateryna Stoyka<sup>1,\*</sup>, Antonio Vitale<sup>1</sup>, Massimo Costarella<sup>1</sup>, Alfonso Avella<sup>1</sup>, Mario Pucciarelli<sup>1</sup> and Paolo Visconti<sup>2</sup>

<sup>1</sup> Medinok S.p.A., Via Palazziello, 79, 80040 Volla, Italy; a.vitale@medinok.com (A.V.);

m.costarella@medinok.com (M.C.); a.avella@medinok.com (A.A.); m.pucciarelli@medinok.com (M.P.)

Department of Innovation Engineering, University of Salento, Street for Monteroni, 73100 Lecce, Italy;

paolo.visconti@unisalento.it \* Correspondence: k.stoyka@medinok.com; Tel.: +39-3206242635

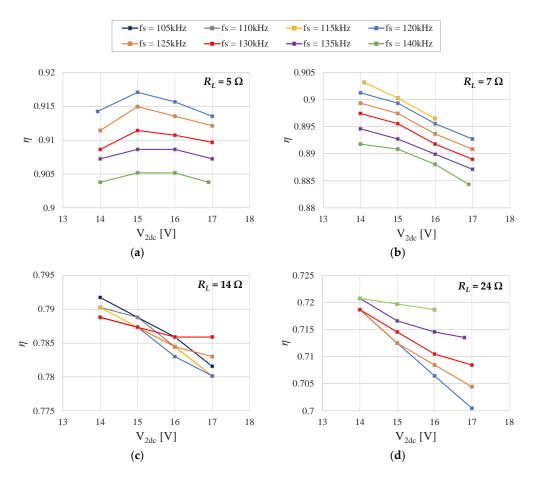

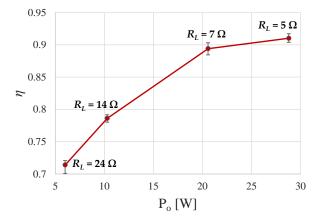

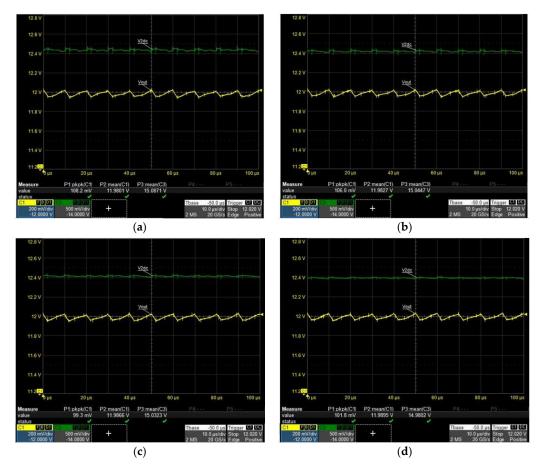

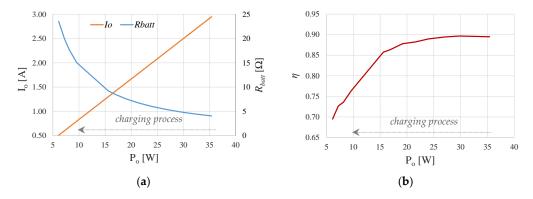

Abstract: Inductive Power Transfer (IPT) is an emerging technology enabling a contactless charging process in manifold applications such as electric vehicles, wearable and portable devices, or biomedical applications. Such technology can be profitably used to develop enhanced electronic solutions in the framework of smart cities, homes and smart workplaces. This paper presents the development and realization of a series-series compensated IPT System (IPTS) followed by a post-regulator implemented by means of a DC-DC converter. Such a system is modeled through a first harmonic approximation method, and a sensitivity analysis of the IPTS performance is carried out with respect to the variations of the primary inverter switching frequency and phase-shift angle. As an element of novelty of this work, the bias points are determined which allow the efficiency maximization while ensuring system controllability. An enhanced dynamic modeling of the system is then performed by means of a coupled mode theory, including the inverter phase-shift modulation and extending its validity to whatever operating frequency. A digital control of the post-regulator is implemented by means of a commercial low-cost microcontroller enabling the output voltage regulation under both fixed and variable load conditions through a voltage mode control technique. An IPTS prototype is eventually realized, which is able to correctly perform the output voltage regulation at the desired nominal value of 12 V for static resistive loads in the range  $[5, 24] \Omega$ , yielding the output power in the range [6, 28.8] W and the experimental efficiencies going from 72.1% (for 24  $\Omega$ ) to 91.7% (for 5  $\Omega$ ). The developed system can also be effectively used to deliver up to 35 W output power to variable loads, as demonstrated during the battery charging test. Finally, an excellent output voltage regulation is ascertained for load transients between 5  $\Omega$  and 24  $\Omega$ , with limited over- and undershoot amplitudes (less than 3% of the nominal output voltage), thus enabling the use of the proposed system for both fixed and variable loads in the framework of smart homes and workplaces applications.

**Keywords:** DC–DC converters; digital control; inductive power transfer systems; modeling; pot cores; switch-mode power supplies; wireless power transfer

# 1. Introduction

The wireless charging of electric and electronic devices and systems has become increasingly popular in everyday life since it allows for a contactless power transfer between a stationary primary source and one or more stationary or movable secondary loads. In this framework, Inductive Power Transfer (IPT) allows for a safe, reliable and cost-effective charging process over relatively large air-gaps via magnetic coupling between the primary transmitting and the secondary receiving coil, by exploiting the same operation principle as that of transformers and coupled inductors but with weaker coupling. Today, IPT Systems (IPTSs) are used in manifold applications such as charging electric vehicles [1], as

**Citation:** Stoyka, K.; Vitale, A.; Costarella, M.; Avella, A.; Pucciarelli, M.; Visconti, P. Development of a Digitally Controlled Inductive Power Transfer System with Post-Regulation for Variable Load Demand. *Electronics* **2022**, *11*, 58. https:// doi.org/10.3390/electronics11010058

Academic Editor: Nikolay Hinov

Received: 24 November 2021 Accepted: 21 December 2021 Published: 25 December 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). extensively discussed in [2], mobile [3] and portable [4] devices, biomedical applications [5], etc. Such technology can be profitably used to develop enhanced electronic solutions in the framework of smart cities [6], homes [7] and smart workplaces [8].

Resonant circuits are normally employed in the primary and/or secondary IPTS side to increase the power transfer capability while minimizing the required voltage and current ratings of the power supply [9]. Different compensation topologies can be adopted in this regard, depending on the resonant circuit configuration. The simplest and most used topology is a Series–Series (S–S) compensation, which employs a resonant capacitor in series with each coupling coil. One of the advantages of the S-S topology is that there is no reflected reactance if the IPTS is operated at the secondary resonant frequency. Thus, the primary inductance can be compensated independently of either the magnetic coupling or the load by a series-connected capacitance in the primary network. Hence, the S–S compensation has been adopted for the IPTS presented in this paper. As regards the IPT coil configuration, different commercial off-the-shelf parts are available from manufacturers such as Würth Elektronik [10], TDK [11] and Abracon [12], satisfying the given constraints of the size, of the self and mutual inductance, as well as of the DC winding resistance and rated current values. However, as the available coupling area becomes smaller, only commercial products with rather high DC winding resistance values are available for a certain inductance target, since small winding cross-section areas are usually adopted to meet the dimensional requirements. Consequently, rather high power losses are expected to occur in the coil windings as the application currents increase, leading to lower overall system efficiencies. Hence, custom coils should be realized for the applications requiring relatively small coupling areas and relatively high currents.

Generally, the main requirements which need to be satisfied by the IPTSs concern the output voltage/current regulation and the system efficiency maximization. The first one depends on the load specifications (battery, resistive load, etc.) and is usually the primary design objective which has to be fulfilled. In recent years, different IPTS architectures and control techniques have been proposed to reach the above requirements. These include the IPT systems with passive [13] and active [14] rectification on the receiving side, as well as the IPTS with regulating rectifiers [15]. More complex solutions include the pre-regulated and the post-regulated IPTSs using the DC/DC converters on the transmitting and the receiving side, respectively [16]. A detailed overview of different IPTS architectures and control techniques is provided hereinafter, and the relative advantages and drawbacks are highlighted.

In this paper, we present a digitally controlled IPT system with a synchronous rectification and a step-down DC/DC converter used as a post-regulator. The output voltage regulation for variable loads is accomplished by means of the digital voltage mode control of the DC/DC converter, while the maximum efficiency is achieved by modulating the switching frequency and the phase-shift angle of the full-bridge inverter located at the transmitting IPTS side. A static system-level modeling of the proposed IPTS has been performed through a First Harmonic Approximation (FHA) method, since the resonant coil currents are nearly sinusoidal, and only the first harmonics of the primary and the secondary voltages and currents contribute to the power transfer.

As a first element of novelty of this work, we have developed the FHA-based static model of the post-regulated S–S IPTS, and carried out a sensitivity analysis of the system performances with respect to the variations of the main operating parameters and component values. In particular, we have adopted such a model with a two-fold purpose: (i) to determine the optimal values of the compensation capacitances for given IPT coils; (ii) to perform the mapping of the system performances with respect to several IPTS operating parameters (namely the inverter switching frequency and phase-shift angle), so as to determine the maximum overall efficiency.

As a second element of novelty, we have investigated the controllability issues of the buck post-regulator cascaded to the IPTS using the developed FHA static model. In this regard, we have shown that the buck output voltage can present a non-monotonic behavior

with respect to the duty-cycle, which may lead to system instability for certain parameters and component values. Hence, feasible operating regions have been determined wherein the system controllability is ascertained.

As a third element of novelty, we have performed the dynamic modeling of the postregulated IPTS by means of Coupled Mode Theory (CMT). In this regard, we have enhanced the original CMT modeling procedure by including the inverter phase-shift modulation and by extending its validity to whatever operating frequency. As a result, the control-to-output transfer function of the post-regulator has been obtained, enabling the digital controller design needed for the output voltage regulation.

An experimental prototype of the IPTS has been eventually developed to be able to deliver up to 35 W output power at the maximum efficiency of 91.7%. The article is arranged as follows: in the next sub-section, an overview of different IPTS architectures and control techniques is provided; in Section 2, the static system-level modeling of the presented IPTS is discussed, followed by the dynamic modeling and digital controller design presented in Section 3. The experimental prototype of the proposed IPTS is described in Section 4, and the measurements results are provided and discussed. Eventually, the conclusions are drawn in Section 5.

## 1.1. Overview of IPTS Architectures and Control Techniques

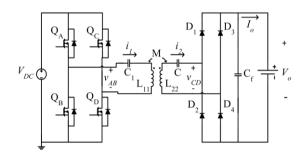

Figure 1 depicts one of the most commonly used architectures of the IPT systems based on the S–S compensation topology and using a full-bridge inverter on the transmitting (TX) side and a passive diode-bridge rectifier on the receiving (RX) side. The primary inverter converts the DC voltage and current waveforms of the source into the AC waveforms applied to the primary resonant tank, which is composed of a primary IPT coil and the respective resonant capacitor. The power is wirelessly transferred between the primary and the secondary coil by means of mutual coupling, and the resulting AC voltage and current waveforms of the secondary resonant tank are rectified by the diode-bridge and delivered to the load. For such IPTS topology, it is not possible to realize the output voltage regulation entirely on the RX side, since the diodes are automatically turned on and off depending on the secondary coil current direction. The research presented in [13] proposed a control scheme to regulate the output voltage of the S–S IPTS with passive rectification by controlling the switching frequency or the phase-shift angle of the full-bridge inverter. A detailed dynamic analysis based on the extended describing function technique was presented and the small-signal model of the system derived including both the frequency and the phase-shift control. However, such a control strategy requires the presence of a communication link between the TX and RX sides, which introduces a delay in the control loop and thus limits the dynamic performances of the proposed control scheme.

Figure 1. S-S IPTS with passive rectification [13].

An active rectification scheme replaces rectifier diodes with power MOSFETs, thus allowing to control their switching process and directly regulate the output voltage on the RX side, without using any communication link with the TX side. In [14], a fixed-frequency phase-shift control strategy was proposed for dual active IPTS including full-bridge inverter and rectifier. In such a scheme, the secondary phase-shift angle is controlled to regulate the system output voltage, while the primary phase-shift angle is adjusted to achieve the

minimum duty-cycle needed for zero-voltage switching (ZVS). The complication of the proposed scheme is that the current phase detection circuits are required on both the TX and RX sides to realize the proposed control strategy.

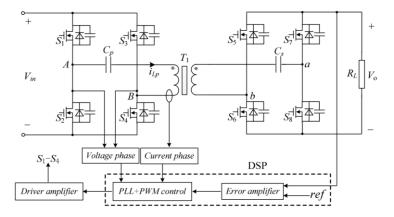

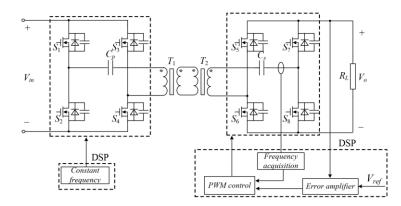

A similar bidirectional S–S IPTS with a double active bridge configuration was presented in [17], with the difference that two cascaded contactless transformers have been adopted for energy charging between electric vehicles. Two control strategies were implemented: the Primary Phase-Locked Loop (P-PLL) and Pulse-Width Modulation (PWM) control (P-PLL&PWM) and the Primary Constant Frequency plus Secondary PWM control (P-CF+S-PWM). In the P-PLL&PWM control scheme depicted in Figure 2, the PWM controller regulates the pulse width of the primary full-bridge inverter to regulate the output voltage, and the PLL control strategy regulates the frequency of the inverter to the achieve the ZVS of power devices on the primary side, while the active bridge rectifier on the RX side works as a conventional rectifier circuit. In the P-CF+S-PWM scheme shown in Figure 3, the primary inverter provides a full square-wave voltage having a constant switching frequency, while the output voltage regulation is realized entirely on the RX side by controlling the rectifier pulse-width duration. Hence, the second approach does not require a communication link between the TX and RX side. The experimental results suggest that the P-CF+S-PWM control has higher efficiency. However, such a strategy does not consider the efficiency maximization and can therefore be improved.

Figure 2. Dual active S–S IPTS with P-PLL&PWM control strategy [17].

Figure 3. Dual active S-S IPTS with P-CF+S-PWM control strategy [17].

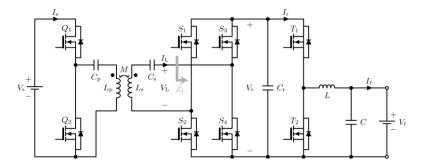

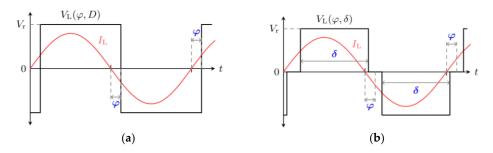

A more complex IPTS scheme with active rectification and a post-regulator on the RX side depicted in Figure 4 was proposed in [18] with the scope to maximize the efficiency as well as increase the amount of extractable power while operating in non-resonant conditions. The proposed method is based on actively modifying the equivalent secondary-side load impedance  $Z_L$  seen at the rectifier input, by controlling the phase-shift  $\varphi$  of the active rectifier and its output voltage level  $V_r$ . This parameter can be controlled by either

adjusting the duty-cycle *D* of the post-regulator or by varying the duty-cycle  $\delta$  of the active rectifier, as shown in Figure 5. The phase-shift  $\varphi$  between the secondary voltage  $V_L$  and current  $I_L$  is realized by inserting a time delay between the primary and secondary side control signals, which is achieved by using a communication link between the primary and secondary side controllers. The proposed scheme considers a constant battery voltage at the IPTS output and does not perform the output voltage regulation, which could be a drawback for different types of load.

Figure 4. S-S IPTS with active rectifier and buck post-regulator [18].

**Figure 5.** Graphs of voltage  $V_L$  and current  $I_L$  delayed by the phase shift  $\varphi$  obtained by varying: (a) the buck duty-cycle *D* and (b) the active rectifier duty-cycle  $\delta$ , where  $V_r$  is the resulting rectified voltage [18].

To enhance regulation capabilities of the IPTS schemes with passive rectification such as the one depicted in Figure 1, pre- or post-regulators can be adopted. Some of the papers introducing IPTSs with post-regulating DC/DC converters have used the perturb-andobserve (P&O) techniques to achieve maximum system efficiency. The research presented in [19] proposed the S–S IPTS using a passive diode-bridge rectifier followed by a cascaded boost-buck converter. A P&O technique was adopted which searches for the optimal post-regulator duty-cycle value maximizing the overall system efficiency obtained at the IPT resonant frequency. Similarly to the work presented in [18], no regulation of the output voltage was included in the above control scheme. In [20], a method for automatic maximum efficiency point tracking of the IPTS followed by a buck-boost converter was proposed. The presented algorithm searches for the minimum input power operating point for a given output power by varying the phase-shift of the inverter, while the PI controller of the buck-boost adjusts the output voltage. Because the searching process is carried out on the TX side, the proposal does not require any feedback from the RX side. The research in [21] proposes some improvements with respect to [20], by adopting a Discrete Sliding Mode Control (DSMC) scheme for the buck-boost post-regulator. The TX side of the adopted IPTS comprises a phase-shift full-bridge inverter, which incorporates the hill-climbing-search-based phase angle control for achieving minimum input current injection from its DC source, thereby attaining minimum the input power operation. The buck-boost converter realizes the output voltage regulation by means of the proposed DSMC scheme, which outperforms classical PI controller-based schemes in terms of better dynamic performances.

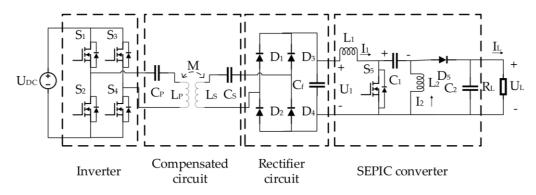

The S–S IPTS with a passive rectifier and a Single-Ended Primary Inductor Converter (SEPIC) depicted in Figure 6 was proposed in [22]. The SEPIC topology offers several benefits in switching power supplies thanks to its non-inverting step-up/step-down conversion ratio, to the possibility of reducing the size of magnetic components by using coupled inductors and to its loss-less resistor behavior in power factor pre-regulation applications [23]. A phase-shift control of the primary inverter was designed to regulate the primary coil current at a given reference value, in order to optimize the equivalent load resistance seen at the post-regulator input for maximum energy efficiency. A peak-current-control of the SEPIC was configured to guarantee the output voltage regulation under different load conditions. A disadvantage of the proposed approach consists of utilizing a refence value for the primary current (to achieve the optimal load conditions) which is very sensitive to the coupling coefficient and system component variations.

Figure 6. S-S IPTS with passive rectifier and SEPIC post-regulator [22].

A more complicated control scheme for the IPTS with a passive rectification and a buck–boost post-regulator was proposed in [24] with the aim of maximizing the overall system efficiency while maintaining a constant output power level. In such a scheme, a primary-to-secondary voltage ratio is regulated through the buck–boost duty-cycle control to reach the maximum efficiency under resonance conditions, while the IPTS input voltage is adjusted to yield the target output power to the load. Such a control scheme requires a pre-regulator (e.g., a boost converter) to change the IPTS input voltage, which ends up being complicated for practical implementations; moreover, the proposed voltage ratio control criterion is only valid under given resonance conditions. Finally, the output voltage regulation is not included in the above control scheme.

The authors in [25] presented a Maximum Efficiency Point (MEP) tracking method for IPTSs whose RX side contains either a passive rectifier with post-regulator or a regulating rectifier. This last rectification topology uses two additional MOSFETs at the input of the diode bridge which are periodically turned on and off to regulate the IPTS output voltage. It is proven that, under resonance conditions, at the MEP, the derivative of post-regulator duty-cycle *D* with respect to the inverter DC input voltage  $V_{in}$  is equal to or smaller than a constant  $\beta$  determined by the system parameters, namely  $dD/dV_{in} \leq \beta$ . It is also shown that increasing  $V_{in}$  allows to reach the MEP as soon as  $dD/dV_{in}$  becomes equal to or lower than  $\beta$ . Thus, the MEP can be tracked without a power or current sensor.

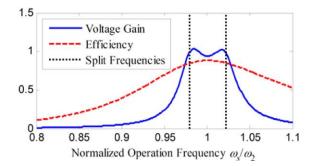

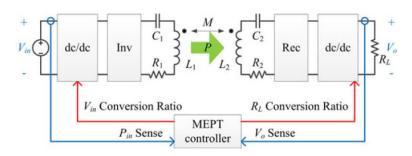

Four different IPTS schemes and relative control techniques were analyzed and compared in [16], with the scope to achieve the output voltage regulation: Lower-side Frequency Control (LFC), Higher-side Frequency Control (HFC), pre-regulation, and post-regulation. The first two techniques are based on the behavior of an open-loop IPTS which presents two peaks near the split frequencies in the "over coupled" region, as depicted in Figure 7. In particular, LFC (HFC) controls the inverter switching frequency on the left (right) side of the low (high) split frequency to regulate the IPTS output voltage. Conversely, the pre- (post-) regulation scheme adopts a DC/DC converter on the primary (secondary) IPT side to regulate the output voltage by fixing the switching frequency and controlling the converter duty-cycle. A Maximum Efficiency Point Tracking (MEPT) control scheme was proposed based on the use of a both pre- and post-regulating DC/DC converter (see Figure 8), where the output voltage regulation is accomplished by the post-regulator controller, while the maximum efficiency is achieved by the pre-regulator controller.

Figure 7. Illustration of the IPTS voltage gain and efficiency including split frequencies [16].

Figure 8. Closed-loop system structure of the MEPT control scheme proposed in [16].

Eventually, Ref. [26] presented an MEPT algorithm for the post-regulated IPTS to match the load impedance to that of the source impedance. The proposed algorithm varies both the switching frequency and the phase-shift of the inverter to minimize the input power, whereas the output power is kept constant by a buck converter, which is used to regulate the battery voltage and current. The drawback of the proposed study is that, during the buck controller design, the influence of the IPTS on the duty-to-output transfer function of the buck converter is not taken into account.

In this paper, we overcome such a limitation by correctly modeling the post-regulator dynamics accounting for the IPTS connected to its input. To this end, we exploit the findings of [27] which used Coupled-Mode Theory (CMT) to deal with the dynamic modeling of the IPTS pre-regulated by a buck converter. Such an approach uses slowly varying amplitudes and phases of coupled modes, rather than resonant currents and voltages, to model the coupled resonances of the IPT stage. It also includes the non-linearities of the inverter and rectifier stages operating at a full square-wave voltage under IPTS resonant conditions. A continuation of [27] can be found in [28], where the steady-state and dynamic characteristics of an open-loop IPTS post-regulated by a buck-boost converter are investigated by means of the CMT. It is shown that, for certain operating conditions and system component values, the steady-state control-to-output curve of the post-regulator can be non-monotonic, since its static and dynamic characteristics are tightly coupled to the IPT stage. In particular, when the control-to-output curve changes its slope and starts decreasing, the system runs into positive feedback and goes out of control. In this paper, we enhance the modeling procedure proposed in [27,28] by including the inverter phase-shift modulation and by extending its validity to whatever operating frequency. Such an enhanced procedure is herein formulated for the buck post-regulator, but its findings are general and can also be applied to other basic converter topologies (e.g., boost, buck-boost, etc.).

A comparison between the main IPTS solutions discussed previously and the system developed in this work is subsequently provided in the Section 4.4, highlighting their relevant features and specifications.

# 2. Static Modeling of Post-Regulated IPTS

## 2.1. Post-Regulated IPTS (PR-IPTS)

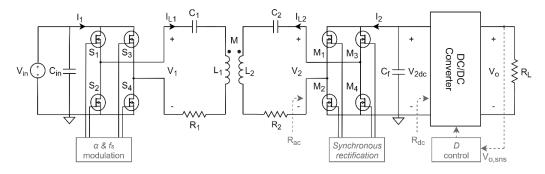

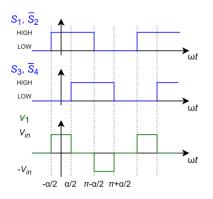

Figure 9 shows a schematic of a Post-Regulated IPTS (PR-IPTS) using a series–series compensation topology. The coupling coils, represented by the self-inductances  $L_1$  and  $L_2$ , are compensated with the series capacitors  $C_1$  and  $C_2$ . The magnetic coupling between the coils is represented by their mutual inductance M. The TX coil is connected to the source through a MOSFET full-bridge inverter implementing a phase-shift and frequency modulation, with the objective of maximizing the overall system efficiency. The phase-shift modulation consists of modulating the phase angle  $\alpha$  between the complementary square-wave gate signal pairs used to control the MOSFETs of the two inverter legs, as depicted in Figure 10. As a result, a modified square-wave voltage  $v_1(t)$  is obtained at the inverter output (indicated by the green waveform in Figure 10). The resistor  $R_1$  includes the equivalent resistances of  $L_1$ ,  $C_1$  and of the two inverter MOSFETs conducting simultaneously.

Figure 9. Series-series post-regulated IPTS schematic.

The RX coil is connected to the resistive load  $R_L$  through a MOSFET full-bridge rectifier followed by a buck DC/DC converter implementing a duty-cycle *D* control at a fixed switching frequency  $f_{Buck}$ . Such control aims to regulate the system output voltage  $V_o$  at a desired nominal value  $V_{o,nom}$ , under both static and dynamic load conditions. As a result of the presence of the buck converter, the equivalent DC resistance seen at the rectifier output is given by (1):

$$R_{dc} = R_L / M(D)^2 \tag{1}$$

where  $M(D) = V_0/V_{2dc} = D$  represents the buck conversion ratio while  $V_{2dc}$  is the intermediate bus voltage between the rectifier and the buck. The resistor R<sub>2</sub> includes the equivalent resistances of  $L_2$ ,  $C_2$  and of the two rectifier MOSFETs conducting simultaneously. A synchronous rectification scheme has been herein adopted for the full-bridge rectifier, in which each MOSFET is turned on after a short conduction of the relative body-diode (as soon as its drain–source voltage decreases below a given negative threshold), and is turned off when its drain–source voltage exceeds the threshold [29]. Thus, the conduction losses can be reduced as compared to the passive diode bridge configuration [30].

#### 2.2. Static Modeling of PR-IPTS

The above PR-IPTS has been modeled using an FHA method, since the primary and the secondary coil currents are nearly sinusoidal, and only the first harmonics of the voltages  $(v_1(t), v_2(t))$  and currents  $(i_{L1}(t), i_{L2}(t))$  contribute to the power transfer. Such FHA quantities can be represented through their respective phasors  $\overline{V}_1 = V_1 e^{j\phi V_1}$ ,  $\overline{V}_2 = V_2 e^{j\phi V_2}$ ,  $\overline{I}_{L1} = I_{L1} e^{j\phi_{L1}}$ ,  $\overline{I}_{L2} = I_{L2} e^{j\phi_{L2}}$ .

As a result of the phase-shift modulation, the peak amplitude of the primary voltage phasor is given by (2):

$$V_1 = \frac{4}{\pi} V_{in} \sin\left(\frac{\alpha}{2}\right) \tag{2}$$

The FHA allows to model the power electronics connected to the RX side with an equivalent AC resistance  $R_{ac}$ , expressed as the ratio between the amplitudes of the first harmonics of voltage and current at the input of the rectifier bridge [1]:

$$R_{ac} = \frac{V_2}{I_{L2}} = \frac{8}{\pi^2} R_{dc}$$

(3)

Under FHA assumption, the analyzed IPTS can be described with the following phasor equation system (4):

$$\begin{cases} \overline{V}_1 = \left(j\omega_s L_1 + \frac{1}{j\omega_s C_1} + R_1\right)\overline{I}_{L1} + j\omega_s M\overline{I}_{L2} \\ \overline{V}_2 = j\omega_s M\overline{I}_{L1} + \left(j\omega_s L_2 + \frac{1}{j\omega_s C_2} + R_2\right)\overline{I}_{L2} = -R_{ac}\overline{I}_{L2} \end{cases}$$

(4)

where  $\omega_s = 2\pi f_s$  represents the angular switching frequency of the inverter. For a certain value of the intermediate bus voltage  $V_{2dc}$ , the equivalent resistance  $R_{ac}$ , seen by the IPT secondary side, can be evaluated using (1) and (3), while the peak amplitude of the secondary voltage first harmonic is given by (5):

$$V_2 = \frac{4}{\pi} V_{2dc} \tag{5}$$

If the phase  $\phi_{V2}$  is taken as a zero reference for the phase angles, the phasor  $\overline{V}_2 = V_2$  is known, and the equation system (4) can be solved to obtain the remaining phasors, as given in (6):

$$\overline{I}_{L2} = -\frac{\overline{V}_2}{R_{ac}}, \quad \overline{I}_{L1} = \frac{\left(j\omega_s L_2 + \frac{1}{j\omega_s C_2} + R_2 + R_{ac}\right)}{j\omega_s M} \frac{\overline{V}_2}{R_{ac}}$$

$$\overline{V}_1 = \frac{\left[\left(j\omega_s L_1 + \frac{1}{j\omega_s C_1} + R_1\right)\left(j\omega_s L_2 + \frac{1}{j\omega_s C_2} + R_2 + R_{ac}\right) + \omega_s^2 M^2\right]}{j\omega_s M} \frac{\overline{V}_2}{R_{ac}}$$

(6)

Starting from (6), it is possible to evaluate the peak amplitude of the primary voltage first harmonic  $V_1$ , and estimate the resulting phase-shift  $\alpha$  by inverting (2):

$$\alpha = 2\arcsin\left(\frac{\pi}{4}\frac{V_1}{V_{in}}\right) \tag{7}$$

If the resulting  $\alpha$  value is real and included in the range  $[0, \pi]$ , the analyzed operating condition (relative to the considered  $V_{2dc}$  value) is feasible, and the primary and secondary IPT average powers  $P_1$  and  $P_2$  can be evaluated according to (8):

$$P_{1} = 1/2 \operatorname{Re}\left\{\overline{V}_{1}\overline{I}_{L1}^{*}\right\}$$

$$P_{2} = 1/2 \operatorname{Re}\left\{\overline{V}_{2}\overline{I}_{L2}^{*}\right\}$$

(8)

Note that such average powers do not take into account the inverter switching losses, the coils ferrite core losses and the post-regulator losses, since simplified FHA modeling do not allow for including such loss contributions. However, the above approach does enable the evaluation of the overall system behavior under different operating conditions of  $f_s$  and  $V_{2dc}$ , which are the two main parameters used herein to optimize the IPTS efficiency  $\eta = P_2/P_1$ .

## 2.3. Compensation Capacitors Selection

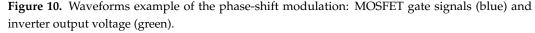

For a given TX and RX coil set, the IPTS power and efficiency levels depend on the selected values of the compensation capacitors  $C_1$  and  $C_2$ , as highlighted by the IPTS modeling solution (5)-(8). Given the IPTS operating parameters and component values listed in Table 1, Equations (5)–(8) have been evaluated for  $V_{2dc}$  = 17 V,  $C_1$  = {100, 200} nF and  $C_2 = \{50, 100, 150, 200\}$  nF. The IPT coil design resulting in the coil parameters of Table 1 will be subsequently described. Note that the analyzed IPTS has been herein designed to deliver an average output power of approximately 20 W at a regulated output voltage of 12 V to a resistive load of 7  $\Omega$ , but different output power levels are also feasible and will be tested in the experimental section of this paper. Figure 11 depicts the simulated IPTS efficiency  $\eta$  (Figure 11a), the primary coil rms current  $I_{L1rms} = I_{L1}/\sqrt{2}$  (Figure 11b), and the normalized phase-shift  $d = \alpha / \pi$  (Figure 11c,d)), for  $C_1 = 100$  nF (solid lines) and  $C_1 = 200$  nF (dashed lines). Note that only the TX coil rms current is shown in Figure 11b, since the RX coil current does not depend on the  $C_1$ ,  $C_2$  and  $f_s$  values. The plots of Figure 11c,d highlight the fact that the phase-shift changes with both  $C_1$  and  $C_2$ , since it is dependent on the  $V_1$ solution in (6). The points with d = 0 represent unfeasible operating conditions for which the output voltage regulation cannot be achieved. The plots of Figure 11a,b show that  $\eta$  and  $I_{1\text{rms}}$  levels only depend on  $C_2$ , while  $C_1$  determines the operating ranges wherein the IPTS modeling solution is feasible ( $\alpha \in [0, \pi]$  or  $d \in [0, 1]$ ). The capacitor values  $C_1 = 100$  nF and  $C_2 = 50$  nF enable achieving the highest simulated efficiency (red solid curve in Figure 11a) at high frequencies, where the converters switching losses and the coils ferrite losses are likely to become high. For this reason, the optimal choice is  $C_2 = 100 \text{ nF}$  (green curve) allowing to maximize the efficiency at ~120 kHz, with both  $C_1 = 100$  nF and 200 nF.

Table 1. IPTS operating parameters and component values.

| <i>V<sub>in</sub></i> (V) | $V_o$ (V) | $R_L$ ( $\Omega$ ) | <i>L</i> <sub>1</sub> (μH) | $R_1$ (m $\Omega$ ) | <i>L</i> <sub>2</sub> (μH) | $R_2 (m\Omega)$ | Μ (μΗ) |

|---------------------------|-----------|--------------------|----------------------------|---------------------|----------------------------|-----------------|--------|

| 24                        | 12        | 7                  | 23                         | 67                  | 23                         | 64              | 12.2   |

**Figure 11.** Predictions of IPTS modeling solution (5)–(8) vs.  $f_s$ , for different values of  $C_1$  and  $C_2$ : (a) IPTS efficiency  $\eta$ ; (b) primary coil rms current  $I_{L1rms}$ ; (c) normalized phase-shift d for  $C_1 = 100$  nF; (d) normalized phase-shift d for  $C_1 = 200$  nF.

#### 2.4. Static Modeling Results

Once the optimal compensation capacitor values have been selected, the IPTS modeling solution (5)–(8) has been evaluated over the ranges  $V_{2dc} = [14, 20]$  V and  $f_s = [60, 160]$  kHz, in order to determine the optimal parameter values maximizing the overall IPTS efficiency. Note that, in practice, a certain value of  $V_{2dc}$  can be achieved through the inverter phase-shift modulation (for a given value of  $f_s$ ), either in an open-loop fashion or through the closed-loop feedback control. However, the latter would require a communication link between the IPT primary and secondary side; therefore, the open-loop strategy has been adopted herein.

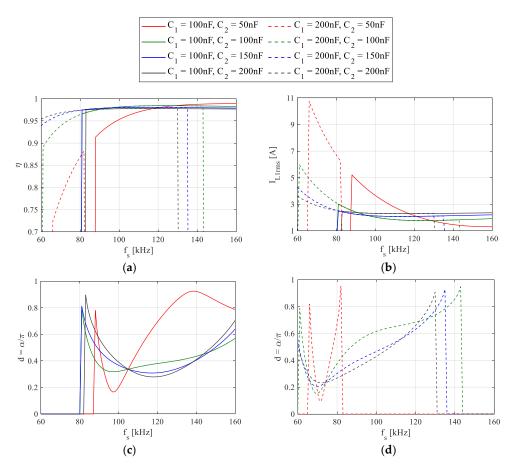

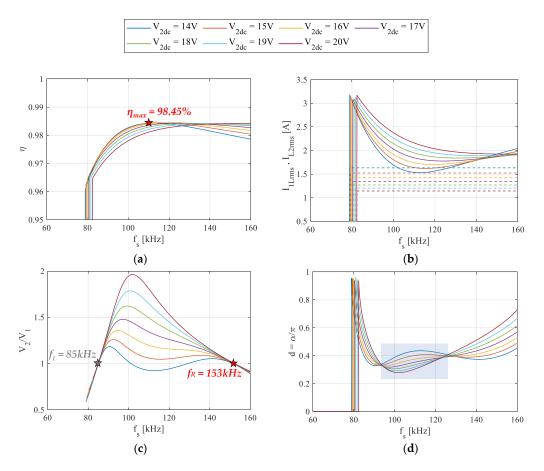

Two different capacitor set-ups, identified as the optimal ones in the previous subsection, have been analyzed and compared: { $C_1 = 100 \text{ nF}$ ,  $C_2 = 100 \text{ nF}$ } and { $C_1 = 200 \text{ nF}$ ,  $C_2 = 100 \text{ nF}$ }. Figure 12 depicts the simulated IPTS efficiency  $\eta$  (Figure 12a), the rms currents  $I_{L1rms}$  (solid lines) and  $I_{L2rms}$  (dashed lines) of the TX and RX coil, respectively (Figure 12b), the IPT stage voltage gain  $V_2/V_1$  (Figure 12c) and the normalized phase-shift *d* (Figure 12d), for the first capacitor set-up { $C_1 = 100 \text{ nF}$ ,  $C_2 = 100 \text{ nF}$ }. The plot of Figure 12a highlights that, for different frequencies, the simulated efficiency can be maximized at different levels of  $V_{2dc}$  (different line colors in the plots). For this set-up, the maximum value  $\eta_{max} = 0.9845$ has been obtained at  $V_{2dc} = 15 \text{ V}$  and  $f_s = 115 \text{ kHz}$ . Figure 12b shows that the secondary coil rms current level (dashed lines) does not depend on the frequency, since it only depends on

$$f_{L} = \frac{1}{2\pi\sqrt{1-k^{2}}} \sqrt{\frac{\omega_{1}^{2} + \omega_{2}^{2}}{2}} - \sqrt{\left(\frac{\omega_{1}^{2} - \omega_{2}^{2}}{2}\right)^{2} + \omega_{1}^{2}\omega_{2}^{2}k^{2}}$$

$$f_{R} = \frac{1}{2\pi\sqrt{1-k^{2}}} \sqrt{\frac{\omega_{1}^{2} + \omega_{2}^{2}}{2}} + \sqrt{\left(\frac{\omega_{1}^{2} - \omega_{2}^{2}}{2}\right)^{2} + \omega_{1}^{2}\omega_{2}^{2}k^{2}}$$

(9)

where  $\omega_1 = 2\pi f_1 = 1/\sqrt{L_1C_1}$  and  $\omega_2 = 2\pi f_2 = 1/\sqrt{L_2C_2}$  are the primary and the secondary side angular resonant frequencies. For the capacitor set-up of Figure 12, the split frequencies are located in  $f_L = 85$  kHz and  $f_R = 153$  kHz. As will be explained in the next section, operating at the right-side split frequency  $f_R$  can be beneficial in terms of better controllability of the post-regulated IPTS, while maintaining high efficiency due to the ZVS inverter operation [31]. Finally, the blue rectangle in Figure 12d highlights a frequency region (from approximately 95 kHz to approximately 125 kHz) wherein the  $V_{2dc}$  voltage decreases as the normalized phase-shift *d* increases. This behavior could determine an instable operation region for the buck controller wherein the regulation of the buck output voltage could be lost, as will be explained hereafter. Hence, it could be impossible to exploit the maximum efficiency over such a frequency range, while operating the IPTS at higher frequencies could lead to decreased efficiency due to the increasing switching and ferrite losses.

**Figure 12.** Predictions of IPTS modeling solution (5)–(8) vs.  $f_s$  for different values of  $V_{2dc}$ , for the capacitor set-up { $C_1 = 100 \text{ nF}$ ,  $C_2 = 100 \text{ nF}$ }: (a) IPTS efficiency  $\eta$ ; (b) TX and RX coil rms currents  $I_{L1rms}$  (solid),  $I_{L2rms}$  (dashed); (c) IPTS RX-to-TX voltage gain  $V_2/V_1$ ; and (d) normalized phase-shift d.

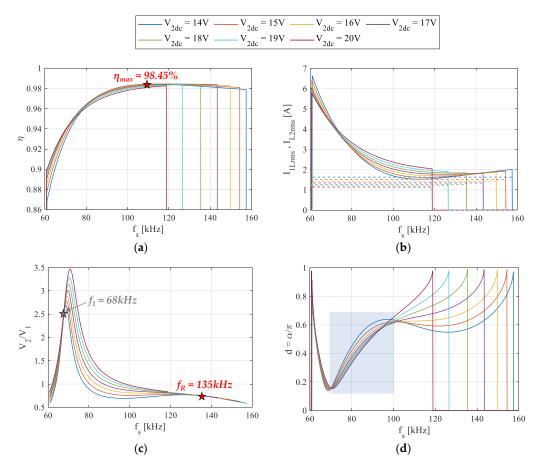

Figure 13 depicts the simulated IPTS efficiency  $\eta$  (Figure 13a), the rms currents  $I_{L1rms}$ (solid lines) and the  $I_{L2rms}$  (dashed lines) of the TX and RX coils, respectively (Figure 13b), the IPTS voltage gain  $V_2/V_1$  (Figure 13c) and the normalized phase-shift *d* (Figure 13d), for the second capacitor set-up { $C_1 = 200 \text{ nF}$ ,  $C_2 = 100 \text{ nF}$ }. Also for this configuration, the maximum value  $\eta_{max} = 0.9845$  has been obtained at  $V_{2dc} = 15$  V and  $f_s = 115$  kHz, since  $C_1$ does not influence the maximum efficiency but the feasible frequency range over which such efficiency can be obtained. The split frequencies, for which the IPTS voltage gain is independent of the load, are now located in  $f_L$  = 68 kHz and  $f_R$  = 135 kHz. Again, the blue rectangle in Figure 13d highlights a frequency region (from approximately 70 kHz to approximately 100 kHz), wherein the  $V_{2dc}$  voltage decreases as the normalized phaseshift *d* increases, over which the buck controller could lose the capability of regulating the output voltage, as explained in the following section. However, compared to the capacitor set-up of Figure 12, now such a critical frequency region is shifted to the left, thus allowing to exploit the maximum efficiency operating conditions around the  $f_s = 115$  kHz point. Hence, the optimal compensation capacitor set-up selected herein is  $\{C_1 = 200 \text{ nF},$  $C_2 = 100 \text{ nF}$ , resulting in the following values of the primary and secondary resonant frequencies  $f_1 = 74$  kHz and  $f_2 = 105$  kHz.

**Figure 13.** Predictions of IPTS modeling solution (5)–(8) vs.  $f_s$  for different values of  $V_{2dc}$ , for the capacitor set-up { $C_1 = 200 \text{ nF}$ ,  $C_2 = 100 \text{ nF}$ }: (a) IPTS efficiency  $\eta$ ; (b) TX and RX coil rms currents  $I_{L1rms}$  (solid),  $I_{L2rms}$  (dashed); (c) IPTS RX-to-TX voltage gain  $V_2/V_1$ ; and (d) normalized phase-shift d.

## 2.5. PR-IPTS Controllability Assessment

The modeling results presented in the previous section are based on the assumption that the buck converter correctly regulates its output voltage for all the analyzed conditions of the inverter switching frequency  $f_s$  and the intermediate bus voltage  $V_{2dc}$ . However, the control characteristics of a post-regulator cascaded to an IPTS are quite different from

a standalone DC/DC converter [28]. This is due to the fact that, as the post-regulator duty-cycle *D* increases, the equivalent resistance  $R_{ac}$  seen by the IPT stage decreases, and the intermediate bus voltage  $V_{2dc}$  can either increase or decrease in function of the IPTS response to the equivalent load variation. Hence, the converter output voltage  $V_{o} = V_{2dc} \cdot M(D)$  can increase or decrease with the duty-cycle, in function of the amount of  $V_{2dc}$  and M(D) variation with *D*. Under certain operating conditions, the output voltage can become non-monotonic with respect to the duty-cycle, which means that the resulting Bode diagram varies significantly with the operating point. This may lead to difficulties in closed-loop control. In this section, we solve the PR-IPTS equations with the buck converter operating in open-loop and show that the non-monotonic behavior of the output voltage with duty-cycle occurs within the operating regions highlighted with blue rectangles in Figures 12d and 13d.

Let us assume that the PR-IPTS is operating in open loop with the buck duty-cycle varying in the range D = [0.1, 0.9]. The system equation (4) is still valid, but the output voltage  $V_o$  is no more regulated at its nominal value. The equivalent AC resistance  $R_{ac}$  seen at the rectifier input changes with the duty-cycle according to (1) and (3), thus varying the IPTS operating point. Let us also assume that the inverter normalized phase-shift *d* is varied in the range d = [0.1, 1]. For each value of *d*, the primary voltage peak  $V_1$  is given by (2) and, if the phase  $\phi_{V1}$  is taken as a zero reference for the phase angles, the phasor  $\overline{V}_1 = V_1$  is known, and the equation system (4) can be solved to obtain the remaining phasors, as given in (10):

$$\overline{I}_{L1} = \frac{\left(j\omega_{s}L_{2} + \frac{1}{j\omega_{s}C_{2}} + R_{2} + R_{ac}\right)}{\left(j\omega_{s}L_{1} + \frac{1}{j\omega_{s}C_{1}} + R_{1}\right)\left(j\omega_{s}L_{2} + \frac{1}{j\omega_{s}C_{2}} + R_{2} + R_{ac}\right) + \omega_{s}^{2}M^{2}}\overline{V}_{1}} \overline{I}_{L2} = -\frac{j\omega M}{\left(j\omega_{s}L_{1} + \frac{1}{j\omega_{s}C_{1}} + R_{1}\right)\left(j\omega_{s}L_{2} + \frac{1}{j\omega_{s}C_{2}} + R_{2} + R_{ac}\right) + \omega_{s}^{2}M^{2}}}{\frac{j\omega MR_{ac}}{V_{2}}}\overline{V}_{1}} \tag{10}$$

$$\overline{V}_{2} = \frac{j\omega_{s}}{\left(j\omega_{s}L_{1} + \frac{1}{j\omega_{s}C_{1}} + R_{1}\right)\left(j\omega_{s}L_{2} + \frac{1}{j\omega_{s}C_{2}} + R_{2} + R_{ac}\right) + \omega_{s}^{2}M^{2}}}{\left(j\omega_{s}L_{1} + \frac{1}{j\omega_{s}C_{1}} + R_{1}\right)\left(j\omega_{s}L_{2} + \frac{1}{j\omega_{s}C_{2}} + R_{2} + R_{ac}\right) + \omega_{s}^{2}M^{2}}\overline{V}_{1}}$$

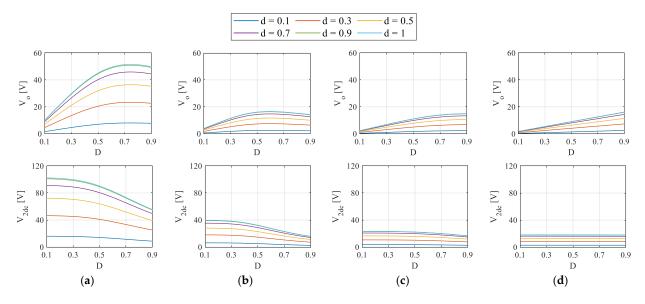

Starting from the result of (10), the voltage  $V_{2dc}$  can be estimated by inverting (5), and the resulting output voltage can be obtained for each analyzed value of *D* as  $V_o = V_{2dc} \cdot D$ . Figure 14 shows the values of  $V_o$  and  $V_{2dc}$  for the capacitor set-up { $C_1 = 200 \text{ nF}$ ,  $C_2 = 100 \text{ nF}$ }, obtained over the given ranges of D and d for  $f_s$  values in the interval [70, 135] kHz. It can be observed that at  $f_s = 70$  kHz (Figure 14a),  $V_o$  is non-monotonic with respect to D, while  $V_{2dc}$  reaches very high levels for low duty-cycle values (high  $R_{ac}$ ). Such a condition could result in an unstable controller behavior within the positive feedback region located at the right-hand-side of the  $V_o$  vs. D curve peak. In this region, an increase in D would result in a decrease in  $V_{o}$ , and the controller would try to further increase D until saturating its value at the maximum allowed limit. Hence, the output voltage regulation would be lost. Similarly, a decrease in D would cause an increase in  $V_o$ , and the controller would try to further decrease the duty-cycle, until reaching the  $V_0$  vs. D curve peak and going to the negative feedback region. In principle, in such a region the controller could be able to guarantee the output voltage regulation, but  $V_{2dc}$  may increase to very high levels, causing possible component failures (such as capacitors, buck converter MOSFETs and relative gate drivers, etc.). Hence, the system operation under conditions resulting in a non-monotonic control-to-output characteristic should be avoided. At  $f_s = 90$  kHz (Figure 14b),  $V_o$  is still non-monotonic with respect to D but  $V_{2dc}$  assumes lower values, while at  $f_s = 110$  kHz (Figure 14c),  $V_0$  becomes monotonic resulting in a correct controller behavior. These findings are in agreement with the results of Figure 13d, where the IPTS operation in the range [70, 100] kHz is not recommended because of the inversion of the  $V_{2dc}$  vs. d trend. Eventually, the plots of Figure 14d depict  $V_o$  and  $V_{2dc}$  for  $f_s = 135$  kHz (corresponding to the right-hand-side split frequency  $f_R$ ), highlighting that  $V_{2dc}$  (and consequently, the IPTS gain  $V_2/V_1$ ) is independent of the duty-cycle D (or, equivalently, of  $R_{ac}$ ), which is in agreement with the results of Figure 13c. Hence, operating IPTS at  $f_R$  can be convenient if the load variations occur, but the overall system efficiency may decrease somewhat (as can be seen

15 of 35

in Figure 13a). To maximize the efficiency, IPTS should be operated at  $f_s = 115$  kHz, which is still a feasible condition located in the stable frequency region, as previously shown in Figure 13d.

**Figure 14.** PR-IPTS output voltage  $V_o$  (top) and intermediate bus voltage  $V_{2dc}$  (bottom) vs. buck duty-cycle *D* for different values of normalized phase-shift *d* at: (**a**)  $f_s = 70$  kHz; (**b**)  $f_s = 90$  kHz; (**c**)  $f_s = 110$  kHz; and (**d**)  $f_s = 135$  kHz.

## 3. Dynamic Modeling and Control of PR-IPTS

In this section, we describe the dynamic modeling of the PR-IPTS based on CMT, similarly to the research developed in [27]. In contrast to the findings of [27], which are valid for a full square-wave inverter operation under resonance conditions, we propose the modified modeling including the inverter phase-shift modulation which is valid for whatever switching frequency. As one of the modeling outputs, we obtained the duty-to-output transfer function of the post-regulator, necessary for the design of the digital controller as discussed hereafter.

## 3.1. Dynamic Modeling of IPT Stage

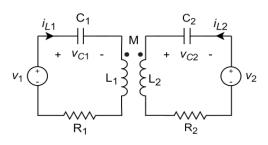

Figure 15 shows the AC equivalent circuit of the IPT stage of Figure 9, where  $v_1$  and  $v_2$  are considered to be the exciting source and sink, respectively. The dynamics of such an equivalent circuit can be described by the equation system (11):

$$\begin{cases}

L_{1}\frac{di_{L1}}{dt} + M\frac{di_{L2}}{dt} + R_{1}i_{L1} + v_{C1} = v_{1} \\

L_{2}\frac{di_{L2}}{dt} + M\frac{di_{L1}}{dt} + R_{2}i_{L2} + v_{C2} = v_{2} \\

C_{1}\frac{dv_{C1}}{dt} = i_{L1} \\

C_{2}\frac{dv_{C2}}{dt} = i_{L2}

\end{cases}$$

(11)

Figure 15. AC equivalent circuit of the IPT stage.

As a result of the phase-shift modulation (see Figure 10), the inverter output voltage  $v_1(t)$  can be described by (12):

$$v_1(t) = \begin{cases} v_{in}, & -\frac{\alpha}{2} \le \omega_s t < \frac{\alpha}{2} \\ 0, & \frac{\alpha}{2} \le \omega_s t < \pi - \frac{\alpha}{2} \\ -v_{in}, & \pi - \frac{\alpha}{2} \le \omega_s t < \pi + \frac{\alpha}{2} \end{cases}$$

(12)

The rectifier input voltage  $v_2(t)$  is determined by the secondary coil current direction:

$$v_2(t) = -sgn(i_{L2}(t))v_{2dc}$$

(13)

According to the CMT, the IPT coil currents  $i_{Ln}(t)$  and the compensation capacitor voltages  $v_{Cn}(t)$  (n = 1, 2) can be represented as given in (14):

$$\begin{cases} i_{Ln}(t) = \sqrt{\frac{2}{L_n}} a_n \cos(\omega_s t + \theta_n) & (14a) \\ v_{Cn}(t) = \frac{1}{\omega_s C_n} \sqrt{\frac{2}{L_n}} a_n \sin(\omega_s t + \theta_n) & (14b) \end{cases}$$

where  $a_n$  and  $\theta_n$  are the amplitudes and phases of the coupled modes representing the state of the primary and secondary resonators. Such variables are assumed to vary slowly with time. Let us note that (14b) has been modified compared to the formulation given in [27], so as to extend its validity to whatever operating frequency. Using (14), the derivatives of the resonant voltages and currents become:

$$\begin{cases} \frac{di_{Ln}}{dt} = \sqrt{\frac{2}{L_n}} \left[ \frac{da_n}{dt} \cos(\omega_s t + \theta_n) - a_n \left( \omega_s + \frac{d\theta_n}{dt} \right) \sin(\omega_s t + \theta_n) \right] \\ \frac{dv_{Cn}}{dt} = \sqrt{\frac{2}{C_n}} \left[ \frac{da_n}{dt} \sin(\omega_s t + \theta_n) + a_n \left( \omega_s + \frac{d\theta_n}{dt} \right) \cos(\omega_s t + \theta_n) \right] \end{cases}$$

(15)

By substituting (15) into (11), it is possible to derive the dynamic equations of the amplitudes and phases of the coupled modes:

$$\frac{da_{1}}{dt} = \omega_{1}a_{1}sin(\omega_{s}t + \theta_{1})cos(\omega_{s}t + \theta_{1}) + \\

+ \frac{\sqrt{L_{1}/2}}{(L_{1}L_{2} - M^{2})}cos(\omega_{s}t + \theta_{1}) \left[ -\frac{L_{2}}{\omega_{s}C_{1}}\sqrt{\frac{2}{L_{1}}}a_{1}sin(\omega_{s}t + \theta_{1}) + \\

- L_{2}R_{1}\sqrt{\frac{2}{L_{1}}}a_{1}cos(\omega_{s}t + \theta_{1}) + L_{2}v_{1}(t) - Mv_{2}(t) + \\

+ MR_{2}\sqrt{\frac{2}{L_{2}}}a_{2}cos(\omega_{s}t + \theta_{2}) + \frac{M}{\omega_{s}C_{2}}\sqrt{\frac{2}{L_{2}}}a_{2}sin(\omega_{s}t + \theta_{2}) \right]$$

(16a)

$$\frac{d\theta_{1}}{dt} = -\omega_{s} + \omega_{1} - \omega_{1} \sin^{2}(\omega_{s}t + \theta_{1}) + \\

-\frac{\sqrt{L_{1}/2}}{(L_{1}L_{2} - M^{2})} \frac{\sin(\omega_{s}t + \theta_{1})}{a_{1}} \left[ -\frac{L_{2}}{\omega_{s}C_{1}} \sqrt{\frac{2}{L_{1}}} a_{1} \sin(\omega_{s}t + \theta_{1}) + \\

-L_{2}R_{1} \sqrt{\frac{2}{L_{1}}} a_{1} \cos(\omega_{s}t + \theta_{1}) + L_{2}v_{1}(t) - Mv_{2}(t) + \\

+MR_{2} \sqrt{\frac{2}{L_{2}}} a_{2} \cos(\omega_{s}t + \theta_{2}) + \frac{M}{\omega_{s}C_{2}} \sqrt{\frac{2}{L_{2}}} a_{2} \sin(\omega_{s}t + \theta_{2}) \right]$$

(16b)

$$\frac{aa_{2}}{dt} = \omega_{2}a_{2}sin(\omega_{s}t + \theta_{2})cos(\omega_{s}t + \theta_{2}) + \\ + \frac{\sqrt{L_{2}/2}}{(L_{1}L_{2} - M^{2})}cos(\omega_{s}t + \theta_{2}) \left[ -\frac{L_{1}}{\omega_{s}C_{2}}\sqrt{\frac{2}{L_{2}}}a_{2}sin(\omega_{s}t + \theta_{2}) + \\ + L_{1}v_{2}(t) - Mv_{1}(t) + \\ + MR_{1}\sqrt{\frac{2}{L_{1}}}a_{1}cos(\omega_{s}t + \theta_{1}) + \frac{M}{\omega_{s}C_{1}}\sqrt{\frac{2}{L_{1}}}a_{1}sin(\omega_{s}t + \theta_{1}) \right]$$

(16c)

$$\frac{d\theta_2}{dt} = -\omega_s + \omega_2 - \omega_2 \sin^2(\omega_s t + \theta_2) + \\

-\frac{\sqrt{L_2/2}}{(L_1 L_2 - M^2)} \frac{\sin(\omega_s t + \theta_2)}{a_2} \left[ -\frac{L_1}{\omega_s C_2} \sqrt{\frac{2}{L_2}} a_2 sin(\omega_s t + \theta_2) + \\

-L_1 R_2 \sqrt{\frac{2}{L_2}} a_2 cos(\omega_s t + \theta_2) + L_1 v_2(t) - M v_1(t) + \\

+ M R_1 \sqrt{\frac{2}{L_1}} a_1 cos(\omega_s t + \theta_1) + \frac{M}{\omega_s C_1} \sqrt{\frac{2}{L_1}} a_1 sin(\omega_s t + \theta_1) \right]$$

(16d)

Note that (12) and (13) should be used in (16) to describe  $v_1(t)$  and  $v_2(t)$ , respectively. Assuming that the slowly varying variables in (16)— $a_n$  and  $\theta_n$  (n = 1, 2)—are constant during a buck switching period  $T_{Buck} = 1/f_{Buck}$ , the time-invariant averaged model can be obtained by taking the average values of both sides of (16) over  $T_{Buck}$ :

$$\left\langle \frac{da_1}{dt} \right\rangle = \frac{\sqrt{L_1/2}}{(L_1L_2 - M^2)} \left[ -\frac{L_2R_1}{\sqrt{2L_1}} a_1 - \frac{M}{\omega_s C_2 \sqrt{2L_2}} a_2 sin(\theta_1 - \theta_2) + \frac{MR_2}{\sqrt{2L_2}} a_2 cos(\theta_1 - \theta_2) + \frac{2L_2 v_{in}}{\pi} cos(\theta_1) sin(\frac{\alpha}{2}) + \frac{2M}{\pi} v_{2dc} cos(\theta_1 - \theta_2) \right]$$

(17a)

$$\left\langle \frac{d\theta_1}{dt} \right\rangle = -\omega_s + \frac{\omega_1}{2} - \frac{\sqrt{L_1/2}}{(L_1L_2 - M^2)a_1} \left[ -\frac{L_2}{\omega_s C_1 \sqrt{2L_1}} a_1 + \frac{M}{\omega_s C_2 \sqrt{2L_2}} a_2 \cos(\theta_1 - \theta_2) + \frac{MR_2}{\sqrt{2L_2}} a_2 \sin(\theta_1 - \theta_2) + \frac{2L_2 v_{in}}{\pi} \sin(\theta_1) \sin(\frac{\alpha}{2}) + \frac{2M}{\pi} v_{2dc} \sin(\theta_1 - \theta_2) \right]$$

(17b)

$$\left\langle \frac{da_2}{dt} \right\rangle = \frac{\sqrt{L_2/2}}{(L_1L_2 - M^2)} \left[ -\frac{L_1R_2}{\sqrt{2L_2}} a_2 + \frac{M}{\omega_s C_1 \sqrt{2L_1}} a_1 \sin(\theta_1 - \theta_2) + \frac{MR_1}{\sqrt{2L_1}} a_1 \cos(\theta_1 - \theta_2) - \frac{2L_1 v_{2dc}}{\pi} - \frac{2M v_{in}}{\pi} \cos(\theta_2) \sin\left(\frac{\alpha}{2}\right) \right]$$

(17c)

$$\left\langle \frac{d\theta_2}{dt} \right\rangle = -\omega_s + \frac{\omega_2}{2} - \frac{\sqrt{L_2/2}}{(L_1 L_2 - M^2)a_2} \left[ -\frac{L_1}{\omega_s C_2 \sqrt{2L_2}} a_2 + \frac{M}{\omega_s C_1 \sqrt{2L_1}} a_1 \cos(\theta_1 - \theta_2) + \frac{MR_1}{\sqrt{2L_1}} a_1 \sin(\theta_1 - \theta_2) - \frac{2Mv_{in}}{\pi} \sin(\theta_2) \sin(\frac{\alpha}{2}) \right]$$

(17d)

while the " $\langle \cdot \rangle$ " operator denotes the averaged values of the relevant quantities over  $T_{Buck}$ . The averaged model (17) can be represented in a more compact form (18):

$$\frac{d\mathbf{x}}{dt} = f(x, v_{in}, v_{2dc}) \tag{18}$$

where:

$$\mathbf{x} = \begin{bmatrix} a_1 & \theta_1 & a_2 & \theta_2 \end{bmatrix}^T, \quad \mathbf{f} = \begin{bmatrix} f_1 & f_2 & f_3 & f_4 \end{bmatrix}^T$$

(19)

and  $f_n$  (n = 1, ..., 4) is the right-hand-side expression of the *n*-th equation in (17). The averaged value over  $T_{Buck}$  of the current at the diode bridge output is given by (20):

$$\langle i_2 \rangle = g_2(\mathbf{x}) = -\frac{1}{\pi} \sqrt{\frac{2}{L_2}} a_2$$

(20)

Denoting the small-signal variations of the state variables and of the IPT input and output voltages as  $\hat{a}_n$ ,  $\hat{\theta}_n$  and  $\hat{v}_n$  (n = 1, 2), the linearized small-signal model of the IPT stage can be described by (21):

$$\frac{d\hat{\mathbf{x}}}{dt} = \mathbf{F}_{\mathbf{x}}\hat{\mathbf{x}} + \begin{bmatrix} \frac{\partial f}{\partial v_{in}} & \frac{\partial f}{\partial v_{2dc}} \end{bmatrix} \begin{bmatrix} \hat{v}_{in} \\ \hat{v}_{2dc} \end{bmatrix}$$

(21)

where:

$$\hat{\mathbf{x}} = \begin{bmatrix} \hat{a}_{1} \\ \hat{\theta}_{1} \\ \hat{a}_{2} \\ \hat{\theta}_{2} \end{bmatrix}, \ \mathbf{F}_{\mathbf{x}} = \begin{bmatrix} \frac{\partial f_{1}}{\partial a_{1}} & \frac{\partial f_{1}}{\partial \theta_{1}} & \frac{\partial f_{1}}{\partial a_{2}} & \frac{\partial f_{1}}{\partial \theta_{2}} \\ \frac{\partial f_{2}}{\partial a_{1}} & \frac{\partial f_{2}}{\partial \theta_{1}} & \frac{\partial f_{2}}{\partial a_{2}} & \frac{\partial f_{2}}{\partial \theta_{2}} \\ \frac{\partial f_{3}}{\partial a_{1}} & \frac{\partial f_{3}}{\partial \theta_{1}} & \frac{\partial f_{3}}{\partial a_{2}} & \frac{\partial f_{3}}{\partial \theta_{2}} \\ \frac{\partial f_{4}}{\partial a_{1}} & \frac{\partial f_{4}}{\partial \theta_{1}} & \frac{\partial f_{4}}{\partial a_{2}} & \frac{\partial f_{4}}{\partial \theta_{2}} \end{bmatrix}$$

(22)

According to (20), the small signal variation of the IPT stage output current is:

$$\hat{i}_2 = \nabla g_2 \hat{x}, \quad \nabla g_2 = \begin{bmatrix} \frac{\partial g_2}{\partial a_1} & \frac{\partial g_2}{\partial \theta_1} & \frac{\partial g_2}{\partial a_2} & \frac{\partial g_2}{\partial \theta_2} \end{bmatrix}$$

(23)

## 3.2. Small-Signal Modeling of PR-IPTS

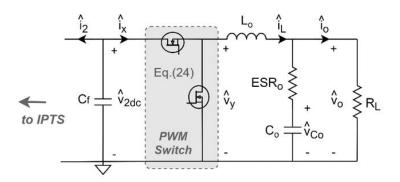

Using the IPTS dynamic model presented thus far, it is possible to develop a systemlevel PR-IPTS model by combining Equations (18)–(23) with the differential equations of the post-regulator. Figure 16 depicts an averaged small-signal equivalent circuit of the buck converter, where the PWM switching cell is replaced with an equivalent two-port AC model described by (24):

$$\hat{i}_x = D \cdot \hat{i}_L + I_L \cdot \hat{d} \tag{24a}$$

$$\hat{v}_y = D \cdot \hat{v}_{2dc} + V_{2dc} \cdot \hat{d} \tag{24b}$$

Figure 16. Averaged small-signal equivalent circuit of the buck converter.

The "^" operator in (24) denotes the small-signal variations of the considered quantities (note that the duty-cycle variation  $\hat{d}$  is different from the normalized phase-shift d used previously).

The small-signal variation of the buck output voltage can be described by (25):

$$\hat{v}_o = ESR_o \left( \hat{i}_L - \frac{\hat{v}_o}{R_L} \right) + \hat{v}_{Co}$$

<sup>(25)</sup>

which yields (26):

$$\hat{v}_o = \frac{R_L E S R_o}{R_L + E S R_o} \hat{i}_L + \frac{R_L}{R_L + E S R_o} \hat{v}_{Co}$$

(26)

Using (23) and (24a), the dynamic equation of the intermediate bus capacitor  $C_f$  can be expressed as given in (27):

$$\frac{d\hat{v}_{2dc}}{dt} = -\frac{1}{C_f} (\hat{i}_2 + \hat{i}_x) = -\frac{\nabla g_2}{C_f} \hat{x} - \frac{D}{C_f} \hat{i}_L - \frac{I_L}{C_f} \hat{d}$$

(27)

Using (26), the dynamic equation of the buck output capacitor  $C_o$  can be expressed as given in (28):

$$\frac{d\hat{\sigma}_{Co}}{dt} = \frac{1}{C_o} \left( \hat{i}_L - \frac{\hat{\sigma}_o}{R_L} \right) = \frac{R_L}{(R_L + ESR_o)C_o} \hat{i}_L - \frac{1}{(R_L + ESR_o)C_o} \hat{\sigma}_{Co}$$

(28)

Using (24b) and (27), the dynamic equation of the buck inductor  $L_0$  can be obtained:

$$\frac{d\hat{i}_L}{dt} = \frac{1}{L_o} \left( \hat{v}_y - \hat{v}_o \right) = \frac{D}{L_o} \hat{v}_{2dc} + \frac{V_{2dc}}{L_o} \hat{d} - \frac{R_L ESR_o}{(R_L + ESR_o)L_o} \hat{i}_L - \frac{R_L}{(R_L + ESR_o)L_o} \hat{v}_{Co}$$

(29)

By combining the IPTS dynamic model (21) with Equations (26)–(29), the seventh-order small-signal model of the PR-IPTS is developed:

$$\frac{d}{dt} \underbrace{ \begin{bmatrix} \hat{\mathbf{x}} \\ \hat{\vartheta}_{2dc} \\ \hat{i}_{L} \\ \hat{\vartheta}_{Co} \end{bmatrix}}_{\hat{\mathbf{x}}} \underbrace{ \begin{bmatrix} F_{\mathbf{x}} & \frac{\partial f}{\partial v_{2dc}} & \mathbf{0} & \mathbf{0} \\ -\frac{\nabla g_{2}}{C_{f}} & 0 & -\frac{D}{C_{f}} & 0 \\ \mathbf{0} & \frac{D}{L} & k_{1} & k_{2} \\ \mathbf{0} & 0 & k_{3} & k_{4} \end{bmatrix} \begin{bmatrix} \hat{\mathbf{x}} \\ \hat{\vartheta}_{2dc} \\ \hat{i}_{L} \\ \hat{\vartheta}_{Co} \end{bmatrix}} + \underbrace{ \begin{bmatrix} \mathbf{0} \\ -\frac{I_{L}}{C_{f}} \\ \frac{V_{2dc}}{L} \\ 0 \end{bmatrix}}_{\mathbf{B}} \hat{d}$$

$$\hat{\vartheta}_{o} = \underbrace{ \begin{bmatrix} \mathbf{0} & 0 & k_{5} & k_{6} \end{bmatrix}}_{C} \begin{bmatrix} \hat{\mathbf{x}} \\ \hat{\vartheta}_{2dc} \\ \hat{\vartheta}_{Co} \end{bmatrix}}$$

$$(30)$$

where:

$$k_{1} = -\frac{R_{L}ESR_{o}}{(R_{L} + ESR_{o})L_{o}}, \quad k_{2} = -\frac{R_{L}}{(R_{L} + ESR_{o})L_{o}}, \quad k_{3} = \frac{R_{L}}{(R_{L} + ESR_{o})C_{o}}, \\ k_{4} = -\frac{1}{(R_{L} + ESR_{o})C_{o}}, \quad k_{5} = \frac{R_{L}ESR_{o}}{R_{L} + ESR_{o}}, \quad k_{6} = \frac{R_{L}}{R_{L} + ESR_{o}}$$

(31)

Note that in (30), the IPTS input voltage is considered constant with time ( $\hat{v}_{in} = 0$ ). From (30), the state-space solution of the system can be obtained as

$$\hat{\boldsymbol{X}} = (\boldsymbol{s}\boldsymbol{I} - \boldsymbol{A})^{-1}\boldsymbol{B}\hat{\boldsymbol{d}}$$

(32a)

$$\hat{v}_o = \boldsymbol{C}(s\boldsymbol{I} - \boldsymbol{A})^{-1}\boldsymbol{B}\hat{d}$$

(32b)

The steady-state operating point of the IPT stage, needed to evaluate (32), can be obtained from the FHA modeling solution (6) presented in the previous section, according to (33):

$$a_1 = I_{L1}\sqrt{\frac{L_1}{2}}, \quad a_2 = I_{L2}\sqrt{\frac{L_2}{2}}, \quad \theta_1 = \phi_{IL1} - \phi_{V1}, \quad \theta_2 = \phi_{IL2} - \phi_{V1}$$

(33)

where  $I_{L1}$ ,  $I_{L2}$ ,  $\phi_{IL1}$  and  $\phi_{IL2}$  are the amplitudes and phases of the primary and secondary current phasors  $\overline{I}_{L1}$  and  $\overline{I}_{L2}$  in (6). Let us note that, to evaluate the phase angles  $\theta_1$  and  $\theta_2$ , all the phase angles obtained from (6) should be decremented by  $\phi_{V1}$  (i.e., the phase of the primary voltage phasor  $\overline{V}_1$ ), since in the CMT formulation such  $\phi_{V1}$  term is considered null. Equation (32b) allows to evaluate the duty-to-output transfer function of the buck converter connected to the IPTS:

$$G_{vd}(s) = \frac{\hat{v}_o}{\hat{d}} = \boldsymbol{C}(s\boldsymbol{I} - \boldsymbol{A})^{-1}\boldsymbol{B}$$

(34)

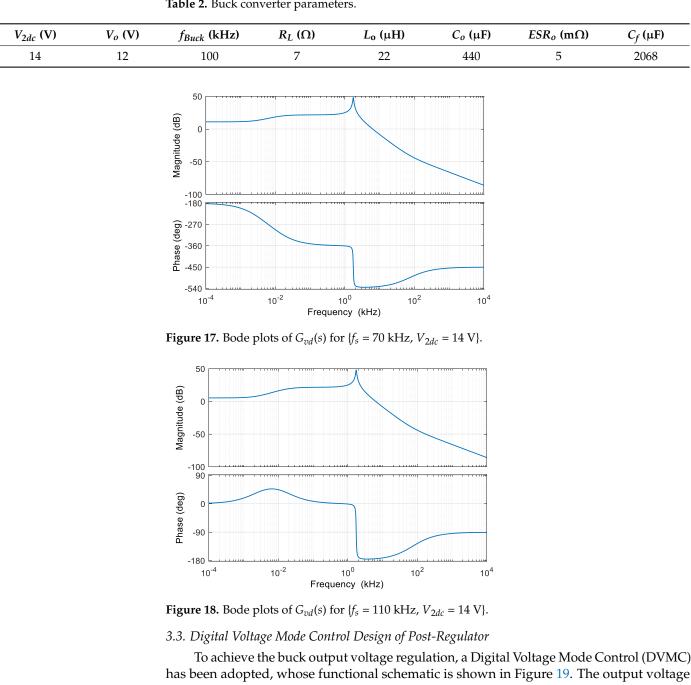

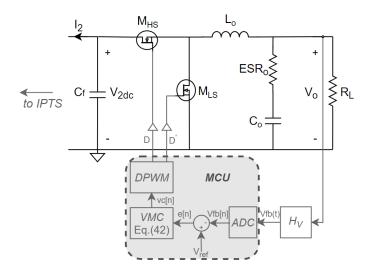

As previously discussed, under certain operating conditions, the buck output voltage can become non-monotonic with respect to the duty-cycle, leading to difficulties in the closed-loop control. Figure 17 depicts the Bode plot of  $G_{vd}(s)$  for the operating point  $\{f_s = 70 \text{ kHz}, V_{2dc} = 14 \text{ V}\}$  located in the unstable region highlighted in Figure 13d, for the buck parameters listed in Table 2. Indeed, the resulting phase of  $G_{vd}(s)$  is close to  $-180^{\circ}$  at low frequencies, because of the negative static gain  $G_{vd0}$ . This means that the increase in the duty-cycle will lead to the decrease in the output voltage, which is in agreement with the plot of Figure 14a highlighting a non-monotonic  $V_o$  vs. D static characteristic. Figure 18 depicts the Bode plot of  $G_{vd}(s)$  for the operating point  $\{f_s = 110 \text{ kHz}, V_{2dc} = 14 \text{ V}\}$  located in the stable region of Figure 13d. Under such conditions, the static gain  $G_{vd0}$  is positive, and the  $V_o$  vs. D static characteristic is monotonic (see Figure 14c). Hence, this last operating point is feasible for the practical controller design discussed hereafter.

Table 2. Buck converter parameters.

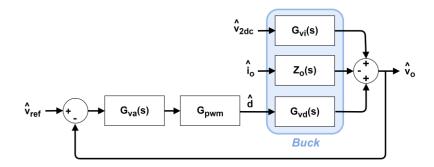

has been adopted, whose functional schematic is shown in Figure 19. The output voltage  $v_o(t)$  is scaled down by means of the resistive sensor  $H_V$  and sampled by the ADC, yielding the feedback voltage  $v_{fb}[n]$  in the *n*-th sampling instant. Such a voltage value is then compared with the digital reference  $V_{ref}$  and the resulting error e[n] is sent to the digital controller which calculates the desired control voltage value  $v_c[n]$ . The output of the controller is delivered to the Digital Pulse Width Modulator (DPWM) which generates the two complementary driving signals for the buck converter MOSFETs.

To properly design the DVMC, the analog version of the controller has been first developed and subsequently transformed into its digital version. The block diagram representation of the analog VMC is shown in Figure 20, which utilizes a single feedback loop to regulate the output voltage at the desired reference value. The blue box represents the dynamic model of the buck converter including its main transfer functions. The controlto-output transfer function  $G_{vd}(s)$  is provided in (34), while the transfer functions  $G_{vi}(s)$ and  $Z_o(s)$  can be obtained through the same modeling procedure. The block  $G_{pwm} = 1/V_{pp}$

represents the PWM gain, where  $V_{pp}$  is the peak-to-peak amplitude of the PWM sawtooth signal (herein,  $V_{pp} = 1$  V has been used).

The analog controller  $G_{va}(s)$  has been designed by the K-factor method [32], to obtain a given phase margin of the compensated loop transfer function  $T_c(s) = G_{va}(s) \cdot G_{pwm} \cdot G_{vd}(s)$ at the desired crossover frequency, ensuring the closed-loop system stability.

Figure 19. DVMC of the buck converter.

Figure 20. Analog VMC block diagram.

Referring to the duty-to-output transfer function of Figure 18, a crossover frequency of  $f_{Buck}/20 = 5$  kHz and a phase margin of 52° have been set, yielding the third-order controller (35) whose coefficients are listed in Table 3:

$$G_{va}(s) = \frac{\omega_{p1}}{s} \frac{(1 + s/\omega_{z1})^2}{(1 + s/\omega_{v2})^2}$$

(35)

Table 3. Analog controller coefficients.

| $\omega_{z1}$ (rad/s) | $\omega_{p1}$ (rad/s) | $\omega_{p2}$ (rad/s) |

|-----------------------|-----------------------|-----------------------|

| $5.99 	imes 10^3$     | 683.86                | $1.65	imes 10^5$      |

To obtain the digital version of such a controller, the Tustin transform (36) has been adopted:

$$s = 2f_{samp} \frac{(1 - z^{-1})}{(1 + z^{-1})}$$

(36)

where the sampling frequency  $f_{samp}$  has been set equal to the buck switching frequency  $f_{Buck}$ , so as to synchronize the sampling process with respect to the switching of the converter.

Substituting (36) into (35) provides the digital controller transfer function  $G_{va}(z)$  given in (37), whose coefficients are listed in Table 4:

$$G_{va}(z) = K_p \frac{b_0 + b_1 z^{-1} + b_2 z^{-2} + b_3 z^{-3}}{1 - a_1 z^{-1} - a_2 z^{-2} - a_3 z^{-3}}$$

(37)

where  $K_p$  is a scaling factor allowing to adapt the ADC resolution  $res_{ADC}$  to the DPWM resolution  $res_{DPWM}$  [33]:

$$K_p = \frac{res_{ADC}}{H_V} \frac{1}{res_{DPWM}}$$

(38)

Table 4. Digital controller coefficients.

| $a_1$          | <i>a</i> <sub>2</sub> | $a_3$           |                |

|----------------|-----------------------|-----------------|----------------|

| 1.193312123257 | -0.202654517506       | 0.009342394250  |                |

| $b_0$          | $b_1$                 | $b_2$           | $b_3$          |

| 0.824716092259 | -0.728775227352       | -0.821925844304 | 0.731565475307 |

The ADC resolution is determined by the ADC full-scale value  $V_{FS}$  and by the number of bits used for the quantization  $N_{bit}$ :

$$res_{ADC} = \frac{V_{FS}}{2^{N_{bit}} - 1}$$

(39)

The DPWM resolution is determined by the number of discrete DPWM levels *N*<sub>DPWM</sub>:

$$res_{DPWM} = \frac{1}{N_{DPWM}} \tag{40}$$

where  $N_{DPWM}$  is determined by a fixed time resolution  $t_{res}$  of the DPWM peripheral and by the desired buck switching frequency  $f_{Buck}$  according to (41):

$$N_{DPWM} = \frac{1}{f_{Buck} t_{res}} - 1 \tag{41}$$

where an edge-aligned mode of the DPWM peripheral has been adopted, which allows realizing a desired PWM period by counting from zero up to the  $N_{DPWM}$  level and then starting a new period.

Applying the inverse Z-transform to (37) yields the digital control law (42):

$$v_{c}[n] = a_{1}v_{c}[n-1] + a_{2}v_{c}[n-2] + a_{3}v_{c}[n-3] + K_{p}b_{0}e[n] + K_{p}b_{1}e[n-1] + K_{p}b_{2}e[n-2] + K_{p}b_{3}e[n-3]$$

(42)

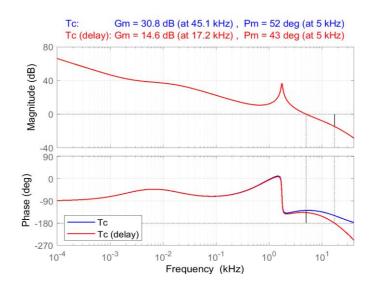

Due to the sampling process, the sampled output voltage shows an additive delay, equal to half the sampling period, as compared to the original signal, which may lead to the phase margin erosion of the compensated loop gain  $T_c(s)$  that can affect the system stability. Figure 21 shows the impact of the sampling delay on the Bode plots of  $T_c(s)$ , highlighting that the desired phase margin  $Pm = 52^\circ$  of  $T_c(s)$  (blue curves) is decreased to  $Pm = 43^\circ$  in the delayed version of  $T_c(s)$  (red curves). Nevertheless, the closed-loop system stability is still ensured with the acceptable values of both gain and phase margins.

Eventually, the absence of the limit cycle phenomenon has been verified for the proposed DPWM scheme. Limit cycles refer to the steady-state oscillations of  $v_o(t)$  and other system variables at frequencies lower than the converter switching frequency, which may result from the presence of signal amplitude quantizers such as the ADC and DPWM modules in the feedback loop [34]. Referring to Figure 19, for a given duty-to-output DC gain  $G_{vd0}$ , the duty-to-feedback voltage DC gain is  $G_{vd0}$   $H_V$ . To prevent limit cycles, the change of the feedback voltage  $\Delta V_{fb}(t)$  determined by the minimum duty-cycle change

$\Delta D_{min}$  (corresponding to the DPWM resolution  $res_{DPWM}$ ) has to be smaller than ADC resolution  $res_{ADC}$ :

$$\Delta D_{min}G_{vd0}H_V < res_{ADC} \tag{43}$$

The static gain  $G_{vd0}$  has been estimated by substituting s = 0 in (34). For the presented controller design, the aforementioned parameter values are listed in Table 5. Substituting such values into (43), the absence of the limit cycle has been ascertained. It is worth mentioning that the presence of the IPTS connected to the buck input has caused the static gain reduction as compared to the stand-alone buck regulator for which  $G_{vd0}$  is equal to the converter input voltage (herein  $V_{in} = 14$  V). This helped prevent the limit cycle onset which otherwise could occur in the digitally controlled buck converter.

Table 5. Digital control loop parameters used in Equations (38)-(41).

| $G_{vd0}$ | $H_V$  | $V_{FS}$ (V) | $N_{bit}$ | res <sub>ADC</sub> (V) | N <sub>DPWM</sub> | t <sub>res</sub> (ps) | <i>res<sub>DPWM</sub></i> | $K_P$  |

|-----------|--------|--------------|-----------|------------------------|-------------------|-----------------------|---------------------------|--------|

| 1.8474    | 0.1522 | 3.3          | 12        | $8.059 	imes 10^{-4}$  | 204,800           | 48.828                | $4.883 	imes 10^{-6}$     | 1084.1 |

**Figure 21.** Bode plots of the compensated loop gain  $T_c(s)$  including the sampling delay effect.

## 4. Experimental Prototype

## 4.1. IPT Coil Realization

To optimize the overall system performances while maintaining the limited coupling area, custom IPT coils have been herein realized by adopting ferrite pot cores and suitable litz-wires. These latter allow to reduce high-frequency skin and proximity effects in the windings, which could lead to an increase in the resulting AC resistance and power losses [35]. In particular, the Ferroxcube P36/22–3C91 pot cores made of 3C91 ferrite material have been adopted [36] and are depicted in Figure 22a. To realize the windings, litz-wire 170/40 has been used, which is composed of 170 strands of AWG #40 wire, recommended for the operating frequency range [100, 200] kHz. At 200 kHz, the resulting skin depth  $\delta_{skin}$  in the copper wire is higher than the litz-wire diameter  $d_{AWG#40}$ , thus allowing to reduce the skin effect:

$$\delta_{skin} = \sqrt{\frac{\rho_{Cu}}{\pi \mu_{Cu} f_s}} = 0.146 \text{ mm} > d_{AWG\#40} = 0.08 \text{ mm}$$

(44)

where  $\rho_{Cu} = 1.68 \times 10^{-8} \ \Omega \cdot m$  and  $\mu_{Cu} = 1.256629 \times 10^{-6}$  are the copper resistivity and magnetic permeability, respectively. The number of strands ( $N_{str} = 170$ ) allows for the rms current handling capability of the litz-wire given by (45):

$$I_{rms} = N_{str} \left(\frac{\pi d_{AWG\#40}^2}{4}\right) J_{rms} = 5.13 \text{ A}$$

(45)

where  $J_{rms} = 6 \text{ A/mm}^2$  represents the maximum allowable rms current density of the copper wire. Thus, the resulting  $I_{rms}$  is sufficiently higher than the expected rms current levels in the coils depicted in Figure 13b (see the feasible frequency range from approximately 100 kHz to approximately 150 kHz).

**Figure 22.** Custom IPT coils realized with Ferroxcube P36/22–3C91 pot cores and litz-wire 170/40: (a) P36/22–3C91 cores; (b) single custom coil; and (c) TX and RX coil set with 3 mm air-gap.

Fifteen turns of the litz-wire 170/40 have been realized on each pot core, and the resulting self-inductances  $L_1$ ,  $L_2$  and the DC winding resistances  $R_{L1}$ ,  $R_{L2}$  have been measured by means of the Extech Instruments LCR200 Passive Component LCR Meter [37]. Such measurement data are listed in Table 6, together with the coupling coefficient values  $k = \sqrt{M/(L_1L_2)}$  obtained between the two identical coils for three different air-gap lengths, namely  $l_g = \{1.5, 3, 6\}$  mm. The air-gap  $l_g = 3$  mm has been herein selected for the final TX and RX coil set depicted in Figure 22c, since such a value yields sufficiently high self-inductances of the coils  $L_1 = L_2 = 23 \mu$ H and a coupling coefficient k = 0.53, which is a good trade-off solution for the considered application.

| <i>l<sub>g</sub></i> (mm) | $L_1, L_2$ (µH) | $R_{L1}, R_{L2}$ (m $\Omega$ ) | k    |

|---------------------------|-----------------|--------------------------------|------|

| 1.5                       | 35              | 50                             | 0.75 |

| 3                         | 23              | 50                             | 0.53 |

| 6                         | 20              | 50                             | 0.34 |

## 4.2. PR-IPTS Boards

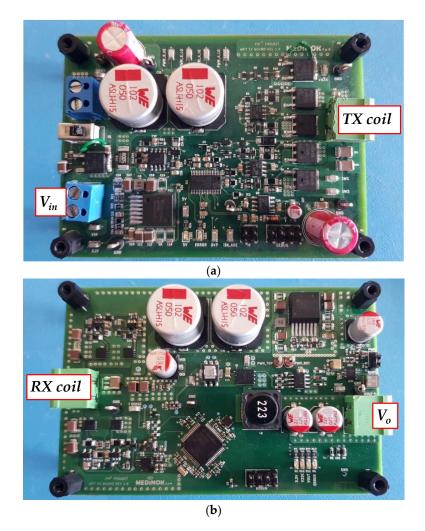

An experimental prototype of the proposed PR-IPTS has been assembled using the components listed in Table 7 (refer to Figures 12 and 22 for the IPTS and buck components, respectively). The realized custom Printed Circuit Boards (PCBs) of the IPT TX and RX stages are depicted in Figure 23, with the dimensions of 95 mm  $\times$  70 mm  $\times$  18 mm and 106 mm  $\times$  70 mm  $\times$  18 mm, respectively.

| Table 7. | PR-IPTS components | • |

|----------|--------------------|---|

|----------|--------------------|---|

| Circuit Components                              | Values                                                                  |

|-------------------------------------------------|-------------------------------------------------------------------------|

| Inverter MOSFETs $S_1$ – $S_4$                  | IPD50N04S4–10: $R_{ds} = 9.3 \text{ m}\Omega$ , $Qg = 14 \text{ nC}$    |

| Rectifier MOSFETs $M_1$ – $M_4$                 | BSZ070N08LS5: $Rds = 7 \text{ m}\Omega$ , $Qg = 14 \text{ nC}$          |

| Buck half bridge                                | BSC0993ND: $Rds_{HS} = 4.2 \text{ m}\Omega$ , $Qg_{HS} = 13 \text{ nC}$ |

| MOSFETs $M_{HS}$ - $M_{LS}$                     | $Rds_{LS} = 5.6 \text{ m}\Omega, Qg_{LS} = 6.7 \text{ nC}$              |

| TX and RX coils $L_1$ , $L_2$                   | $L_1 = L_2 = 23 \ \mu H$ , $R_{L1} = R_{L2} = 50 \ m \Omega$            |

| Buck output inductor <i>L</i> <sub>o</sub>      | $L_o = 22 \ \mu H$ , $R_{Lo} = 23 \ m \Omega$                           |

| TX and RX compensation capacitors $C_1$ , $C_2$ | $C_1 = 200 \text{ nF}, C_2 = 100 \text{ nF}$                            |

| IPTS input capacitor C <sub>in</sub>            | $C_{in} = 2440 \ \mu F$                                                 |

| Intermediate bus capacitor $C_f$                | $C_f = 2068 \ \mu F$                                                    |

| Buck output capacitor $C_o$                     | $C_o = 440 \ \mu\text{F}, ESR_o = 5 \ \text{m}\Omega$                   |

Figure 23. PCBs of the experimental prototype: (a) TX board; and (b) RX board.

On the TX board, the switching frequency and phase-shift modulation of the fullbridge inverter has been digitally implemented through the Infineon 32-bit XMC1302-T038X0064AB microcontroller with ARM<sup>®</sup> Cortex<sup>®</sup>-M0 [38], which allows to properly configure the peripherals using the proprietary Integrated Development Environment (IDE) Dave Infineon<sup>®</sup> [39]. Thus, two PWM signal pairs synchronized at the same switching frequency have been generated from two different DPWM peripherals of the Micro Controller Unit (MCU) and subsequently delivered to the IRS2106SPBF drivers of the two inverter legs [40]. Each PWM signal pair includes two complementary square-wave signals used to drive the high- and low-side MOSFETs of the respective leg, and a 100 ns dead-time has been introduced to prevent a cross-conduction of the switches. To realize a desired phase-shift angle, a delay has been added to the second PWM signal pair with respect to the first one. Both DPWM peripherals have a fixed time resolution  $t_{res} = 15.625$  ns, resulting in a number of discrete digital levels  $N_{DPWM}$  which depends on the desired inverter switching frequency  $f_s$ , according to (46):

$$N_{DPWM} = \left\lceil 0.5 \left( \frac{1}{f_s t_{res}} - 1 \right) \right\rceil \tag{46}$$

where a center-aligned mode of the DPWM peripherals has been set, which allows to realize a desired PWM period by first counting up from zero to the  $N_{DPWM}$  level and then down to zero [38]. For the switching frequency  $f_s = 100$  kHz, (46) yields  $N_{DPWM} = 320$ , while for  $f_s = 200$  kHz, it provides  $N_{DPWM} = 160$ . The delay between the two DPWM peripherals, needed to implement a normalized phase-shift angle in the range d = [0, 1], can then be realized with discrete DPWM steps in the range  $[0, N_{DPWM}]$ , resulting in the normalized phase-shift resolution  $\Delta d_{min}$  given by (47):

$$\Delta d_{min} = 1/N_{DPWM} \tag{47}$$

For  $f_s = 100$  kHz, (47) yields  $\Delta d_{min} = 0.003125$ , while for  $f_s = 200$  kHz, it provides  $\Delta d_{min} = 0.00625$ . Hence, the phase-shift resolution is lower than 1% for the switching frequency range of interest  $f_s = [100, 200]$  kHz.

On the RX board, the DVMC of the buck converter has been realized through the Infineon 32-bit XMC4200-F64X256 microcontroller with the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 [41]. Its main peripheral parameters of interest are provided in Table 5, where a high-resolution DPWM peripheral of the XMC4200 MCU has been adopted. The generated complementary DPWM signals are used to drive the buck MOSFETs  $M_{HS}$ - $M_{LS}$  through the IRS2011SPBF gate driver [42]. Each of the rectifier MOSFETs  $M_1$ - $M_4$  is switched by the respective IR1161LPBF controller [29], according to the synchronous rectification scheme previously described in Section 2.1.

## 4.3. Experimental Results

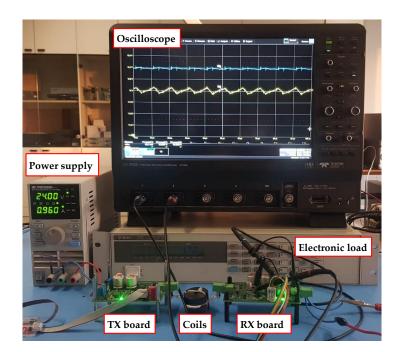

## 4.3.1. Efficiency Assessment with Electronic Load

The developed PR-IPTS prototype has been tested under different load conditions to assess its power and efficiency performances and output voltage regulating capabilities for variable load demands. Figure 24 shows a complete experimental set-up used during the tests, including the TX and RX boards with the coupling coils, a BK Precision 9111 180 W Multi Range 60 V/8 A DC Power Supply connected to the IPTS input, an HP Agilent Keysight 6060B 300 W 60 A/60 V DC Electronic Load connected to the system output, and a Teledyne LeCroy HDO9404 Digital Oscilloscope.

Figure 24. Experimental set-up used to test the developed PR-IPTS prototype.